# CMOSプロセス・フロー概要

群馬大学 松田順一

#### CMOSプロセス・フロー概要

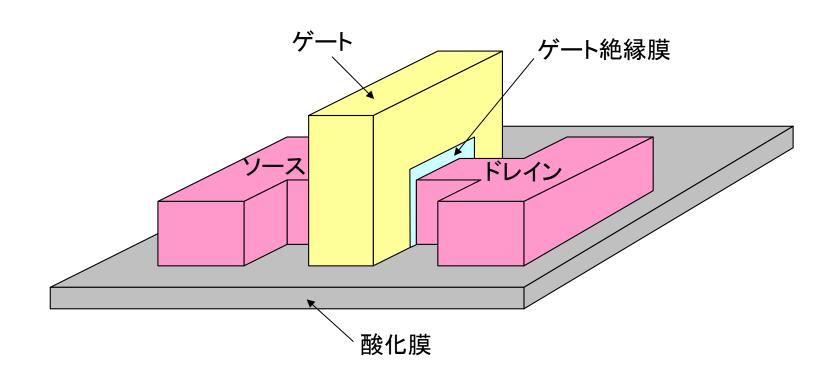

- ウエル形成 (n-MOSFETとp-MOSFETの分離)

- •素子分離形成(STI、LOCOS)

- MOSFET形成

- ・ゲート酸化膜形成

- ・ゲート電極形成

- サイドウォール形成(LDD構造)

- ・ソース・ドレイン形成

- 配線形成

- 層間膜形成、コンタクト(またはビア)形成、メタル配線形成

- パッシベーション膜形成

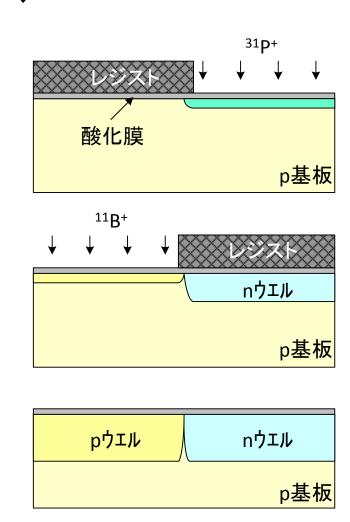

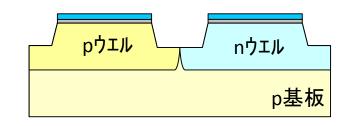

## CMOSプロセス・フロー(1)

熱酸化 レジスト塗布 nウエル領域露光 <sup>31</sup>P+イオン注入 レジスト除去

#### ウエル形成

レジスト塗布 pウエル領域露光 <sup>11</sup>B+ イオン注入 レジスト除去

ウエル拡散

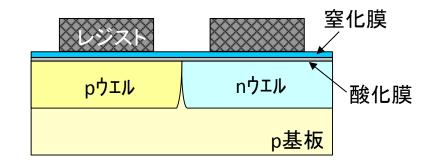

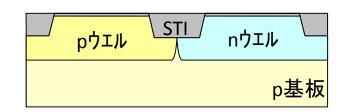

## CMOSプロセス・フロー(2)

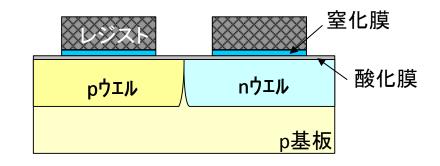

窒化膜デポジション レジスト塗布 STI領域露光

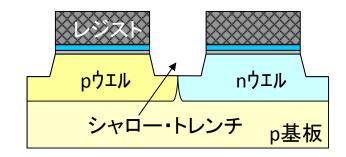

トレンチ形成 (素子分離)

トレンチ・エッチング

レジスト除去

STI (Shallow Trench Isolation)

#### CMOSプロセス・フロー(3)

熱酸化 HDP酸化膜デポジション 室化膜 Pウェル P基板

トレンチ埋め込み(素子分離)

HDP酸化膜平坦化 (CMP)

HDP (High Density Plasma)

CMP (Chemical Mechanical Polishing)

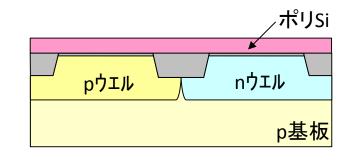

#### CMOSプロセス・フロー(4)

酸化膜除去 ゲート酸化 閾値電圧用イオン注入 ポリSiデポジション

#### ゲート形成

レジスト塗布 ゲート領域露光 ポリSiエッチング (ゲート形成) レジスト除去

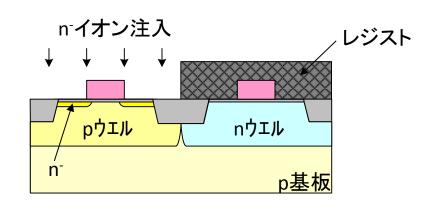

## CMOSプロセス・フロー(5)

レジスト塗布 n-ch Tr領域露光

n-形成用イオン注入

レジスト除去

LDD**形成** (ホット・キャリア耐性向上)

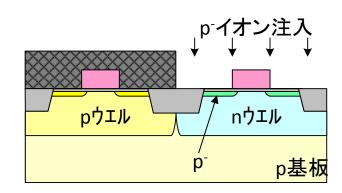

レジスト塗布 p-ch Tr領域露光 p-イオン注入 レジスト除去

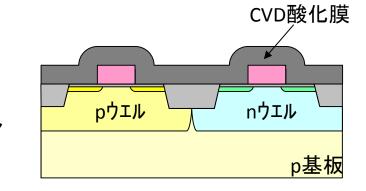

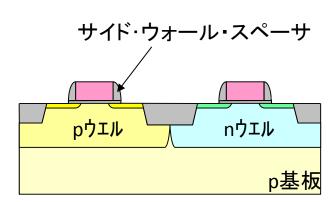

### CMOSプロセス・フロー(6)

CVD酸化膜デポジション

サイド・ウォール スペーサ形成 (ホット・キャリア耐性向上)

CVD酸化膜エッチング

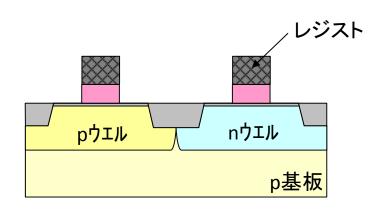

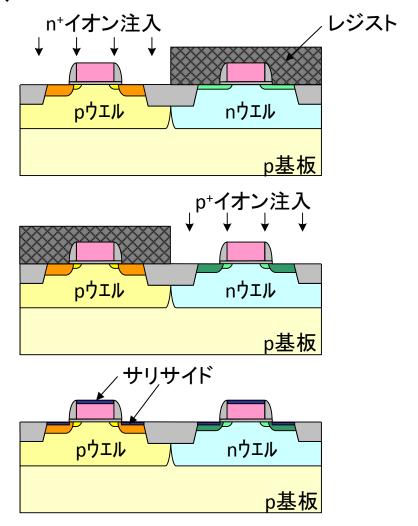

### CMOSプロセス・フロー(7)

レジスト塗布 n-ch Tr領域露光 n<sup>+</sup>イオン注入 レジスト除去

ソース・ドレイン形成

レジスト塗布 p-ch Tr領域露光 p<sup>+</sup>イオン注入 レジスト除去

サリサイド形成 (WSi, TiSi, CoSi, NiSi) ソース・ドレインの低抵抗化

サリサイド (Self Aligned Silicide)

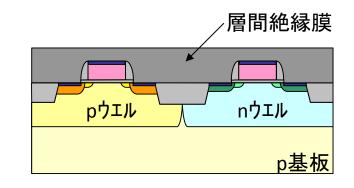

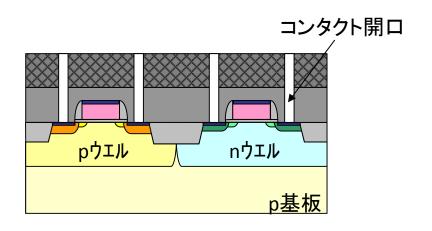

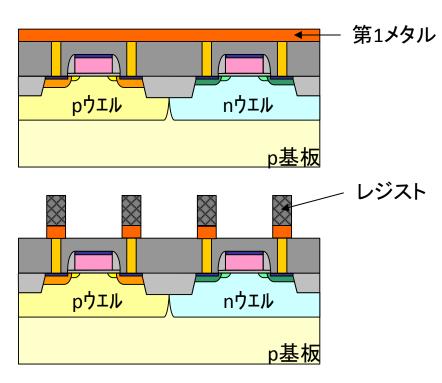

### CMOSプロセス・フロー(8)

層間絶縁膜デポジション 層間絶縁膜平坦化

層間膜及び コンタクト形成

> レジスト塗布 コンタクト領域露光 コンタクトエッチング レジスト除去

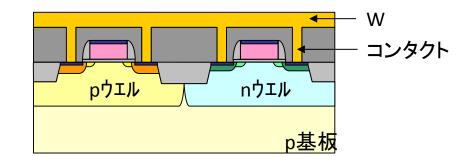

### CMOSプロセス・フロー(9)

バリア・メタル・スパッタ Wデポジション

#### メタル配線形成

Wエッチバック バリア・メタル・スパッタ 第1メタル・スパッタ バリア・メタル・ス パッタ

レジスト塗布 配線領域露光 第1メタル・エッチング レジスト除去

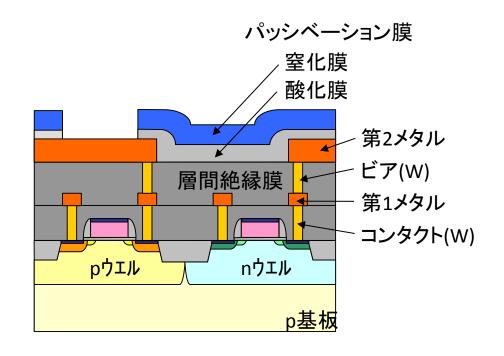

#### CMOSプロセス・フロー(10)

多層メタル配線 パッシベーション 膜形成 層間絶縁膜デポジション

ビア形成 (コンタクトと同様に形成)

第2メタル配線形成 (第1メタルと同様に形成)

パッシベーション膜形成 (窒化膜+酸化膜)

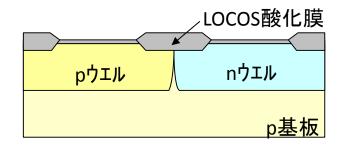

### CMOSプロセス・フロー(補足1)

レジスト塗布 素子分離領域露光 窒化膜エッチング レジスト除去

LOCOS形成 (素子分離)

LOCOS酸化

pウェル nウェル p基板

窒化膜エッチング

# FinFET(補足2)