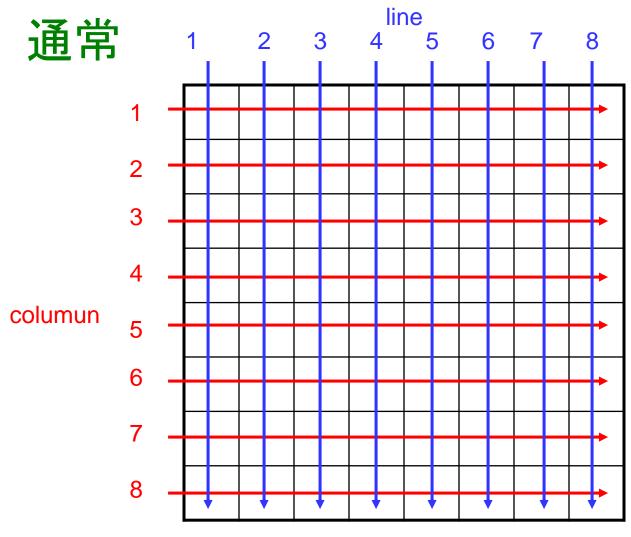

# アナログ集積回路のレイアウト技術

担当 群馬大学 大学院電気電子工学専攻 小林春夫

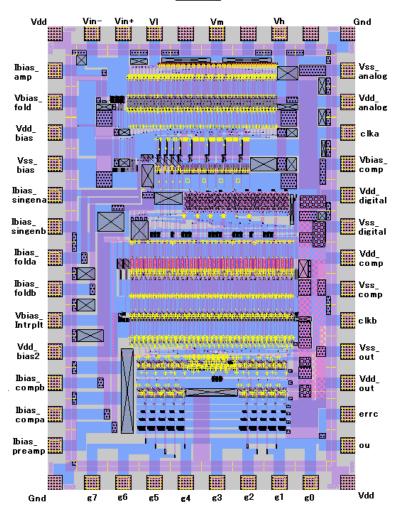

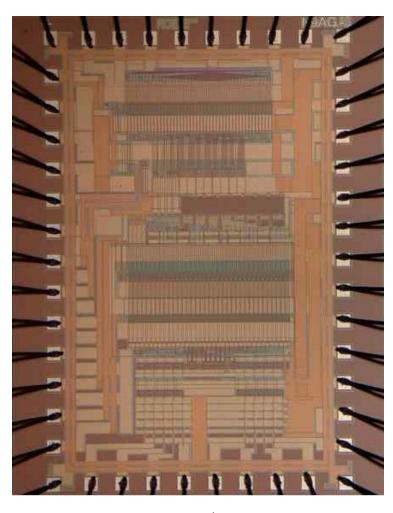

#### レイアウト設計(ICパターン設計)とIC

ADC.mag

CMOSアナログICの レイアウト設計

レイアウト設計データを もとにファブリケーション されたチップ

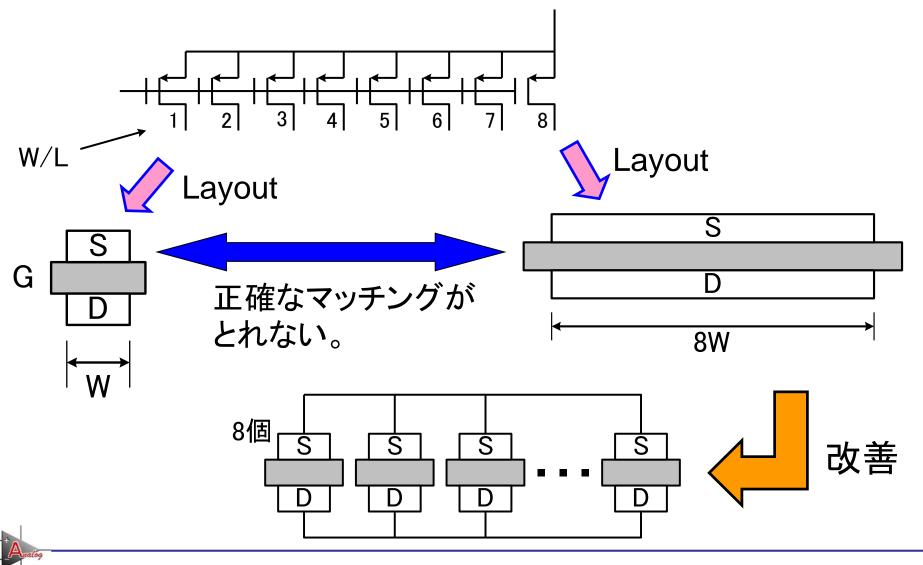

#### 電流モード回路での整数比電流発生回路のレイアウト

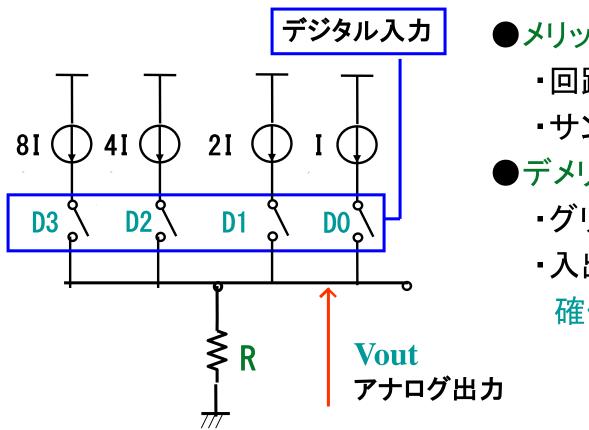

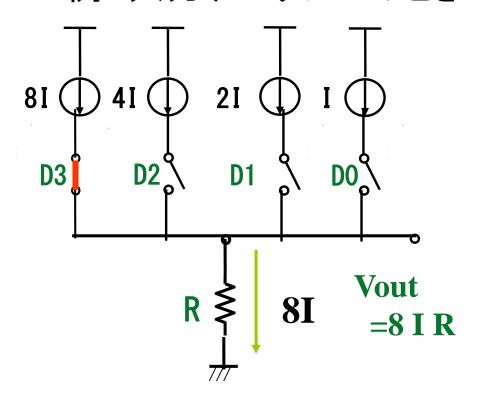

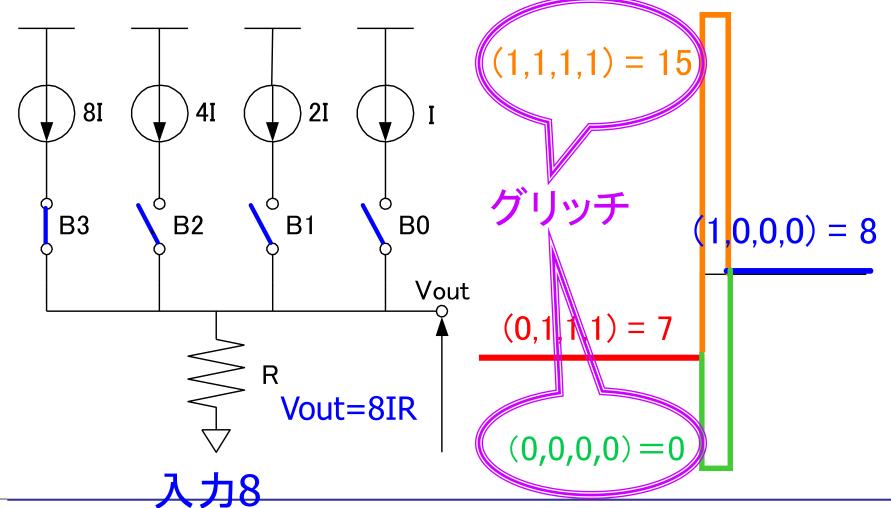

#### 電流型2進重み付け DA変換回路 (回路)

#### ●メリット

- ・回路規模が小さい

- サンプリング速度が速い

- ●デメリット

- グリッチが大きい

- ・入出力間の単調性が 確保出来ない

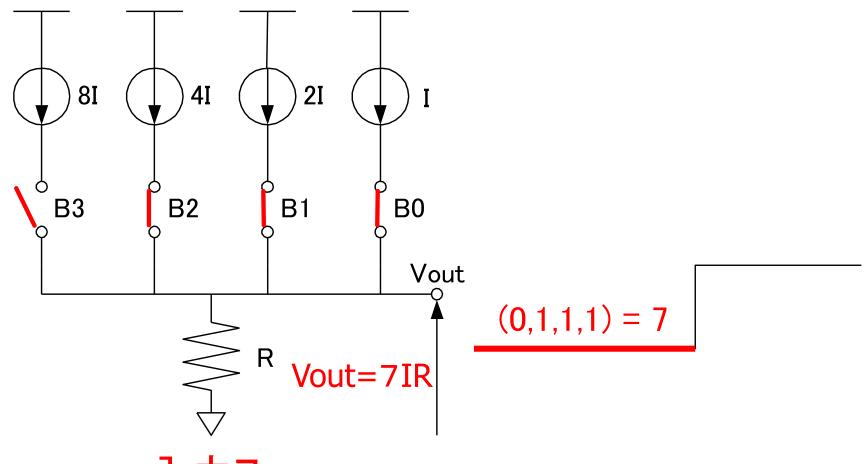

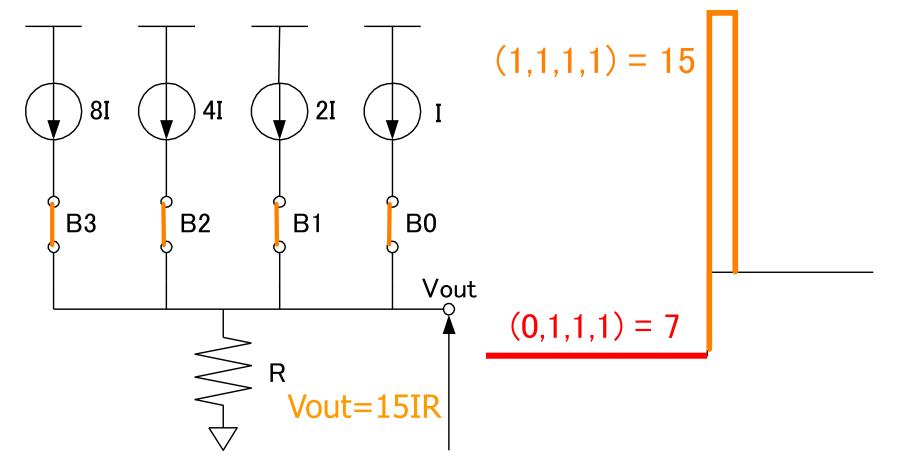

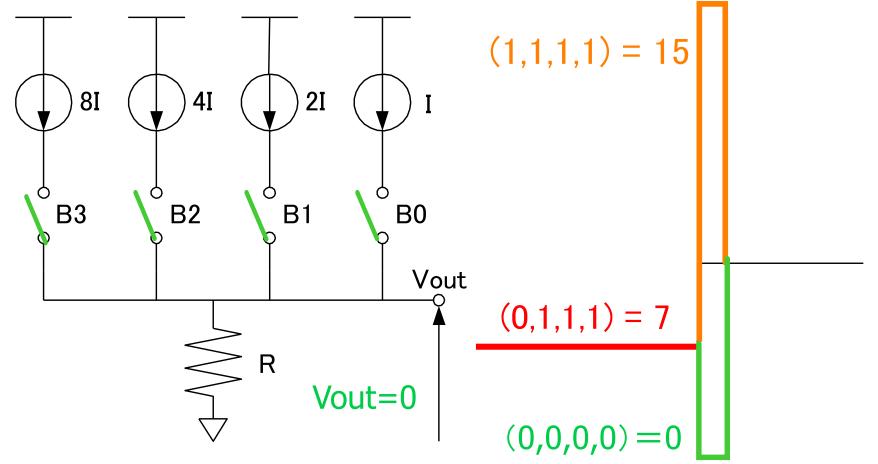

#### 電流型2進重み付け DA変換回路 (動作)

例: 入力データが3のとき

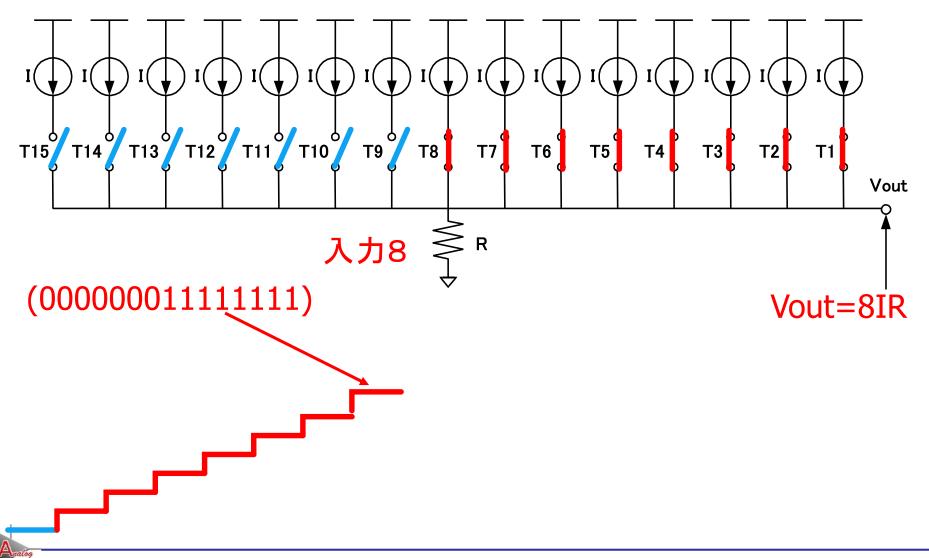

例: 入力データが8のとき

#### 2進重み付けDA変換回路

(原理)

| デジタル  | スイッチ |    |    | 出力 |         |

|-------|------|----|----|----|---------|

| 入力データ | D3   | D2 | D1 | D0 | Vout    |

| 0     | 0    | 0  | 0  | 0  | 0       |

| 1     | 0    | 0  | 0  | 1  | IR      |

| 2     | 0    | 0  | 1  | 0  | 2IR     |

| 3     | 0    | 0  | 1  | 1  | 3IR     |

| 4     | 0    | 1  | 0  | 0  | 4IR     |

| 5     | 0    | 1  | 0  | 1  | 5IR     |

| 6     | 0    | 1  | 1  | 0  | 6IR     |

| 7     | 0    | 1  | 1  | 1  | 7IR     |

| 8     | 1    | 0  | 0  | 0  | 8IR     |

| :     |      |    | :  |    | :       |

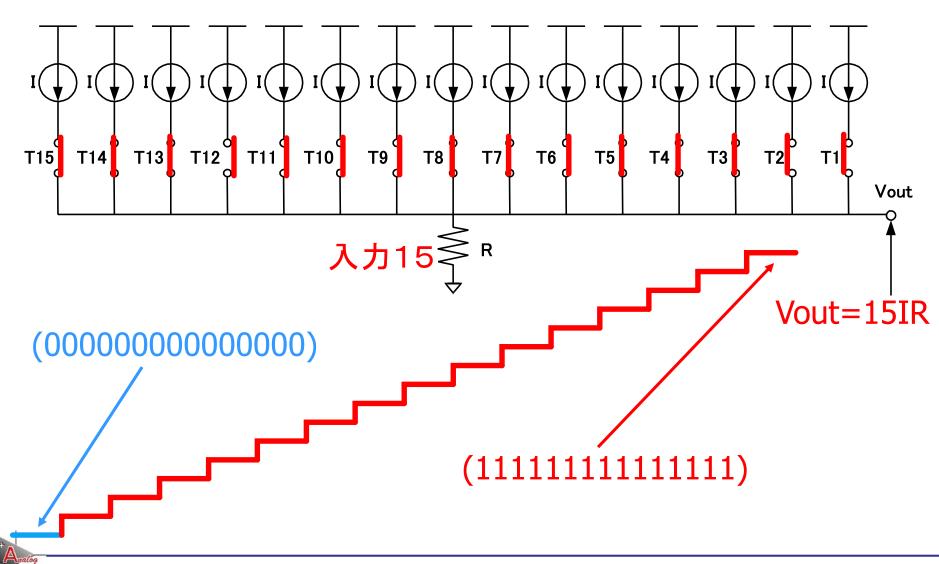

| 15    | 1    | 4  | 4  | 1  | 1 E T D |

スイッチ 1のとき ON 0のとき OFF

デジタル入力データに 比例したアナログ出力 Vout が生成される。

アナログ技術シリーズ・アナログ集積回路

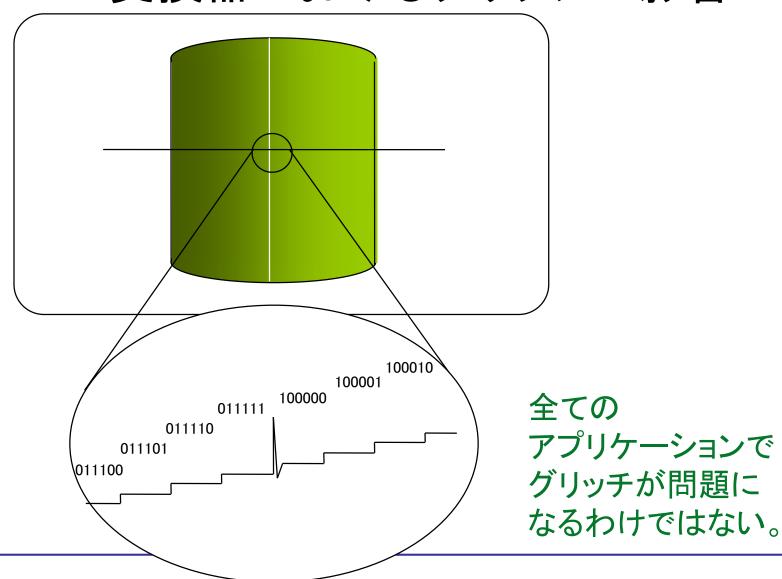

### グラフィックデスプレイ用 DA変換器におけるグリッチの影響

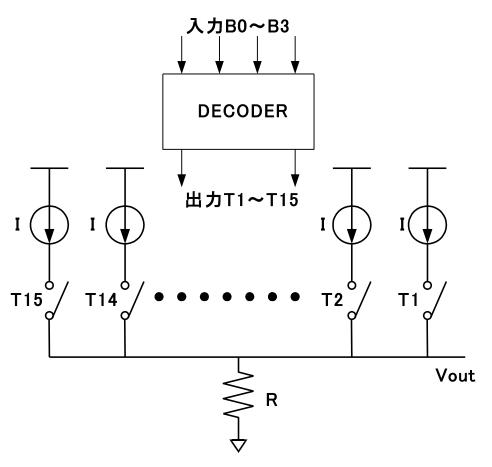

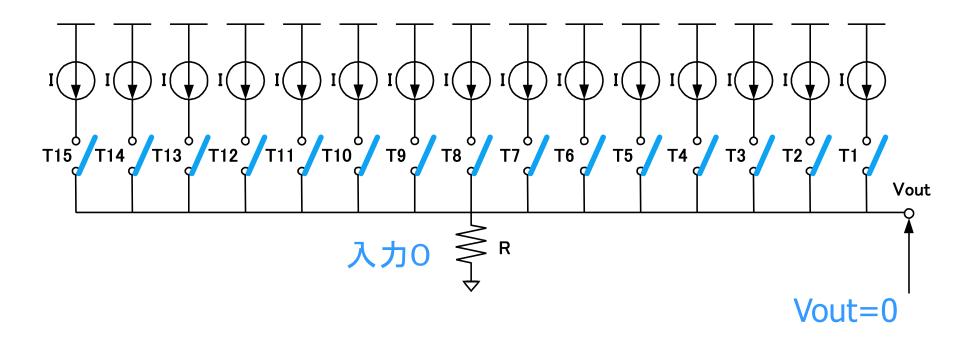

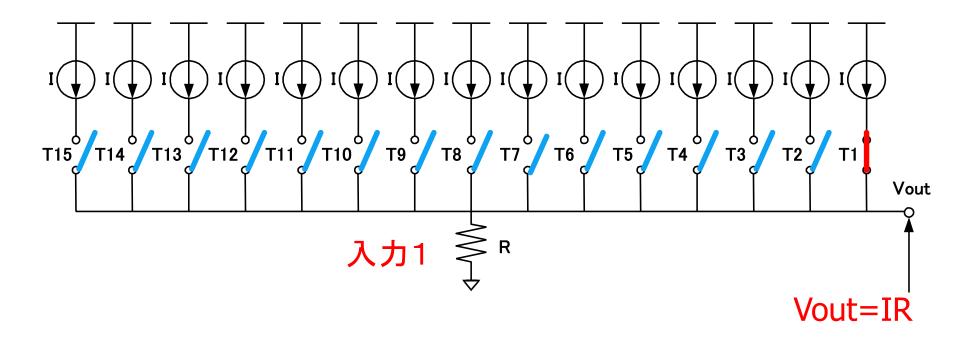

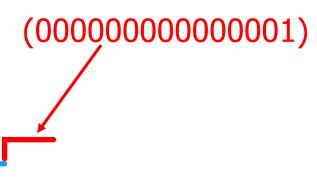

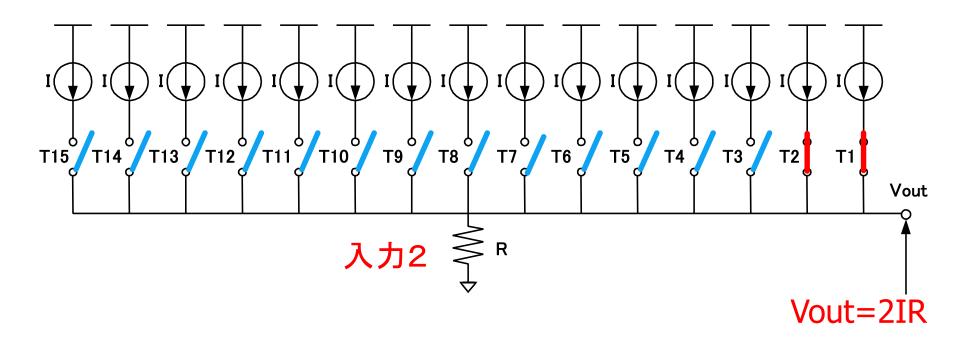

#### セグメント型DA変換器

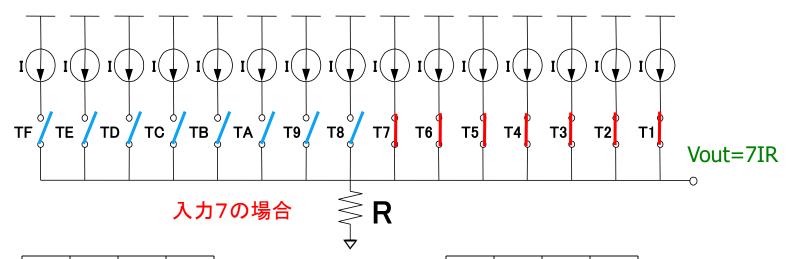

4bitセグメント型DA変換器

- ●メリット

- グリッチが小さい

- ・入出力間の単調性が

確保できる

- ●デメリット

- ・回路規模が大きい

- サンプリング速度が やや低下する

(00000000000000)

(00000000000011)

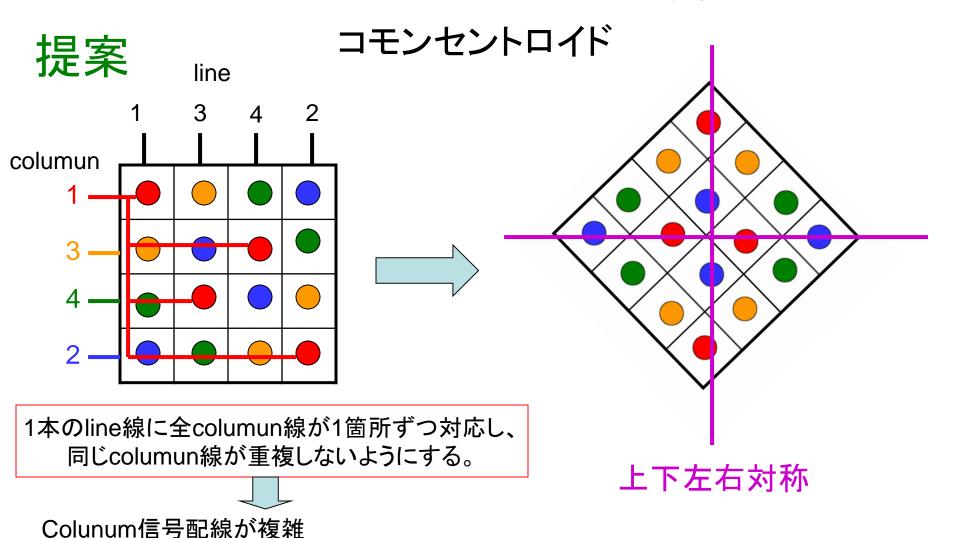

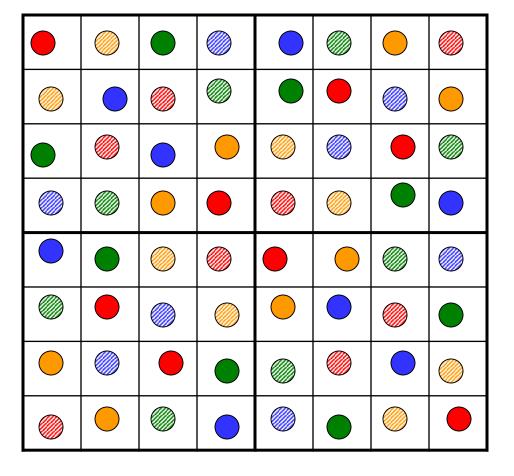

#### セグメント型DA変換器の電流セル配列のレイアウト

| T1 | T2 | Т3        | T4 |

|----|----|-----------|----|

| T5 | T6 | <b>T7</b> | T8 |

| T9 | TA | ТВ        | TC |

| TD | TE | TF        |    |

DAC線形性改善

| TE | Т3 | T7 | T9 |

|----|----|----|----|

| T6 | T1 | TC | T5 |

| T8 | TA | F  | ТВ |

| T4 | TD | T2 |    |

規則的に電流セルをレイアウト

Random Walk (酔歩)状にレイアウト

電流源のシステマテック・ミスマッチのDAC非線形性への影響

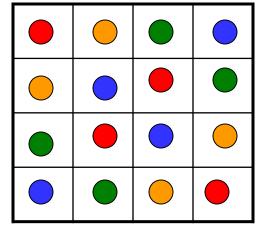

#### セグメントDACのONさせる順番

#### セグメントDACのONさせる順番

Local Decoderがそのまま使える。

アナログ技術シリーズ・アナログ集積回路

#### 6ビットの場合

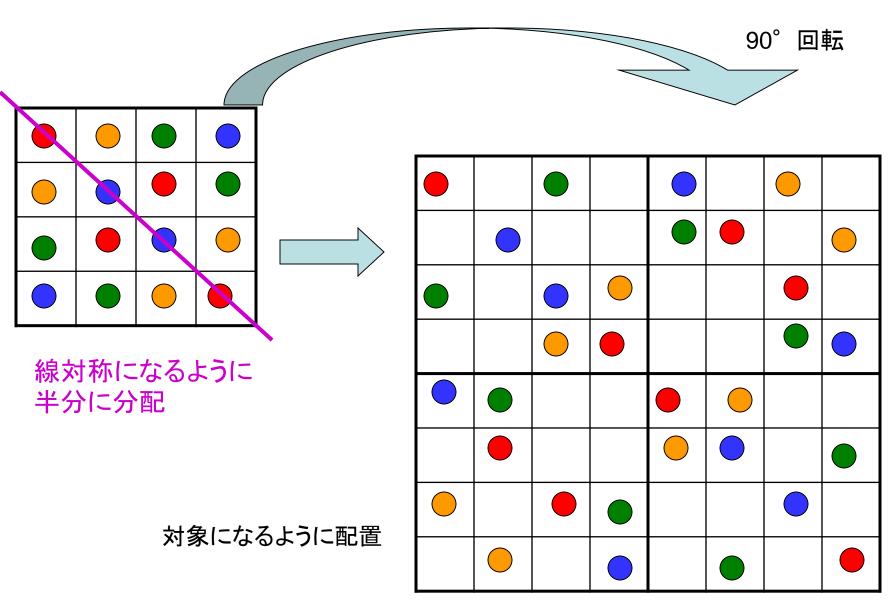

#### 6ビットの場合(8x8=64)

#### 前の4色と対象に追加の4色を配置

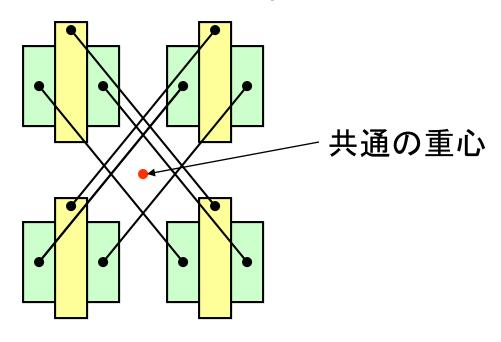

#### コモンセントロイド(Common Centroid) レイアウト

MOSトランジスタのペアのミスマッチ低減

Common Centroid配置

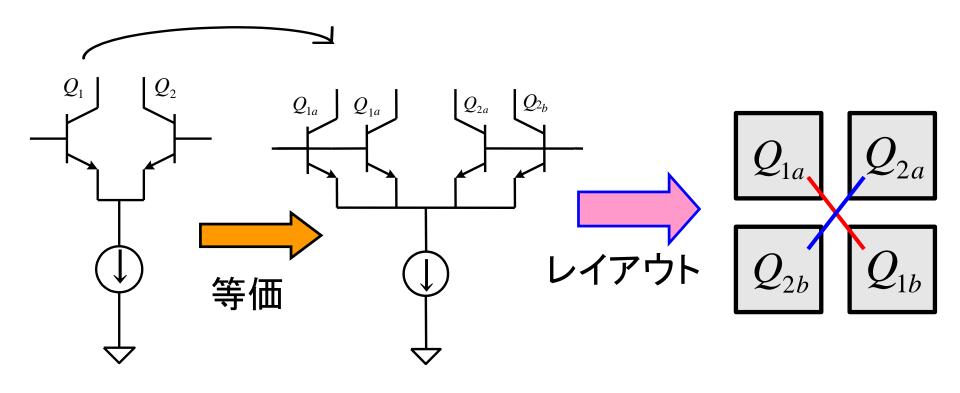

#### バイポーラトランジスタ・ペアのコモンセントロイド配置

面積半分のエミッタ2つに分解

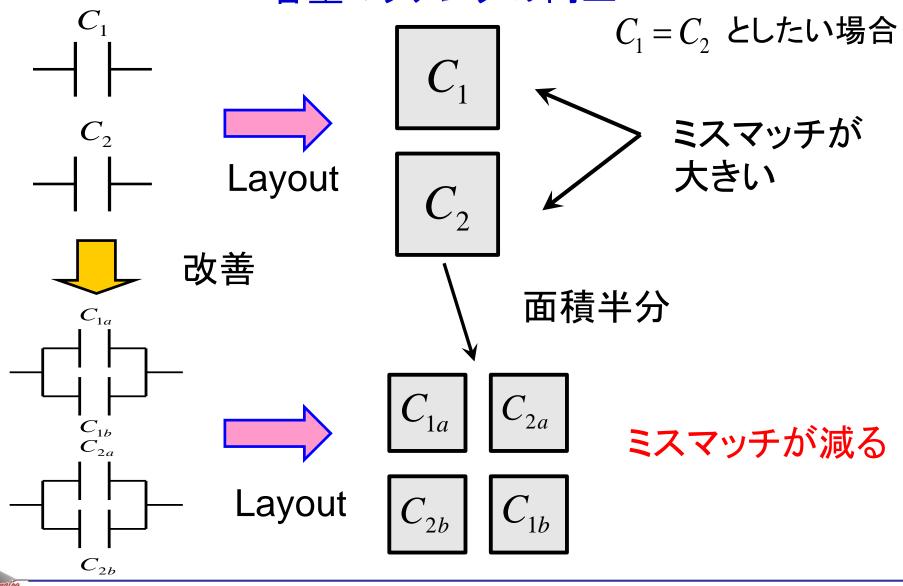

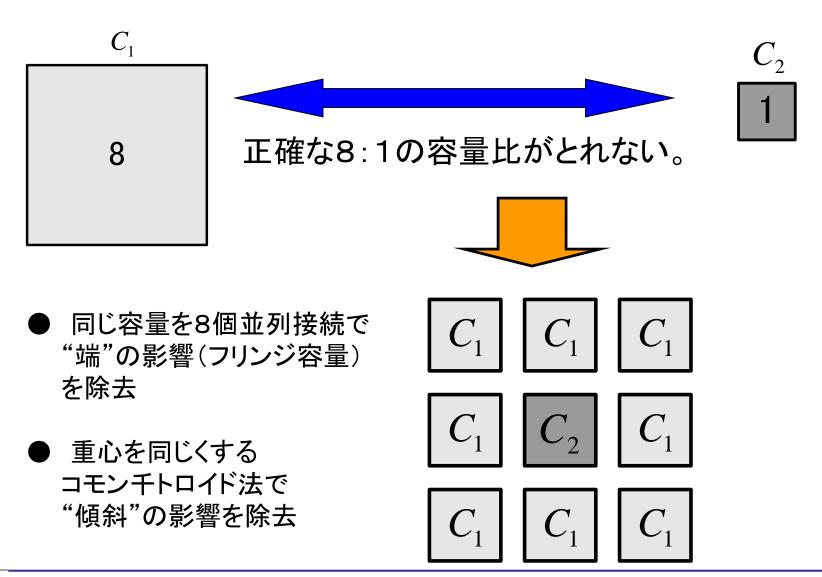

# コモンセントロイド・レイアウト法による 容量マッチングの向上

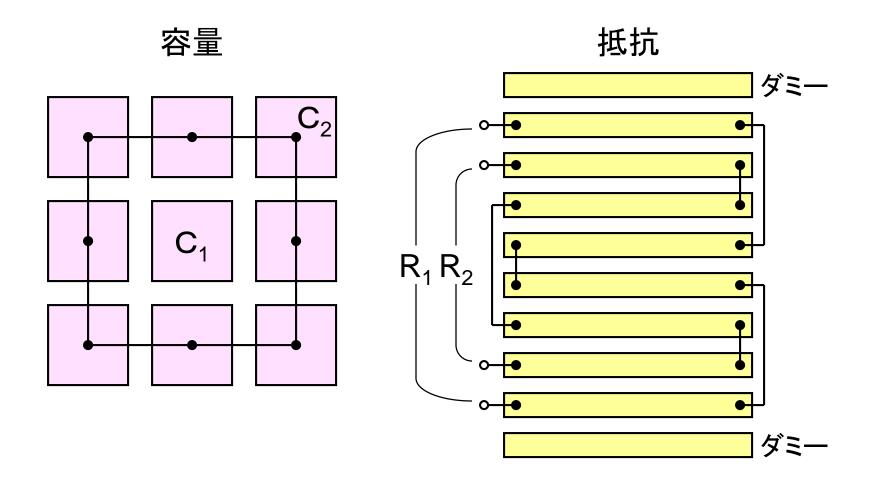

#### 容量のマッチングをとるためのレイアウト

#### R, C のミスマッチ低減のための

#### Common Centroid 配置

付録

# アナログ集積回路での 美しい回路/レイアウトとは何か

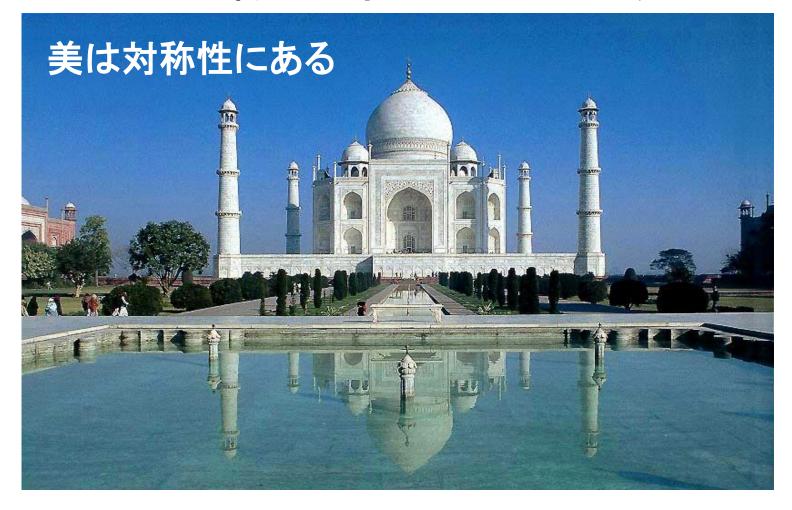

「美は対称性にある」(白石洋一先生)

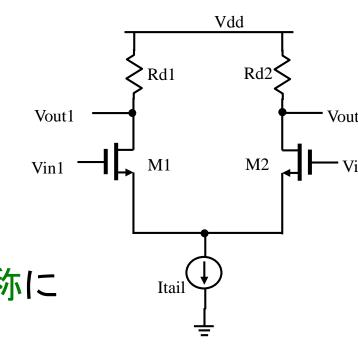

## アナログ回路のレイアウト

- 見た目が美しいのは 良いレイアウト

- 「美しいレイアウト」とは何か

その一つとして アナログ回路は<u>差動回路</u>が多用 回路が対称 → レイアウトも対称に

# レイアウト設計者が求める美しさ

タージマハール

群馬大学 白石洋一先生 資料より

アナログ技術シリーズ・アナログ集積回路

### UCLA Royce Hall 左右対称ではない

クイズ: なぜ対称に 作らなかったのか