# R3 年度 群馬大学電気電子工学特別講義 II (集積電子回路工学) 源代担当分最終レポート 解説

源代 裕治

#### 2022年1月4日

## 1 課題について

今回の講義では、回路を理解するために、従来の回路論の定式化とは異なる定式化を提案した。回路自体はひとつでも、それを見る立ち位置が違うので、違う様相が見えてくる。そんな回路論である。以下これを"我々の回路論"と呼ぼう。\*1

一連のレポート課題では我々の回路論をLTspiceを用いて体験してもらおうとした。しかし残念ながら、この意図はうまく伝わらなかったようで、皆さん、従来の回路論から課題に挑戦していた。講義とレポート課題は別物と認識していたようだ。

結果が正しければ、どちらの見方をしようと勝手ではないか、という主張も道理である。だが、別の見方は別の発想を生み、別の成果を生むことがある。従来の回路論を学んだ皆様には、その違いを堪能して欲しかったのである。

ここの解説では、我々の回路論の見方で回路を見る、あるいはむしろ鑑賞する、と どのように見えるかを述べて行きたい。学生諸子に於かれては、最終レポートで色々 と思案された後であろうから、今回はすんなり納得してもらえる、ことを期待して いる。

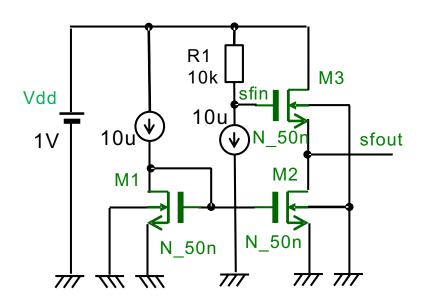

課題の回路を図1に示す。題意は、Source Follower(SF) の出力抵抗を色々な方向

<sup>\*1 &</sup>quot;新回路論"とか"公理的回路論"とかの呼び方も考えたが、しっくり来ない。私が独自に考案したものであるが、"私の回路論"というのも気が引ける。ということで、本稿では講義を聴講してくれた方を巻き込むような名前を使うことにする。

から考えよう、というものであった。そのまま言えば "sfout のノード抵抗を論ぜよ" で十分である。

図1 課題回路

その主旨をもう少し break down して、以下のような表現とした。

- 1. SF の出力抵抗を求めよ。

- 2. その出力抵抗を、シミュレーションを用いて構成要素に分解しなさい。候補しては、ゲートに付けた R1 10k  $\Omega$  の出力への効き、SF M3 の gm、そのバックゲートの gm、電流源 M2 のドレイン抵抗などが考えられる。1. の結果と辻褄が合うだろうか。

- 3. SF の出力抵抗を半分にしたい。どうやったら実現できるか。その場合のトレードオフは?

これらは課題の主旨を限定してものであるから、望むらくは、この表現をきっかけ として、様々な側面にドンドン展開して欲しかった。学問や技術というのは、そう やって学んで行くものであろう。

## 2 回路の鑑賞

課題そのものの取り扱いは、少し先、第4節に記す。手っ取り早く結果を知りたい方は、そこまで飛ばしても良いが、理解が表面的になってしまう危惧がある。ここは腰を落ち着けてもらいたい。

回路にそれぞれの意味や役割がある。この感覚は回路を鑑賞するときには重要でいるいろな数値や数式では表せない。設計者の責務は、素子達が各々の役割を果たしたときに、全体として上手く働くように、素子達を組織して行くことにある。

SF の役割で最大のものは、ゲートで受けた信号を、そのままソースに伝達することである。その存在意義は、出力の負荷込みのノード抵抗に対し、SF 自体の出力抵抗が十分に小さい所にある。この意味が分からなければ、"回路設計論 2021 講義資料\_4\_回路屋の身だしなみ"  $p.10\sim p.11$  を復習して欲しい。

Baker 先生の短チャネルモデルは、電源電圧 1V で動作すること、W や L が基本サイズ 50nm の整数倍で使うこと、W/L=2.5um/100nm で 10uA 流すこと、などがガイドラインとなっている。課題の設定はこのガイドラインに合わせてある。

回路の場所によって流したい電流値は相当違うし、それに合わせて W/L も調整することになるが、製造可能な最小サイズが 50nm であるという限界を超える微細寸法は使えないと考えるのが妥当であろう。また、どんなデバイスモデルにも適用限界がある。想定サイズ付近で最も精度が出るようにパラメータを合わせこんである。適用限界を超えると精度が保証されない。ベンダーのデバイスモデルでは、当然その適用限界が明示されているが、Baker さんの教育モデルでは不明である。なので、節度を持ってトランジスタサイズを決めた方が良い。一般的な相場感覚でいうと、基本サイズ 50nm に対し、W は 1000 倍、L は 10 倍までとするのが良いだろう。もちろん、十分な根拠がある分けではない。

考察の対象とするのは図 1 の M3 の SF である。周りの回路は M3 の動作点を決めるためにある。課題では、M3 のドレインは Vdd に、バックゲートは GND に繋いでいる。ゲートには Vdd から 100mV 下がった電位が供給される。M2 が M1 とのカレントミラーになっており、ドレイン電圧 (正確にはドレイン電位というべきだが、慣例に従う) に関わらず 10uA を流そうとする。このような役割を電流源 (CS:

Current Source) と呼ぶ。講義では真空管やディスリートのトランジスタの時代に用いられた動作点設定回路にも言及したが、IC 時代になってからはカレントミラーの電流源を用いることが普通になった。

M2 の CS がドレイン電圧に関わらず 10uA 流すと言っても、ドレイン電圧が変動すると、それに応じて電流値も変動する。M1 と M2 のドレイン電圧が異なると、M1 電流と M2 電流が一致しない。これを回路屋はミラー精度とかミラー誤差という観点で捕らえる。M1 のドレイン電圧はダイオード接続で決まっており、ミラーされる側のドレイン電位は信号レベルに依存して変わってくるので、精密に合わせることは出来ないが、ミラー誤差がどの程度になるかは、回路屋として把握しておく数値である。

さらに、ある限界以下にドレイン電圧が下がると、CS がもはや電流を引けなくなる。回路が動作する間、その限界を侵さないように、動作レンジを決める必要がある。これも回路屋が常に意識していなければならない制約である。M2 の CS の動作限界を見てもらうのが第6回レポート課題の主旨であった。

信号が SF を伝わるとき、M3 のゲート電位は上がったり下がったりするが、どこまで下げられるかというと、M2 のドレイン電流が大きく減じる電圧まで、というのが回路的見方である。経験的に、SF 電流の設計値に対し、ざっくり半分になるまでは特性劣化が許容できる。M2 の電流が半分になるドレイン電圧は電流源としてはかなりやばい所にあって、ちょっとの変化で大きく電流が減じるような動作点であろう。このような定性的な推察から、CS トランジスタの動作限界を見ると良い。

この動作限界は、MOS ではざっくりオーバードライブ電圧 (Vod) と一致する。 Vod は既習と思うが、ゲートソース間電圧 (Vgs) がトランジスタのスレッショルド電圧 (Vth) をどのくらい超えたところで使っているかを表す。式で書くと Vod = Vgs - Vth になるが、単なる差分として覚えると、いつまで経ってもトランジスタの気持ちが分からないと思う。 Vod は、MOS トランジスタの二乗則に出てくる因子で、トランジスタにどれだけ電流を流してやろうという気持ちを表しているのである。 CSトランジスタのドレイン電圧が Vod まで下がるとトランジスタが非飽和領域に入り、ドレイン電流を決めるのが Vod でなくなってくる。

Vth はトランジスタの種類によって決まってくるもので、設計者の選択肢は少な

い。課題では  $N_50n$  と指定されている。しかし大抵は正確には分からない値である。一方 Vgs はカレントミラーの駆動段、ダイオード接続の M1 のドレイン電圧である。CS の動作限界を広げるためには Vgs を下げれば良く、そのためには M1 と M2 の W を増やせば良い。L を小さくしても Vod を下げることができるが、今 100nm を使っているので、限界の 50nm に近い。

他方、電源電圧が許す場合、Vod はむしろ大きくした方が良い。Vod を下げる方向のサイズ調整は、ミラー精度の悪化を招く傾向があるからである。これにはいくつかのばらつきメカニズムが関与するので思案することは多いが、CSトランジスタのLは、信号パスのトランジスタよりLを長めにしたいというのが、回路屋の希望である。

今回のプロセスは Vth が大きめなので、1V で動作させる回路は何かと苦しくて、L=100nm くらいが実用限界の感触を持っている。Vdd=1.2V にすると、何かと設計が楽になる。そうしたら L=200nm くらいまで使えるようになるのではないだろうか。

この辺りの感覚は説明に困るが、回路屋は様々な制約に遭遇しながら、美しい回路を探り続けるのが仕事である。そのような経験を積んで、段々に身にける感覚だと思う。ただしそれでも見込み違いは多い。用心深さも適度に必要である。\*2

## 3 回路論の要約と言い洩らした事

講義で話したことをきちんと復習すると長くなるので、箇条書きでまとめることにする。これら個々の主張が絡み合って、全体として我々の回路論を構成する。Wilesさんの経験談を紹介したが、諸君もまだ真っ暗な部屋に入って、家具にぶつかりながら探りまわっている最中かもしれない。しかし、およその様子が想像できるくらい動き回った後になって、どこかにある照明のスイッチを見つける瞬間に遭遇する。それを点けた途端、その部屋がどうなっているかが一望できる。そこまで、よく考えてもらうことを期待する。

<sup>\*2</sup> 電気系の学生の全てが回路の専門家になるわけではないが、電気系で学んだという経歴には、回路で色々と思案した経験が必要なものではないかと思う。今後どの分野に進むにしろ、その修業は無駄にはなるまい。

- 1. 回路とは、電位と電流を持つ graph である。

- ここで graph とは数学用語で、点と線分の接続関係だけに注目し、他の要素を切り捨てた対象を指す。入門的には、長さが伸び縮みしても変わらない幾何学的性質を研究する、と説明されるが、graph には本来"長さ"の概念がないことを注意しておこう。\*3

- 点のことを node、線のことを branch と呼ぶ。これらは数学で graph を 扱うときの用語とは異なるが、電気系 CAD の主要企業である Cadence 用語を用いることにする。

- 回路 graph には node ごとに割り当てられた scalar 属性と、branch ごとに割り当てられた scalar 属性があり、前者を"電位"、後者を"電流"と呼ぶ。

- 2. branch には2つの端子 (terminals) があり、それらはどこかのノードに繋がっている。

- 片側だけつながっている branch 等を対象にしない点で、回路 graph は 一般の graph よりは限定されている。

- 3. branch の電流は、片方の端から入って、反対の端から同じ大きさで出てくる。

- この性質により、電流は branch の中を "伝わる" ように見える。

- 流入する電流を正値、流出する電流を負値で表す習慣である。

- branch の向きを先に決めてから、電流値の正負を決めると考るのも良い。

- branch の両端で、電流の絶対値は同じで、極性が逆という見方もできる。

- 回路シミュレータの本を見ると、この性質を違う観点からの名称で"スタンプ規則"と呼んでいる。しかし、当然の性質として利用していて、その根拠は示していない。我々の回路論では、これは公理である。

- 4. どの node も、branch からの電流の総和は 0 である。これを Kirchhoff の電流則 (KCV) という。

- KCL により、branch の属性 (すなわち電流) と node の属性 (すなわち電流) が関係付けられる。

<sup>\*&</sup>lt;sup>3</sup> そんな幾何学的性質があるのか疑問に思うかもしれない。例えば、一筆書きで書けるかどうかは、graph 的性質である。

- KCL は "電流保存則" であるが、電磁気学でいう Ampere の法則ではない。我々の回路論の現段階では、長さの概念も時間の概念も未だ定義されていないのである。

- 回路の実装では、node は配線、branch は素子である。これでは graph の点と線との対応が逆ではないかという違和感を持つかも知れない。この違和感を払拭する説明は私自身持っていないが、graph 論には "双対性 (そうついせい) がある。点と線という単語を入れ替えても理論が成立するという不思議な性質である。むしろ数学の graph 論の入門で、点は長さを持たないもの、線は伸びているものという既存幾何からのイメージを流用することで、誤解を与えている所が大きいように思う。

- 5. branch 両端の電位の差 (電位差) を "電圧" という。

- どちらの端子電位からどちらの端子電位を引くかは辻褄があっていれば 良いが、branch の向きと会わせると良い。

- どこかのノードから出発して、もとのノードに戻ってくる経路に対し、電圧の総和は 0 になる。同じノードの電位差を求めているのであるから、当然の帰結である。これは Kirchhoff の電圧則 (KVL) と呼ばれる。 KCLが回路の公理なのに対し、我々の回路論では、KVL は単なる定理 (公理系から導かれる有用な命題) である。

- 6. branch の性質は、その両端の電圧 V と、そこに流れる電流 I の関係で特徴づけられる。

- branch 特性は IV 平面上の曲線で特徴付けられると言って良い。

- 7. IV 特性が原点を通る直線であるような branch を"抵抗"という。

- その IV 直線の傾きを conductance という。単位は S(ジーメンス)。その 逆数が抵抗値で、単位は  $\Omega$  (オーム) である。

- Ohm の法則は我々の回路論では抵抗の定義である。物理現象とのリンクは、別途検証する問題である。

- 8. IV 特性が垂直の branch を電圧源、水平のものを電流源という。

- 電圧の単位は V(ボルト)、電流の単位は A(アンペア) である。

- 電圧源は電圧を供給するものという歴史的刷り込みがあるが、我々の回路

論では、どんな電流を流しても電圧が変わらない branch を指す。

- 同様に、電流源はどんな電圧を与えても電流が変わらない branch である。

- 0 V の電圧源は 0  $\Omega$ 抵抗と同じである。 0 A の電流源は配線が途切れているのと同じである。

- 9. 複数の branches から成る回路で、うち2つの nodes を選んでその IV 特性を考えることができる。同じ IV 特性を持つ任意の回路は、それを含むもっと大きな回路に含まれるとき、どのように構成されているかは区別できない。そこでこれらを"等価回路"と呼ぶ。

- 同じ IV 特性を持つ等価回路は無数に存在する。

- 複数の branch を組み合わせて作る等価回路を "複合 branch" と呼ぶことにする。\*4

- 10. IV 特性が直線になる任意の branch は、適切な値を持つ 抵抗、電圧源、電流源の複合 branch で構成できる。これを"直線性定理"という。

- IV 直線は、直線上の1点の位置と傾きが決まれば、一意に定まる。

- 直線の V 切片と傾きに注目して作る等価回路が "Thevenin 等価回路" である。

- 直線の I 切片に傾きに注目して作る等価回路が "Norton 等価回路" である。

- いずれの等価回路でも傾きが同じなので、抵抗値も同じになる。

- ただし、Thevenin は抵抗 branch、Norton はコンダクタ branch を使っていると考える方が、理論的には正しいかも知れない。

- 11. branch の中には、よその branch の電流とか、よその node の電位とかに依存して IV 特性が決まるものもある。

- このような特性を持つ実デバイスを一般に"能動素子"と呼んでいる。

- 我々の回路論から見れば、このような branch は "受動 branch" と呼ぶべきものであるが、慣例に従おう。

- 能動素子の IV 特性は総じて非線形である。そこで回路では、能動素子を

<sup>\*4</sup> 一般には合成抵抗など "合成" という用語の方が良く使われる。用語の違いは目的意識の差で、組み合わせた結果そうなっちゃったという受動的立場か、所望の IV 特性を得るために branches を組み合わせて作ったという能動的立場かによるものであろう。

どの領域で使うか、あるいは別の言い方で"動作点"をどこに設定するか、 が重要になってくる。

• シミュレータでは、どの解析の前でも動作点解析 (OP 解析) を必ず実行する。設計された回路の動作点がどこにあるかを探ってくれる訳である。 しかし、それが適切な動作点であるかは、シミュレータの関知するところではない。

実際の回路は GND と電源の間で動作する。どんな複雑な回路でも、これら二つの特別な nodes の近くに全てが繋がっていると考えてよい。この点で回路 graph は、一般の graph よりかなり限定された graph と思える。GND は電位の基準 0 を与えるもので、全ての nodes は GND に至る道を持つ。これにより各 node の電位が決まる。シミュレータは電圧ではなく電位で方程式を立てるので、スケマに GND を入れておかないと動かない。今回の講義では扱わなかったが、容量素子があると電位が決まらない node が出てくる可能性がある。逃げ手として OP 解析では、容量素子に並列に大抵抗を付けて node 電位を確定している。

このような状況は講義のときには私自身認識していなかったが、ちゃんと説明しておくべきであった。この状況があって、回路内の任意の node で GND に対する Thevenin 等価回路を考えることに意味が出てくる。その抵抗値をノード抵抗という。もっと普通に使われる用語に"ノードインピーダンス"という言い方がある。それはそれで良いのであるが、インピーダンスは乱用気味の用語なので、抵抗を指すときは出来るだけ抵抗と呼ぶことにする。

node の抵抗は IV 直線の傾きなので、原点から動作点に直線を引いても求まらないのが普通である。例外は IV 直線がタマタマ原点を通過する場合だけである。\*5 ノード抵抗を求めるときに、原点から直線を引くことはシバシバ犯す間違いなので、要注意である。そもそも、動作点の電位は分かっても、どの branch 電流を使うかに合理性はないので、IV 平面上の 1 点を選ぶことは出来ない。

正しく IV 直線の傾きを求めるには、その node の電位を少し変動させたときに、 どれだけ電流が流れるか、あるいは少し電流を注入したときに node の電位がどれだ

<sup>\*&</sup>lt;sup>5</sup> 同様の状況は、遅延と群遅延の関係においても同様である。群遅延を原点を通らない直線とする解説は少ないが、そのような画が見えると、両者の違いが良く分かるだろう。

け変化するかを見る必要がある。この時、IV 特性が直線とみなせる範囲で変化させるている必要がある。node の IV 特性は大抵非線形なので、変化させすぎてはいけない。

従来の回路論ではこの辺りを、V/I と  $\Delta$   $V/\Delta$  I (あるいは微分記号を用いて dV/dI) の違いとして説明している。これは実際の作業と一致するので分かりやすいのだが、我々の回路論は、ノードの動作点において、IV 曲線と出来るだけ良く重なる直線を探し、その傾きとしてノード抵抗を把握するという見方をする。頭の中の IV 平面で、直線を動かすのである。

電源は GND から電圧源でつながっており、理想的には (つまり単純モデルでは) ノード間抵抗は 0  $\Omega$ である。そこでノード抵抗を見るときには、対 GND で見ても、対電源で見ても同じ値となる。そこでノード抵抗を調べるときには、電源を基準としても良い。これも、感覚として身に着けておくべき知識である。

## 4 課題の解答

#### 4.1 設問1の説明

1番で問うている SF の出力抵抗とは、GND に対する sfout ノードの、その動作点における IV 特性の傾きである。この問題は第 3 回レポート課題で既に経験してもらった。気づいた学生さんは少なかったが、これを思い出してもらいたかった。今、当時の作業を復習してもらえば、理解が深まると思う。

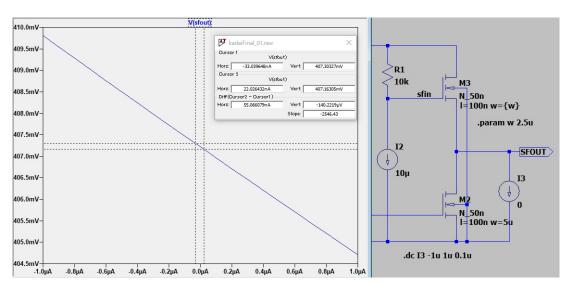

レポート課題3では、ノードの電圧を振ることでノード抵抗を調べたが、この方法だとまず動作点を求めるシミュレーションをしてノードの電位を求め、次に電圧源をつないで電圧を振った時の電流を見るという手順となる。もう少し楽な方法は、電圧源ではなく電流源をつなぐことである。電流源電流を0にしておけば動作点解析(OP解析)がズレることはなく、0から電流値をスイープ(DC解析)すれば、その傾きからノードの抵抗値が分かる。

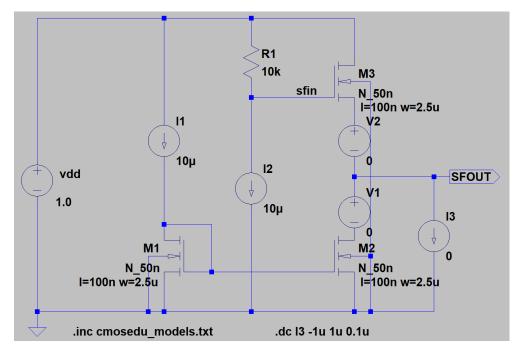

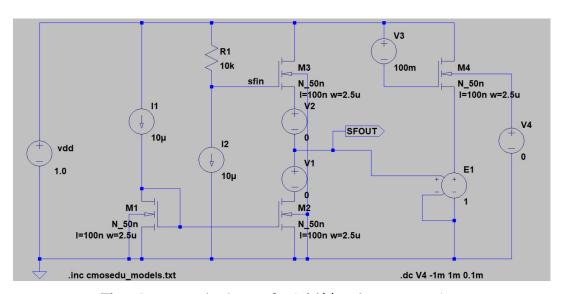

図 2 に LTspice の回路図 (スケマ) を示す。 I3 が測定用の電流源である。

スケマ入力ではいくつか、根本的間違いを犯していた方がいた。

まず、LTspice の NMOS シンボルは、大きく nmos と nmos4 に分かれる。前者

図2 出力に電流源を付加した LTspice スケマ

はバックゲートをドレインに接続済みのもので、後者はバックゲートもオープンになっている4端子素子である。この両者は設定可能なプロパティが違うので、たとえバックゲートをドレインにつなぐ使い方であっても混同はできない。今回は nmos4のシンボルを用いなければならない。

4 端子 MOS を用いたとしても、LTspice デフォルトでは NMOS という素子を呼びに行く。これがどんな素子かは知らない。(Vth が大分大きいので、どうやら Long Channel のプロセスのトランジスタらしい。) 課題で指定しているトランジスタは Baker さんのデバイスモデルの short channel MOS なので、Model Name を NMOS から  $N_50n$  に書き換えておく必要がある。

ついでに、nmos4 のシンボルはそのままでは W/L を表示しない。それが見えないスケマは間違いの元なので、この属性を visible にしておく必要がある。LTspiceでは、マウスカーソルをシンボルの上に置いて、CTL+ 右ボタンでメニューを出すという、使いにくいし見つけにくい設計になっている。であるにしても、その手間を惜しむべきでない。

トランジスタの Model Name を変更して、.inc なり.lib なりでモデルの実体ファイルとのリンクを取ることで、シミュレーションが可能になる。この辺りの注意は講義中に何度か指摘したが、聞き漏らした学生さんが結構いた。

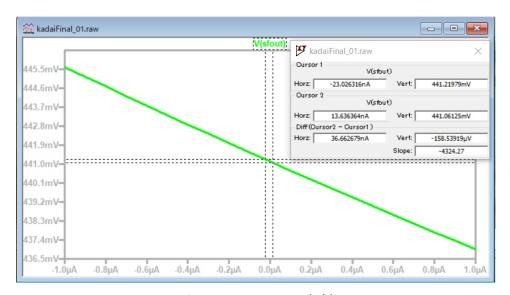

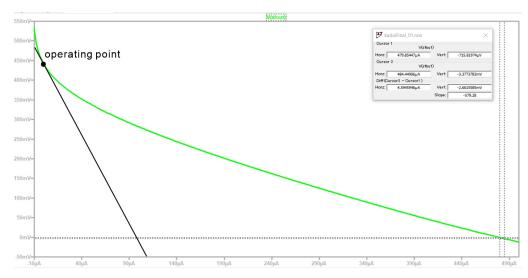

電流源 I3 の DC 値を 0 にしておくことで、OP 解析 (動作点解析) 結果に影響を与えない。DC 解析では I3 の電流値を少し振って、その傾きを見る。0 から始めても良いが、0 を挟む形で正負対象にスイープ電流を指定すると、電流が0 の時の傾き測定精度が上がるだろう。結果を図 3 に示す。スイープした範囲で IV 曲線が直線に近い。カーソル値のウインドウから、傾きはは 4324  $\Omega$ であることがわかる。カーソル位置で読み値は微妙に変わるが、回路鑑賞には大抵 2 桁の精度があれば良い。

図3 SFOUT の DC 解析

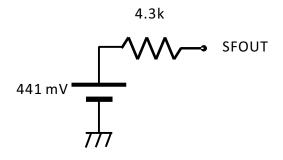

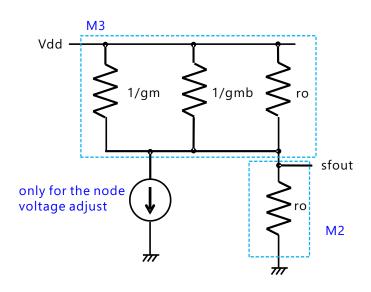

動作点付近での SFOUT は、図 4 に示す Thevenin 等価回路であることが見えてくるであろうか。

図 4 SFOUT の Thevenin 等価回路

この抵抗値を求めるのに TR 解析を用いた方が何名かいた。結果が一致しているので、方法としては問題ないだろう。ただし、自分が何をやっていたかを把握している必要がある。何と言っても、伝達関数とは何か、という問いと、ノード抵抗はいく

ら、という問いは牛刀と果物ナイフくらいの違いがある。

回路の鑑賞時にもう一つ注意しておくべき点は、I3=0A のときに 441mV という SFOUT の電位である。これは、M2 の電流源が動作するのに十分な電位であろう。 信号変化により sfin が変動するとき、その変動幅 (ダイナミックレンジ) が気になるが、vdd-0.2V までは全く問題あるまい。換言すると、この回路では 200mV 程度の振幅の信号が通せるに違いない。

念のため、という意味であれば、各部の電位や電流を見て、所望の値であるかを確認すると良い。実設計でも、回路の各部の波形観測は重要で、回路の動きを理解し、どこが苦しくてどこに余裕があるかを把握する作業は、必須に近い。\*6

I3 電流のスイープ幅をもっと広げると、図 5 に示すように、IV 特性は直線とはとても言えなくなる。これが一般に回路の非線形性と言われるものである。シミュレーション結果に手書きで、動作点の黒丸と図 4 の IV 直線を追記した。IV 直線はIV 曲線の動作点における接線になっている様子が観測できる。

SFOUT が 0 になる付近では、出力抵抗が 580  $\Omega$ 程度にまで低下している。M3 にこんなに電流を流すところまでトランジスタモデルが合わせこまれているか疑問であるが、その時の電流が 479 $\mu$ A くらいである。SFOUT を GND にショートすると、この電流が流れる。何人かの方は、SFOUT の元の電位が 441 $\mu$ A であるから、R=V/I=441 $\mu$ A79 $\mu$ 921  $\mu$ 0と計算していた。この方法は線形回路で良く見かける解説に従っていると思うが、見ているものが間違っている。

SF にとって、電流を引っ張るときより気になるのが、電流を流し込んだときの挙動である。M3 には 10uA 流す動作点に設計しているが、SFOUT に外から 10uA 流し込んだらどうなるか。M2 はいつでも 10uA を引こうとするので、外部から入れた電流がそっくり M2 に流れて、M3 に流れる電流が 0 になる。この状態で SF は全く機能しない。その状態に至るまでに図 5 から分かるように急激な抵抗増加がある。\*7

M2 が引けるよりもっと多くの電流を外から流し込むとどうなるか。推察し、シ ミュレーションし、結果を考察する。是非、自分で研究していただきたい。

シミュレータに関し、何人かの学生さんは、DC 解析をすべきところで TRAN 解

<sup>\*6</sup> コーナー解析だけをして事足れり、とするエンジニアは、何年経験を積んでも回路の気持ちが理解できないと思う

<sup>\*7</sup> 図5のどこをどんな風に見るか、もう分るよね?

図 5 SFOUT の DC 解析 (レンジ拡張版)

析をしていた。現場のエンジニアでも手ぬきをするときはそうすることもあるが、両者の違いは明確に意識している。それを認識せずに TRAN 解析を使っているのではないかと懸念した。講義で TRAN 解析を扱わなかったのは必要なかったからだけでなく、それを使ってはいけない問題だったからである。

ではなぜ Spice は、こんなに様々な解析を用意しているのか。ひとつに統一できないのか。というのは、当然湧いて来る疑問である。こちらも電気系の B3 には是非、自分で研究していただきたい。

#### 4.2 設問2の説明

設問 1 で求めた SFOUT のノード抵抗  $4324~\Omega$ が、回路的にどのようにして決まってきているかを要因に分解しようという問題である。設計の現場では、要因毎のオーダー感を持っていないと仕事にならない。

SFOUT に繋がっているのは、M3のソースと M2のドレインの二つである。ここに当然出力負荷がつながってきて SF 回路のゲインとか最大スルーレートとかが決まってくるのである。無負荷の状態でノード抵抗 (この場合は出力抵抗とも言う) を見積もっておけば、どの程度の負荷なら駆動可能かを見積もれるのである。

M2 のドレイン抵抗は第 6 回レポート課題で見積もった。今回の課題とはドレイン電流に微妙な差があるが、164k  $\Omega$ 付近の値であることは変わるまい。M3 側も同じドレイン抵抗が見えている筈なので、両ドレイン抵抗は並列接続で 80k  $\Omega$ 付近の

オーダーになる。これは観測されている (simulation 結果だが) SFOUT 抵抗 4.3k  $\Omega$  に比べて十分大きい。これから、ドレイン抵抗は出力抵抗にあまり効いていないと評価することができる。\*8

であるとすると M3 の gm が主要因に違いない。この値は OP 解析の時点で求まっているので、simulator によっては提示する機能を持っている。LTspice にもあるかも知れないが見つけていない。代わりにどんな回路 simulator でも使えるアイデアを、図 6 に示す。動作点を合わせるため、レプリカトランジスタを用いるという手法である。その M4 が、SF トランジスタ M3 と同種 ( $N_50n$ ) で同じ W/L を持ち、動作点も合わせたトランジスタである。

M4 の 4 つのドレイン、ゲート、バックゲートは、それぞれ vdd, sfin, GND につなげば M3 と同じになる。問題はソースで、これを SFOUT ノードに繋いだのでは、M3 の動作点が大幅にずれてしまう。そこで、VCVS 素子 E1 を使って E1 を使って E2 のドレイン電位をコピーしているのである。E1 は一方向にのみ電圧を伝えるので、E2 動作点の変化は E3 動作点に影響しない。

図 6 SF トランジスタのレプリカを追加した LTspice スケマ

しかし端子電位を単にコピーするだけなら gm 測定に必要な変動を与えることができないので、V3 と V4 を追加している。それぞれゲートの gm とバックゲートのgmb を測るための電源である。V3 の反対側は電源ではなく sfin ノードに繋ぐ方が

<sup>\*8</sup> 余談ながら、最近の微細プロセスでは、ドレイン抵抗が出力抵抗の支配項のひとつになっている。これに対処するため、常用される回路自体が変わってくるかも知れないと感じている。

合理的かも知れない。ここでは M4 のゲートをつなぐと sfin が微妙に変化してしまい M3 の動作点自体を変えてしまう危険を危惧した。

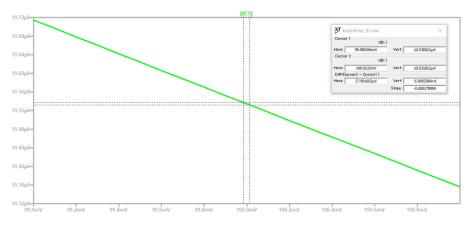

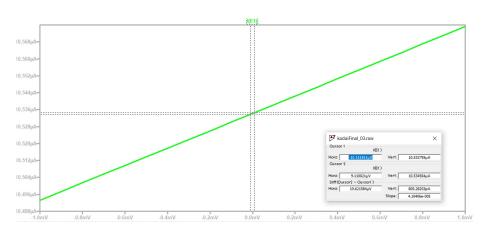

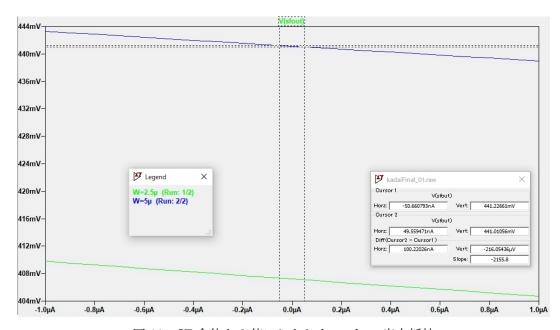

図 7 の傾きから gm=179.0uS、図 8 の傾きから gmb=41uS と見積もられる。4 倍 の差があるので gm が支配的であることは変わりないが、gmb の考慮で結果が 2 割 くらい変わってくるので、無視してよい要因ではない。ドレイン抵抗に関しては、両 者の和の gm が見えてくるので、220uS = 4545  $\Omega$ となる。これだけで、SFOUT 抵抗の大部分を占めていることが分かる。これを 80k  $\Omega$ と並列させると 4.3k  $\Omega$ となり、ぴったり一致する。R1 の影響は無視して良さげである。

図7 M4のgm (V3スイープ)

図 8 M4の gmb (V4 スイープ)

SF の出力抵抗を求める式は、CMOS 回路のほとんどの教科書に載っていると思うので、今回の結果をそれと比べてみると理解が深まると思う。

今回の近似を等価回路で書くと、図 9 のようになる。M3 のゲート電位は固定なので、ソースから見た gm は 1/gm の抵抗に見える。そこで等価回路はよく見る電

流源ではなく、抵抗の symbol を用いている。同様にバックゲート電位も固定なので、ソースから見ると 1/gmb の抵抗に見える。ゲートを駆動している抵抗 R1 は図に表れて来ない。電流源は考えなくてもよいのだが、sfout の DC レベルを合わせるために書き入れた。実際の値がどうであるかは、出力抵抗を考えるときにはどうでもよい。

M2 と M3 の ro は、今回は手抜きで同じ値としたが、厳密には違う値である。M3 の ro は、図 6 のレプリカトランジスタ M4 のドレインに電圧源を加えて、0V 付近でスイープすることでシミュレーションできる。

図9 sfout の線形等価回路

#### 4.3 設問3の説明

与えられた負荷を駆動するために必要な駆動能力をどうやって実現するか、という 設計の現場で日々遭遇する問題から持ってきた。この設問で与えられた条件だけで は正解はなく、一般論から方策を探って行くしかない。これも、日々設計者が置かれ ている状況である。

SF の入力側、sfin を駆動する抵抗が 10k  $\Omega$ で、SFOUT の抵抗が 4.3k  $\Omega$ では、SFを使っても駆動能力が 2 倍程度にしかならない。これはかなりがっかりする結果である。そのくらいなら、SF に流す 10uA を SF 駆動段に使って、抵抗を半減して 5k  $\Omega$ を 20uA で駆動すれば、同じ消費電流で同じ振幅で、さらに駆動力も同等になる。

SF をつかったおかげで信号レベルが下がってしまい、後段の動作マージンがなくなってしまうのでは元も子もない。

ということで、このような状況では、もっと効率よく出力抵抗を下げたい、という要望が発生する。Razavi 先生の教科書には、CMOS プロセスで SF を出力抵抗を下げる目的で使うのは無意味ではないかという旨の記載がある。直ちに納得するわけではないが、それはそうかも知れないと思わなくもない。

SF の能力が足りないとき、同じことだが SF の能力を増やしたいときの定跡は、動作電流を増やすことである。電流を 2 倍にすれば、gm は  $\sqrt{2}$  になる。設問 2 の結果から、出力抵抗も 0.8 倍くらいにはなりそうである。\*9

図 10 に、M2 の W を 2 倍にした時の IV カーブを示す。出力抵抗は 2546  $\Omega$ となり、元の 4324  $\Omega$ の 0.6 倍になった。予想外の出来である。(と、私もまだ MOS 特性の理解が足らない。)

図 10 SF 電流を 2 倍にしたときの sfout 出力抵抗

電流だけ増やす方法は、出力レベルを下げてしまう欠点がある。sfout 電位は、元の 441mV から 407mV に下がってしまった。無暗に増やしてゆくことはできないだろう。

もうひとつの定跡は、SF 回路全部の幅を増やすことである。これなら出力レベル

<sup>\*9</sup> このように、定性と定量を組み合わせた推論は、設計者の必須技能である。これは自分で訓練して身につけないといけない。教えてくれる所はないし、あったとしても受け身ある限りは、身につかない。

が下がらないので、2 倍といわず、4 倍や 8 倍にも簡単にできる。反比例して出力抵抗が下がってゆく。図 11 には、図 10 と同じ IV 曲線と、W を 2 倍にした IV 曲線を示した。ついでにレベル変化も見ようという意図である。おかげで M2 と M3 の両方の W を 2 倍にした線の傾きが見にくくなっているがカーソルを読むと 2156  $\Omega$  と、期待通り当初の半分になっている。

図 11 SF 全体を 2 倍にしたときの sfout 出力抵抗

これらの方法の欠点は、消費電力が増えることと、駆動段から見た SF の負荷がドンドン重くなってゆくことである。動作点で見ると違いは分かりづらいが、高速信号を入れたときに見えてくる。さまざまな得失のなかから、美しい回路を選んで行くのが設計者である。

トランジスタの W や L を変えるだけで出力抵抗を下げるという試みは、まずうまく行かない。L を小さくできれば良いが、プロセス限界を超えるところまでは出来ない。大抵は最初から限界に近い所で使っている。W を増やせば、その平方根でgm が増えてゆくはずであるが、出力抵抗は期待したほどは減ってゆかない。図 10と図 11を比べてみれば良い。W が増えても Id が増えないと、トランジスタの電流密度が下がりgm を減らす効果が見えて来るからである。(図 10で期待以上の効果が得られたのと裏返しである。)

## 5 最後に言っておきたいこと

今回は回路エンジニアの日常の話をしたのですが、エンジニアの卵たちには存外難解だったようです。SFのような簡単な回路要素でも、今回紹介したように考えていることは沢山あるのです。それでもまだ話し足らないこともあります。たとえば容量性負荷の駆動で考えることなどです。これを扱おうとすると、我々の回路論に時間の概念を組み込む必要があります。その大変さは昨年の講義資料を眺めてもらえれば、察することができるかも知れません。

いつかはその長い道を進む時が来るかも知れませんがその前に、毎日の学習において、改めて欲しいことが幾つかあります。

まずレポートの書き方です。学生である以上、必須の技能です。最低限のフォーマットと内容レベルは満たしてください。当然ながら、読んでもらうことを前提に書きましょう。しかし、とても判読不能なスクリーンショットを貼りつけているだけで、説明も何もないレポートがありました。結果だけを提示されても、判断がつきかねます。不必要に長いレポートは悪ですが、要件が欠けているレポートは存在価値がありません。

ノートの書き方も同様です。1年後の自分は今の自分とは別人と思った方が良いです。記録を残す時は、1年後自分が理解できるか、と問うてみましょう。1年以上前の自分のメモをみて、何を追記しておけば良かったかを考えてみましょう。

今回の私の資料、図の線の太さが揃っていなかったり、記号の向きがフリップしていたりと誤植も目立つのですが、ちゃんとした報告書にするときはこのような点にも気を配りましょう。英語の先生に、"スペルミスがあるレポートを提出すると、あなたの信用が下がりますよ"と注意されたことがあります。

論文の書き方は、良い本がありますし、WEBでも色々公開されています。それら を見つけ出すのも、学生に必須な能力です。研究ください。

レポートの期限が来たので未完成のまま提出するというのは、学生なら許される部分もあるかも知れませんが、エンジニアの仕事の進め方では論外です。実務で期限に間に合わないという状況に陥った時は、直ちに何らかの対策が必要です。もし選んだ対策が失敗した場合は、大きなペナルティが発生します。スケジュールをキープする

ことは最優先事項です。

課題3の回答で多く見られたのですが、案を出しただけで検証していないものがありました。これは、エンジニアリングの基本に反します。直近の課題に対し解決策を考案したり、不可解な現象の機構に仮説を立てたりするのはエンジニアの日常ですが、思いついた仮説がしょっちゅう間違っていることも知っています。そんな状況があるので、間違いを失敗にしてしまわないための知恵と努力が必要になるのです。エンジニアの提出した解答を採点してくれるのは、先生ではなく現実なのです。

学年が進むにつれ、自分で問題を解決する能力が期待されます。どこかで読んだのですが、

学士: 教えられた事が実行できる

修士: 問題の解決方法を自分で見つけられる

博士: どの問題を解くべきかを自分で見つけられる

という基準があるそうです。元になる文書は見つけられませんでしたので、過ちも含まれていると思いますが、それぞれの段階で、何を期待されているかの道標になると思います。学年が上がっていきなり厳しくできるというものではないので、先を見ながら修行して行きましょう。

最後に、色々と至らない講義でしたが、最後までつきあってもらって、どうもありがとう。