## LSIテスト技術の基礎と動向

- LSIテスト技術の基礎

- VTS(VLSI Test Symposium) 2021報告

畠山一実

2021.06.29 Kazumi Hatayama

1

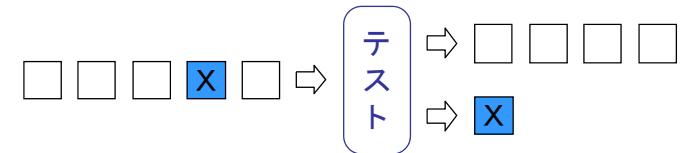

## LSIのテストとは

LSIのテストとは製造されたチップに含まれる不良品を選別する作業

X : 不良品

2021.06.29 Kazumi Hatayama

3

## アウトライン

- ◆はじめに

- ◇LSIテスト技術の基礎

- 論理回路テスト生成手法

- テスト容易化設計

- ◇VTS2021報告

2021.06.29 Kazumi Hatayama

2

## テスト装置: テスタ

高性能SoCテスタ

低価格テスタ

SoC:System-on-a-Chip

2021.06.29 Kazumi Hatayama

4

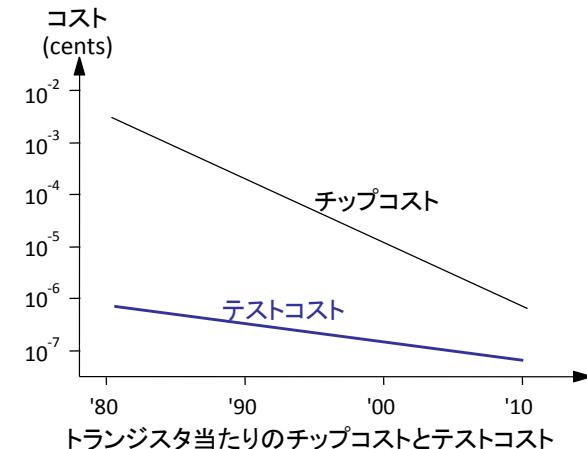

## LSIテストの課題

LSIの高集積化に伴って以下の課題が重大化

- ・テストコスト

- ・テスト品質

2021.06.29 Kazumi Hatayama

5

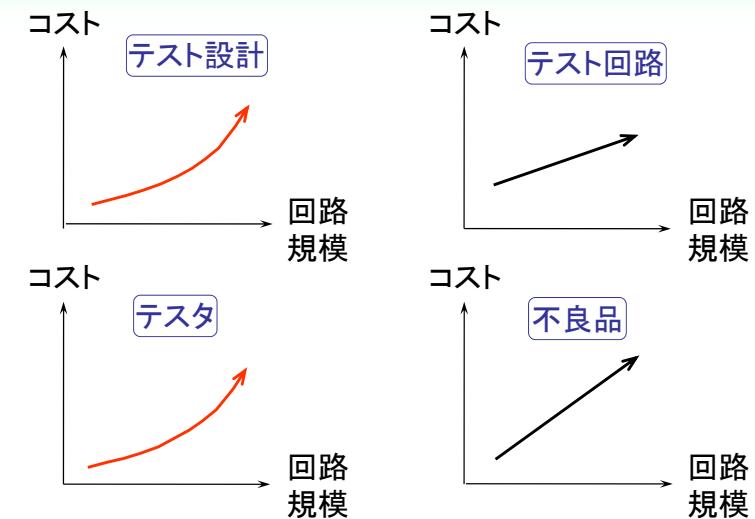

## テストコストとその要因

全体テストコストには様々な要因が係わり

何が重要かは場合によって異なる

- ・**テスト設計コスト**

計算機処理時間, 人手作業工数, ツール費用

- ・**テスト回路のコスト**

エリアオーバヘッド, 配線オーバヘッド

- ・**テスタコスト**

テスタ使用時間, テスタ性能向上

- ・**不良品のペナルティ**

補償, 信用失墜, 不良解析工数

2021.06.29 Kazumi Hatayama

7

## テスト・クライシス

LSIの大規模・高集積化とともにテストコストが爆発

2021.06.29 Kazumi Hatayama

6

## テストコストと回路規模の関係

2021.06.29 Kazumi Hatayama

8

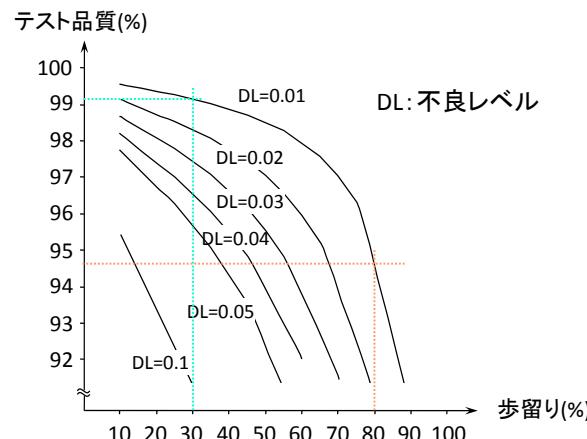

## テスト品質の重要性

テスト品質は製品の不良レベルに直接かかわる

$$DL = 1 - Y^{(1-T)}$$

DL: 不良レベル

良品と判定されたLSI中の不良品の割合

Y: 歩留り

製造LSI中の良品の割合

T: テスト品質

不良品を選別できる確率

2021.06.29 Kazumi Hatayama

9

## アウトライン

◇はじめに

◆LSIテスト技術の基礎

－論理回路テスト生成手法

－テスト容易化設計

◇VTS2021報告

2021.06.29 Kazumi Hatayama

11

## テスト品質と不良レベルの関係

歩留りが下がると高いテスト品質が必要になる

2021.06.29 Kazumi Hatayama

10

## 論理回路テスト生成手法

1. 論理回路のテストとは

2. 故障モデルとテスト方法

3. テスト生成基本アルゴリズム

2021.06.29 Kazumi Hatayama

12

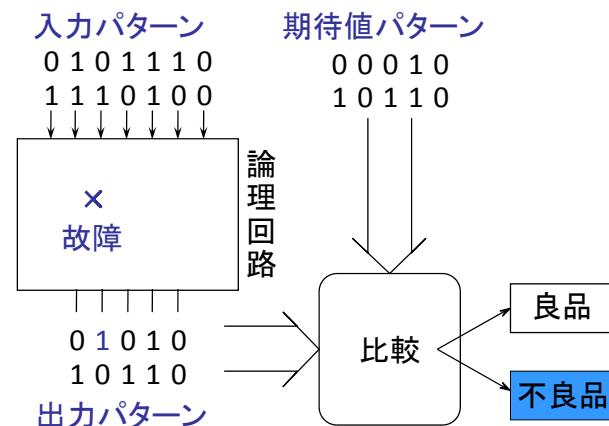

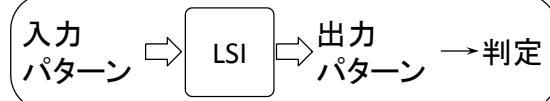

## 論理回路のテストの仕組み

出力パターンと期待値パターンを比較して良否を判定

2021.06.29 Kazumi Hatayama

13

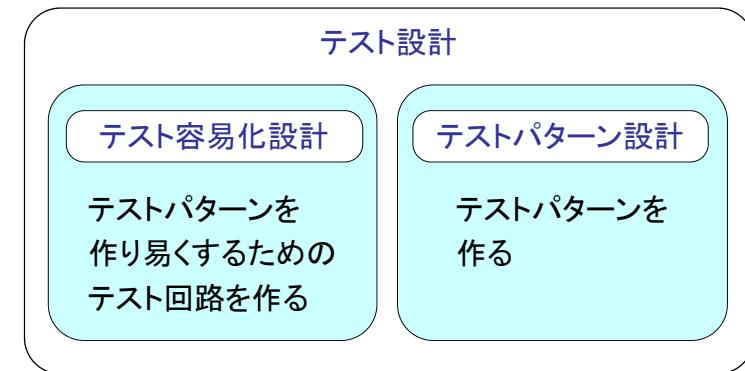

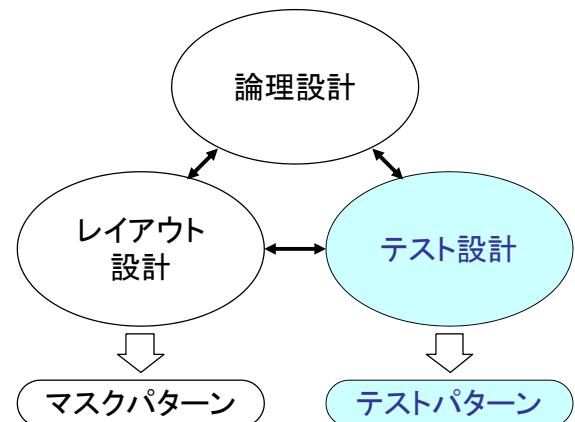

## 広い意味でのテスト設計

テスト設計は広義には2つの内容を含む

2021.06.29 Kazumi Hatayama

15

## テスト設計の位置づけ

テスト設計とはテストのための入力パターンの設計

2021.06.29 Kazumi Hatayama

14

## テスト品質の良し悪し

テスト品質の良し悪しはテストパターンの良し悪しによる

| テストパターンの良し悪し | テストの結果      |

|--------------|-------------|

| 良くない         | <p>TEST</p> |

| 良い           | <p>TEST</p> |

2021.06.29 Kazumi Hatayama

16

# 良いテストパターンを作るには

良いテストパターンを作るには様々な工夫が必要

## ・テスト生成手法の改良

- ・故障検出能力の向上

- ・故障モデルの拡張

- ・テストパターン数の削減

## ・テスト容易化設計の活用

- ・テスト生成時間の短縮

- ・テスト実行時間の短縮

- ・テストパターン品質の向上

2021.06.29 Kazumi Hatayama

17

# 論理回路テスト生成手法

1. 論理回路のテストとは

2. 故障モデルとテスト方法

3. テスト生成基本アルゴリズム

2021.06.29 Kazumi Hatayama

18

# 故障モデルの分類

テスト設計を考える際には**故障のモデル化**が必要

## ◎故障のタイプによる分類

- ・縮退故障(stuck-at) : 信号線が一定レベルに固定

- ・短絡故障(short/bridge) : 信号線が他の信号線と短絡

- ・開放故障(open) : 信号線が断線

- ・遅延故障(delay) : 信号伝播遅延が増大

[遷移故障(transition) : 遅延が大幅に増大]

- ・その他の故障:トランジスタ故障, メモリ故障, 機能故障, . . .

## ◎故障の数による分類

单一故障(single), 多重故障(multiple)

## ◎故障の状態による分類

永久故障(permanent), 間欠故障(intermittent), 過渡故障(transient)

2021.06.29 Kazumi Hatayama

19

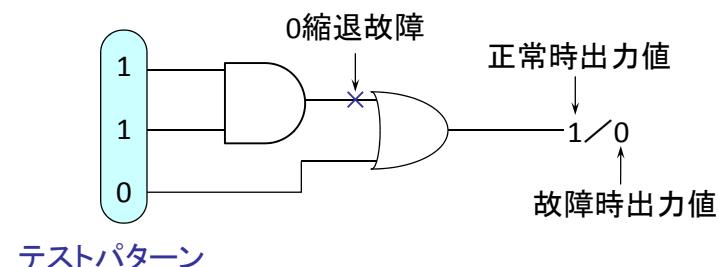

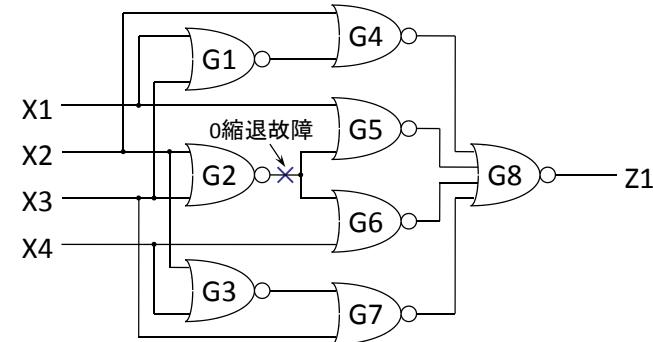

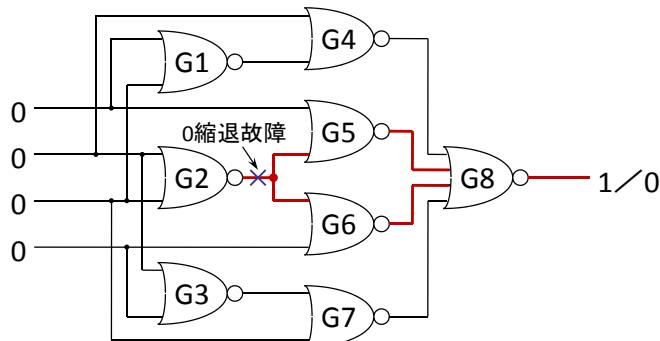

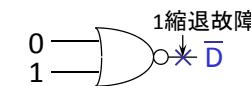

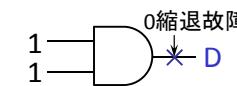

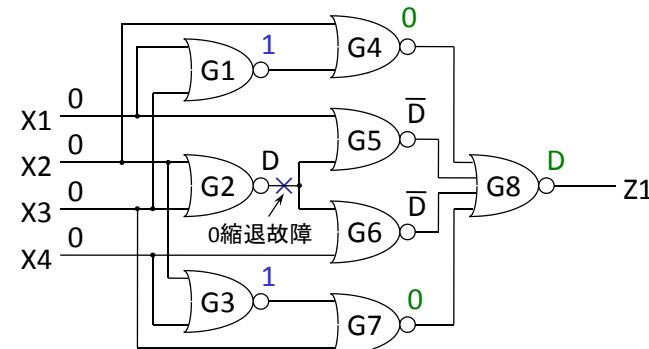

# 縮退故障のテスト方法

縮退故障は**スタティックなパターン**でテスト可能

2021.06.29 Kazumi Hatayama

19

2021.06.29 Kazumi Hatayama

20

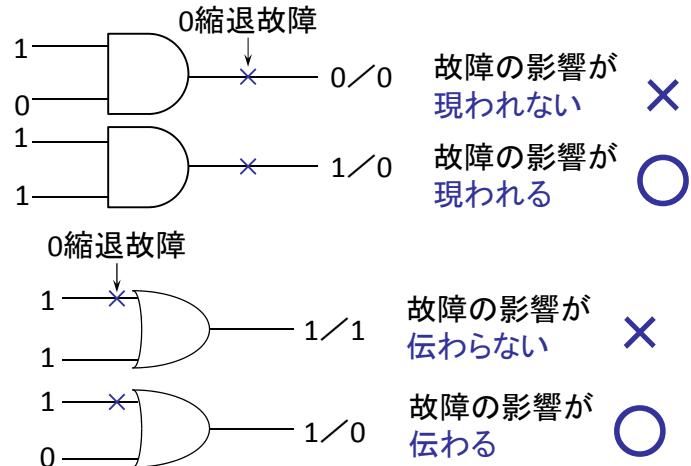

## 故障の顕現化と伝播

テストするためには故障の影響の顕現化と伝播が必要

2021.06.29 Kazumi Hatayama

21

## 単一縮退故障の仮定

以下では単一縮退故障を主体として話を進める

- ・単一縮退故障が最も取り扱いやすい

テストパターン作成方法が最もわかりやすい

- ・他の故障の多くは単一縮退故障のテストパターンで検出できる

○多重縮退故障についてはほとんどをカバー

○短絡故障についても大部分は検出可能

★ただし、最近ではカバーできない故障が重要になりつつある(遅延故障、開放故障等)

2021.06.29 Kazumi Hatayama

23

## 縮退故障のテストの例

故障を顕現化させてそれを伝播する

2021.06.29 Kazumi Hatayama

22

## 故障検出率

テストパターン品質の尺度として故障検出率を用いる

### 故障検出率の定義

あるテストパターンTPに対してTPの故障検出率FCを次式で定義する

$$FC = N_{df} / N_{af}$$

ここで、

$N_{af}$ : モデル化された故障の総数

$N_{df}$ : モデル化された故障のうち、

TPで検出される故障の総数

2021.06.29 Kazumi Hatayama

24

# 論理回路テスト生成手法

1. 論理回路のテストとは

2. 故障モデルとテスト方法

3. テスト生成基本アルゴリズム

2021.06.29 Kazumi Hatayama

25

## 主なテスト生成アルゴリズム

### 組合せ回路用アルゴリズム

- ・一次元経路活性化法

- ・Dアルゴリズム

- ・PODEM法

- ・FANアルゴリズム

- ⋮

### 順序回路用アルゴリズム

- ・拡張Dアルゴリズム

- ⋮

2021.06.29 Kazumi Hatayama

26

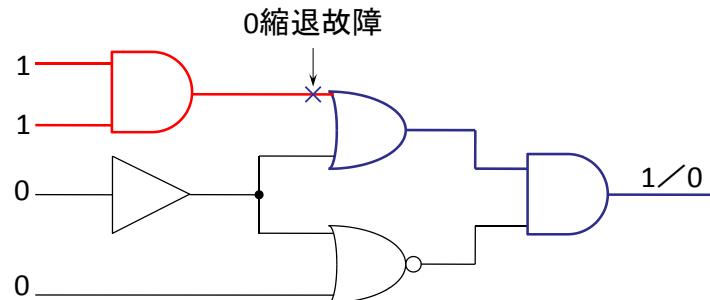

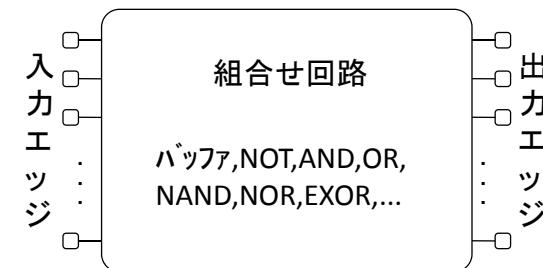

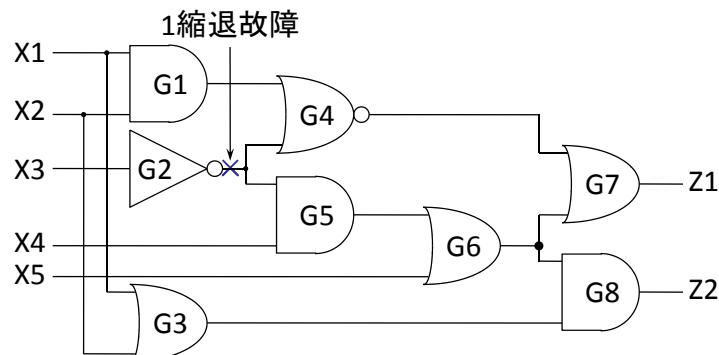

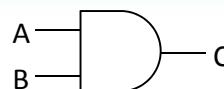

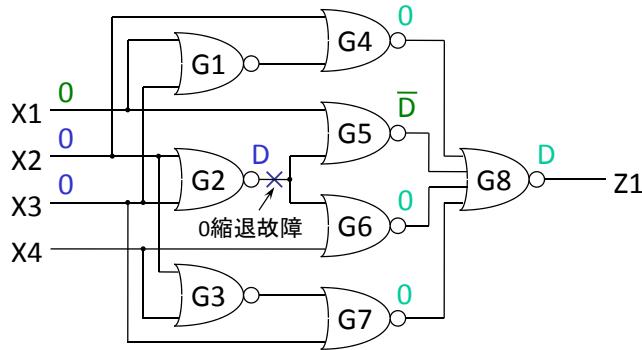

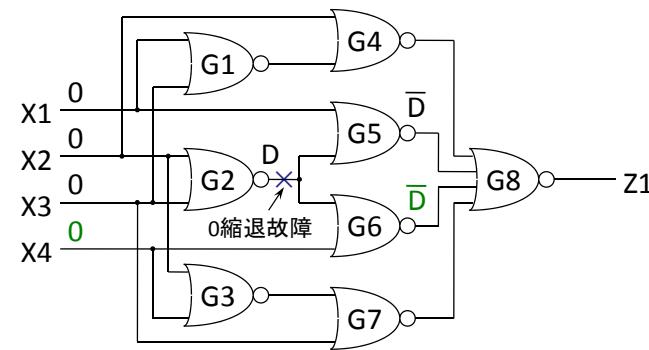

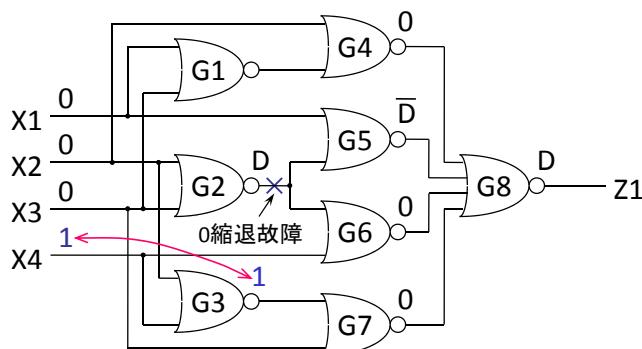

# 組合せ回路用アルゴリズム

組合せ回路モデルに対してテストパターンを生成

ある信号線に0(または1)縮退故障を仮定し,

これを検出するための入力パターンを求める

2021.06.29 Kazumi Hatayama

27

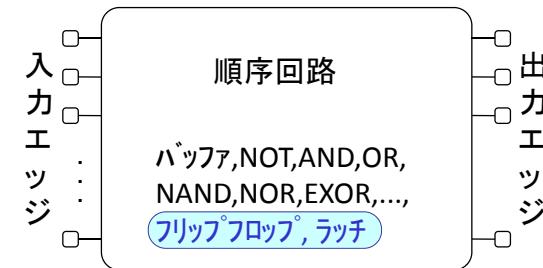

## 順序回路用アルゴリズム

順序回路モデルに対してテストパターンを生成

ある信号線に0(または1)縮退故障を仮定し,

これを検出するための入力パターン系列を求める

2021.06.29 Kazumi Hatayama

28

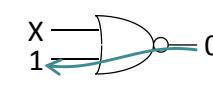

# 一次元経路活性化法

故障伝播経路を決めてその経路を活性化

1. 故障点に故障の影響が現われる条件を求める

(故障顕現化条件)

2. 故障の影響を出力点まで伝播する経路を決める

(故障伝播経路)

3. 故障伝播経路を活性化する条件を求める

(経路活性化条件)

4. 以上の条件を満たす入力パターンを求める

2021.06.29 Kazumi Hatayama

29

# 一次元経路活性化法: 欠点

一次元の経路では故障伝播できない場合がある

(例: シュナイダーの回路)

→故障伝播経路の再収れんが必要

2021.06.29 Kazumi Hatayama

31

# 一次元経路活性化法: 生成例

・顕現化条件 :  $G2=0$

・伝播経路 :  $G2-G5-G6-G8$        $\Rightarrow$

・活性化条件 :  $X4=1, X5=0, G3=1$

$X1=1, X2=0,$

$X3=1, X4=1,$

$X5=0$

2021.06.29 Kazumi Hatayama

30

# シュナイダーの回路のテスト

故障伝播経路の再収れんが必要

2021.06.29 Kazumi Hatayama

32

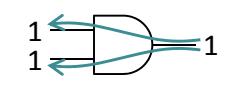

## Dアルゴリズム(D-alg.)

キューブ演算によりテストパターンを求める

### 1. 故障挿入: 故障点に故障論理値D(または $\bar{D}$ )を与える

D…正常時1, 故障時0

$\bar{D}$ …正常時0, 故障時1

基本Dキューブを用いる

### 2. 前方操作: 故障論理値を前方(出力側)に伝播する

伝播Dキューブを用いる

### 3. 後方操作: 論理素子の出力値から入力値を決める

基本キューブ(Cキューブ)を用いる

2021.06.29 Kazumi Hatayama

33

## D-alg.で用いるキューブの例

| A | B | C |

|---|---|---|

| 0 | X | 0 |

| X | 0 | 0 |

| 1 | 1 | 1 |

| 0 | X | D |

| X | 0 | D |

| 1 | 1 | D |

| 1 | D | D |

| D | 1 | D |

| D | D | D |

基本キューブ

| A | B | C |

|---|---|---|

| 0 | 0 | 1 |

| 1 | X | 0 |

| X | 1 | 0 |

| 0 | 0 | D |

| 1 | X | D |

| X | 1 | D |

| 0 | D | D |

| D | 0 | D |

| D | D | D |

基本Dキューブ

| A | B | C |

|---|---|---|

| 0 | D | D |

| D | 0 | D |

| D | D | D |

| D | D | D |

伝播Dキューブ

2021.06.29 Kazumi Hatayama

34

## キューブの使用方法

### ・故障挿入: 基本Dキューブ

### ・前方操作: 伝播Dキューブ

### ・後方操作: 基本キューブ

決定済 → 1 → 0

決定済 → D → 1

矛盾!

2021.06.29 Kazumi Hatayama

35

## D-alg.: テスト生成例

シュナイダーの回路に対してもテストパターン生成可能

|      | X1 | X2 | X3 | X4 | G1 | G2 | G3        | G4        | G5        | G6        | G7 | G8 |        |

|------|----|----|----|----|----|----|-----------|-----------|-----------|-----------|----|----|--------|

| (1)  | 0  | 0  |    |    |    | D  |           |           |           |           |    |    | [G2]   |

| (2)  | 0  | 0  | 0  |    |    | D  |           |           | $\bar{D}$ |           |    |    | [G5]   |

| (3)  | 0  | 0  | 0  |    | D  | 0  | $\bar{D}$ | 0         | 0         | D         |    |    | [G8]   |

| (4)  | 0  | 0  | 0  | 1  | D  | 0  | $\bar{D}$ | 0         | 0         | D         |    |    | [G6]   |

| (5)  | 0  | 0  | 0  | 1  | D  | 1  | 0         | $\bar{D}$ | 0         | 0         | D  |    | [G7] × |

| (3') | 0  | 0  | 0  | 0  | D  |    | $\bar{D}$ | $\bar{D}$ | D         |           |    |    | [G6]   |

| (4') | 0  | 0  | 0  | 0  | D  | 0  | $\bar{D}$ | $\bar{D}$ | 0         | D         |    |    | [G8]   |

| (5') | 0  | 0  | 0  | 0  | D  | 1  | 0         | $\bar{D}$ | $\bar{D}$ | 0         | D  |    | [G7]   |

| (6') | 0  | 0  | 0  | 0  | 1  | D  | 1         | 0         | $\bar{D}$ | $\bar{D}$ | 0  | D  | [G4] ○ |

2021.06.29 Kazumi Hatayama

36

## D-alg.: テスト生成例(つづき1)

ステップ(1)～(3): 故障挿入 & 前方操作

2021.06.29 Kazumi Hatayama

37

## D-alg.: テスト生成例(つづき3)

ステップ(3'): 前方操作(対象変更: G8→G6)

2021.06.29 Kazumi Hatayama

39

## D-alg.: テスト生成例(つづき2)

ステップ(4)～(5): 後方操作→矛盾

2021.06.29 Kazumi Hatayama

38

## D-alg.: テスト生成例(つづき4)

ステップ(4')～(6'): 前方/後方操作→生成完了

2021.06.29 Kazumi Hatayama

40

# アウトライン

◇はじめに

## ◆LSIテスト技術の基礎

－論理回路テスト生成手法

－テスト容易化設計

◇VTS2021報告

2021.06.29 Kazumi Hatayama

41

# テスト容易化設計の必要性

大規模かつ高機能なLSIでは方策なしにテスト設計に取り組むことは不可能（テスト生成コストが莫大）

テスト容易化のアプローチ

・問題をより易しい問題に変換する

スキャン設計方式,

階層型テスト容易化方式

・テスト生成をできるだけしないようにする

組込み自己テスト方式,

万能テスト方式

2021.06.29 Kazumi Hatayama

43

# テスト容易化設計

## 1. スキャン設計方式

## 2. 組込み自己テスト方式

2021.06.29 Kazumi Hatayama

42

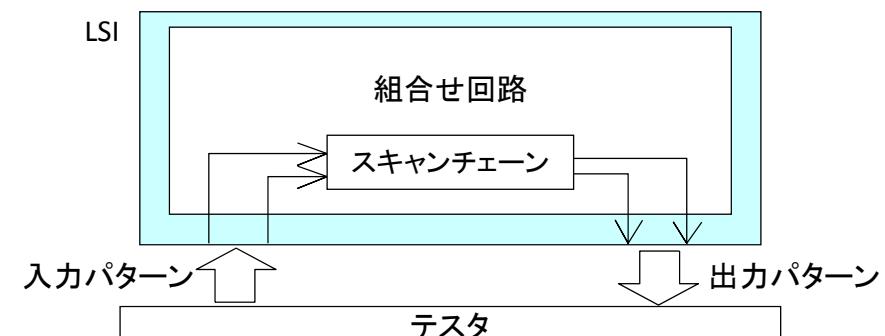

# スキャン設計によるテスト容易化

スキャン設計ではテストからの入力パターンをスキャンチェーン（一般に複数）を通してフリップフロップ(FF)に書込むことにより内部状態を設定し、FFでの出力パターンをスキャンチェーンを通してテストに読出すことにより内部状態を観測する

2021.06.29 Kazumi Hatayama

44

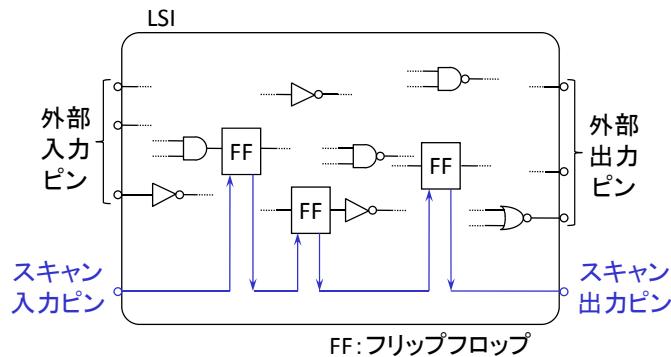

## スキャンチェーンの構成例

FFを外部から直接制御観測できるようになる

2021.06.29 Kazumi Hatayama

45

## スキャン方式の短所

種々のオーバーヘッドが短所

### ゲートオーバーヘッド

方式によって異なるが一般に全体の5~10%程度がスキャンのための回路(フリップフロップ中も含む)

### ディレイペナルティ

方式によって異なるが一般に5~10%程度はディレイが増加

### スキャン専用ピン

方式によって異なるが一般に2~4本程度必要

2021.06.29 Kazumi Hatayama

47

## スキャン方式の利点

順序回路のテスト生成の問題を組合せ回路の

テスト生成問題に簡約化できる

### テストパターン生成の困難さの比較

| 回路種別  | 状態数       | テストパターン作成工数         |                             |

|-------|-----------|---------------------|-----------------------------|

|       |           | 原理                  | アルゴリズム                      |

| 組合せ回路 | $2^P$     | $K_1 \cdot 2^P$     | $K_2 \cdot P^k$             |

| 順序回路  | $2^{P+F}$ | $K_1 \cdot 2^{P+F}$ | $(K_2 \cdot P^k) \cdot 2^F$ |

P:入力ピン数, F:フリップフロップ数

$K_1, K_2$ :比例定数, k:係数(1~2)

2021.06.29 Kazumi Hatayama

46

## スキャン方式の課題

テスト時の動作が通常動作と異なる

### テスト困難な部分がある

- 論理回路からメモリにアクセスする部分のテスト等複数クロックサイクルが必要なケース

### 過剰な電力を消費する

- 通常動作時は回路全体の20%程度しか動作しない場合でも、テスト時には50%以上動作することもある

- 低電力設計された回路でも、低電力機能を利用せず動作させる必要がある

2021.06.29 Kazumi Hatayama

48

# テスト容易化設計

1. スキャン設計方式

2. 組込み自己テスト方式

2021.06.29 Kazumi Hatayama

49

## 組込み自己テスト(BIST)方式

BISTはテストパターン印加を省略するための手段

(BIST : Built-In Self Test)

通常のテスト方法

BIST方式によるテスト方法

2021.06.29 Kazumi Hatayama

50

## テスト対象によるBIST方式の分類

テスト対象ごとにBIST方式も異なる

・ロジックBIST

・主として疑似乱数(ランダム)パターンでテスト

・メモリBIST

・マーチング等のメモリテストパターンを発生

・アナログBIST

・回路ごとに工夫

・一般的手法としてはD/A, A/D変換を利用

2021.06.29 Kazumi Hatayama

51

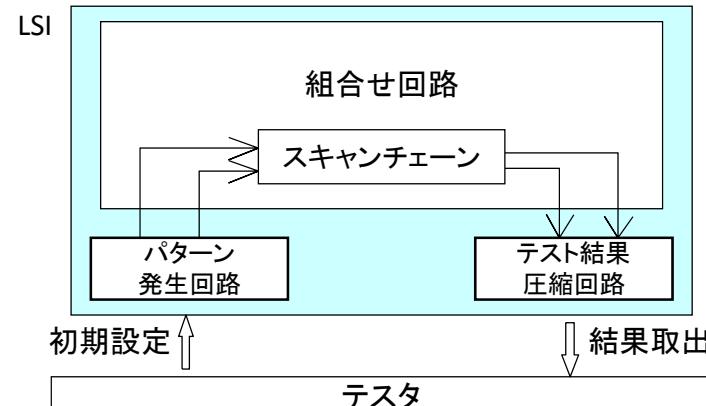

## スキャンベースBIST方式

スキャンベースBIST方式はTPGの出力をスキャンチェーンに接続し

スキャンチェーンを通して内部状態を設定する方式

2021.06.29 Kazumi Hatayama

52

## スキャンベースBISTの利点と欠点

### BISTの利点

- ・テストのテストデータ量がきわめて少ない

- ・スキャンチェーン数が拡大可能

- ・少ピンでテストできる

- ・実動作のスピード(at-speed)でテストできる

- ・実動作時の保守用にも利用できる

### BISTの欠点

- ・ゲートオーバーヘッドが大きい

- ・非常に高い故障検出率を得るのが難しい

- ・故障解析が難しい

- ・設計制約が厳しい(不定値伝播禁止)

2021.06.29 Kazumi Hatayama

53

## データミニスティックBIST

スキャンテストと同等のパターンをBISTで発生することによりテスト品質を向上

- ・ランダムBIST: ランダムパターンを発生(LFSR)

- ・データミニスティックBIST:

- テスト生成で求めたテストパターンをBISTのランダムパターンに埋め込む

- ・Reseeding

- ・ビット反転

- ・近傍パターン群発生

2021.06.29 Kazumi Hatayama

55

## スキャンベースBIST方式の問題点

スキャンベースBISTでは故障検出率が低下

故障検出率の低下 : フルスキャン…99%以上

→スキャンベースBIST…80~95%

### 原因

- ・ランダムテスト不適故障の存在

### 対策

- ・重み付き乱数の利用 : 複数重みを切り替えて使用

- ・検査点の挿入…ランダムテスト容易性向上

- ・特定パターンの発生 : データミニスティックBIST

2021.06.29 Kazumi Hatayama

54

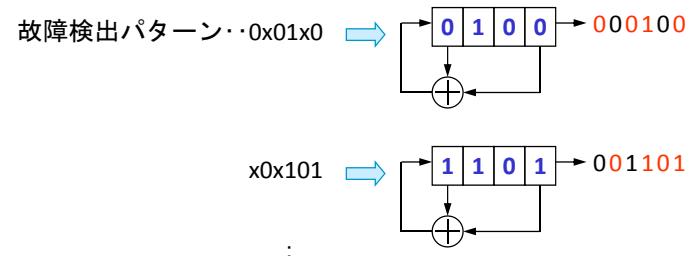

## reseeding

- ・テスト生成で求めた故障検出パターンをLFSRから出力するための種パターン(seed)を求める

種パターンを替えながら乱数パターンを発生

2021.06.29 Kazumi Hatayama

56

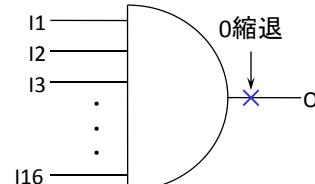

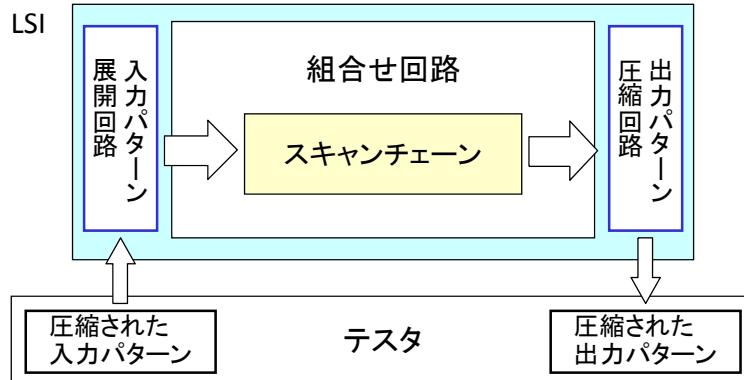

## 圧縮パターンテスト方式

- ・テスト入力パターンを圧縮してテスタから印加し、内部で展開してスキャンテストを実行。

テスト結果を内部で圧縮してテスタに取り出す。

2021.06.29 Kazumi Hatayama

57

## アウトライン

- ◇はじめに

- ◇LSIテスト技術の基礎

- －論理回路テスト生成手法

- －テスト容易化設計

- ◆VTS2021報告

2021.06.29 Kazumi Hatayama

59

## 圧縮パターンテスト方式の利点と課題

- ・圧縮パターンテスト方式の利点

- ・スキャン方式に比べてテストデータ量が大幅に減少

- ・スキャンチェーン数が拡大可能

- ・設計制約はスキャン方式と同等

- ロジックBISTより不定値伝播の問題が小さい

- ・圧縮パターンテスト方式の課題

- ・効率的な入力/出力パターンの圧縮

- ・不定値の影響を受けない出力パターンの圧縮

- ・at-speedでのテスト

2021.06.29 Kazumi Hatayama

58

## VTS2021報告

- ・VTSについて

- ・VTS2021の概要

- ・論文発表の全体動向

- ・注目セッションの紹介

- ・まとめ

2021.06.29 Kazumi Hatayama

60

# VTS (VLSI Test Symposium)

## ・VTSの沿革および概要

- ・1983年にVLSI Test Workshopとしてスタート

- ・1991年からはSymposium

- ・LSIテスト分野ではITC (International Test Conference) に次ぐ

主要な国際会議

- ・ITCが企業主体であるのに対して、VTSはどちらかといえば

アカデミック

- ・2002年から企業事例のためのIP(Innovative Practice) Track

を設置し、企業からの参加者拡大に取組み中

2021.06.29 Kazumi Hatayama

61

## VTS開催一覧

|      | Year | Date        | Location      |

|------|------|-------------|---------------|

| 1st  | 1983 | 03/30-03/31 | Atlantic City |

| 2nd  | 1984 | 03/21-03/22 | Atlantic City |

| 3rd  | 1985 | 04/01-04/02 | Atlantic City |

| 4th  | 1986 | 03/18-03/19 | Atlantic City |

| 5th  | 1987 | 03/24-03/25 | Atlantic City |

| 6th  | 1988 | 03/22-03/23 | Atlantic City |

| 7th  | 1989 | 04/11-04/13 | Atlantic City |

| 8th  | 1990 | 04/10-04/11 | Atlantic City |

| 9th  | 1991 | 04/16-04/18 | Atlantic City |

| 10th | 1992 | 04/07-04/09 | Atlantic City |

| 11th | 1993 | 04/06-04/08 | Atlantic City |

| 12th | 1994 | 04/25-04/28 | Cherry Hill   |

| 13th | 1995 | 04/30-05/03 | Princeton     |

| 14th | 1996 | 04/28-05/01 | Princeton     |

| 15th | 1997 | 04/27-04/30 | Monterey      |

| 16th | 1998 | 04/26-04/30 | Monterey      |

| 17th | 1999 | 04/25-04/29 | Dana Point    |

| 18th | 2000 | 04/30-05/04 | Montreal      |

| 19th | 2001 | 04/29-05/03 | Los Angeles   |

| 20th | 2002 | 04/28-05/02 | Monterey      |

| 21st | 2003 | 04/27-05/01 | Napa          |

|      | Year | Date         | Location      |

|------|------|--------------|---------------|

| 22nd | 2004 | 04/25-04/29  | Napa          |

| 23rd | 2005 | 05/01-05/05  | Palm Springs  |

| 24th | 2006 | 04/30-05/04  | Berkeley      |

| 25th | 2007 | 05/06-05/10  | Berkeley      |

| 26th | 2008 | 04/27-05/01  | San Diego     |

| 27th | 2009 | 05/03-05/07  | Santa Cruz    |

| 28th | 2010 | 04/19-04/22  | Santa Cruz    |

| 29th | 2011 | 05/01-05/04  | Dana Point    |

| 30th | 2012 | 04/23-04/26  | Maui          |

| 31st | 2013 | 04/29-05/01  | Berkeley      |

| 32nd | 2014 | 04/14-04/16  | Napa          |

| 33rd | 2015 | 04/27-04/29  | Napa          |

| 34th | 2016 | 04/24-04/27  | Las Vegas     |

| 35th | 2017 | 04/09-04/12  | Las Vegas     |

| 36th | 2018 | 04/22-04/26  | San Francisco |

| 37th | 2019 | 04/23-04/25  | Monterey      |

| 38th | 2020 | 04/27-10 Mo. | Virtual       |

| 39th | 2021 | 04/25-04/28  | Virtual       |

2003-2006: プログラム委員、2007-2018: 実行委員

2007-2010: IP Track 2011-2014: Special Sessions

2015-2016: Publicity (Vice Chair) 2017-2018: Asian Initiative

2021.06.29 Kazumi Hatayama

62

# アウトライン

- ・ VTSについて

- ・ [VTS2021の概要](#)

- ・ 論文発表の全体動向

- ・ 注目セッションの紹介

- ・ まとめ

2021.06.29 Kazumi Hatayama

63

## VTS2021概要

- ・開催日 : 2021年4月26日(月)～28(水)

- ・開催場所 : Virtual (Zoom Online)

- ・参加者 : 約230名 (日本からは13名以上)

- ・基調講演 : 2件

- ・論文発表 : 9セッション27件・投稿論文80件(採択率=34%)

- ・企業発表 : 4セッション11件+パネル1件

- ・チュートリアル : なし

- ・特別セッション : 8件

- ・その他 : 学位論文コンテスト(予選)

2021.06.29 Kazumi Hatayama

64

# VTS2021 At-a-Glance

| Plenary Session |                                                                                                                                          |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------|

| Keynote 1       | S. Leef (DARPA): Algorithm to Architecture to RTL to GDSII: Incorporating Security into All Phases of SoC Design and Implementation Flow |

| Keynote 2       | K. Arabi (Altazo): Edge Computing Trends, Design and Test Challenges                                                                     |

| Regular Paper Sessions |                                                             |

|------------------------|-------------------------------------------------------------|

| RP1                    | Security Meets Testing                                      |

| RP2                    | Reliability Testing                                         |

| RP3                    | Analog and Mixed Signal Testing                             |

| RP4                    | Architecture and Software Reliability and Test              |

| RP5                    | Diagnosis and Root Cause Analysis                           |

| RP6                    | Emerging Technologies Test and Reliability                  |

| RP7                    | New Directions in Diagnosis, Calibration and Fault Modeling |

| RP8                    | System and Timing Fault Testing                             |

| RP9                    | Industrial Practices                                        |

2021.06.29 Kazumi Hatayama

65

## VTS2020 At-a-Glance (cont.)

| Special Sessions |                                                                                                                                    |

|------------------|------------------------------------------------------------------------------------------------------------------------------------|

| SS1              | Machine Learning for Semiconductor Test and Reliability                                                                            |

| SS2              | Test for AI Chips: from DFT to On-line Testing                                                                                     |

| SS3              | Physical Attacks through Chip Backside: Threats, Challenges, and Opportunities                                                     |

| SS4              | Machine Learning in Test: A Survey of Analog, Digital, Memory, and RF Integrated Circuits                                          |

| SS5              | Reliability Analysis for AI/ML Hardware                                                                                            |

| SS6              | CAD for Hardware Security - Automation is Key to Adoption of Solutions                                                             |

| SS7              | Operating Systems under Test: An Overview of the Significance of the Operating System in the Resiliency of the Computing Continuum |

| SS8              | Noisy Intermediate-Scale Quantum (NISQ) Computers: How They Work, How They Fail, How to Test Them?                                 |

| Innovative Practice Sessions |                                                                                                                                       |

|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| IP1                          | Enabling In-System Test for Automotive SoCs: Online Self-Check and Field Test Requirements and Considerations for Safety-Critical ICs |

| IP2                          | Changing the Economics and Implementation of Scan Testing                                                                             |

| IP3                          | Emerging Challenges in Chiplet Testing                                                                                                |

| IP4                          | Design, Test and EDA Challenges in Achieving Automotive Quality on Nanoscale Designs                                                  |

| IP5                          | Panel: Temperature Testing for Automotive: Optional or a Necessity?                                                                   |

| Students Activities |                                                      |

|---------------------|------------------------------------------------------|

| DT1-DT3             | TTTC's E. J. McCluskey Doctoral Thesis Presentations |

2021.06.29 Kazumi Hatayama

66

## 基調講演1

- S. Leef (DARPA): SoCの設計・実装フロー全般へのセキュリティの実装の連携

—アルゴリズム→アーキテクチャ→RTL→GDSII

- DARPAでのセキュリティ対応設計・実装メソドロジ: 3つのプログラム

- ・動作設計(SHINE), 機能設計(AISS), 実装設計(SPIRAL)

- セキュリティ考慮高位合成: 脆弱性レポートを出力

- ・脆弱性DB: 対象資産, 脆弱性&分類, 脅威の種類, 潜在シナリオ, 検証方法

- セキュアSoC自動実装: セキュリティと経済性を最適化

- ・重点領域: サードパーティ攻撃, リバースエンジニアリング, サプライチェーン, 悪意のあるHW

- ・システム合成&最適化: 電力とセキュリティの迅速な推定が重要

- ・セキュアなレイアウトの実現: セキュリティの必要な資産の特定と保護

- ・課題: 確実な特定, PPA(性能, 電力, 面積)への影響の最小化

- ・戦略: レイアウト脆弱性DB, 脆弱性検出&対策手法, セキュリティ定量化, ...

- ・参照モデル: 検出(アクセス性評価), 対策(アクセス性低減), 最適化(影響最小化)

- 結論

- ・セキュリティの考慮はチップの設計&実装のプロセス全般を通して取り組むべき

2021.06.29 Kazumi Hatayama

67

## 基調講演2

- K. Arabi (Altazo): エッジコンピューティング・トレンド, 設計とテストの課題

- HWの時代が再び到来: HWアクセラレータ(GPU, NPU, ...)→量子コンピュータ

- コンピュータの経済学

- ・データ(新たな油)→計算パワー(生産性)→ブロードバンド(インフラ)→通貨

- コンピュータアーキテクチャ: 初期はチューリングマシン, ノイマン, ハーバード

- 命令セットの進化: CISC→RISC→VLIW→ML/AI(命令なし)

- 構成の進化: マルチコア→GPU&DSP→専用アクセラレータ

- 計算の進化: メインフレーム→PC→クラウド(BB)→モバイル(3G)→エッジ(4G/5G)

- ・5G: エッジコンピューティングを中心としたコネクティビティ・信頼性が1つのキー

- エッジコンピューティング: 実時間データで動作(クラウドはビッグデータで動作)

- 牽引役: 低電力, プライバシー, レイテンシ, データの過負荷

- 分野: モバイル, 5G NW, 自動運転, スマートシティー, インダストリ4.0, 極限エッジ

- ・極限エッジ: 何兆個もの計算要素が小さな電池駆動デバイスに

- ・クラス最高の電力性能比: LSTM, GRNN, DNN, DS-CNNなどにも対応

- エッジコンピューティングのテスト

- ・テストはエッジコンピューティングのキーの1つ: 重要な観点は分野ごとに相違

- ・強靭性, 極端な温度, ゼロ欠陥(自動運転), システムでのテスト(5G NW, 自動運転)

2021.06.29 Kazumi Hatayama

68

# アウトライン

- VTSについて

- VTS2021の概要

- 論文発表の全体動向

- 注目セッションの紹介

- まとめ

2021.06.29 Kazumi Hatayama

69

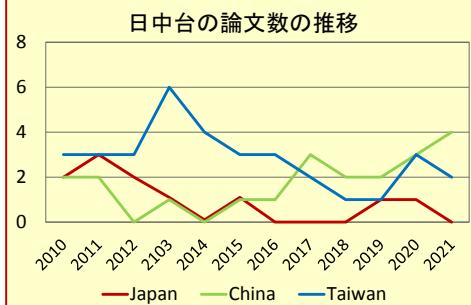

## 論文発表数:国別

- 採択論文数: 27件 (採択率は不明)

- 日本からは0件(3年ぶり)

- 国別採択論文数は右図のとおり

- 米国が半数未満に減少 (2010年以降では初めて)

- アジア(中国)と欧州(ドイツ)が健闘

2021.06.29 Kazumi Hatayama

70

## 論文発表数:分野別

- 前回(VTS2020)及び前々回(VTS2019)との比較

| トピック別論文数       | 採択率      | VTS2021     | VTS2020     | VTS2019      |

|----------------|----------|-------------|-------------|--------------|

|                |          | 34% (27/80) | 34% (31/91) | 33% (35/107) |

| ディレイ/性能テスト     | 1 / 0.3  | 2 / 0.7     | 2 / 0.7     | 0.7          |

| 電力考慮テスト        | 0 / 0.0  | 0 / 0.0     | 1 / 0.3     | 0.3          |

| ATPG/DFT       | 0 / 0.0  | 4 / 1.3     | 5 / 1.8     | 1.8          |

| メモリテスト         | 2 / 0.7  | 1 / 0.3     | 1 / 0.3     | 0.3          |

| アナログ/MSテスト     | 4 / 1.3  | 2 / 0.7     | 1 / 0.3     | 0.3          |

| 高速I/O/RFテスト    | 0 / 0.0  | 0 / 0.0     | 2 / 0.7     | 0.7          |

| 3D-ICテスト       | 1 / 0.3  | 1 / 0.3     | 3 / 1.0     | 1.0          |

| その他のデバイステスト    | 2 / 0.7  | 2 / 0.7     | 3 / 1.0     | 1.0          |

| デバッグ/故障診断/歩留改善 | 4 / 1.3  | 5 / 1.7     | 6 / 2.0     | 2.0          |

| システム高信頼化/劣化対応  | 7 / 2.3  | 7 / 2.0     | 4 / 1.5     | 1.5          |

| セキュリティ         | 3 / 1.0  | 9 / 3.0     | 9 / 3.0     | 3.0          |

| その他            | 3 / 1.0  | 1 / 0.3     | 1 / 0.3     | 0.3          |

| 合計             | 27 / 9.0 | 34 / 11.0   | 38 / 13.0   |              |

VTS2019/VTS2020の分野別にはCTCからの優秀論文を各3件を含む

2021.06.29 Kazumi Hatayama

71

## 分野別の状況

- 分野別の状況

- 全体構成: やや変動あり

- ATPG/DFT関連: 大幅に減少

- AMS/RF関連: やや復調

- メモリテスト: 依然として低迷

- 3D-ICテスト: 変動中

- セキュリティ関連: 大幅に減少

- AI応用関連: 引き続き **堅調**

- 高信頼化関連: こちらも引き続き **堅調**

- その他は検証関連

|            | VTS 2021 | VTS 2020 | VTS 2019 | VTS 2018 |

|------------|----------|----------|----------|----------|

| USA        | 11       | 16       | 29       | 19       |

| Japan      | 0        | 1        | 1        | 0        |

| China      | 4        | 3        | 2        | 2        |

| Taiwan     | 2        | 3        | 1        | 1        |

| India      | 2        | 0        | 0        | 0        |

| Other Asia | 0        | 2        | 0        | 0        |

| France     | 0        | 0        | 1        | 1        |

| Germany    | 4        | 3        | 0        | 2        |

| Netherland | 1        | 0        | 1        | 0        |

| Belgium    | 0        | 1        | 0        | 0        |

| Greece     | 0        | 0        | 0        | 0        |

| Austria    | 0        | 0        | 0        | 2        |

| Italy      | 2        | 2        | 0        | 1        |

| Poland     | 0        | 0        | 0        | 0        |

| Canada     | 1        | 0        | 0        | 2        |

| Total      | 27       | 31       | 35       | 30       |

2021.06.29 Kazumi Hatayama

72

# アウトライン

- VTSについて

- VTS2021の概要

- 論文発表の全体動向

- 注目セッションの紹介

- まとめ

2021.06.29 Kazumi Hatayama

73

## ATPG/DFT関連

- RP8: System and Timing Fault Testing

- IP2: Changing the Economics and Implementation of Scan Testing

- SS2: Test for AI Chips: from DFT to On-line Testing

- ATPG/DFT関連では一般1件、企業セッション3件、特別セッション2件の講演あり

- RP8.3, IP2.2及びSS2.1について紹介

| 講演No. | タイトル                                                                                       | 著者                                                                                           | 所属               |

|-------|--------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|------------------|

| RP8.3 | Two Pattern Timing Tests Capturing Defect-Induced Multi-Gate Delay Impact of Shorts        | S. Pandey, Z. Liao, S. Nandi, A. Sinha, Georgia Tech., S. Natarajan, A. Singh, A. Chatterjee | Intel, Auburn U. |

| IP2.1 | The Packetized Future: The Transition from Pin-Muxed to Bus-based Scan Data Distribution   | G. Eide, J.F. Cote                                                                           | Siemens EDA      |

| IP2.2 | Solving Test Challenges in Adopting High Protocol Scan for Production                      | J. Aki, D. Dohmann                                                                           | Teradyne         |

| IP2.3 | Catching up with the SerDes – How Test is Moving from GPIO to High Speed Serial Interfaces | A. Nagarandal, R. Fish                                                                       | Synopsys         |

| SS2.1 | Test AI Chips with Many Cores                                                              | Y. Huang                                                                                     | HiSilicon        |

| SS2.3 | ATPG Methodology for Industrial AI SOC Chips                                               | G. Guo                                                                                       | Enflame          |

2021.06.29 Kazumi Hatayama

74

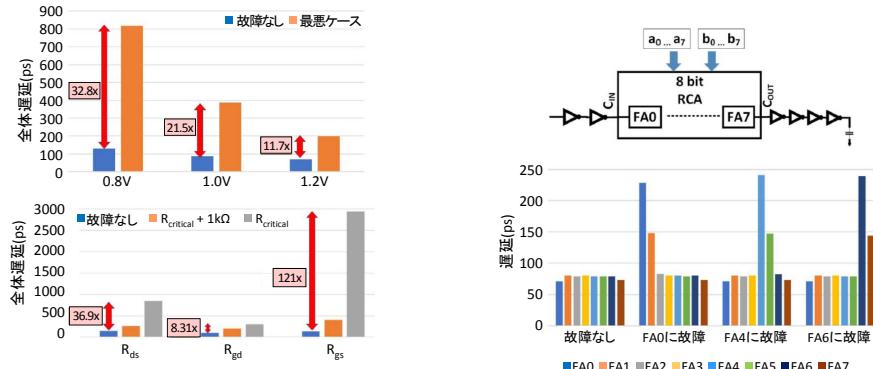

## 講演の概要: RP8.3

- S. Pandey (Georgia Tech.): 短絡欠陥起因の複数ゲート遅延に対応する2パターンテスト

- 歩留り向上: 微細化による予期せぬ欠陥により困難化

- テスト品質向上が重要

- 一部の抵抗性短絡欠陥はDCテストでは検出不可→2パターンテストが必要

- 特定のパターンに対してパス遅延が通常より50~80倍になる場合あり

- 入出力に接続するゲートの遅延に影響するため

- 提案手法: セル内の短絡(中間の抵抗値)に対するマルチパターンテスト手法

- 故障モデル: ソース, ドレイン, ゲートのそれぞれの間の抵抗性短絡

- クリティカルパスの遅延テストで大きな遅延を発生させる故障を優先的に選択

- クリティカルな抵抗値( $R_{critical}$ )の探索には2分探索法の変形を使用

2021.06.29 Kazumi Hatayama

75

## 講演の概要: RP8.3 (cont.)

- 評価実験: 標準セル(2NANDほか), 柄上げ加算器を使用

- 欠陥のVddに対する感度: Vddが低いほど遅延増が大(0.8Vで30倍以上)

- 欠陥の位置に対する感度: ゲート-ソース間が最大( $R_{critical}$ で120倍以上)

- 8ビット柄上げ加算器(全加算器(FA)8段で構成)での遅延増:

- 2段先のFAまで遅延増あり, 3段先以降は影響なし

2021.06.29 Kazumi Hatayama

76

## 講演の概要:IP2.2

- J. Aki (Teradyne): 高プロトコルスキャンの生産適用におけるテスト課題を解決

- ・高速シリアルI/Fを利用したスキャン: テスト時間&スキャンピンの対策として注目

- ・テスト装置(ATE)における課題: シグナルインテグリティ(SI), ドライバソフトの品質

- ・講演内容: これらの課題に対する解決策を提示

- ・SIの事例: USB3.2 Gen2x1・BER(ビットエラー率)の増加によりテスト時間が増大

- ・通常のUSBシステム: 全体で23dBの損失が発生

- ・US ATEシステム: DIB(デバイスI/F基板)の工夫により信号減衰&ジッタを解決

- ・ベンチ評価基板からATEへの移行: 様々な変換が必要

- ・ブート時間の低減, ブートプロセスの簡略化してテストに最適化

- ・データパケットの利用効率向上: パケットの使用方法を工夫して最適化

- ・テストのワクワクする未来

- ・どのプロトコルを使用するかには様々な選択肢あり

- ・個別の課題もあれば共通の課題もあり

- ・改善と最適化に多くのチャンスあり

2021.06.29 Kazumi Hatayama

77

## 講演の概要:SS2.1

- Y. Huang (HiSilicon): メニーコアAIチップのテスト

- ・AIアクセラレータ: AI用途の計算パワーのエンジンとして人気上昇中

- ・様々なアーキテクチャ・十分な理解が設計&テストの観点から非常に重要

- ・講演内容: DFTの観点から種々のAIチップに共通するポイントを整理

- ・DFT実装(ATPG実行)形態: コア単位, スーパーコア単位, チップ一括を比較

- (スーパーコア: 複数のコアを1つにまとめたブロック)

- ・コア単位: 面積増, テスト時間, テストモードなどに問題

- ・チップ一括: ATPG実行時間/メモリ, 消費電力などに問題

- ・スーパーコア単位: 様々な点でSweet Spotとなりうる

- ・複数コアのテスト: 同一パターンの同時供給(Broadcast)も可能・電力は要注意

- ・コアレベルDFT: 圧縮回路, BIST回路など・許容レベルの面積

- ・複数コアレベルDFT: パターン発生回路, ブロードキャストスキャンチェーンなど

- ・スキャンピンをスーパーコア間で共有するなどの工夫も可能

コア単位

スーパーコア単位

チップ一括

2021.06.29 Kazumi Hatayama

78

## AMS/RFテスト関連

- RP3: Analog and Mixed Signal Testing

- RP7: New Directions in Diagnosis, Calibration and Fault Modeling

- AMS/RFテスト関連では一般4件の講演あり

- RP3.1及びRP7.2について紹介

| 講演No. | タイトル                                                                                 | 著者                                                                                             | 所属                       |

|-------|--------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|--------------------------|

| RP3.1 | Automated Observability Analysis for Mixed-Signal Circuits                           | S. Sunter, K. Jurga                                                                            | Siemens EDA, Poznan U.   |

| RP3.2 | Design for Testability of Low Dropout Regulators                                     | W. Eisenstadt, A. Tulsiram                                                                     | U. Florida               |

| RP3.3 | Maintaining NIST-Traceability for MEMS Sensors via In-Field Electrical Recalibration | I. Bassi, S. Ozev, D. Chang                                                                    | Arizona S. U., Alphacore |

| RP7.2 | Trim Time Reduction in Analog/RF ICs Based on Inter-Trim Correlation                 | V. A. Niranjan, D. Neethirajan, C. Xanthopoulos, E. de la Rosa, C. Alleyne, S. Mier, Y. Makris | UT Dallas, Qualcomm      |

2021.06.29 Kazumi Hatayama

79

## 講演の概要:RP3.1

- S. Sunter (Siemens EDA): MS回路に対する観測性の自動解析

- ・MS回路の欠陥Sim.: 適切な準備があれば実用時間で可能に・自動化が進展

- ・高品質化のための次のステップ: 未検出欠陥の原因解析→検出可能化

- ・提案手法: 未検出欠陥の観測性の自動解析手法

- ・特定テスト入力に対する可観測性を解析・欠陥個所からの経路をフォロー

- ・各未検出欠陥に対して短絡/開放欠陥による電圧変化の伝搬状況を確認

- ・実験評価: ITC'17 AMSベンチマークの8ビットSAR ADCを使用

- ・48の欠陥のうち17が未検出・短絡欠陥が3, 開放欠陥が14

- ・17の未検出欠陥のうち9が活性化できず→より良いテスト入力が必要

- ・活性化できた8のうち6が観測できず→より良い出力解析が必要

- ・残りの2は影響を途中までしか伝搬できず→より良いDFTが必要

2021.06.29 Kazumi Hatayama

80

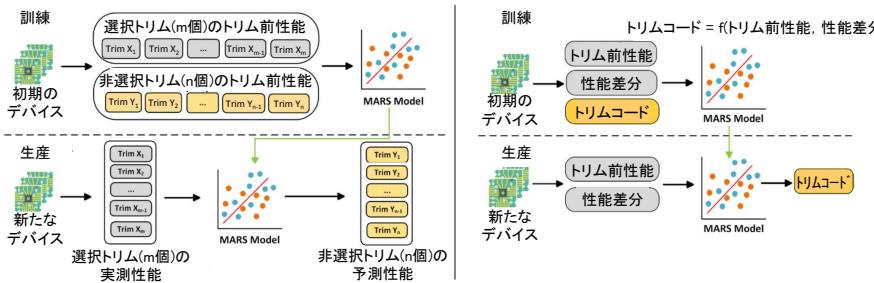

## 講演の概要: RP7.2

### • V. A. Niranjan (UT-Dallas): トリム間相関に基づくアナログ/RF ICのトリム時間削減

- ・トリミング(製造後の性能較正): アナログ/RF ICの製造&テスト工程で重要

- ・チップごとに性能パラメータを個別に微調整・高歩留り&高性能を両立

- ・一般的な方法: デジタルトリムコードの選択と測定を繰り返して性能を最適化

→現在のアナログ/RF ICでは数100のトリム・多くの時間(コスト)が必要

- ・提案手法: 機械学習ベース手法によりトリム間相関を利用してトリム時間を削減

- ・トリムコードのモデル化: トリム前性能予測モデル, トリムコード予測モデル

- ・取得済のトリムデータから回帰モデルにより他の最適トリムコードを推定

- ・予測に用いるトリムの対象を遺伝的アルゴリズム(GA)を用いて最適化

2021.06.29 Kazumi Hatayama

81

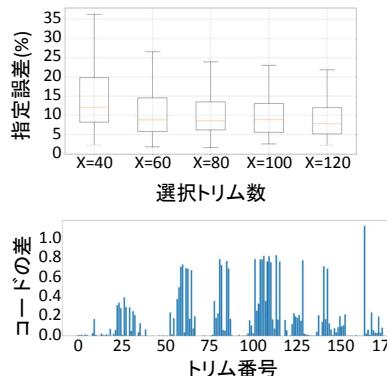

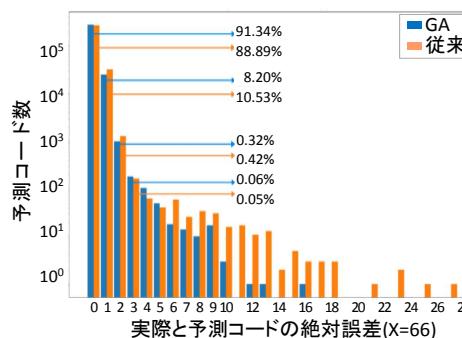

## 講演の概要: RP7.2 (cont.)

- ・実験評価: 先端プロセスのRFトランシーバIC(5712チップ)を使用

- ・トリム数(N)は173: すべてのトリム前性能及び最適トリムコードのデータあり

- ・トリム前性能の予測精度: 高い相関あり, 精度は選択トリム数(X)に従って向上

- ・トリムコードの予測精度: コードの差は非常に小さい(最大で1程度)

- ・遺伝的アルゴリズム(GA): 従来手法と比較して誤差を改善

2021.06.29 Kazumi Hatayama

82

## AI応用関連

### • RP5: Diagnosis and Root Cause Analysis

### • RP7: New Directions in Diagnosis, Calibration and Fault Modeling

### • SS1: Machine Learning for Semiconductor Test and Reliability

### • SS4: Machine Learning in Test: A Survey of Analog, Digital, Memory, and RF IC

#### ・AI応用関連では一般1件, 特別セッション5件の講演あり

#### ・他にAIハードのテストと信頼性に関する2件の特別セッションあり

#### ・RP7.1について紹介

| 講演No. | タイトル                                                                           | 著者                                                                                                           | 所属              |

|-------|--------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|-----------------|

| RP5.3 | Unsupervised Root-Cause Analysis with Transfer Learning for Integrated Systems | R. Pan, X. Li, K. Chakrabarty                                                                                | Duke U.         |

| RP7.1 | Identifying Good-Dice-in-Bad-Neighborhoods Using Artificial Neural Networks    | C.-H. Yang, C.-H. Yen, T.-R. Wang, C.-T. Chen, M. Chern, Y.-Y. Chen, J.-N. Lee, S.-Y. Kao, K.-C. Wu, M. Chao | NYMCTU, Realtek |

| SS1.1 | Machine Learning for Semiconductor Reliability                                 | H. Amrouch                                                                                                   | U. Stuttgart    |

| SS1.2 | Explainability as a Frontier for Machine Learning in IC Test                   | B. Tan                                                                                                       | New York U.     |

| SS1.3 | Physics-Informed Convolutional Neural Network for Electrostatics Analysis      | W. Jin                                                                                                       | UC Riverside    |

| SS4.1 | How Machine Intelligence can Solve Test Problems (and How it can't)            | S. K. Millican                                                                                               | Auburn U.       |

| SS4.2 | What has been Done - Studies of Machine Intelligence in Test                   | S. Roy                                                                                                       | Auburn U.       |

2021.06.29 Kazumi Hatayama

83

## 講演の概要: RP7.1

### • C.-H. Yang (NYMCTU): ANNを用いたGDBN(悪い近傍の中の良品ダイ)の識別

#### ・GDBN: 疑わしいダイを棄却して不良率を低減する効率的手法

#### ・BNR(隣接の不良ダイの比率): 棄却判定の指標として有効(実験で確認済)

#### ・提案手法: 新たなNNベースの拡張GDBN手法

#### ・より広い範囲の近傍を用いて各ダイの疑惑レベル(SL)を正確に予測

#### ・SLを指標とすることで十分に不良率を低減しつつ歩留り損失を最小化

#### ・実験評価: 65nm製品(24ロット, 約3Mダイ), 7×7の近傍を使用, BNR利用と比較

#### ・提案手法がBNR利用と比べて歩留り損失を効率的に低減できることを確認

| SL利用     | 見逃し不良(元データ) | 棄却した見逃し不良 | 歩留り損失(%) | 不良率(DPPM) |

|----------|-------------|-----------|----------|-----------|

| SL > 1.0 |             | 0.00      | 0.000%   | 8.60      |

| SL > 0.9 |             | 1.47      | 0.003%   | 8.09      |

| SL > 0.8 |             | 2.17      | 0.007%   | 7.86      |

| SL > 0.7 |             | 2.61      | 0.011%   | 7.70      |

| SL > 0.6 |             | 3.01      | 0.018%   | 7.57      |

| SL > 0.5 |             | 3.43      | 0.028%   | 7.42      |

| SL > 0.4 |             | 3.87      | 0.044%   | 7.27      |

| SL > 0.3 |             | 4.44      | 0.072%   | 7.08      |

| BNR利用       | 見逃し不良(元データ) | 棄却した見逃し不良 | 歩留り損失(%) | 不良率(DPPM) |

|-------------|-------------|-----------|----------|-----------|

| BNR > 100%  |             | 0.00      | 0.000%   | 8.60      |

| BNR > 87.5% |             | 0.62      | 0.001%   | 8.38      |

| BNR > 75.0% | 25.11       | 1.10      | 0.004%   | 8.22      |

| BNR > 62.5% |             | 1.39      | 0.009%   | 8.12      |

| BNR > 50.0% |             | 2.10      | 0.033%   | 7.88      |

2021.06.29 Kazumi Hatayama

84

# アウトライン

- ・ VTSについて

- ・ VTS2021の概要

- ・ 論文発表の全体動向

- ・ 注目セッションの紹介

- ・ まとめ

2021.06.29 Kazumi Hatayama

85

# VTS2022は未定

- ・VTS2022については詳細は未定

- ・Webサイト(<http://www.ttc-vts.org>)で確認ください

2021.06.29 Kazumi Hatayama

87

# VTS2021の特徴

- ・今回のVTS2021の特徴をまとめると以下のとおり。

## (1) セキュリティ関連は論文数が減少

- ・論文数は大幅に減少したが、依然としてAI、車載と合わせて、3大トピックの一角

- ・セキュリティサポートツールの動きもあり

## (2) AIチップのテストや高信頼化も話題に

- ・「AI for Test」だけでなく「Test for AI」への取り組みも活発化

- ・2件の特別セッションが設置された

## (3) 中国のプレゼンスが引き続き高い

- ・国別論文数も5年連続で2位(同率を含む)を維持

- ・実行委員(OC)2名+プログラム委員(PC)1名

- ・日本は小林先生(OC)のみ

2021.06.29 Kazumi Hatayama

86