## 高性能逐次比較型AD変換器 アーキテクチャ

早川 晃 趙 楠 (群馬大学工学部 電気電子工学科) 堀田 正生 (武蔵工業大学工学部 電子通信工学科 ) 小林 春夫 (群馬大学工学部 電気電子工学科)

## 目次

- 研究目的

- 逐次比較型AD変換について

- 高信頼性AD変換器の提案

- 誤差補正アルゴリズム

- ・ 低消費電力の構成

- まとめ

## 研究目的

- 車載用AD変換器を開発する

- 高信頼性

- 12~14ビット精度

- 低消費電力(従来の1/5)

- 中速サンプリング(20MS/s)

- 低コスト(小チップ面積デジタルCMOSプロセス)

## 研究背景

- 車載用エレクトロニクスの技術産業の要求大

- マイコンと組み合わせたAD変換器の高信頼性化

高速

高精度

低消費電力

低コスト化

車載用では高信頼性が最重要課題

## 目次

- 研究目的

- 逐次比較型AD変換について

- 高信頼性AD変換器の提案

- 誤差補正アルゴリズム

- ・ 低消費電力の構成

- まとめ

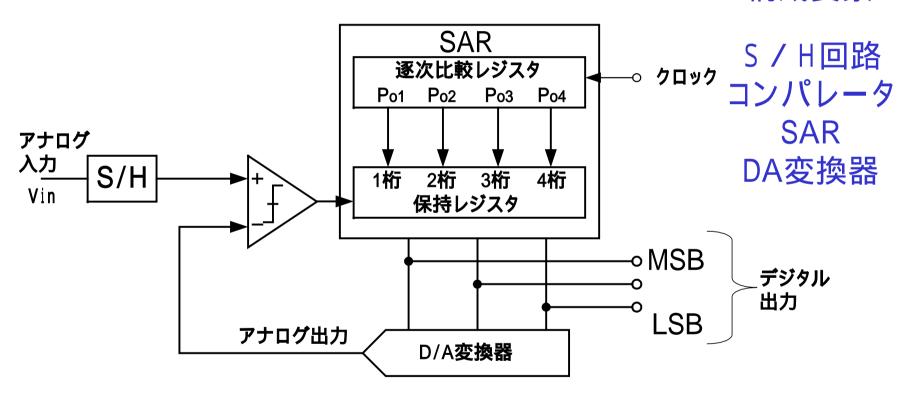

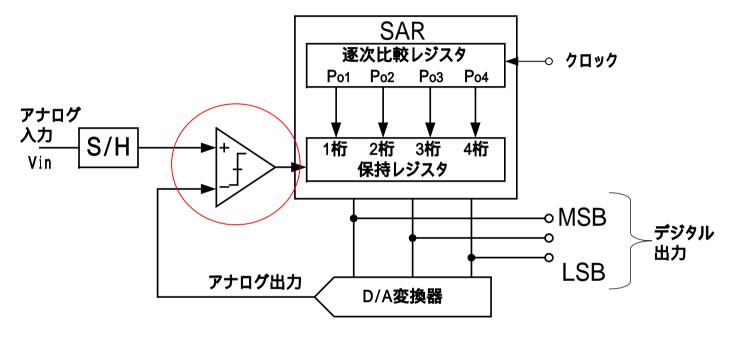

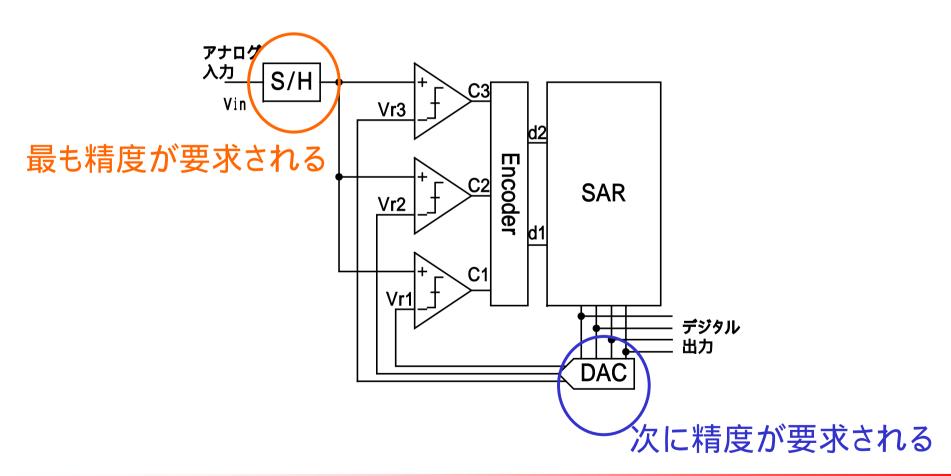

## 逐次比較形AD変換器の構成

#### 構成要素

SAR = Successive Approximation Register

#### 逐次比較型AD変換器の特徴

## 利点

## 欠点

- 低電力消費

- 高分解能

- 高精度

- 出力データのレイテンシー (遅れ)がない

- 小型

- サンプリング速度が中速

- 高精度化のため、DACや コンパレータ等の要求が 厳しい

車載用マイコン 工業用制御等で広く利用

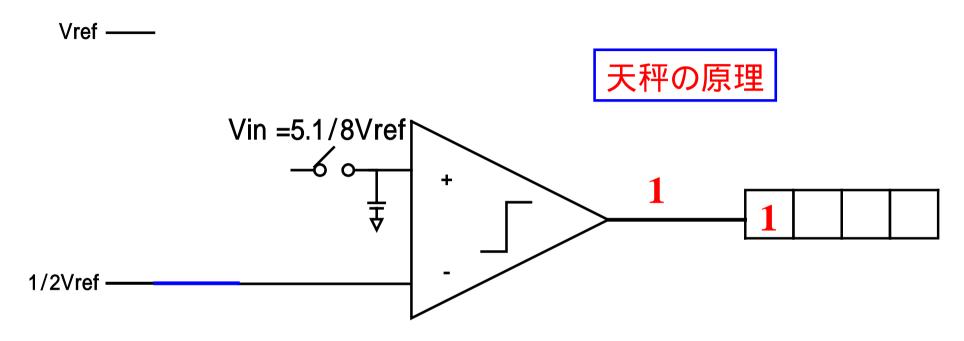

## 逐次比較型AD変換器動作説明1

0 —

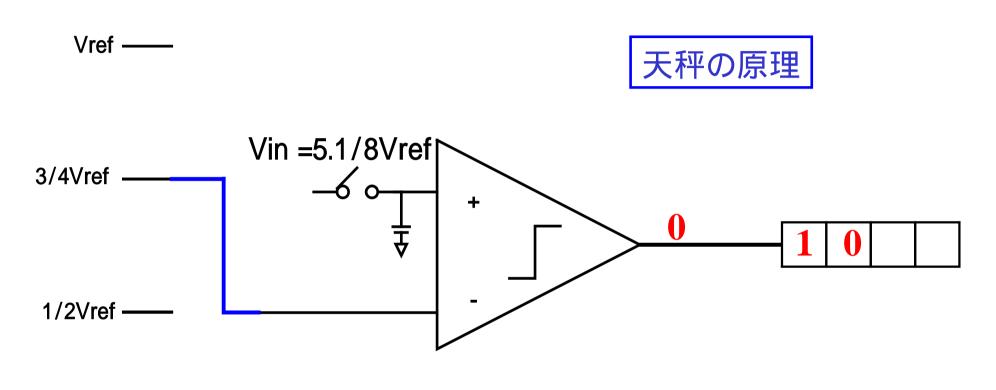

## 逐次比較型AD変換器動作説明2

1/4Vref ——

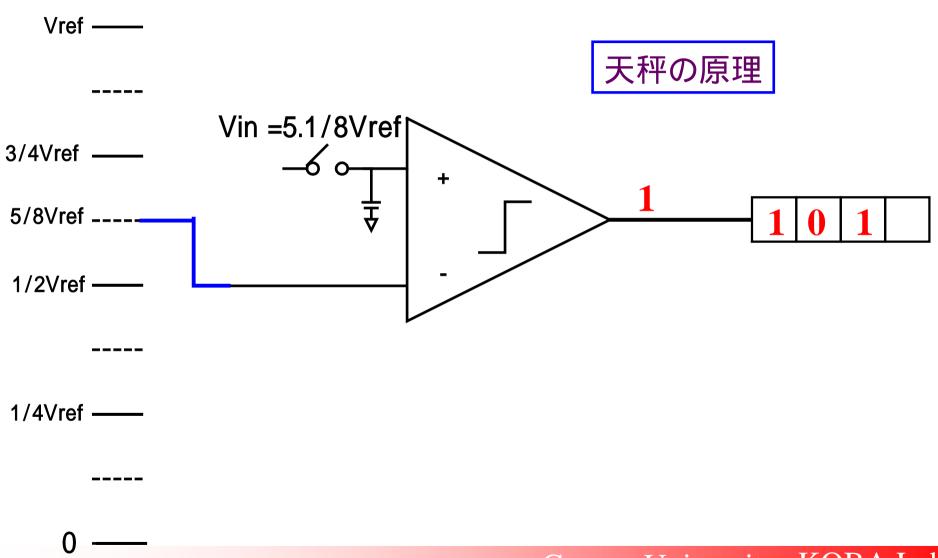

## 逐次比較型AD変換器動作説明3

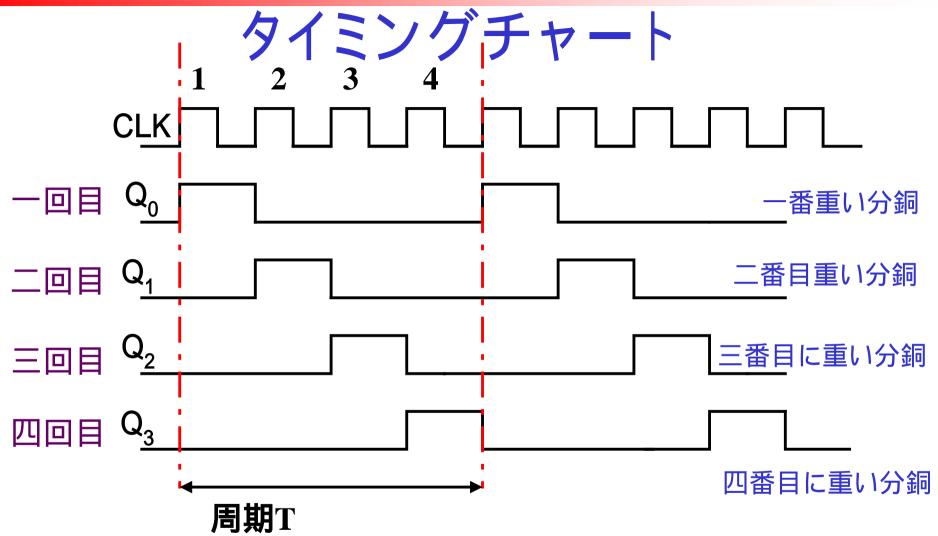

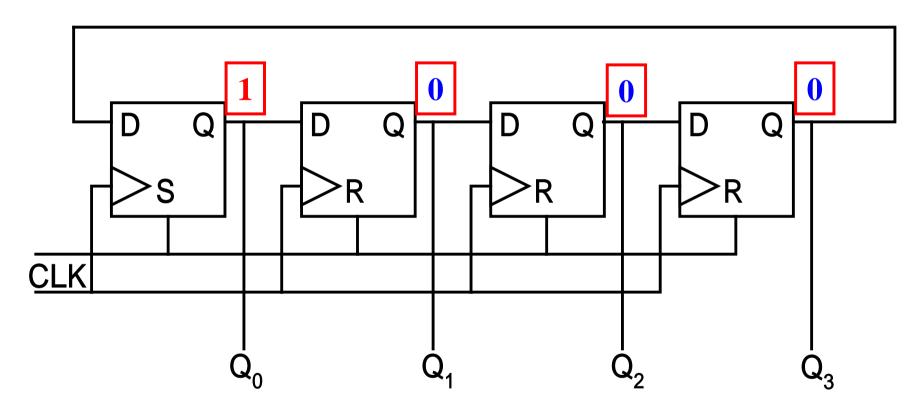

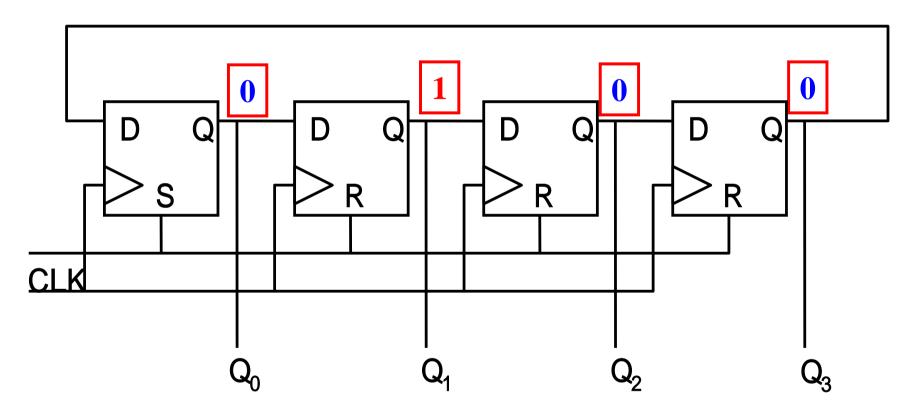

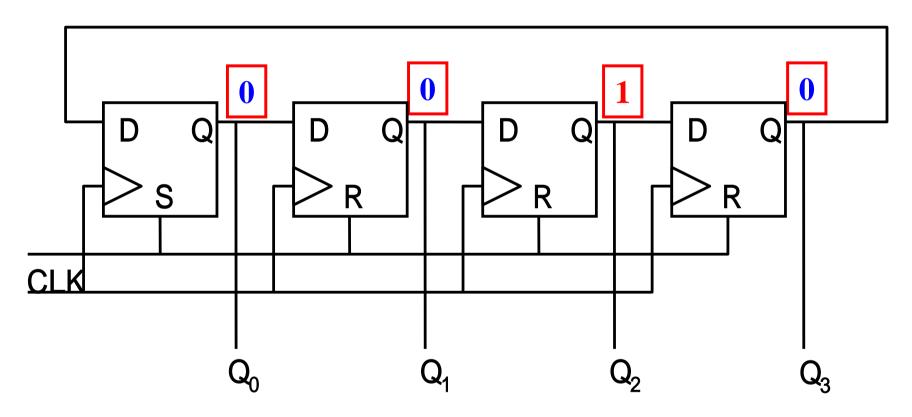

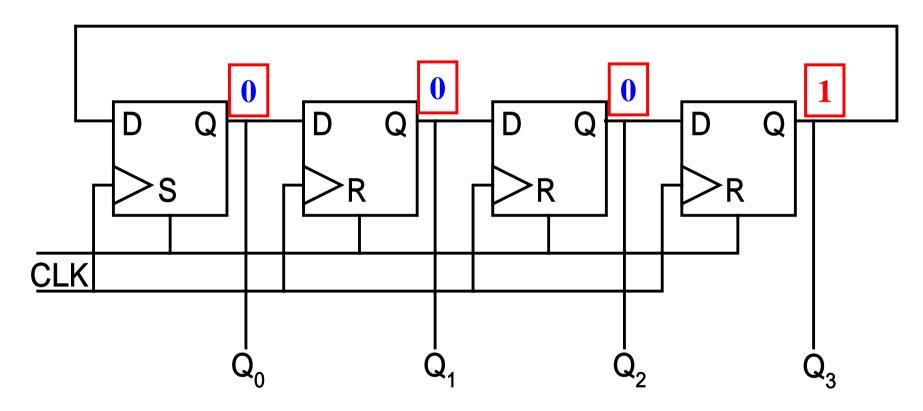

周期T毎にAD変換 クロックを発生させるためにリングカウンターを使用

クロックが進むと $Q_0$   $Q_1$   $Q_2$   $Q_3$ と進む

## 目次

- 研究目的

- 逐次比較型AD変換について

- 高信頼性AD変換器の提案

- 誤差補正アルゴリズム

- ・ 低消費電力の構成

- まとめ

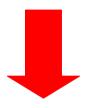

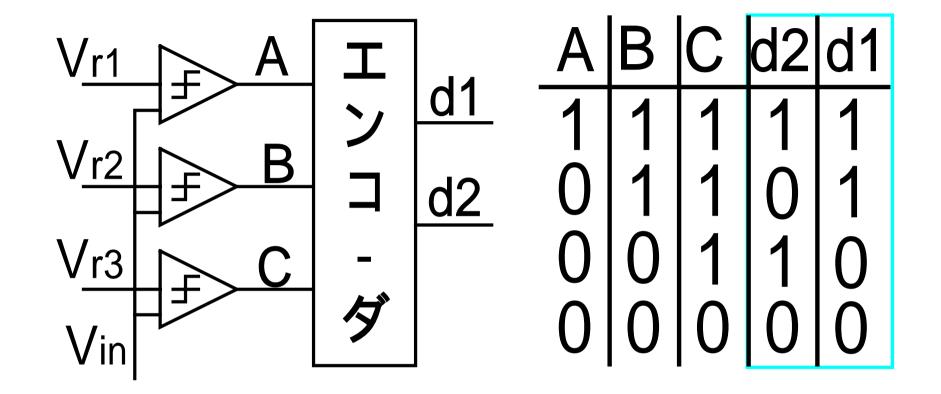

## 従来逐次比較型ADCの問題点

コンパレーター個では一度間違えてしまうと修正がきかない

車載用の高信頼性要求のため、改善が必要

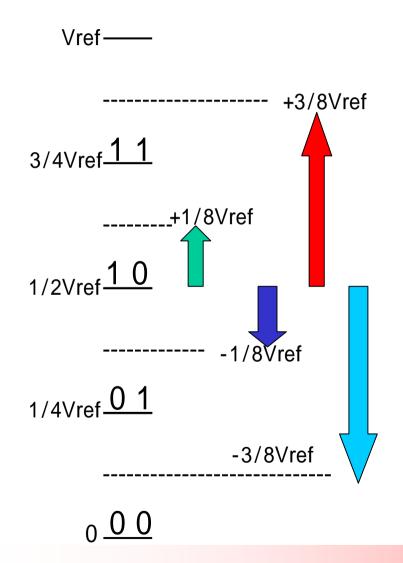

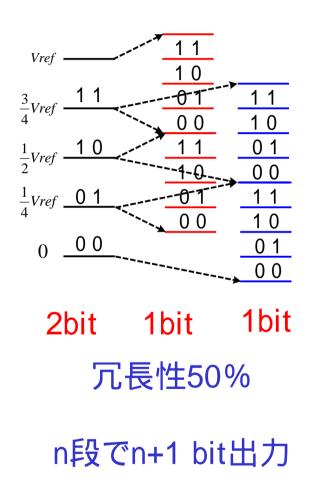

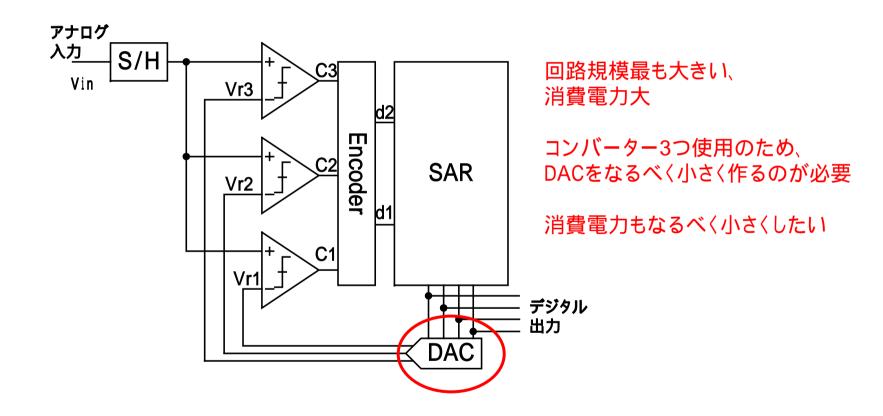

三個のコンパレータを使用し、 比較電圧範囲に冗長性を持たせる

前段でのエラーは後段でデジタル補正可能

3個のコンパレータとエンコーダで 2bitのデジタルデータ出力を作る

## 目次

- 研究目的

- 逐次比較型AD変換について

- 高信頼性AD変換器の提案

- ・誤差補正アルゴリズム

- ・ 低消費電力の構成

- まとめ

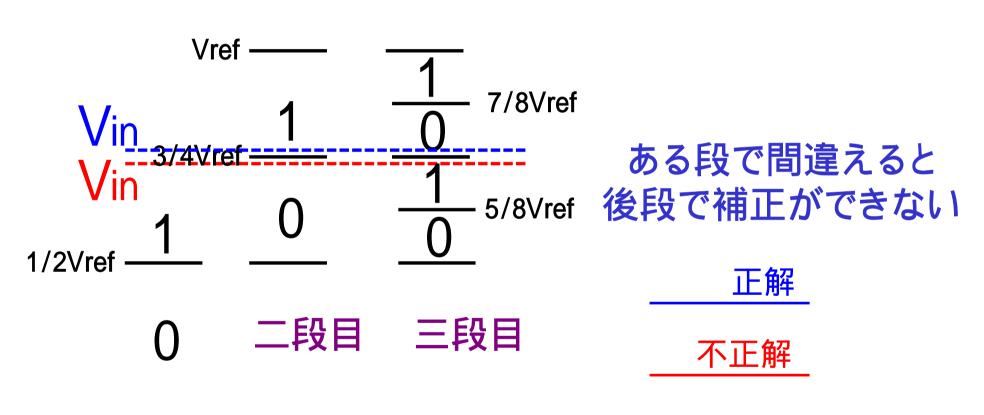

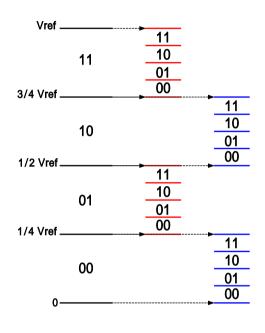

## 1個のコンパレータによる逐次AD変換 (従来法)

一段目

## 1個のコンパレータによる逐次AD変換 (従来法)

一段目

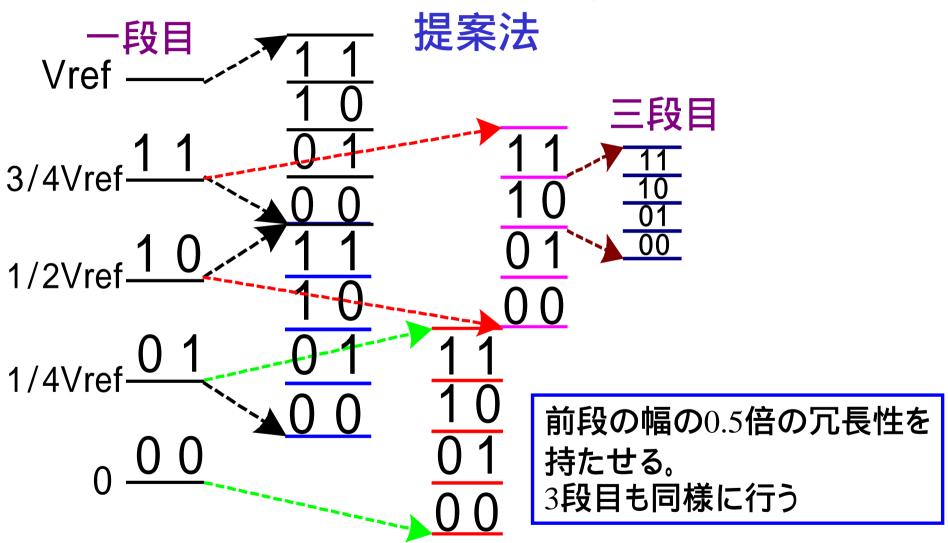

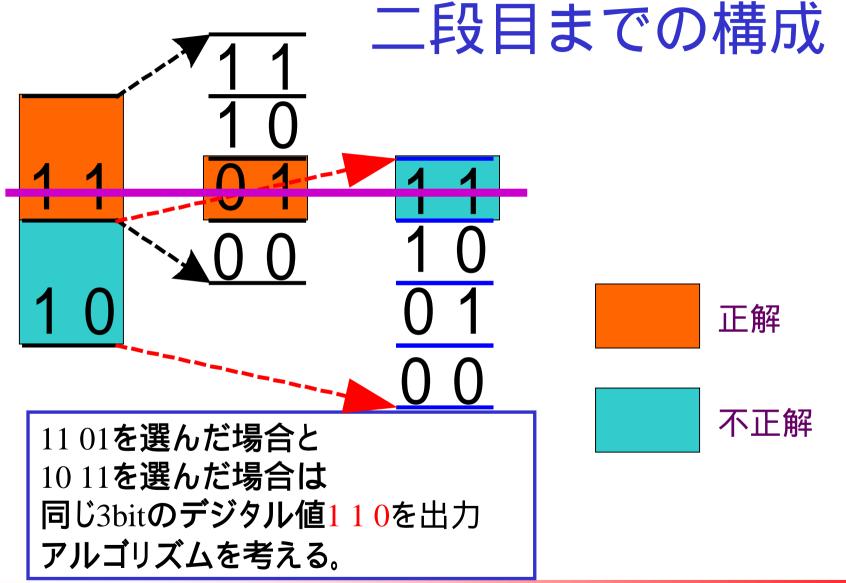

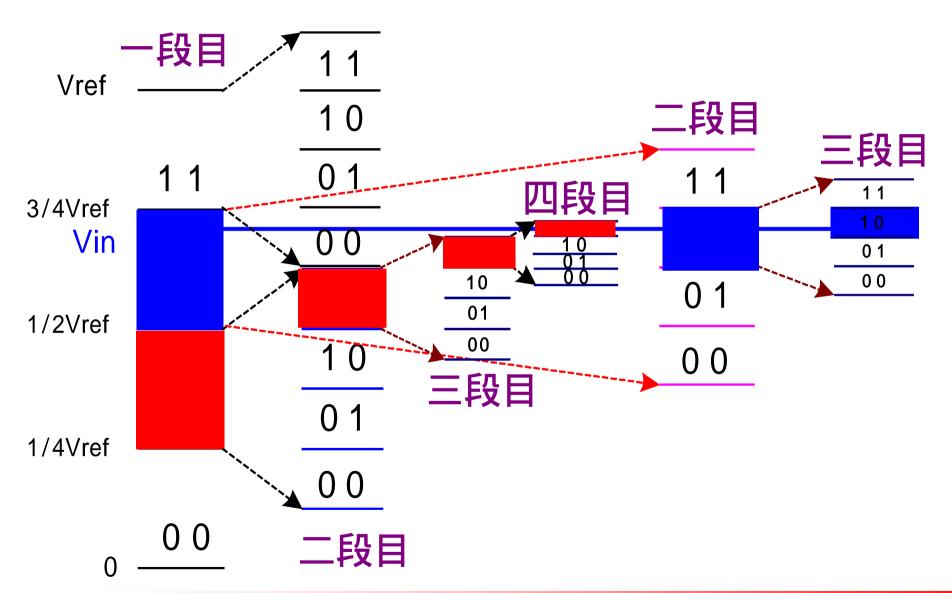

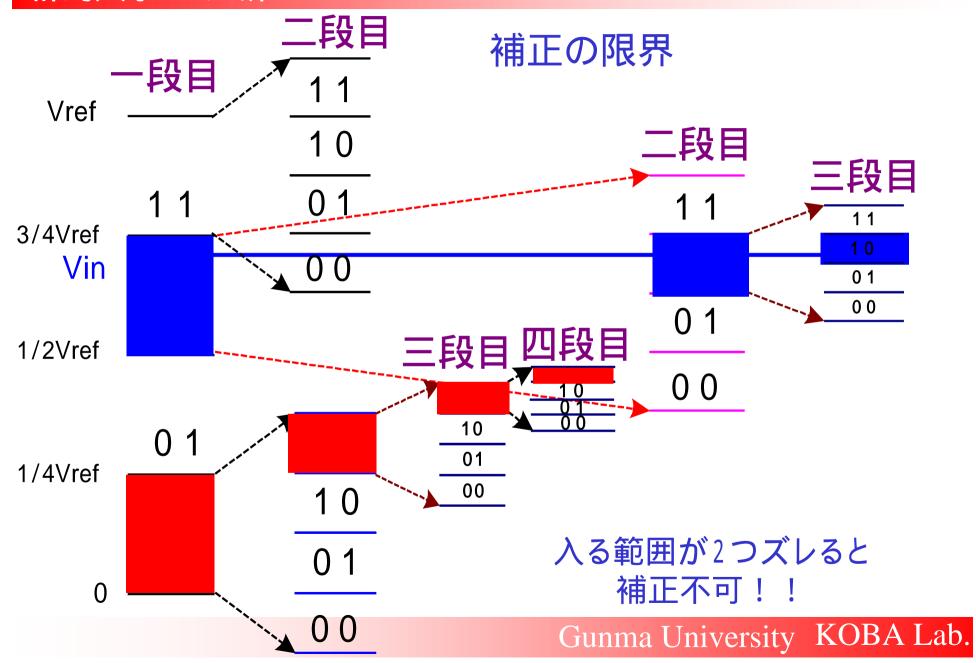

### 3個のコンパレータによる誤差補正アルゴリズム

二段目

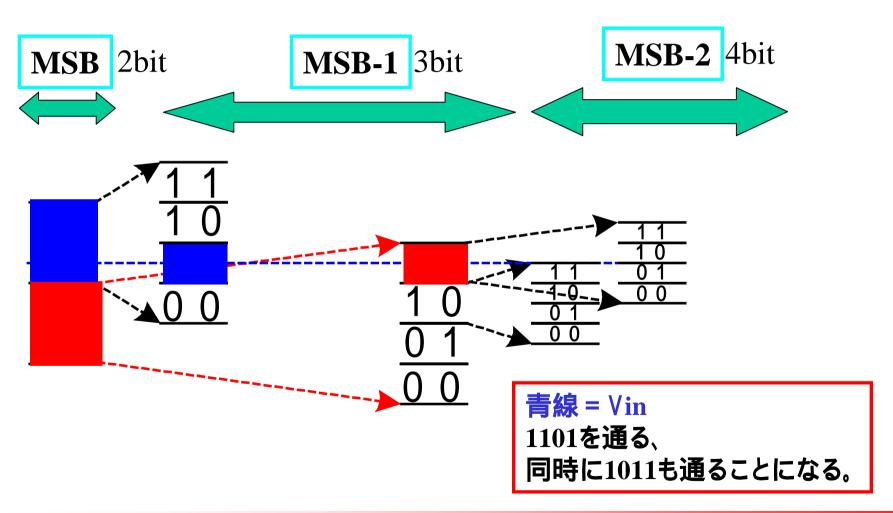

## アルゴリズム

#### 誤差補正原理の説明

10 10, 01 10 00, 11 **x**

10 11の場合 前段を11 現在段を01に変更

10 00の場合

前段を01 現在段を10に変更

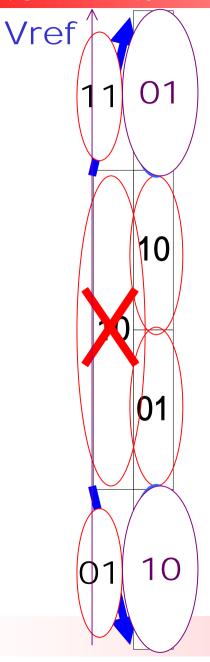

## 2段目からの中心参照電圧

2段目では

11を選んだ場合1/2Vrefに+3/8Vref

10を選んだ場合1/2Vrefに+1/8Vref

01を選んだ場合1/2Vrefに-1/8Vref

00を選んだ場合1/2Vrefに-3/8Vref

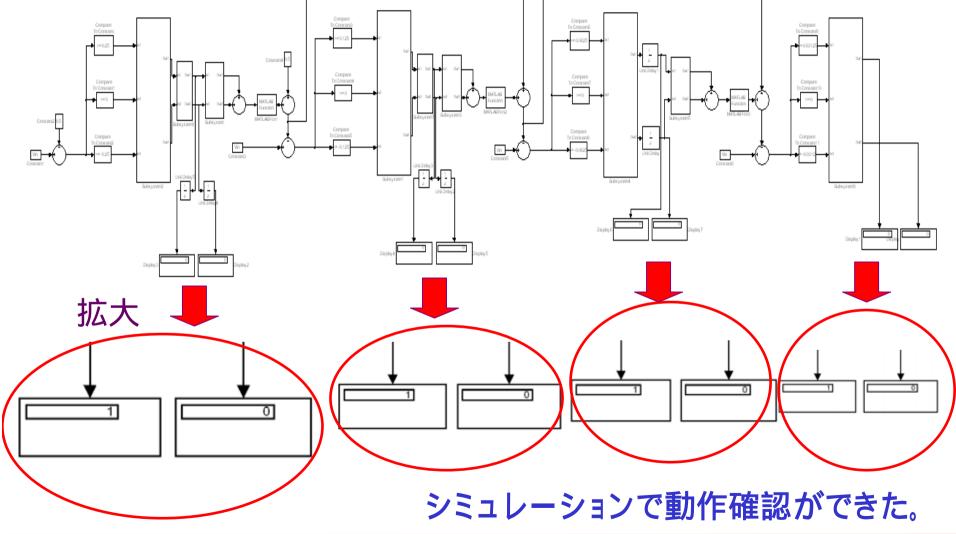

## Matlabでのシミュレーション

#### 各動作モードの比較

2bit 2bit 2bit 冗長性なし

n段で2n bit出力

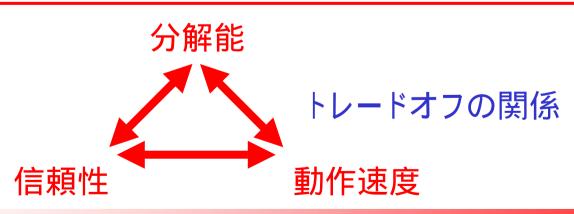

## 冗長性と分解能のトレードオフ

#### 動作速度一定では、

- 冗長性がある場合、分解能が低い

- 冗長性がない場合、分解能が高い

#### 分解能一定では、

- 冗長性がある場合、動作速度が低い

- 冗長性がない場合、動作速度が高い

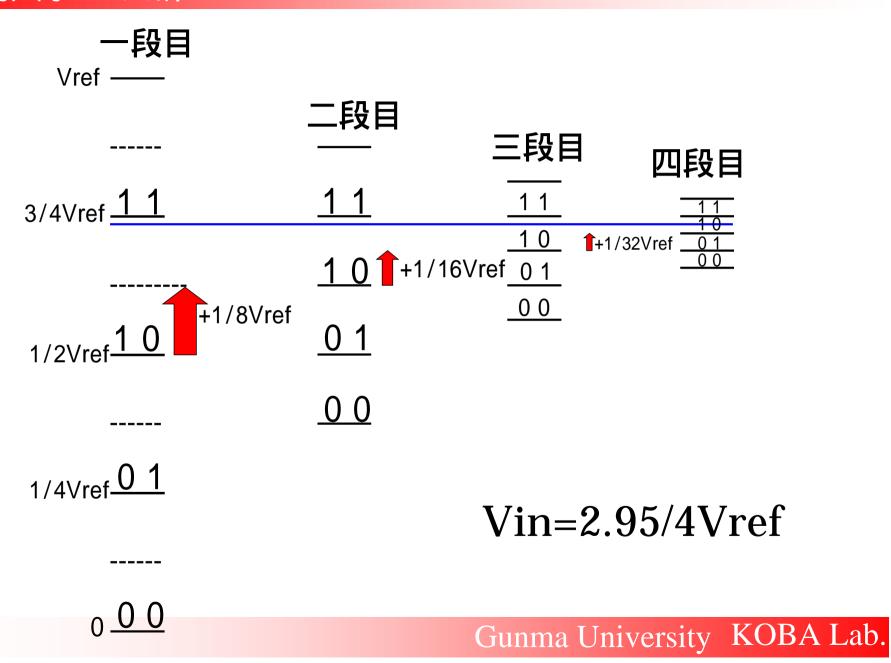

# 元長性50%のビッチャート 三段目 四段目 群馬大学 コバ研 一段目 二段目

## 目次

- 研究目的

- 逐次比較型AD変換について

- 高信頼性AD変換器の提案

- 誤差補正アルゴリズム

- ・ 低消費電力の構成

- まとめ

## 提案構成の回路規模と消費電力

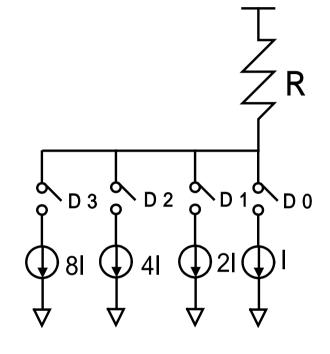

### 逐次比較型AD変換器内部DA変換器の構成

- 抵抗ストリング

- 容量

- (容量+抵抗ストリング)方式

- (電流源+抵抗)方式

検討

- デジタル補正による高分解能可

- 小チップ面積化可能

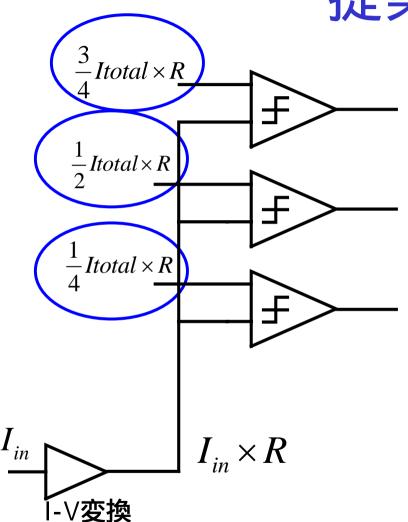

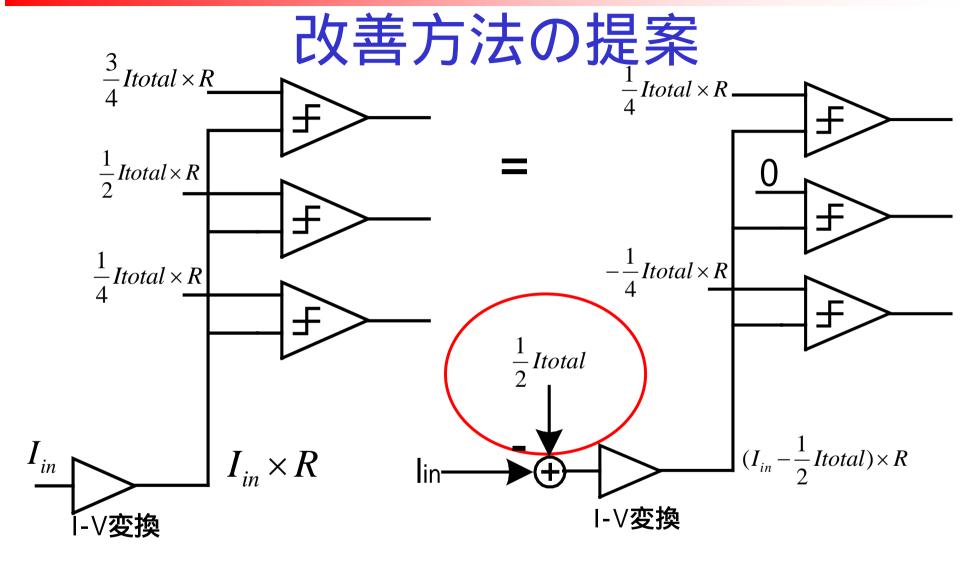

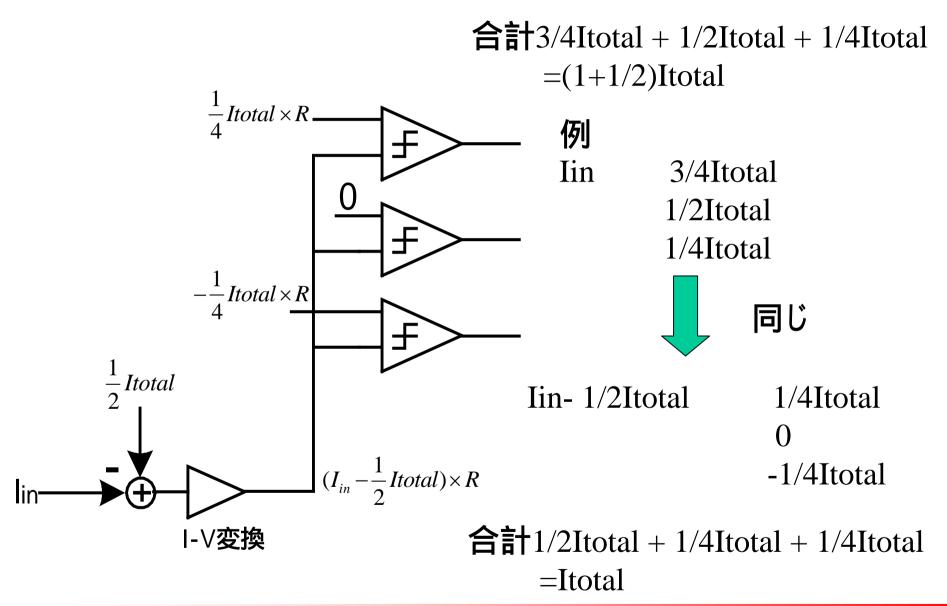

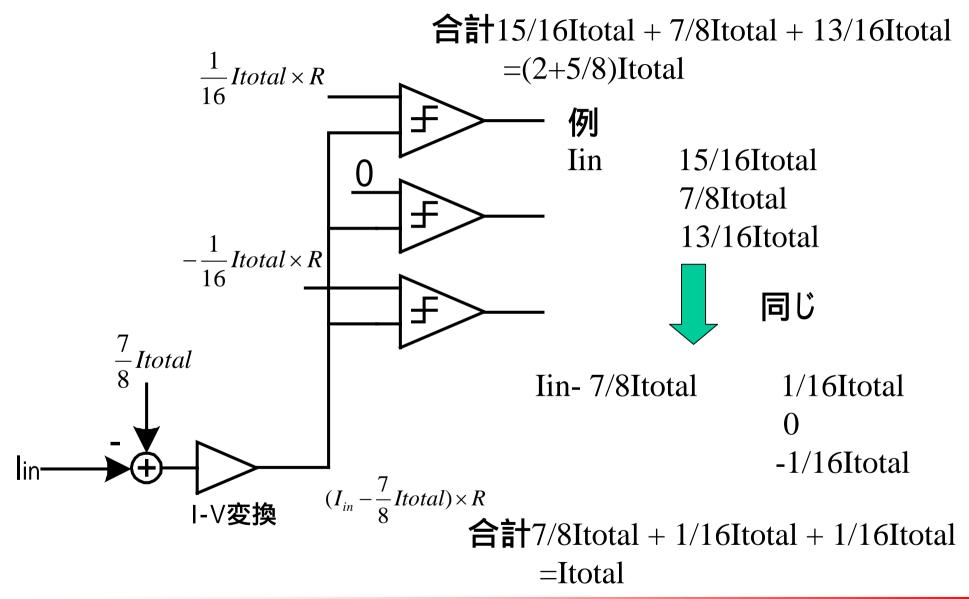

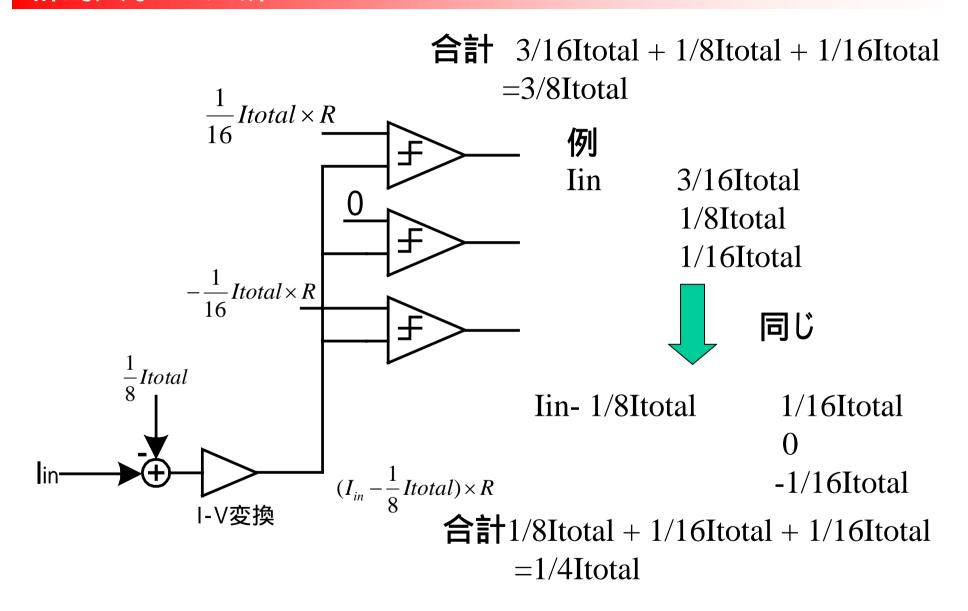

## 提案構成の問題点

従来方式でのDACの最大消費電流を1

提案方式では電流の合計が1を超える

従来より電流源+抵抗ストリングDACの 消費電力、チップ面積が三倍になる

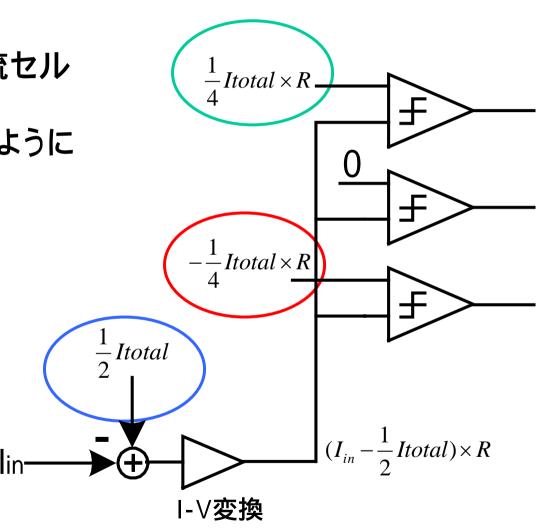

合計3/4Itotal + 1/2Itotal + 1/4Itotal = (1+1/2)Itotal < 3Itotal

差動構成で-1/4ltotal Rが容易に実現

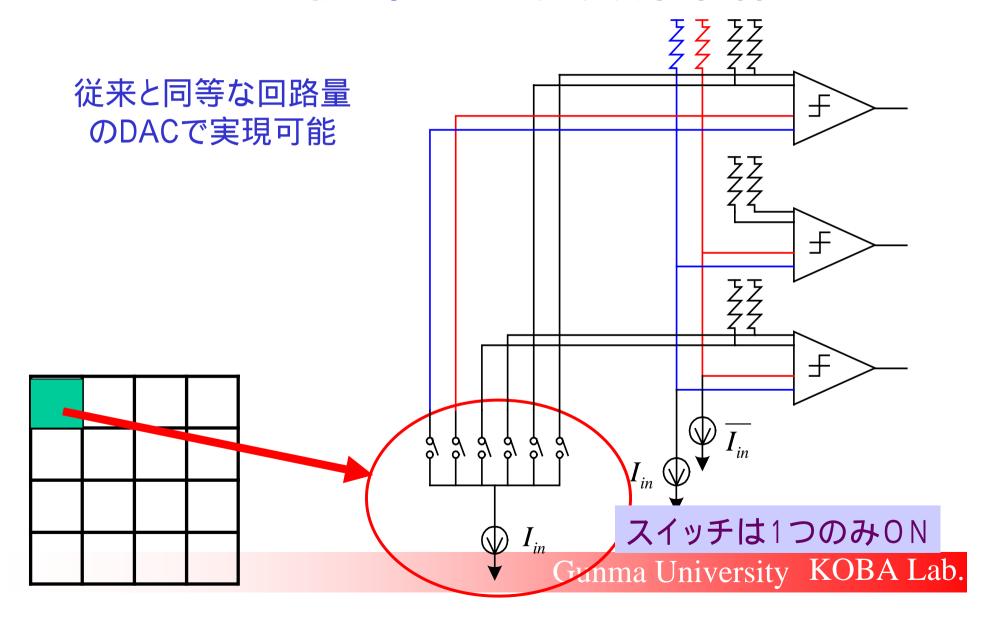

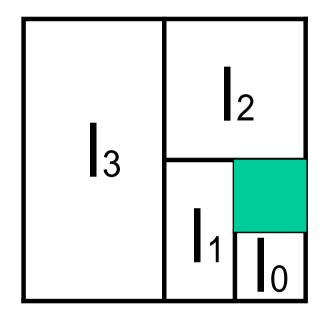

色に対応した場所の電流セルを使う。

この合計の値が1になるように考える。

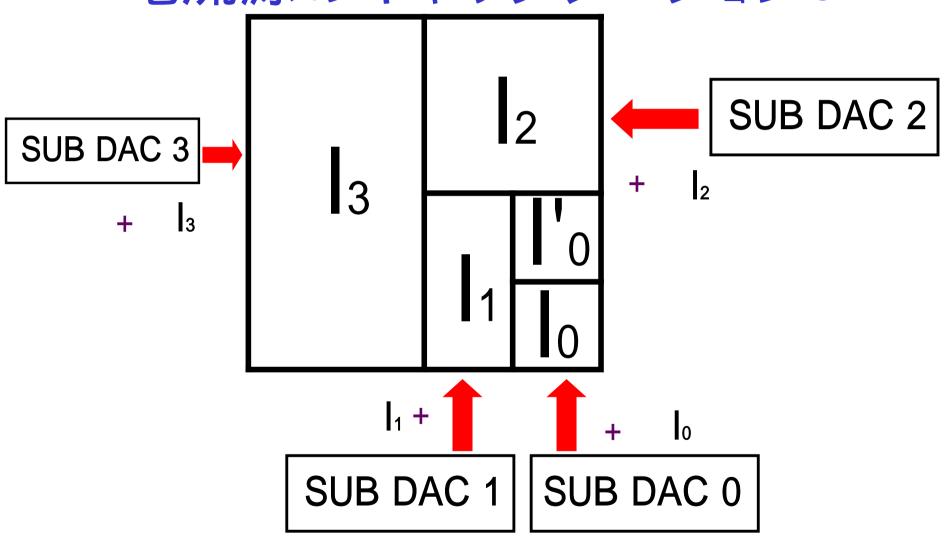

# 提案DAC実現回路

# 素子精度の要求について

### 高分解能の逐次比較ADを実現するには

高精度のDACが必要

12bit以上の精度 電流源キャリブレーションが必要

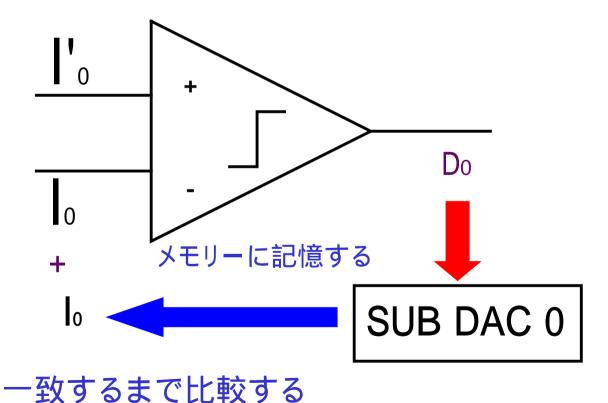

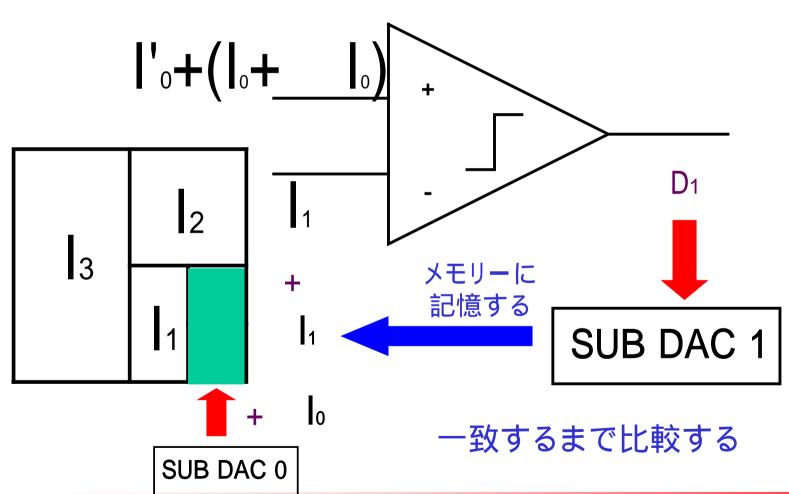

# 電流源のキャリブレーション

$$I_3 = 2I_2$$

$I_1 = I_0' + I_0$

$$I_2 = I_1 + I_0' + I_0$$

- 電流源を2進の重みをつけて分割

- I'₀をリファレンスとする

# 電流源のキャリブレーション2

# 電流源のキャリブレーション3

## 目次

- 研究目的

- 逐次比較型AD変換について

- 新しい提案方法

- 誤差補正アルゴリズム

- ・ 低消費電力のための提案

- まとめ

## まとめ

- 車載用高信頼性AD変換の開発を行った

- 冗長回路(コンパレータ3個)を用いて誤差補正を可能にした **高信頼性**

- 低消費電力構成の提案

- 電流源のキャリブレーション 14bit精度

- Process Portabilityのあるアーキテクチャ

# 課題

- 12~14bit全体の動作確認

- コンパレータのオフセットを対策