# 電子回路設計と古典数学

Electronic Circuit Design based on Classical Mathematics

# 小林 春夫, 桑名 杏奈 (群馬大学)

Haruo KOBAYSHI, Anna KUWANA (Gunma University)

#### 1. はじめに

江戸時代の和算家 久留島喜内は優れた詰将棋をいくつも残している。一方、電子回路設計は将棋のようなところがある。(現在のようなコンピュータ将棋が発展する前は)将棋は頭を使うゲームで理屈・理論に基づくようであるが、将棋指しの得意不得意や好みのような「理外の理」で戦法が選ばれるところがある。同様に電子回路設計では理論化・体系化は完全には確立されておらず、設計者の経験や得意不得意、好みで回路方式が選択されるところがある。電子回路設計分野のこの状況を打破しこの分野を「アナログサイエンス」としてさらに発展させるため、筆者らはアナログ・デジタル混載の電子回路設計の理論化・体系化や新回路方式の開発を目的として和算を含めた古典数学をこれに応用する研究を行ってきた。本稿ではベテラン将棋棋士が自戦記集を記すのと同じような気持ちで、筆者らがこれまでいくつか取り組んできた研究事例とその根底にある「思い」を紹介する。

### 2. 古典数学を用いた電子回路設計の研究事例

#### (a) フィボナッチ数列重み付けを用いた冗長比較近似AD変換器:

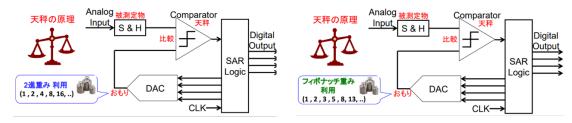

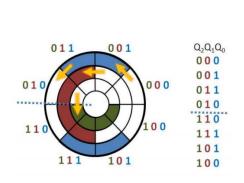

逐次比較近似AD変換器 (Analog-to-Digital Converter: アナログ・デジタル変換器) は「天秤の原理」によりアナログ信号をデジタル信号に変換する回路である。そこでは通常2進重み付けされた「分銅」を用いるが、約1.6進であるフィボナッチ数列重み付けされた「分銅」を用いて高性能化できることを示した。(図1)

- [1] 小林春夫, 小林佑太朗「フィボナッチ数列と電子回路の話し」 群馬県和算研究会会報 第50号 (2016年3月)

- [2] Y. Kobayashi, H. Kobayashi, "Redundant SAR ADC Algorithm Based on Fibonacci Sequence", Key Engineering Materials, pp.117-126 (2016).

図1逐次比較近似 AD 変換器. (左)2 進重み付け. (右)フィボナッチ数列重み付け.

## (b) フィボナッチ数列重み付け DA 変換器:

多くの DA 変換器(Digital-to-Analog Converter: デジタル・アナログ変換器) は2進重み づけで構成されているが、フィボナッチ数列重み付け DA 変換器の構成を考案した。こ れは (a)のフィボナッチ数列重み付け逐次比較近似 AD 変換器内での使用に適している。 [3] T. Arafune, Y. Kobayashi, S. Shibuya, H. Kobayashi,

"Fibonacci Sequence Weighted SAR ADC Algorithm and its DAC Topology",

IEEE International Conference on ASIC, Chengdu, China (Nov. 2015)

#### (c) 白銀比重み付けを用いた冗長比較近似AD変換器:

同様に、白銀比(約1.42 進)重み付け逐次比較近似 AD 変換器の利点を明確化した。

[4] 小林佑太朗、荒船拓也、 澁谷将平、 小林春夫「擬似白銀比を用いた逐次比較近似 AD 変換 器冗長アルゴリズム設計」電気学会論文誌 (和文誌 C), vol. 137, no. 2, pp.222-228 (2017 年 2 月).

## (d) 多角数性質を用いたDA変換器:

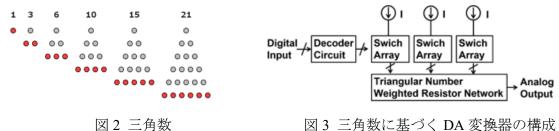

任意の自然数は三角数(1, 3, 6, 10, 15, 21,...(図 2))の 3 つ以下の和で表現することが できる。この性質を用いて3個の電流源と(筆者らが考案した)三角数抵抗ネットワー クで DA 変換器が構成できることを示した。(図3) さらにこれを任意の N 角数(多角 数) の場合に一般化した。

[5] Y. Du, X. Bai, M. Hirai, S. Yamamoto, A. Kuwana, H. Kobayashi, K. Kubo,

"Digital-to-Analog Converter Architectures Based on Polygonal and Prime Numbers",

17th International SOC Design Conference, Yeosu, Korea (Oct. 2020).

図3 三角数に基づく DA 変換器の構成

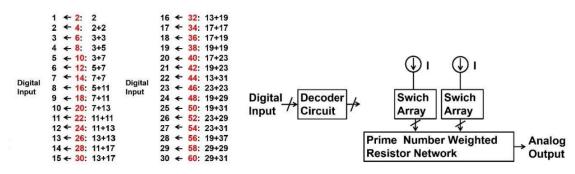

## (e) 素数の性質を用いた DA 変換器:

ゴールドバッファの予想:「任意の偶数は2個の素数の和で表すことができる。」(図4) この性質を利用して2個の電流源と(筆者らが考案した)素数抵抗ネットワークで DA 変換器が構成できることを示した。(図5)

[6] X. Bai, Y. Du, T. M. Tran, A. Kuwana, H. Kobayashi,

"Digital-to-Analog Converter Architectures Based on Goldbach Conjecture for Prime Numbers in Mixed-Signal ULSI", 30th International Workshop on Post-Binary ULSI Systems (May 2021).

図4 ゴールドバッファの予想

図5 素数の性質に基づくDA変換器

フェルマーの最終定理のように、整数論の定理は理解しやすいが証明は非常に難しいものが多い。しかしながら回路設計の立場からは「整数論の定理」(結果)を活用するのみで「証明」をおこなうわけではない。また全ての整数に対しては証明されていない「ゴールドバッハの予想」も、回路設計の立場からすれば使用する数 (例えば1024x1024=1048756)まで成立することを計算機シミュレーションでしらみつぶしに計算チェックすればその成果を利用できる。したがって、数学を専門としていない回路設計分野の者にも整数論の成果を十分活用できる。

### (f) N進数を用いたDA変換器:

N進数を用いたDA変換器の構成を考案し、従来の2進重み付け構成DA変換器より特性が良くなる可能性を示した。

[7] M. Hirai, H. Tanimoto, Y. Gendai, S. Yamamoto, A. Kuwana, H. Kobayashi, "Nonlinearity Analysis of Resistive Ladder-Based Current-Steering Digital-to-Analog Converter", International SOC Design Conference, Yeosu, Korea (Oct. 2020)

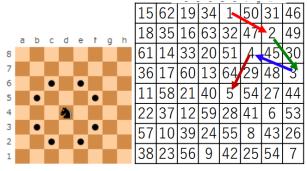

#### (g) 方陣を用いたDA変換器の単位セル選択アルゴリズムによる線形性向上技術:

- DA変換器の単位セル選択に魔方陣、ラテン方陣を用いるアルゴリズムを開発した。

- [8] 東野将史, 小林春夫「魔方陣レイアウトによる DA 変換器の直線性の改善」 和算ジャーナル 第 2 号 (会報通巻 52), (2018 年 3 月)

- [9] M. Higashino, S. N. B. Mohyar, Y. Dan, Y. Sun, A. Kuwana, H. Kobayashi, "Digital-to-Analog Converter Layout Technique and Unit Cell Sorting Algorithm for Linearity Improvement Based on Magic Square", Journal of Technology and Social Science, Vol.4, No.1, pp.22-35 (Jan. 2020).

- [10] D. Yao, Y. Sun, M. Higashino, S. N. Mohyar, T. Yanagida, T. Arafune, N. Tsukiji, H. Kobayashi, "DAC Linearity Improvement with Layout Technique using Magic and Latin Squares", IEEE International Symposium on Intelligent Signal Processing and Communication Systems, Xiamen, China (Nov. 2017)

さらにオイラー・ナイトツアー方陣 (ナイトツアー方陣と魔方陣の両方の性質をもつ) を用いるアルゴリズムを調べた。ナイトツアー(Knight tour)はチェスのKnight (八方桂馬) の動きを模したアルゴリズムである。

[11] D. Yao, A. Kuwana, H. Kobayashi, "Segmented-type DAC Unit Cell Selection Algorithm based on Euler's Knight Tour & Magic Square", 第11回 電気学会東京支部栃木・群馬支所合同研究発表会 オンライン開催 (2021年3月)

同じような研究がロシアのサンクトペテルブルク工科大学からナイトツアー方陣の使用が提案されている。しかしながら、サンクトペテルブルク市は数学者オイラーが長年滞在した都市であるにも関わらず、このグループからはまだオイラー・ナイトツアー方陣を調べた発表はないようである。(図6,7)

図6 チェスのナイトの動きとナイトツアー

図7 サンクトペテルブルク市

#### (h) Gray code入力による低グリッチDA変換器:

Gray code は米国ベル研究所のFrank Gray により1947年に特許出願された、2進符号とは異なるデジタル数値の符号化方式である。(図8) ロバストな符号であるのでAD変換器にはよく用いられている。しかしこの分野の大家の先生によればDA変換器には適用された事例はないとのことであった。そこで敢えて実現法をあれこれ検討してみた末に、構成を考案することができた。Gray code を用いるとDA変換器で入力切り替え時に出力アナログ信号に生じるスパイク上のノイズ(グリッチ)を低減できる。

| Decimal<br>numbers | Natural<br>Binary code | Gray code |

|--------------------|------------------------|-----------|

| 0                  | 0000                   | 0000      |

| 1                  | 0001                   | 0001      |

| 2                  | 0010                   | 0011      |

| 3                  | 0011                   | 0010      |

| 4                  | 0100                   | 0110      |

| 5                  | 0101                   | 0111      |

| 6                  | 0110                   | 0101      |

| 7                  | 0111                   | 0100      |

| 8                  | 1000                   | 1100      |

| 9                  | 1001                   | 1101      |

| 10                 | 1010                   | 1111      |

| 11                 | 1011                   | 1110      |

| 12                 | 1100                   | 1010      |

| 13                 | 1101                   | 1011      |

| 14                 | 1110                   | 1001      |

| 15                 | 1111                   | 1000      |

|                    |                        |           |

図8 Gray code: 前後に隣接する符号間のハミング距離が必ず 1

[12] R. Jiang, G. Adhikari, Y. Sun, D. Yao, R. Takahashi, Y. Ozawa, N. Tsukiji, H. Kobayashi, R. Shiota, "Gray-code Input DAC Architecture for Clean Signal Generation", IEEE International Symposium on Intelligent Signal Processing and Communication Systems, Xiamen, China (Nov. 2017).

### (i) Gray code, 剰余系を用いた時間デジタル変換器:

Gray code および剰余系を用いた時間デジタル変換器を開発した。従来のフラッシュ型時間デジタル変換器に比べて、性能は同等で回路規模・消費電力を激減できる。

- [13] C. Li, H. Kobayashi, "A Residue Number System Based Time-to-Digital Converter Architecture and its FPGA Implementation", Key Engineering Materials, pp.127-132 (2016)

- [14] C. Li, H. Kobayashi, "A Glitch-Free Time-to-Digital Converter Architecture Based on Gray Code", 電気学会論文誌(和文誌 C), vol. 136, no. 1, pp.22-27 (2016 年 1 月)

## (j) 剰余系を用いた髙周波波形サンプリング回路の開発:

波形サンプリングを行うと周波数領域で折り返しが生じる。これを剰余系と考え積極的 に利用し、高周波信号波形の周波数推定に用いる方式を考案した。

- [15] 阿部優大, 片山翔吾, 李 从兵, 小林春夫「孫子算経 (剰余系)の電子回路設計への応用」 第14回全国和算研究大会, 栃木県佐野市(2018年8月26日)

- [16] Y. Abe, S. Katayama, C. Li, A. Kuwana, H. Kobayashi, "Frequency Estimation Sampling Circuit Using Analog Hilbert Filter and Residue Number System", IEEE International Conference on ASIC, Chongqing, China (Oct. 2019)

#### (k) 高周波波形の黄金比等価時間サンプリングを用いた高効率波形取得方式:

AD変換器テストで正弦波入力周波数とサンプリングクロック周波数が黄金比にすると効率的に波形取得が可能であることを示した。これを黄金比サンプリングと名付けた。 [17] Y. Sasaki, Y. Zhao, A. Kuwana, H. Kobayashi, "Highly Efficient Waveform Acquisition Condition in Equivalent-Time Sampling System", IEEE Asian Test Symposium, Hefei, Anhui, China (Oct. 2018)

#### 3. 古典数学を用いた電子回路設計の学生教育への展開

群馬大学電子情報理工学科 学部 1 年生の講義にて電子工学と情報工学の融合分野としてこれらの「古典数学を用いた電子回路設計」の講義を専門課程の導入教育として 2020 年度まで 4 年間 毎年 90 分 x 4 回 行ってきた。フィボナッチ数列、黄金比、魔方陣、剰余系は学部 1 年生にもわかりやすい題材である。下記に講義資料を公開している。https://kobaweb.ei.st.gunma-u.ac.jp/analog-web/analogworkshop.html

孫子算経に剰余系が記されていると紹介すると、中国からの留学生から「小中学校で孫子算経を学んだが日本の大学に来て出てくるとは思わなかった」との感想があった。

#### 4. さらなる発展を目指して

この分野の一連の研究紹介の国際学会での下記の招待講演を行った。(図9)

[18] (Invited) H. Kobayashi, H. Lin, "Analog/Mixed-Signal Circuit Design Based on Mathematics", IEEE International Conference on Solid-State and Integrated Circuit Technology, Hangzhou, China (Oct. 2016)

講演後、聴衆のお一人から「あなたの話を気に入った。自分はシンガポールで半導体ビジネスをしているが、遊びに来い。蟹をごちそうする」と言っていただいた。

2014年に米国系半導体メーカー主催の講演会にて300人以上の聴衆のもと、下記講演を行ない、話を楽しんでもらえた。

[19] 小林春夫「温故知新:古典数学の掘り起しと AD/DA 変換器設計への応用」第 2 回アナログ・グルとの集い ~日本の電子産業を強くする技術とは~ 東京 (2014 年 12 月)

2021年10月の国際会議でも下記の招待講演を行う予定である。

[20] (Invited) H. Kobayashi, A. Kuwana, et. al., "Classical Mathematics and Analog/Mixed-Signal IC Design", IEEE International Conference on ASIC, Kunming, China (Oct. 2021)

またこれらの関連研究テーマにて、文部科学省科学研究費、群馬大学 ICT 教育・数理データ科学に関するプロジェクト研究に採択された。

集積回路分野は経済・産業に強く結びつき、近年この分野の学会では技術の面白さに加えて「どのくらい性能は上がったか、低消費電力化できたか、回路の小型化(低コスト化)できたか」という結果すなわち直近の実利を強く問われることが多い。(図 10)一方、数学では「何に役に立つのか」ということは問わずに「知的な面白さ・研究者の感性」に基づき研究を進めている印象を受ける。江戸の庶民は和算を囲碁・将棋のように楽しみで学んでいたと書物には記されている。数学の成果がのちに思いも知れないブレークスルーを生じることがしばしばあることは歴史が示している。両者の研究スタンスは対極をなす。筆者らは大学においては、集積回路設計研究に数学研究のスタンスを取り入れる必要があると考え、その一つとして「古典数学に基づく電子回路設計の研究」を行ってきている。少しずつこの分野の研究者に関心を持ってもらってきている。

**謝辞:**原稿を見ていただきました田部井勝稲先生に感謝します。

図9 中国での集積回路国際学会に研究室から大勢で参加

図 10 群馬大学で開発した AD 変換器