## 計測制御工学 第12回講義

# アナログ・電源・高周波回路での スペクトル拡散技術

小林春夫

群馬大学大学院理工学府 電子情報部門

[koba@gunma-u.ac.jp](mailto:koba@gunma-u.ac.jp)

下記から講義使用 pdfファイルをダウンロードしてください。

出席・講義感想もここから入力してください。

<https://kobaweb.ei.st.gunma-u.ac.jp/lecture/lecture.html>

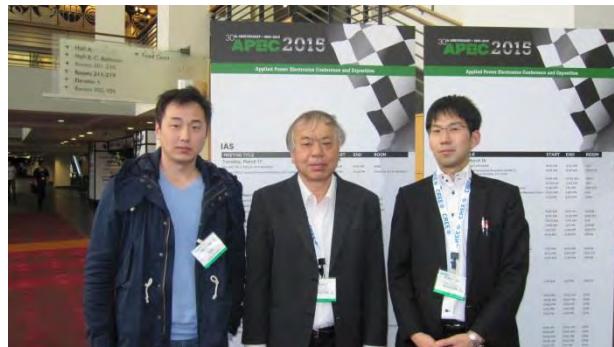

2015年3月23日

Applied Power Electronics Conference and Exposition

(APEC) 米国ノースカロライナ州シャーロット市

2015月15-19日に参加して

# 国際学会について思う

群馬大学 小林春夫

# 学会活動の意義

「学会活動は個人活動ではない。

企業と大学教育機関との連携の場を提供し、

企業の実力アップと技術力強化、

事業化推進に不可欠である。

国の産業の創造と発展、事業化拡大に貢献する。」

(萩原良昭氏 現 崇城大学教授

元 ISSCC プログラム委員長、ソニー、

群馬大学客員教授)

# 国際学会参加の意義

- 情報収集、情報発信

- 海外の研究機関・研究動向を知る

- 海外研究者との交流（人を知る）

- **逆説的：** 国内ではできない

日本の研究者との交流もしばしば経験

- **現地でこそ得られること多し**

- I can see what the eyes cannot see.

- I can hear what the ears cannot hear.

- I can feel what the heart cannot feel.

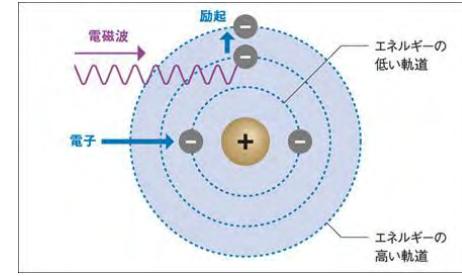

# 国際学会に参加すると “電子が励起状態”の如く

「アメリカ、ヨーロッパ、日本、韓国、中国、中東アジアの参加者しか見えませんでした。

東南アジアの参加者は全く見当たらなかったです。

特に Plenary sessionは本当にびっくりしました。Presentation sessionでは約500人以上の参加者になったと思います。

たくさん有名な人々、普段では論文の中でしか知らない名を生で見られたのは本当に嬉しかったです。たとえば、

Willy Sansen, Asad Abidi, Boris Murmann,

Richard Schreier など。」 マレーシアからの留学生

ニザム(Shaiful Nizam Mohyar)君 ISSCC2015に参加して

# 研究者・技術者の モチベーションの向上

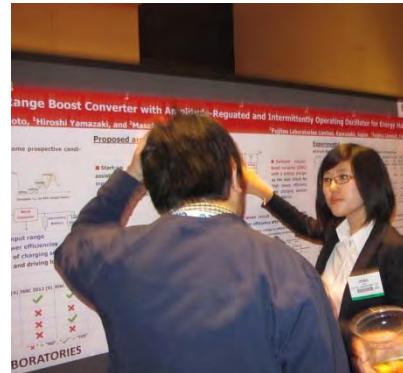

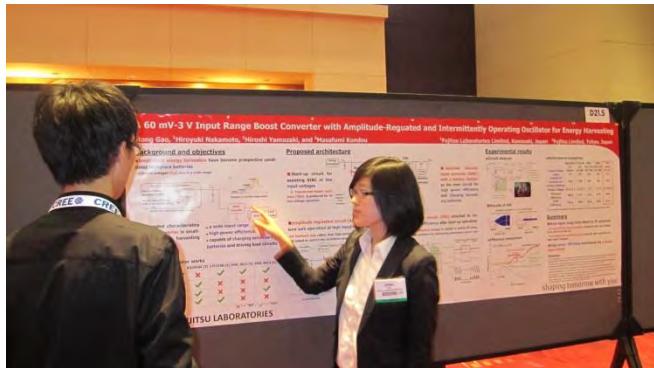

高虹さん(群馬大学 小林研 修士卒)

富士通研究所での研究成果でAPEC2015 でポスター発表

H. Gao, H. Nakamoto, H. Yamazaki, M. Kondou, " A 60mV-3V Input Range Boost Converter with Amplitude-Regulated and Intermittently Operating Oscillator for Energy Harvesting", APEC, Charlotte NC (Mar. 2015).

名門 コロンビア大学(米国ニューヨーク市)でもセミナー

(エポック社 陶山研様のアレンジに深謝)

# 論文発表による対外アピール

- 研究者個人として

- 研究機関として

- 企業が産学連携を行う一つの目的

大学は論文・学会発表を行う文化あり

→ 共著で発表を行い

企業の知名度を上げる

# 海外の国際会議で 「日本」を外から見る

- 研究分野で日本の強み、弱みを知る

APEC 2015 では SiC, GaN がホットな話題

たくさんのセッション、セミナー、多くの参加者

- 海外での研究機関、研究者を知る

デンマーク Aalborg 大学から非常に多くの発表

➡ パワエレ分野で9人の教授(3名はIEEE Fellow)

トロント大学から多くの印象に残る発表

- 世界の潮流を知る

外に出れば「グローバル化」の理解が深まる

# 米国での 産業に密接な国際会議では

「大学の先生が学会を立ち上げ・主導し

産業界に参加・協力を呼びかける」

のではなく

「その分野の産業・技術の振興のために必要」と戦略的グランドデザインを描き

产学が共同で国際学会・展示会を開催との印象をもつ

# 過剰な論文採択競争に注意

「今の学校教育では

数学は競争の道具になってしまっている。

数学には本来の面白さがあるのに

学校では それを十分に教えることが

できない状況になっている。」

(数学教師)

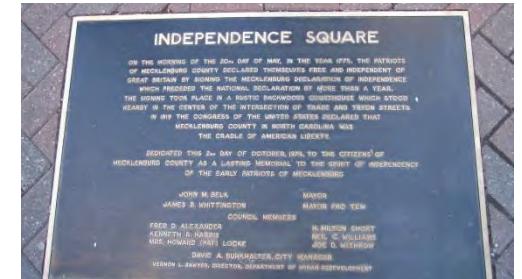

# 国際学会 開催地の地理、歴史を調べる

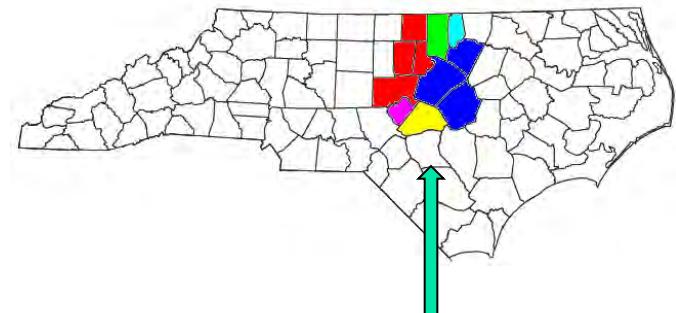

ノースカロライナ州：イギリスから独立したアメリカ合衆国

当初13州の一つ。南北戦争では南部連合側に最後に参入。

APEC2015開催地

Charlotte市

ノースカロライナ州

Research Triangle

現代ではシャーロット都市圏や、ローリー(ノースカロライナ州立大学)・

ダーラム(デューク大学)・チャペルヒル(ノースカロライナ大学)の

リサーチ・トライアングル地区を中心に経済的に大躍進を示し、

州人口も急速に伸びている。

# 技術・産業の過去と未来

10年前の国際会議での議論との比較

10年後の国際会議ではどのような議論か？

10年、20年後に「あの時、どの議論が正しく

どの議論は正しくなかったか、それはなぜか」

を振り返ることができる。

奢れば不孫なり、儉なれば固なり。不遜ならんよりは固なれ。

# 勉強には予算を使う、他は儉約

- APEC2015 に研究室から3名参加

- 日曜日のEducational Session から全て参加

- 儉約：郊外のモーテルに宿泊、電車で会場に通う

# 「静」の時間を持つ

日々の事に追われ考える時間が持てない

海外での国際学会に参加するときには

日本、職場からの情報を絶つ

ものを深く考える時間を持てる

学を絶てば憂いなし（老子）

# 学会がなければ

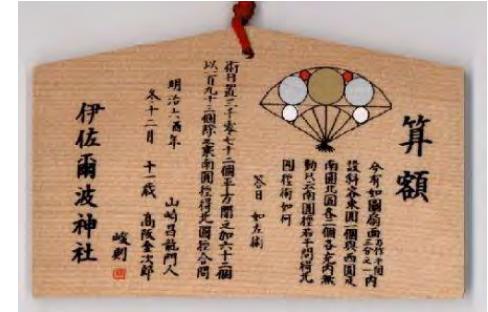

「和算は流派ごとに免許を発行し、

解法や秘伝を門外不出とし、

**国内を横断したアカデミーもなかつた。**

自然科学と孤立して発展、

科学に活用されにくい。芸の方向に発展。

明治の開国時、西洋の近代数学との

実用性の差は歴然。」 **白河一郎氏**

「和算はなぜ消えた」 IBM科学コラムより

# 学会(アカデミー)もしくじる

- ライプニッツ 1692年

全ての数を0と1で表す

驚くべき表記法を提案(2進数)

パリの王立アカデミーに理解されず

→ 20世紀になり、デジタル計算機の基礎理論

- Joseph Fourier upset the French academy in 1807.

フーリエ級数展開の理論は最初は認められず。

現在は工学にも広く用いられている。

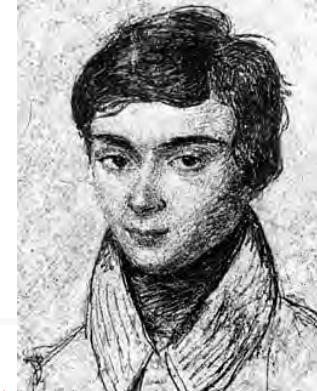

# 早熟の天才 ガロアの悲運

エヴァリスト・ガロア(1811-1832, フランス)

論文をフランス学士院に提出、コーシーが紛失。

再提出するも預かったフーリエが急死し紛失。

一人の女性をめぐり 決闘で敗れて死す(19才)

死後、その数学上の業績が認められる。

5次以上の方程式には

一般的な代数的解の公式は存在しない

2013年4月8日

# 新年度 講義の開始にあたり

2013年3月に米国出張で

出会った言葉

群馬大学 理工学研究院 電子情報部門

小林春夫

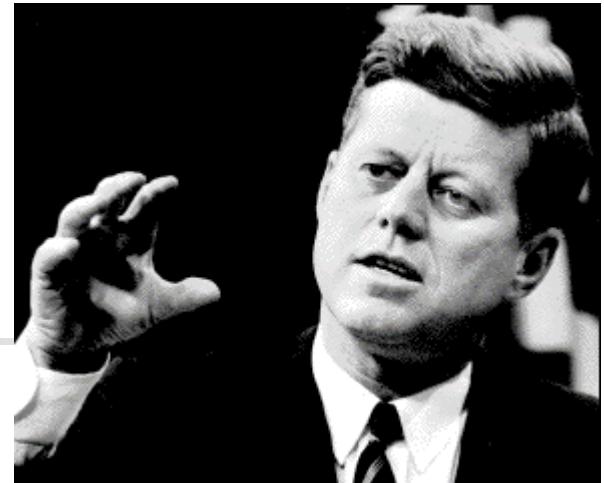

# John F. Kennedy

A man may die, nations may rise and fall,

but an idea lives on.

Ideas have endurance without death.

人は死に、国は興りそして滅びるかもしれない。

しかし、考え・思想は生き続ける。

ジョン・F・ケネディ 第35代大統領

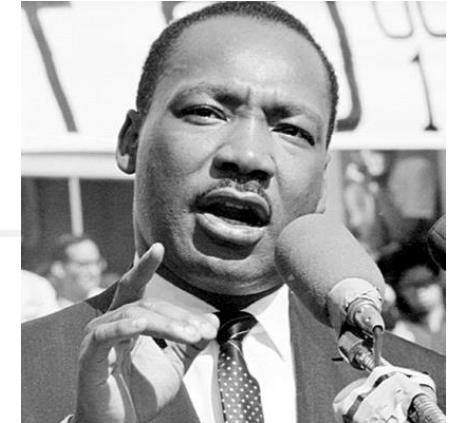

# Martin Luther King, Jr.

The ultimate measure of a man is

not where he stands in moments of

**comfort** and **convenience**,

but where he stands at times of

**challenge** and **controversy**.

人の真価は 順境ではなく

逆境にいるときに測られる。

キング牧師

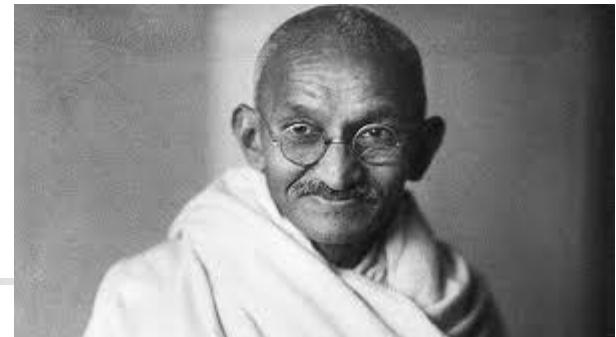

# Mahatma Gandhi

Live as if you were to die tomorrow.

Learn as if you were to live forever.

明日死んでも悔いないように 今日を生きよ。

未来永劫生きるつもりで必至で学べ。

マハトマ・ガンディー

# △ΣDA変調器のデジタルディザ信号による 性能改善と回路設計の検討

群馬大学

工学部 電気電子工学科 学部4年

小林研究室

小島潤也 新井薰子 小林春夫

# アウトライン

---

- 研究背景・目的

- 提案回路の構成

- シミュレーション構成・結果

- FPGA実装

- まとめ

# アウトライン

---

- 研究背景・目的

- 提案回路の構成

- シミュレーション構成・結果

- FPGA実装

- まとめ

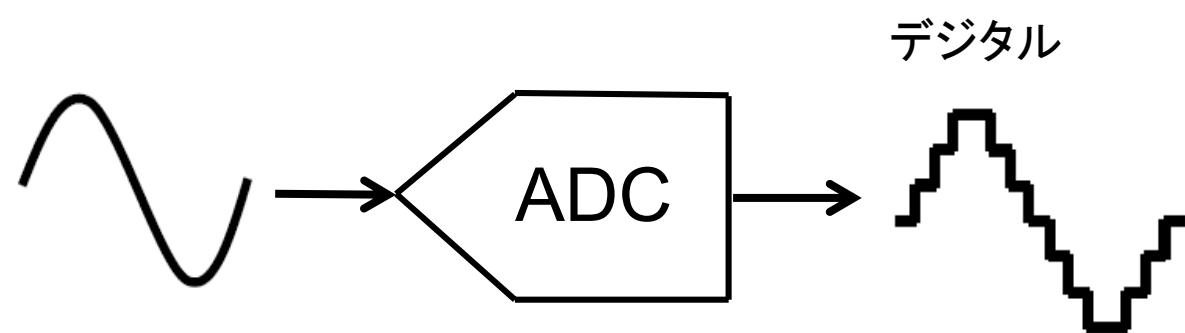

# 研究背景

集積回路の信号処理

デジタル回路に恩恵

〔 アナログ・デジタル変換器 (ADC)

デジタル・アナログ変換器 (DAC) 〕

高性能を要求

アナログ：連続的な信号

- ・自然界の信号(音、光)

・アナログ時計

など

デジタル：離散的な数値の信号

- ・2進数

・デジタル時計

など

# 研究目的

直流信号、低周波信号に対して

簡単な回路構成

高分解能、高線形で出力できる

デジタル・アナログ変換器(DAC)を開発

△ΣDA変換器に注目

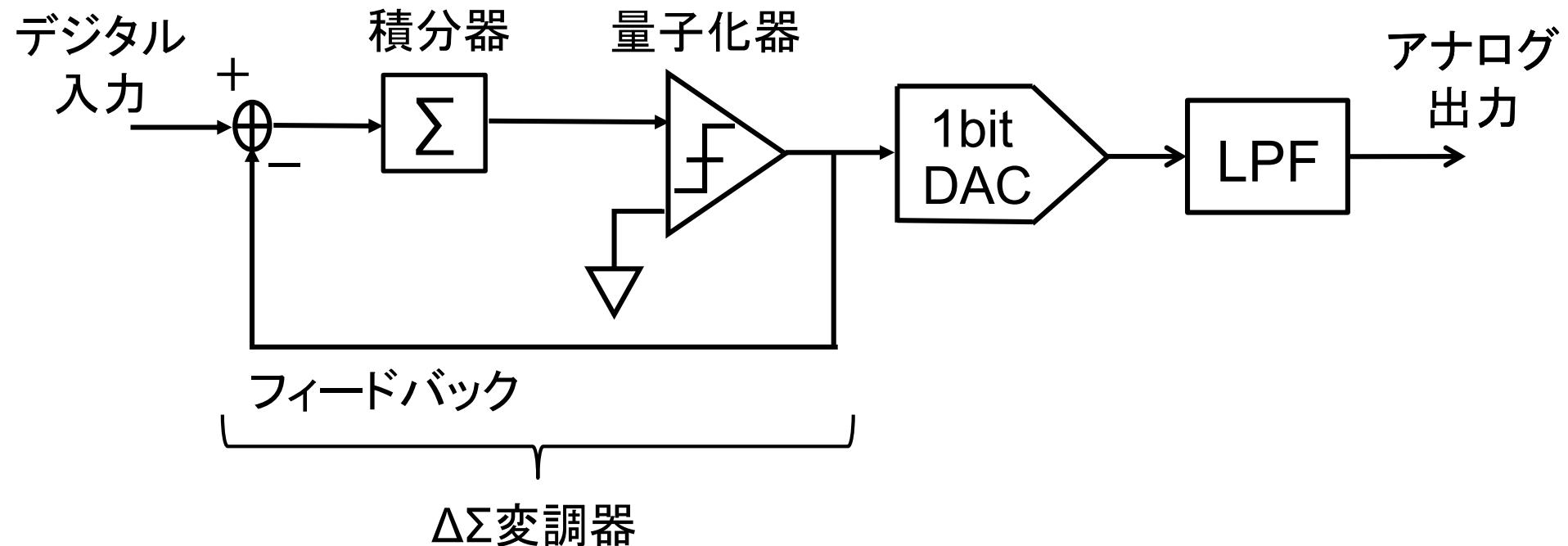

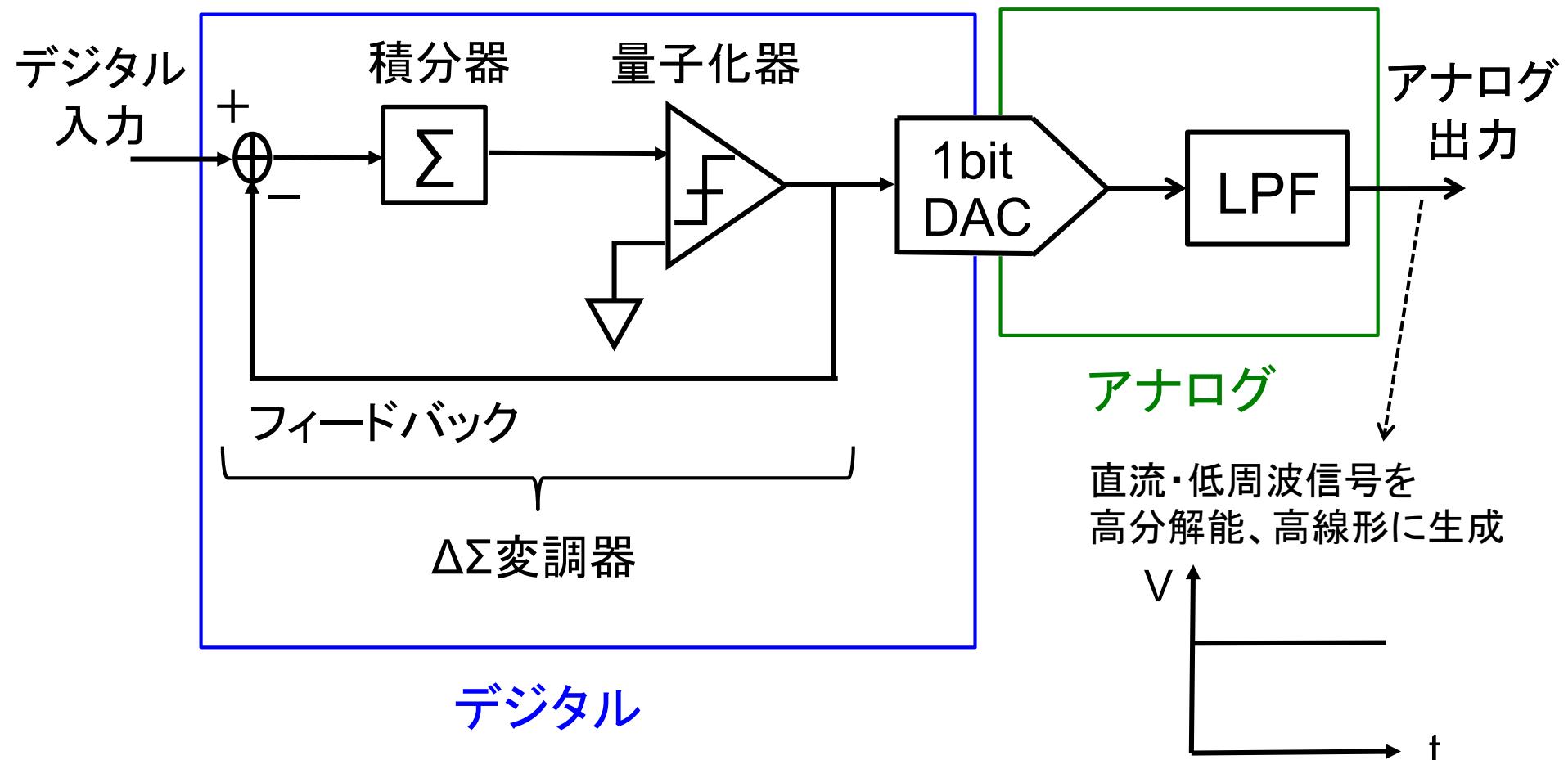

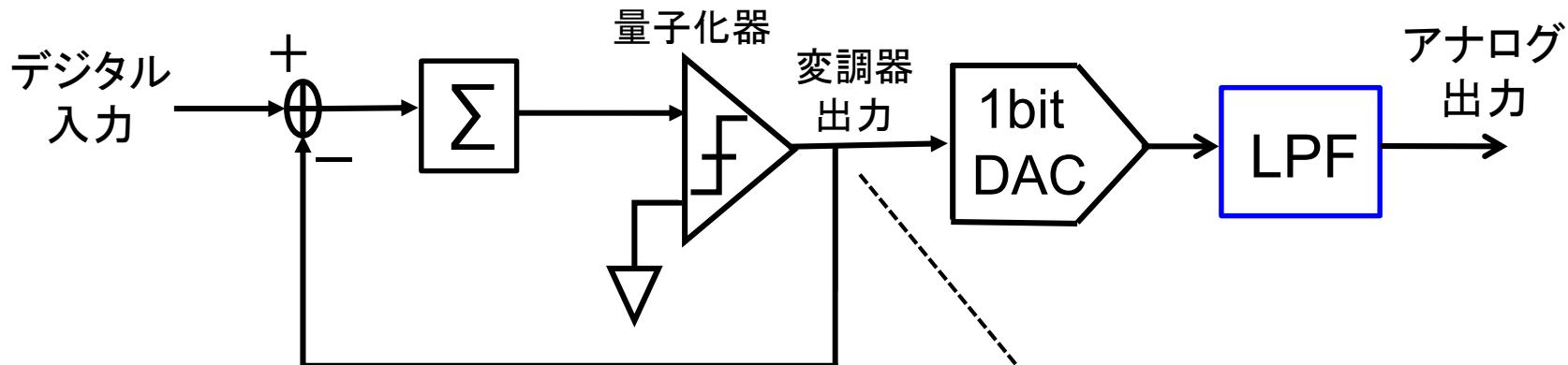

# $\Delta\Sigma$ DA変換器の構成

# $\Delta\Sigma$ DA変換器の構成

\* ナイキストDAC  $\Rightarrow$  [10bit以上

高線形性] の回路設計は難しい…

- ・電子計測器

- ・LSI試験装置等に使用

# $\Delta\Sigma$ DA変換器の特徴

## メリット

- 大部分はデジタル回路

- わずかなアナログ回路

- 高分解能

- 高線形性

高精度

外部からのノイズに 強

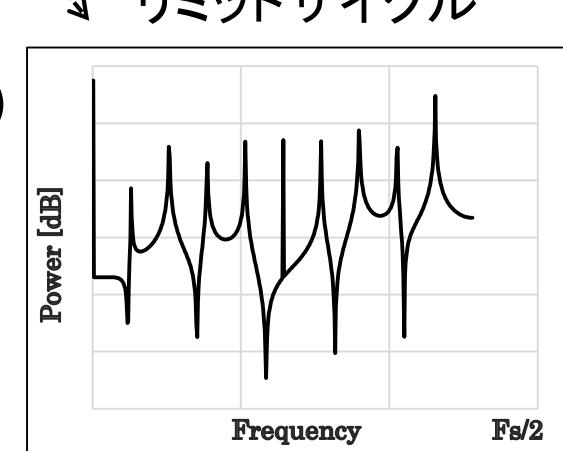

## デメリット

- 微小信号では変調器出力に

入力信号成分にない周期信号成分が出力

(リミットサイクル)

※量子化器による非線形性が原因

# $\Delta\Sigma$ DA変換器の特徴

アナログをLPFで急峻に落とす… 困難

$$\text{出力} = \text{信号成分} + \frac{\text{リミットサイクル}}{\text{(ノイズ成分)}}$$

目的

・リミットサイクルを低減させ高性能に

・LPFの性能要求を緩和

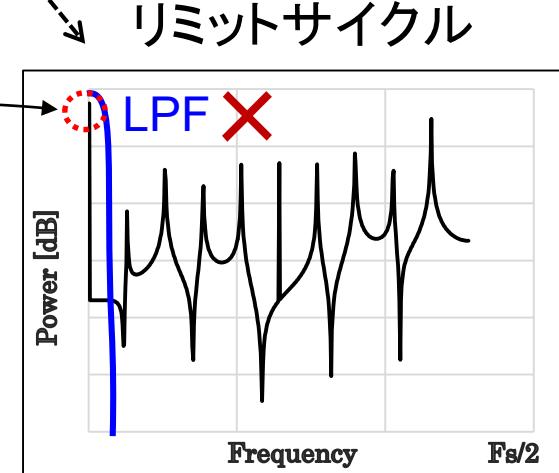

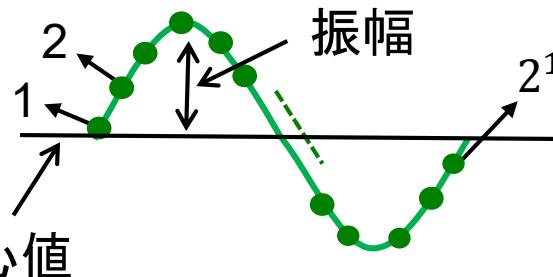

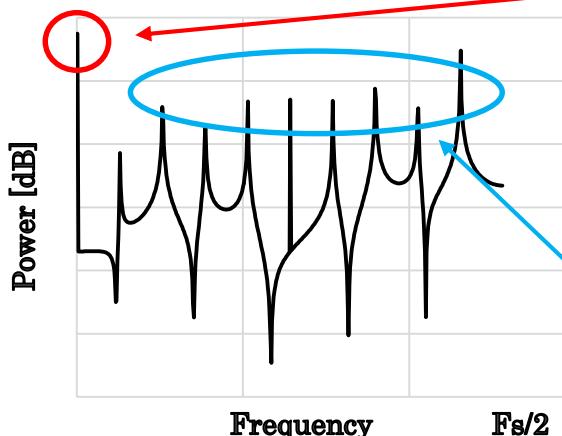

# 提案手法のイメージ

# 提案手法のイメージ

<イメージ図>

リミットサイクル

階段状

なめらかに！

# アウトライン

---

- 研究背景・目的

- 提案回路の構成

- シミュレーション構成・結果

- FPGA実装

- まとめ

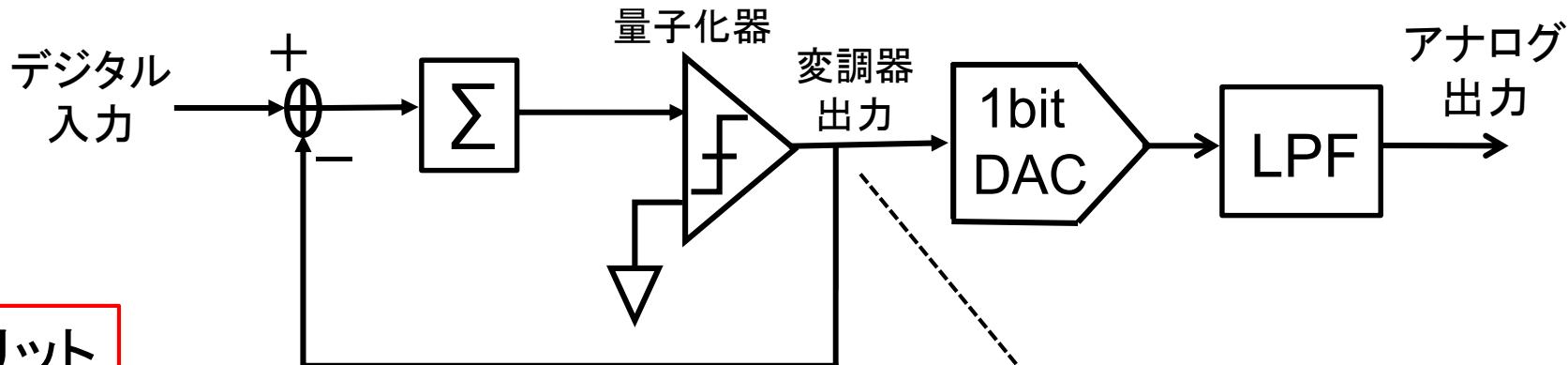

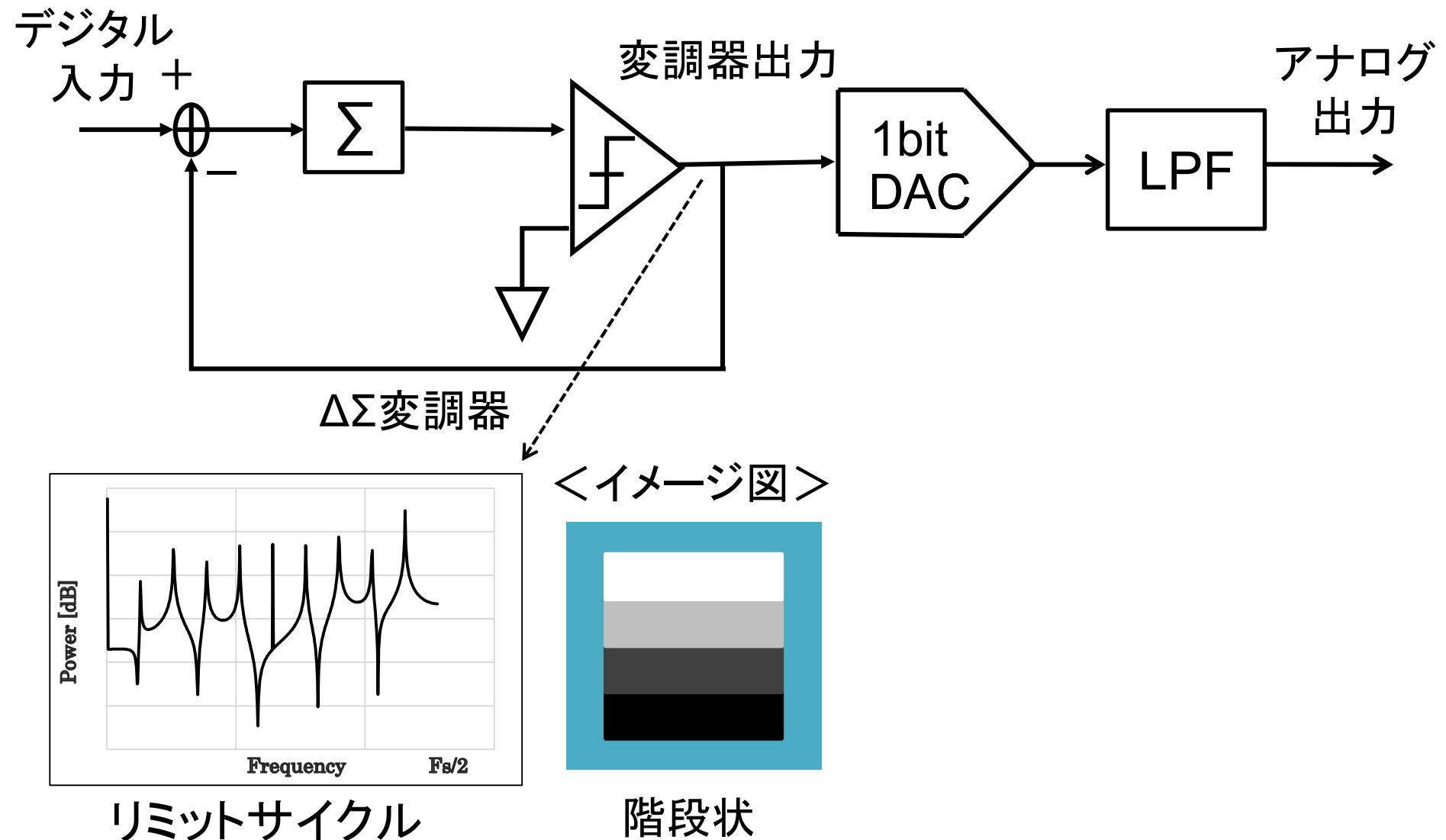

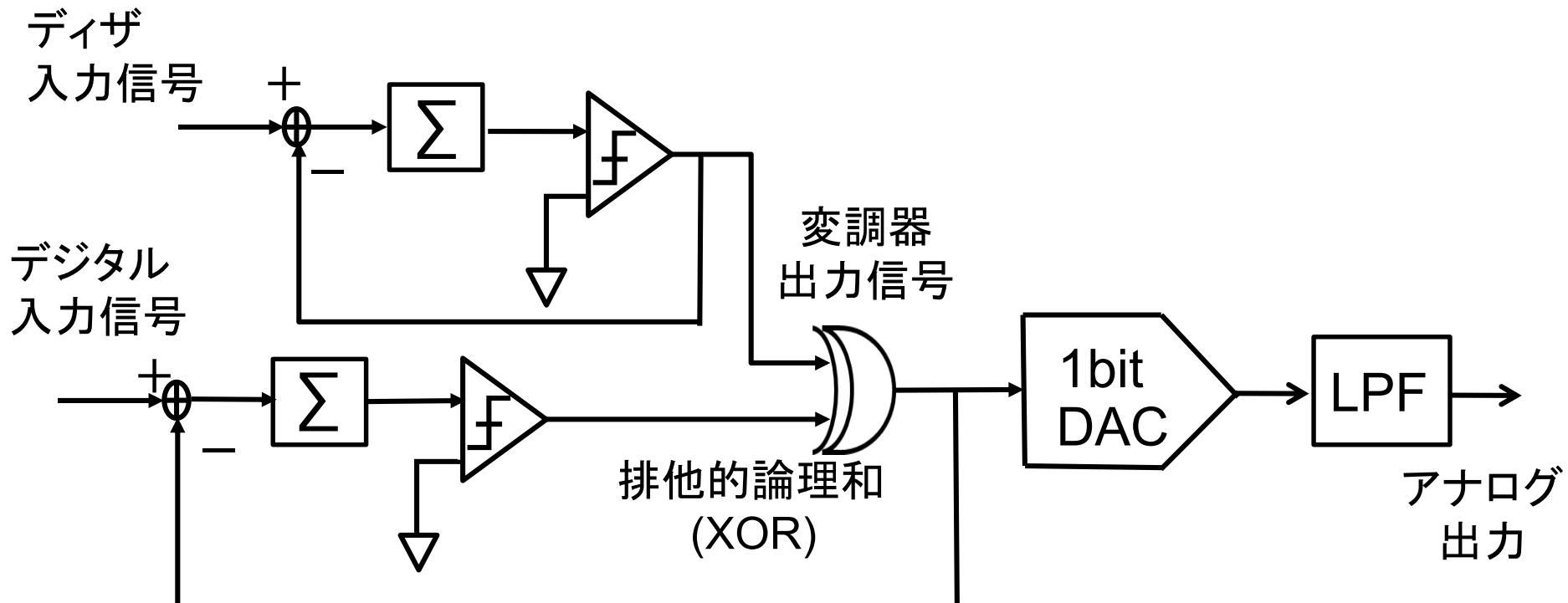

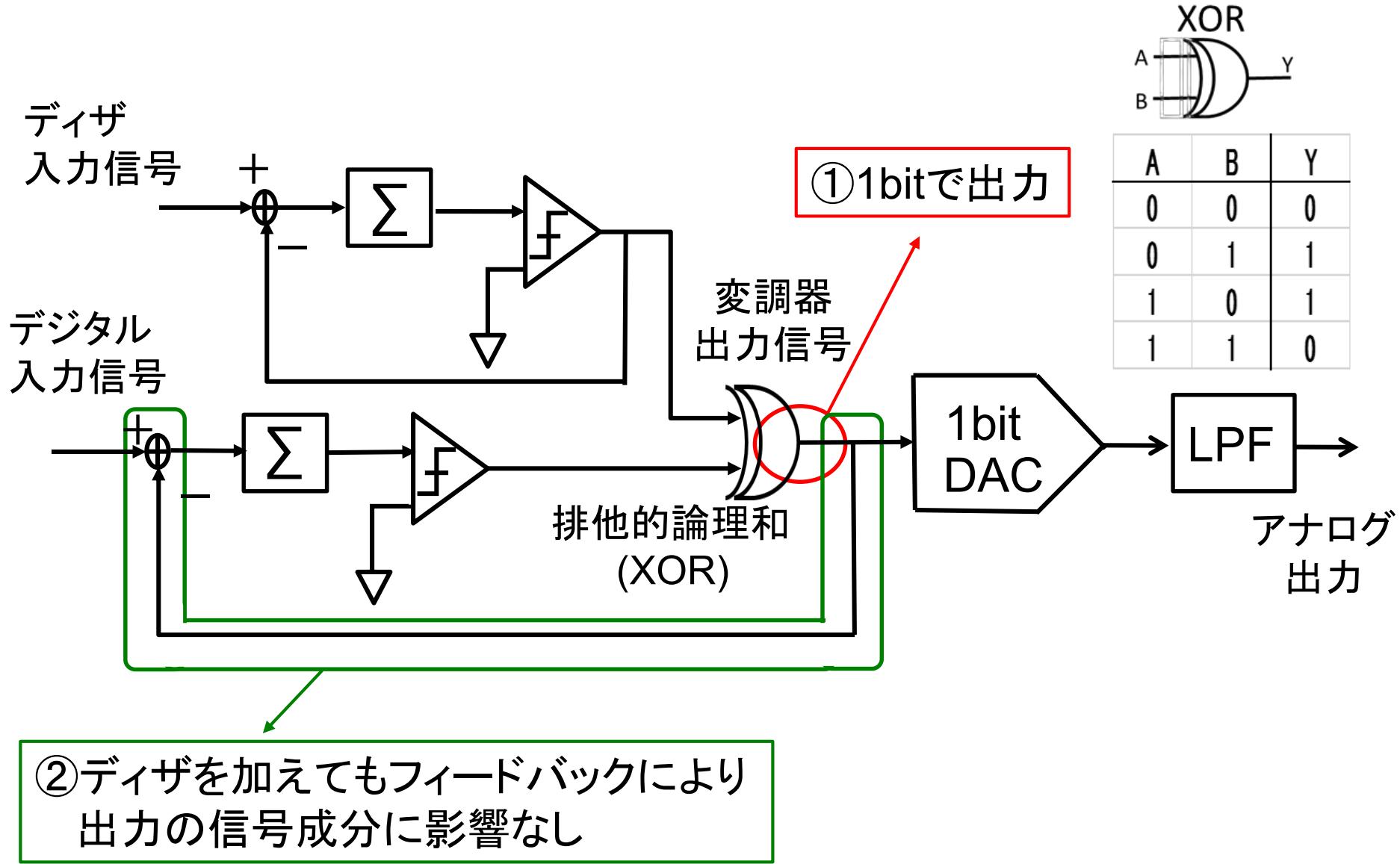

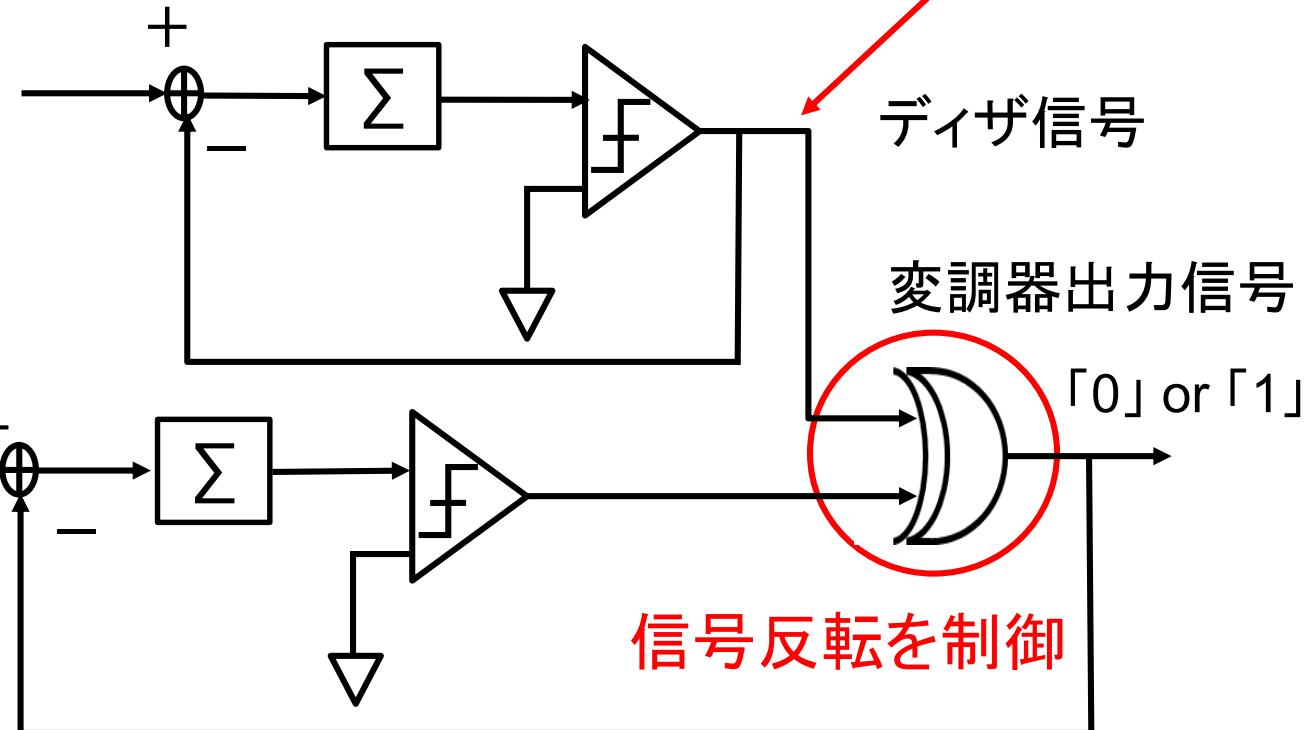

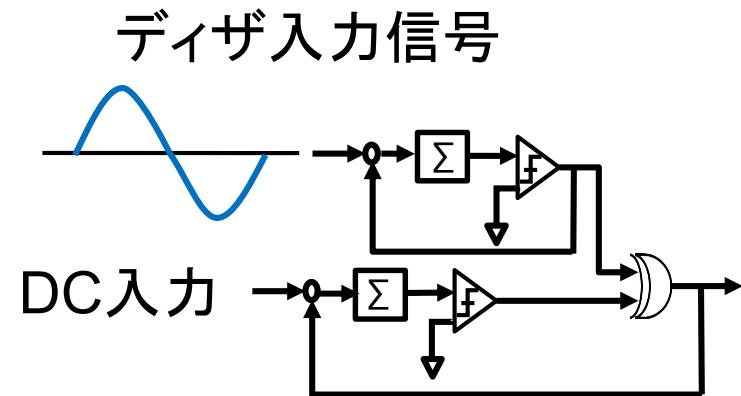

# 提案回路の構成

# 提案回路の構成

# 提案回路の構成

デイザ

入力信号

デジタル

入力信号

②ディザを加えてもフィードバックにより

出力の信号成分に影響なし

①1bitで出力

|   |   | Y |

|---|---|---|

|   |   | 0 |

|   |   | 1 |

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

1bit

DAC

LPF

アナログ

出力

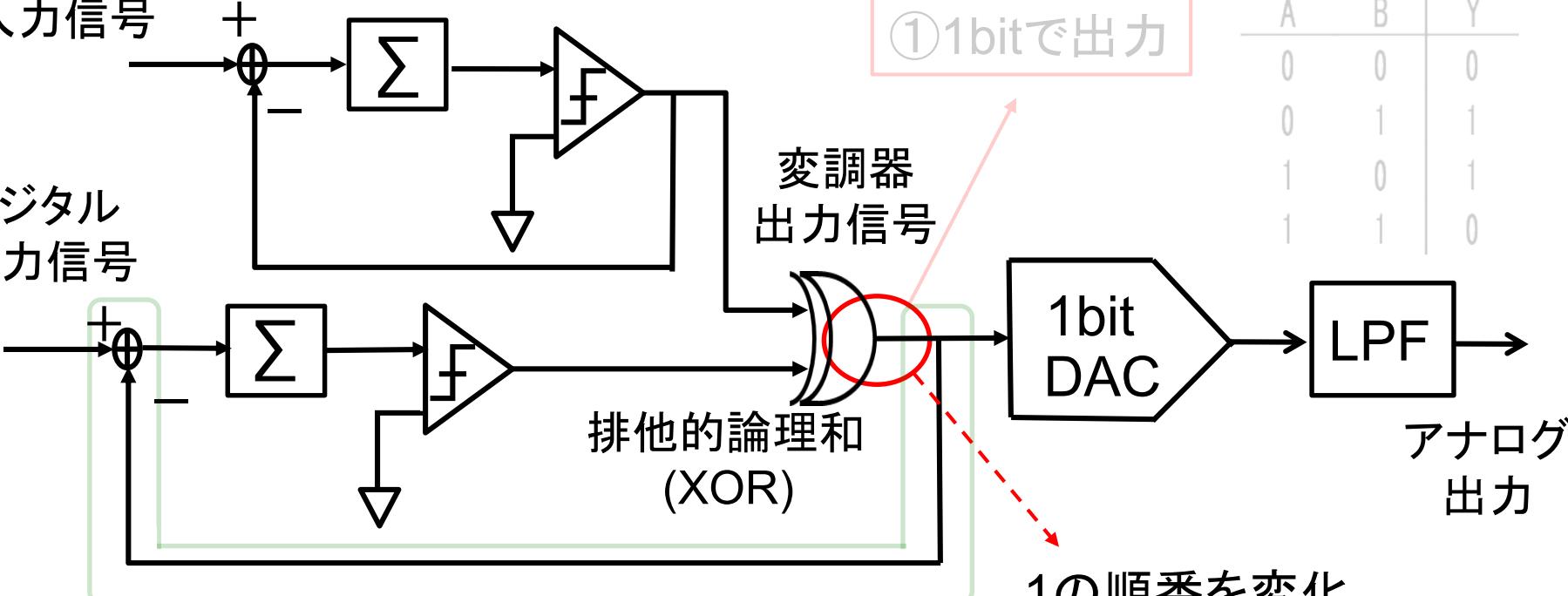

1の順番を変化

リミットサイクル低減

今までにない新しい方法

# アウトライン

---

- 研究背景・目的

- 提案回路の構成

- シミュレーション構成・結果

- FPGA実装

- まとめ

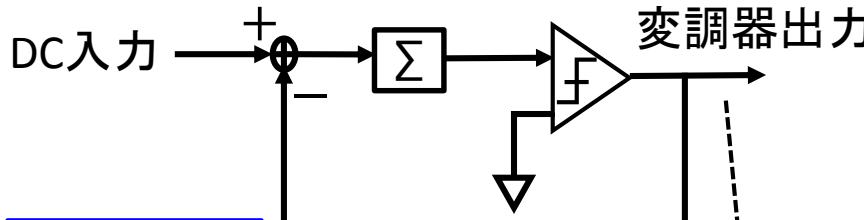

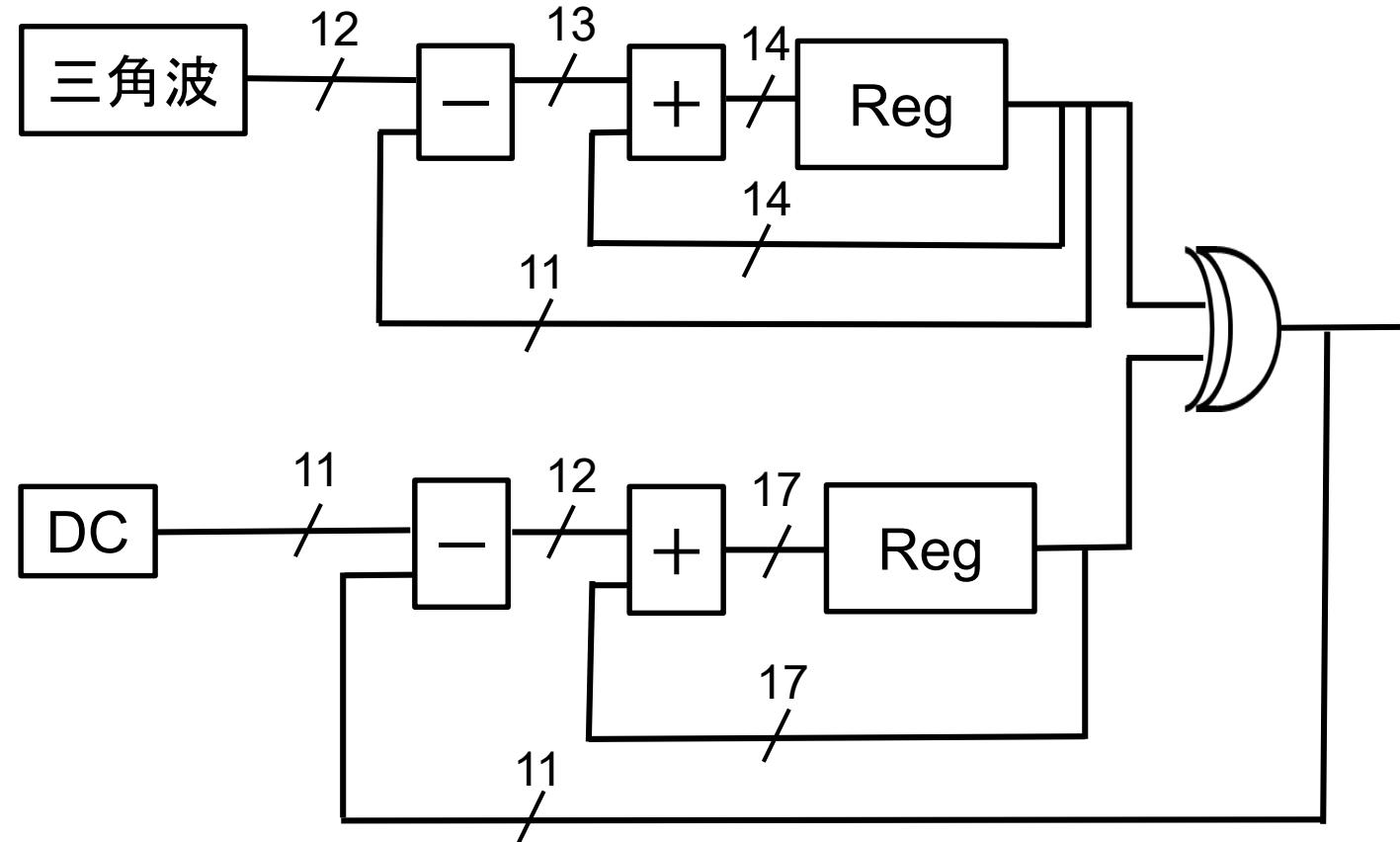

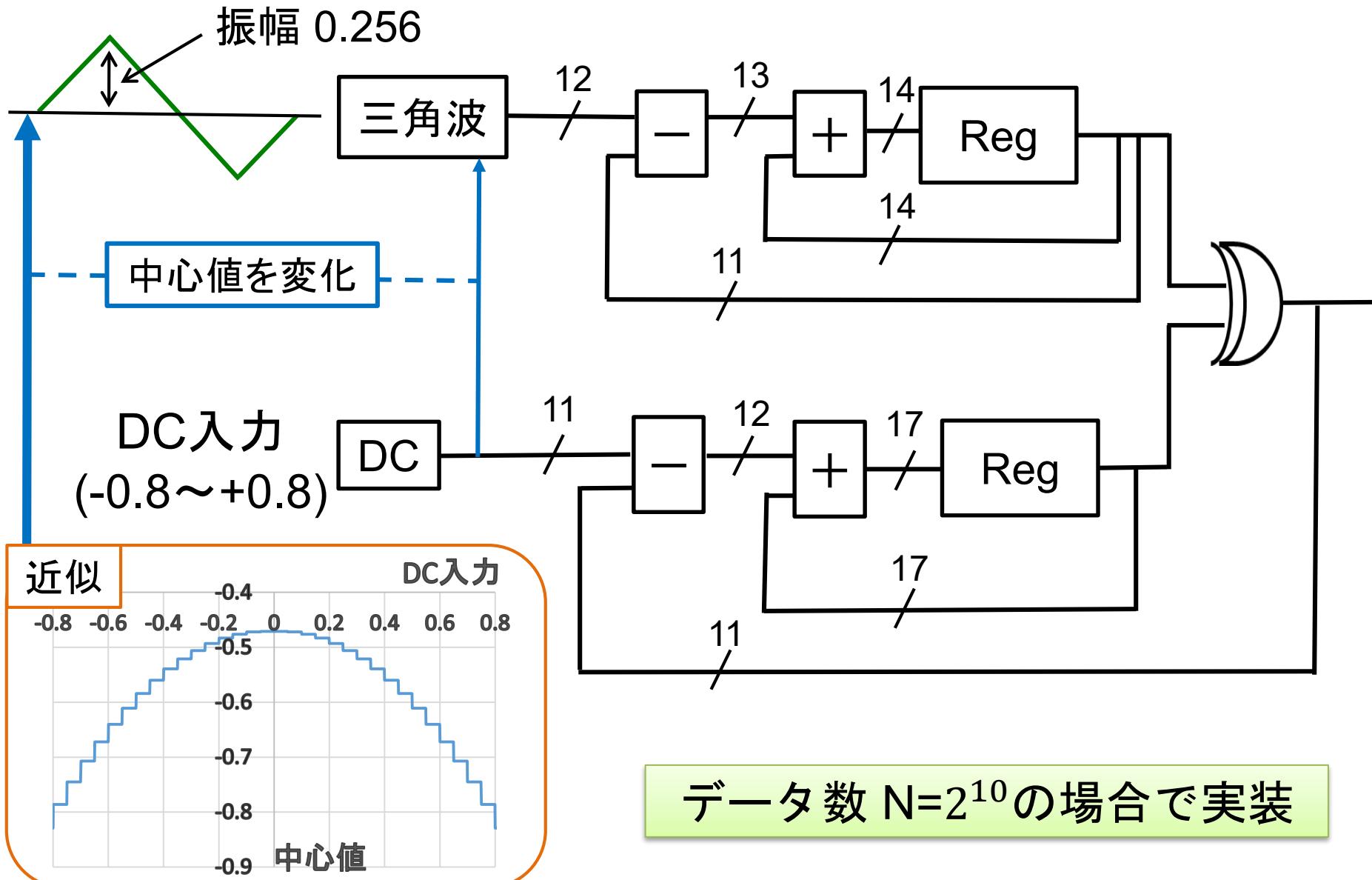

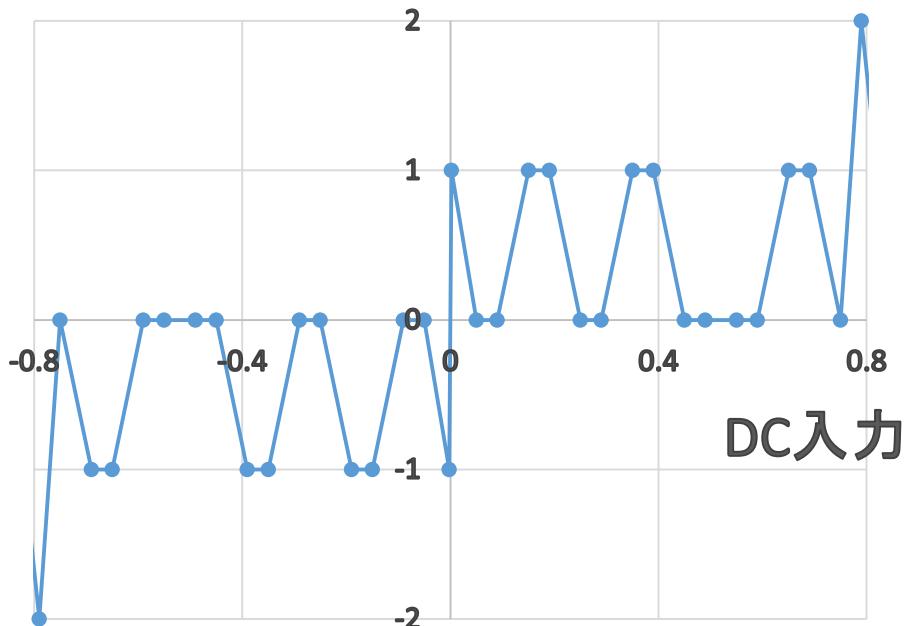

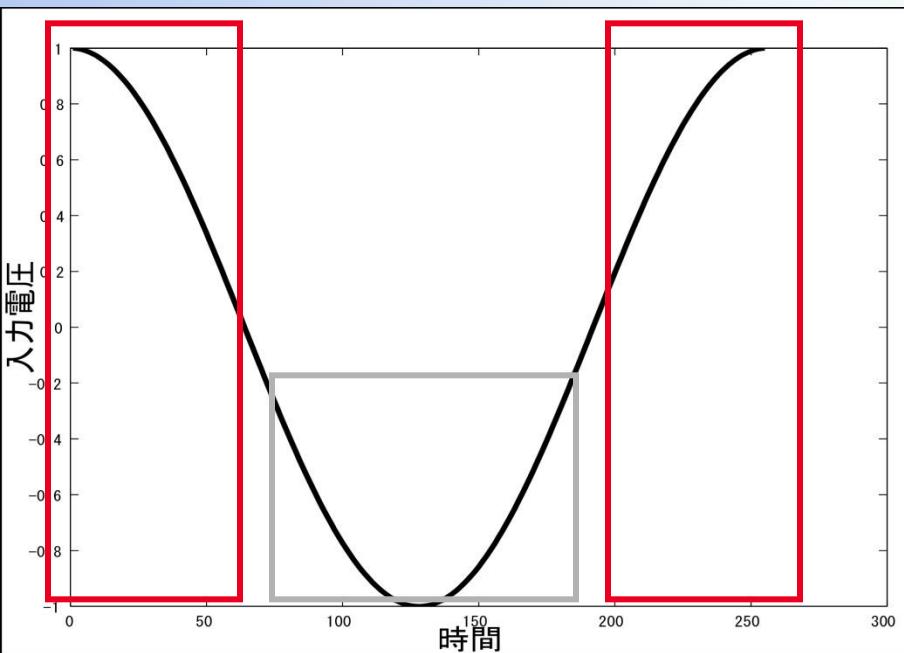

# シミュレーション構成

◆ データ数:  $N=2^{10}$

正弦波

出力される「1」の数を等しく

リミットサイクルが低減

振幅・中心値を変化させ「1」の数を制御

デイザ入力信号

デジタル入力信号

DC: -1~1

$N=2^{10}$

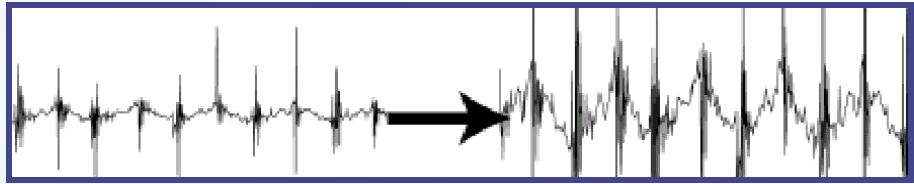

# シミュレーション構成

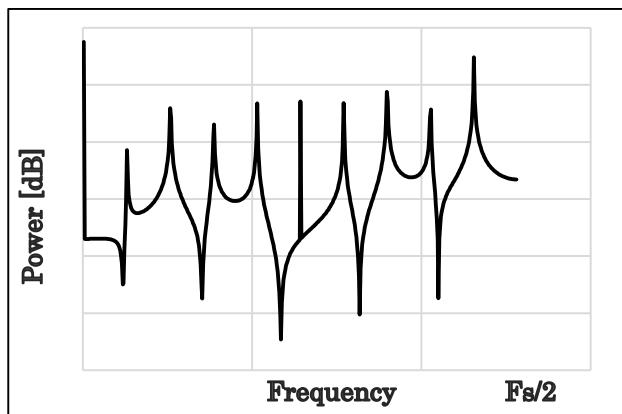

- ・ ディザ信号なし

時間領域

1 0 0 0 1 0 0 0 1 0 0 0 1 0 0 0

周期的

- ・ ディザ信号あり

1 0 0 0 0 1 0 1 0 0 0 0 0 1 0 0

非周期的

- ✓ 「0」と「1」の順番が異なる

- ✓ 全体の「1」の数は同じ

周波数領域

信号電力は同じ

線形性あり

ノイズ成分

拡散

$$N=2^{10}$$

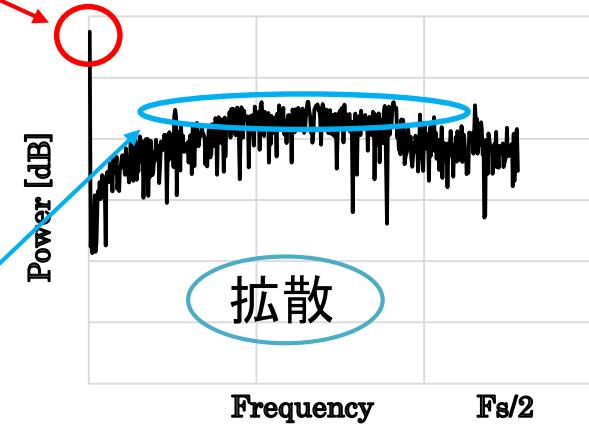

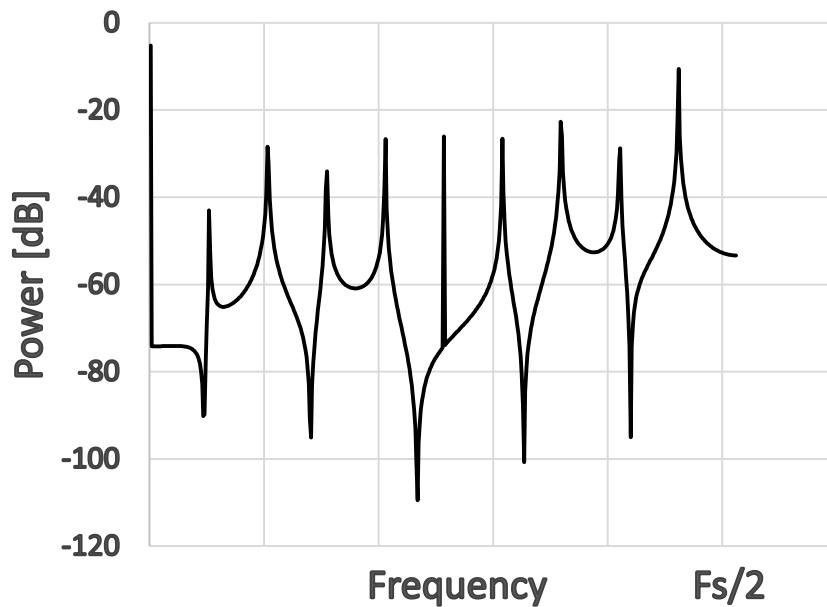

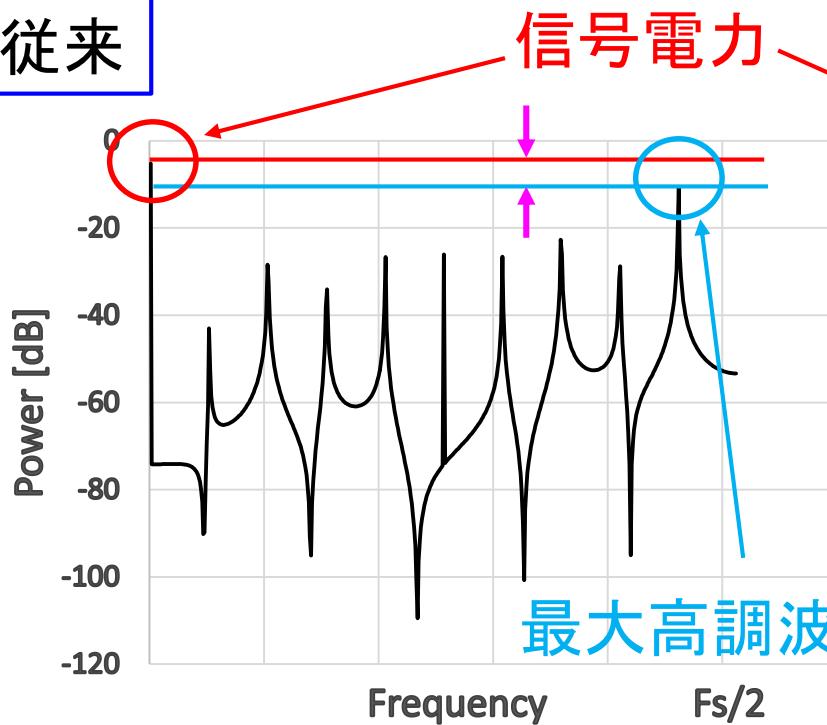

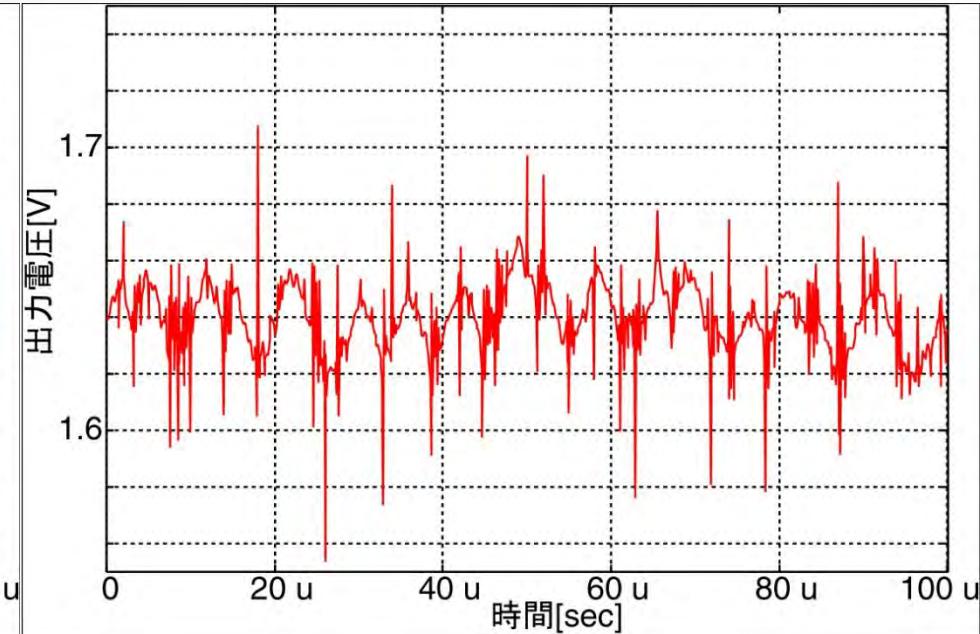

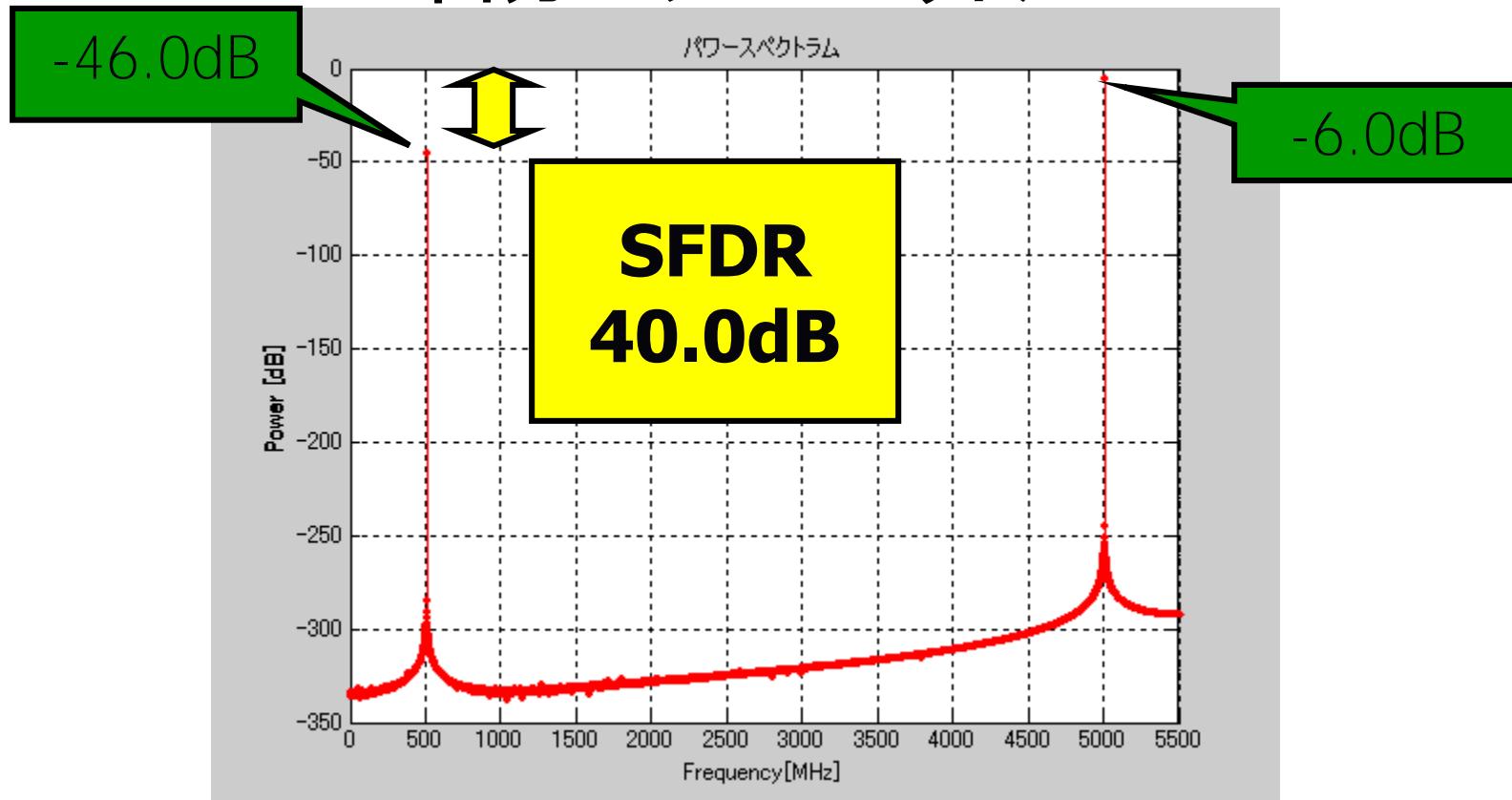

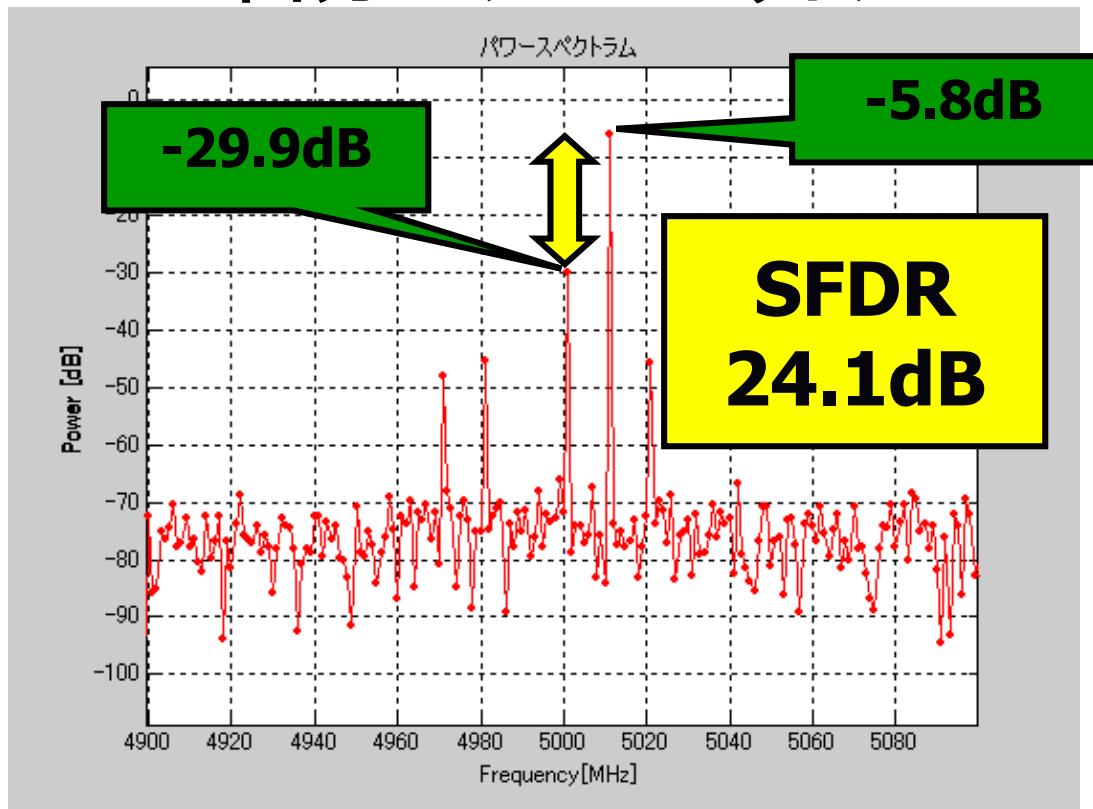

## シミュレーション結果

正弦波

中心值:-0.520

**DC = 0.1**

振幅:0.094

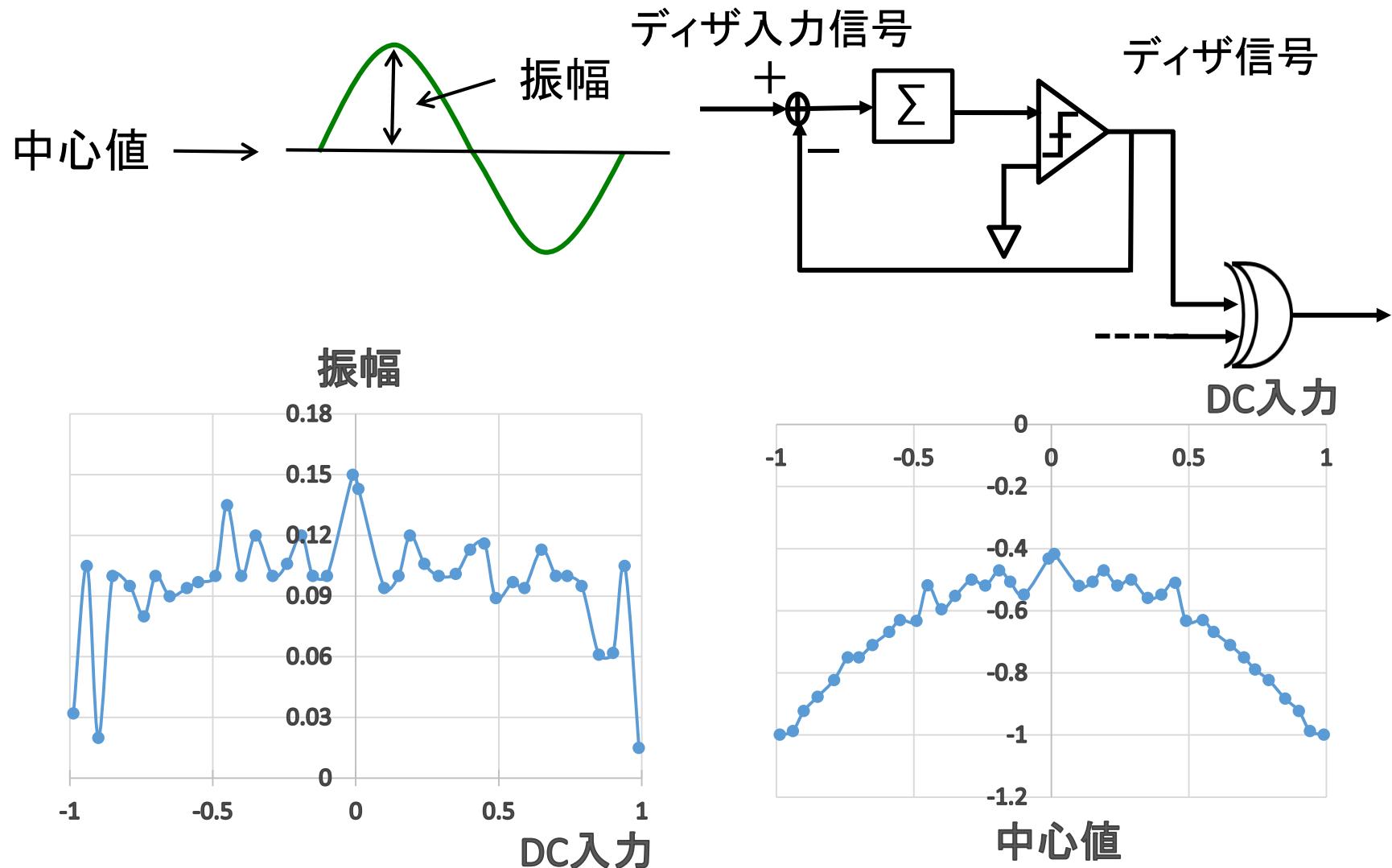

# 從來

## 提案

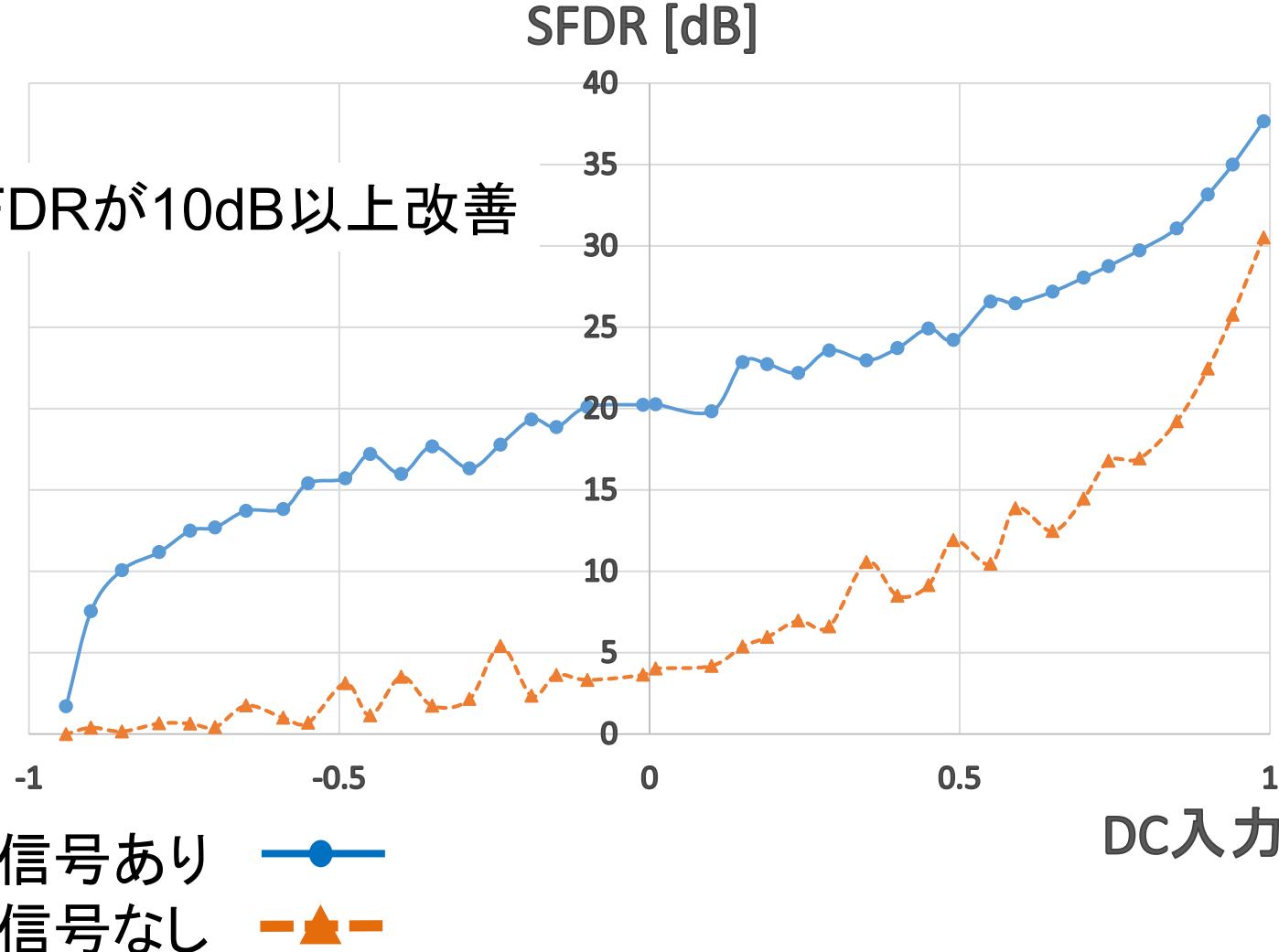

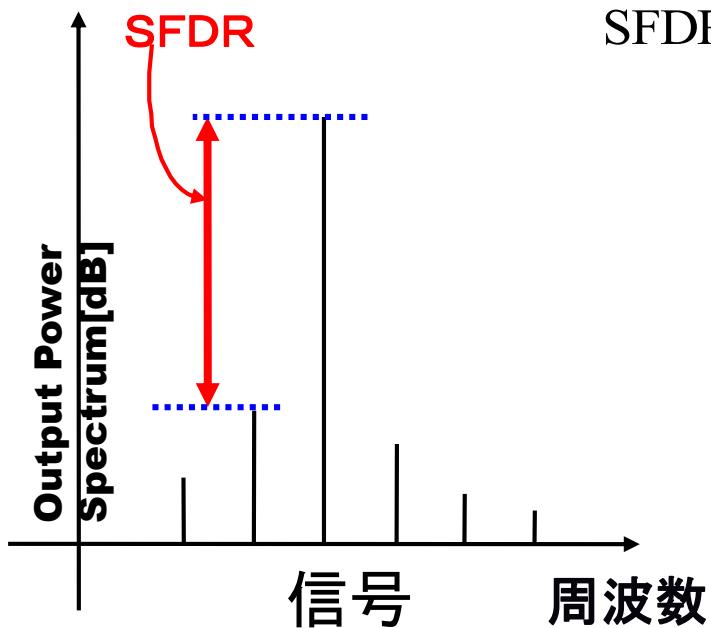

# SFDR(Spurious Free Dynamic Range)

- 評価法:  $SFDR = \frac{\text{信号電力}}{\text{最大高調波電力}}$

$$SFDR = 5.4 \text{ dB} < 22.9 \text{ dB}$$

従来

提案

$N=2^{10}$

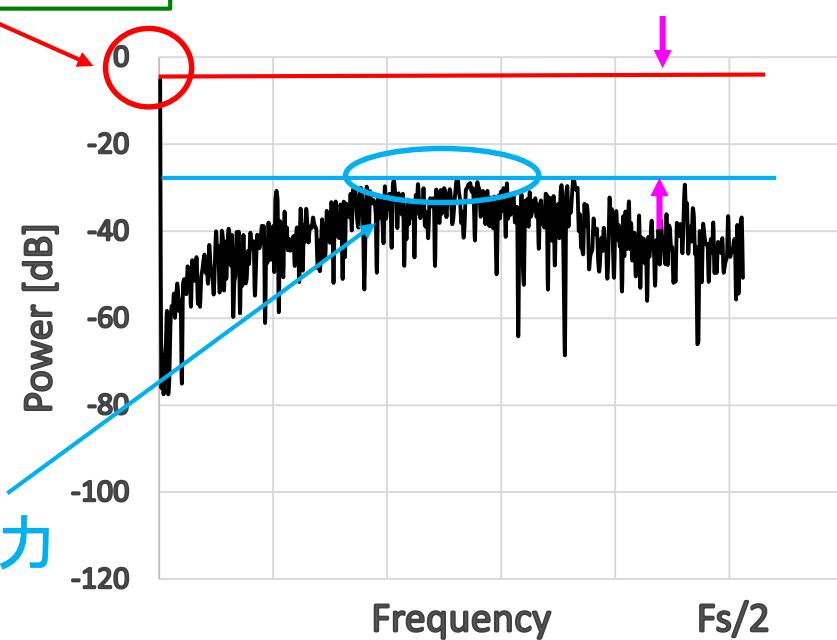

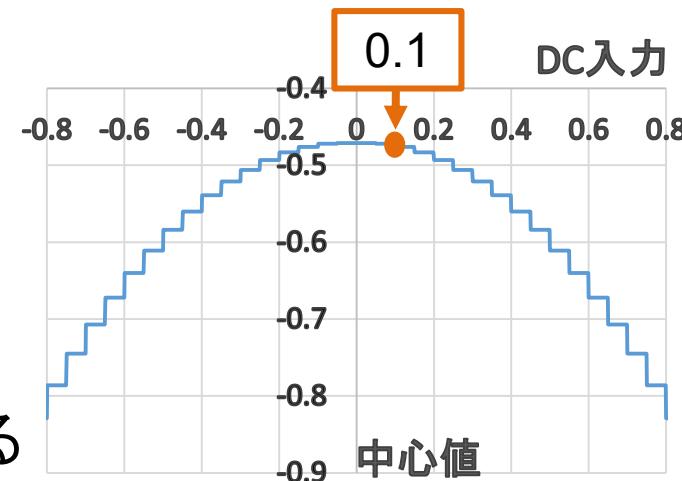

# ディザ信号

- ◆ 最大高調波電力が小さくなる正弦波の振幅・中心値

N=2<sup>10</sup>

# SFDRの比較

SFDRが10dB以上改善

# アウトライン

---

- 研究背景・目的

- 提案回路の構成

- シミュレーション構成・結果

- **FPGA実装**

- まとめ

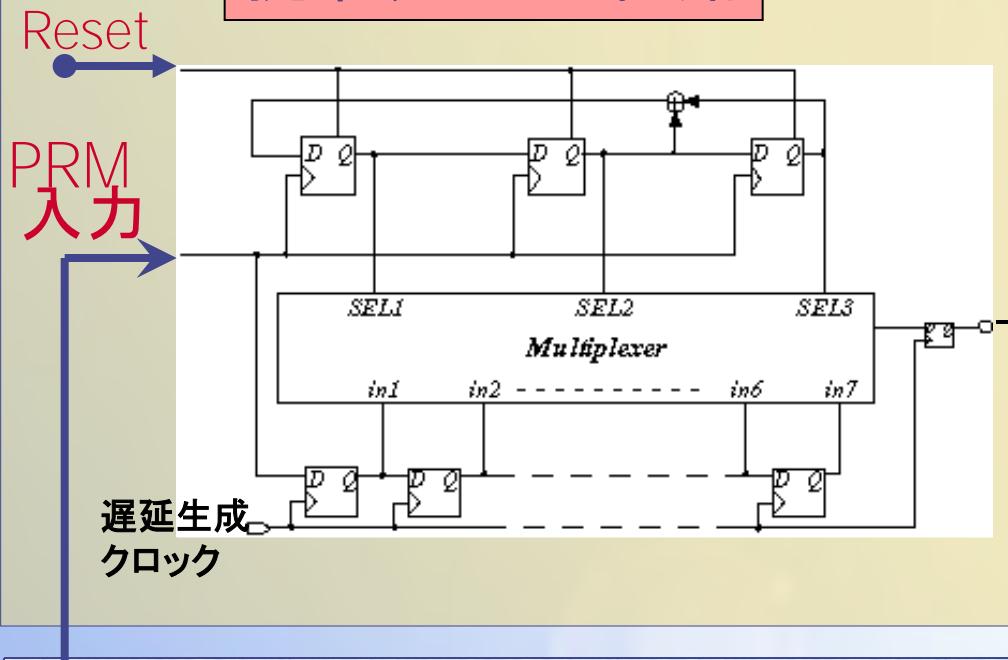

# デジタル回路への道

## デジタル回路実現のために

- ◆ ディザ入力信号で

使用する正弦波の発生

- ◆ DC入力に対して正弦波の

振幅、中心値を毎回変更

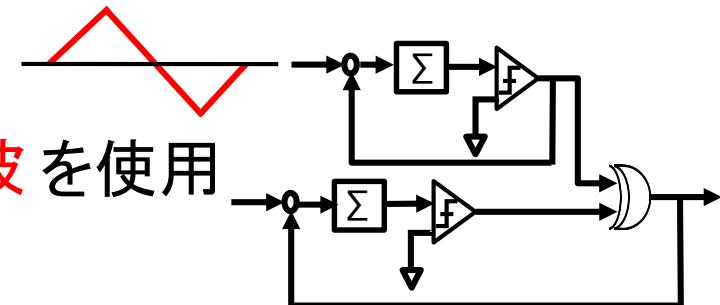

# デジタル回路への道

## デジタル回路実現のために

- ◆ ディザ入力信号で使用する正弦波の発生

- ◆ DC入力に対して正弦波の振幅、中心値を毎回変更

### ＜変更点＞

◆ 三角波を使用

◆ 振幅 : 0.256 と一定

中心値: 近似を使用(p.21)

中心値を自動的に決定

Let's Go !

(ex) DC=0.1 のとき

$$\begin{cases} \text{振幅} = 0.256 \\ \text{中心値} = -0.476 \end{cases}$$

DC入力のみを変化させる

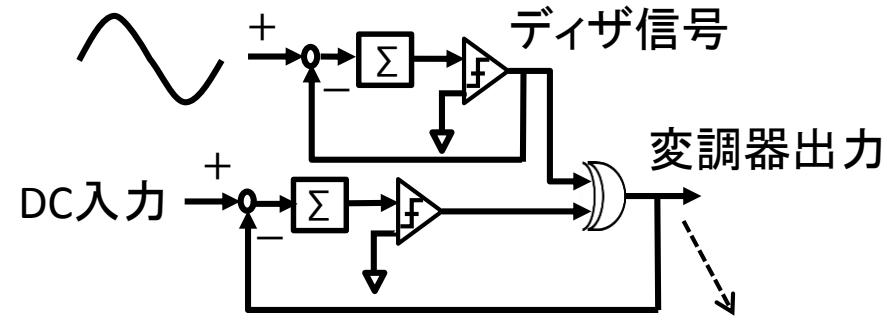

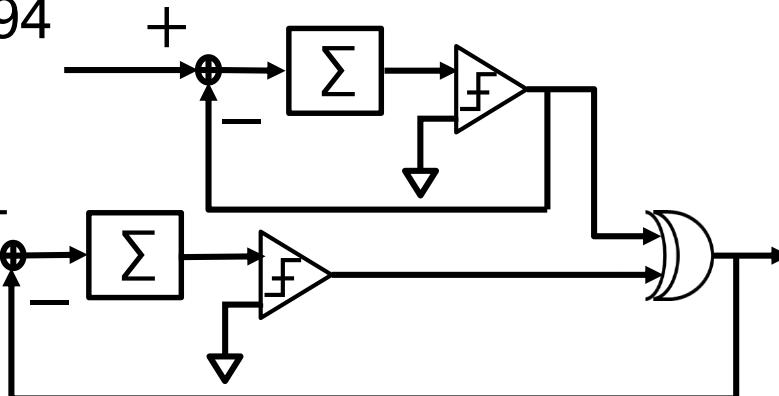

# デジタル回路(提案回路)

# デジタル回路(提案回路)

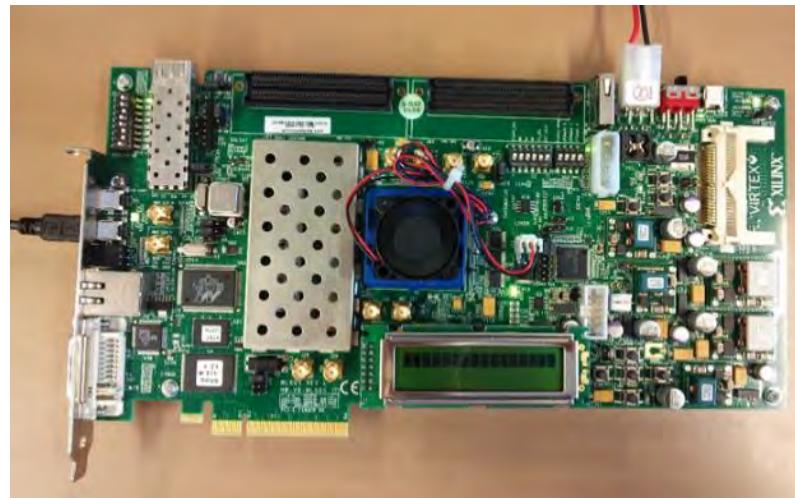

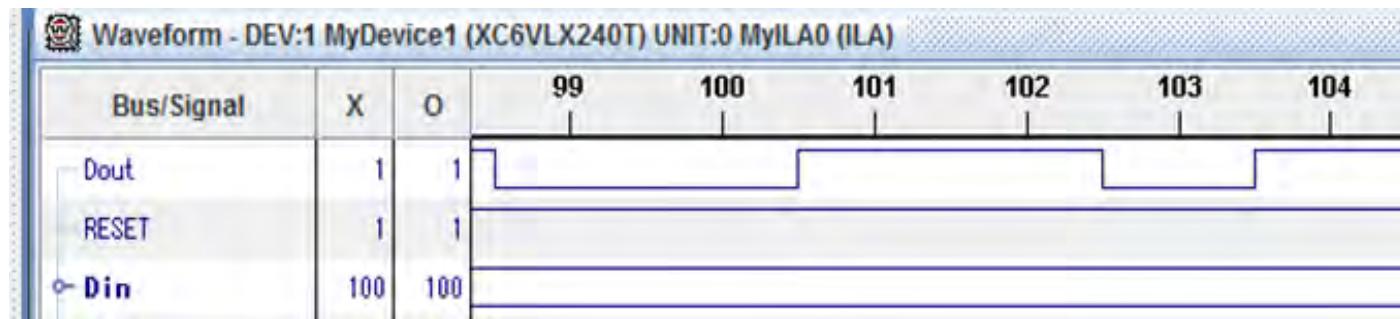

# FPGAのボードと出力波形

Xilinx

Virtex-6 ML605

FPGAのボード

(周波数 50MHz)

出力波形の一部

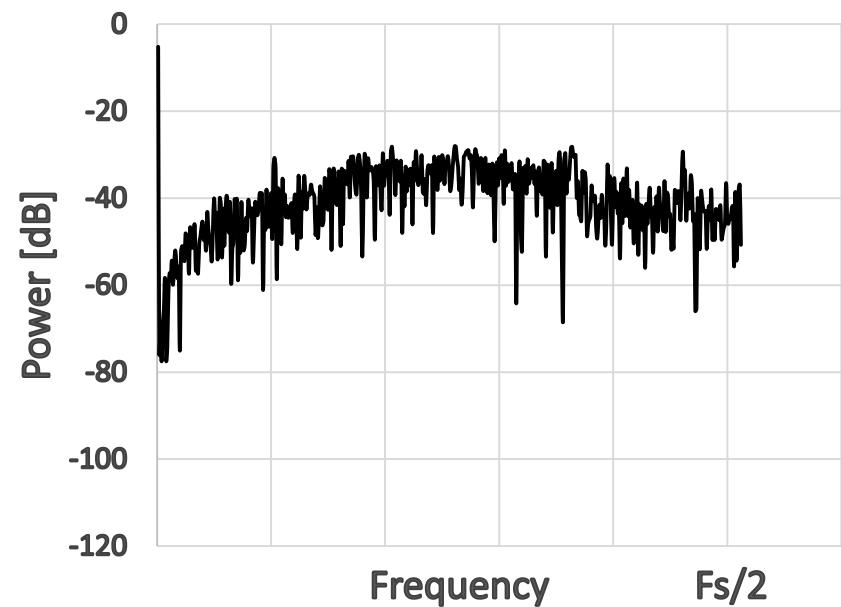

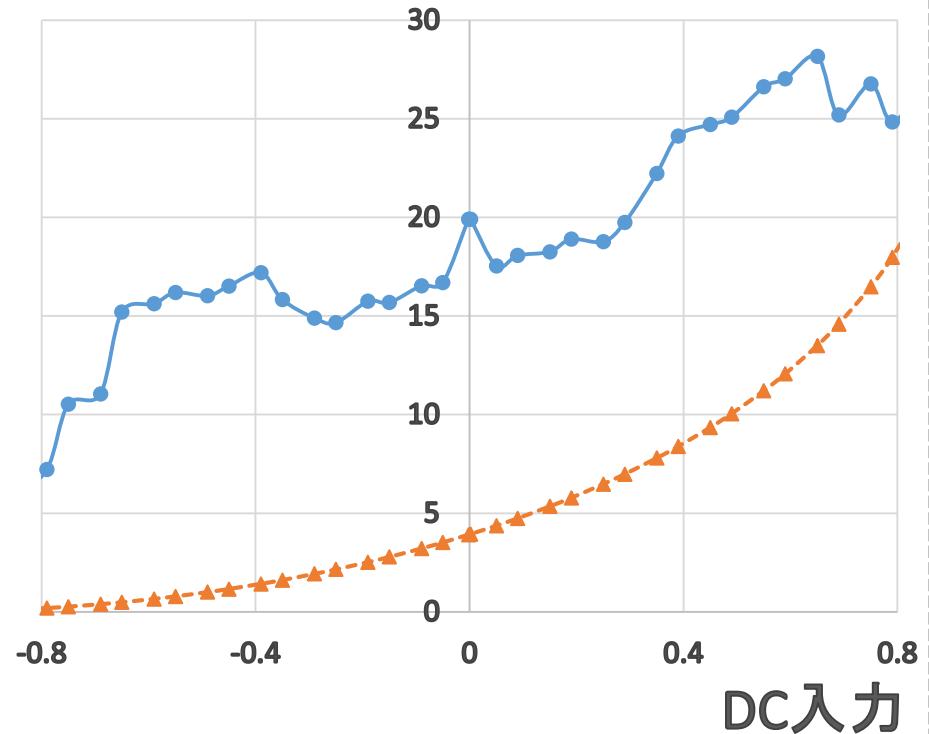

# FPGAの結果

SFDR [dB]

ディザ信号あり    ●

ディザ信号なし    ▲

😊 SFDRが10dB以上改善

従来と提案の「1」の数の差

「1」の数の差は

±2の範囲に収まった

➡ 😊 線形性あり

# アウトライン

---

- 研究背景・目的

- 提案回路の構成

- シミュレーション構成・結果

- FPGA実装

- まとめ

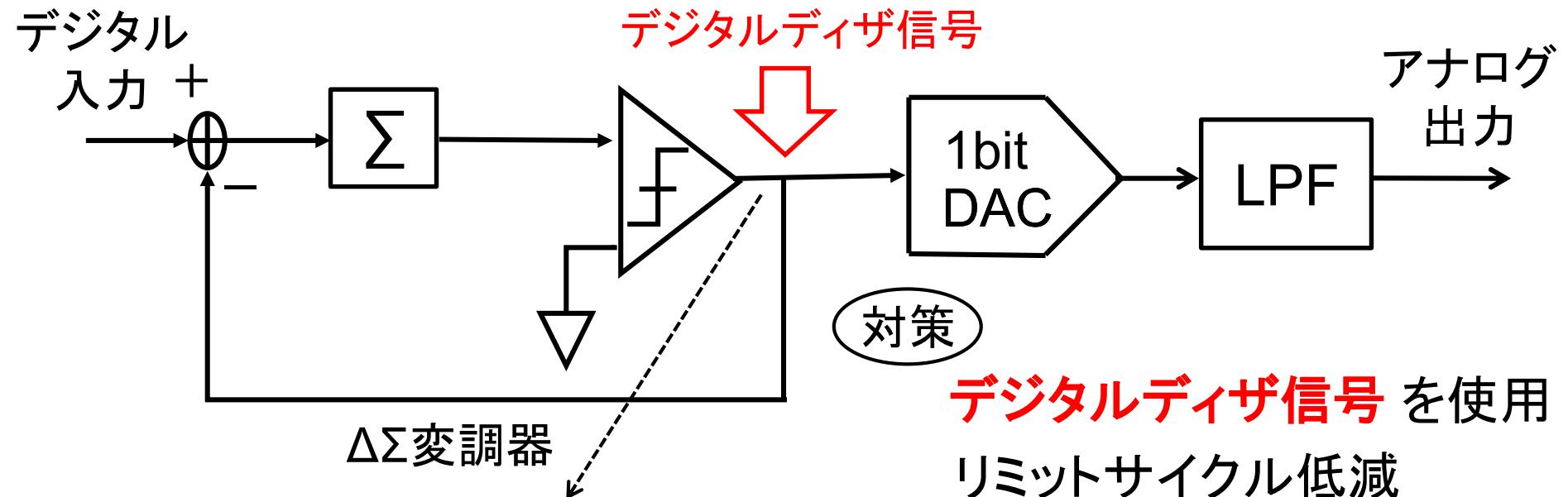

# まとめ

<まとめ>

ΔΣ変調器では

従来: 直流・低周波信号でリミットサイクルが発生

提案: ディザ信号と排他的論理和を用いた構成

- リミットサイクル低減 ⇒ LPFの性能要求を緩和

- SFDR向上

- 線形性あり

- FPGAでの動作を確認

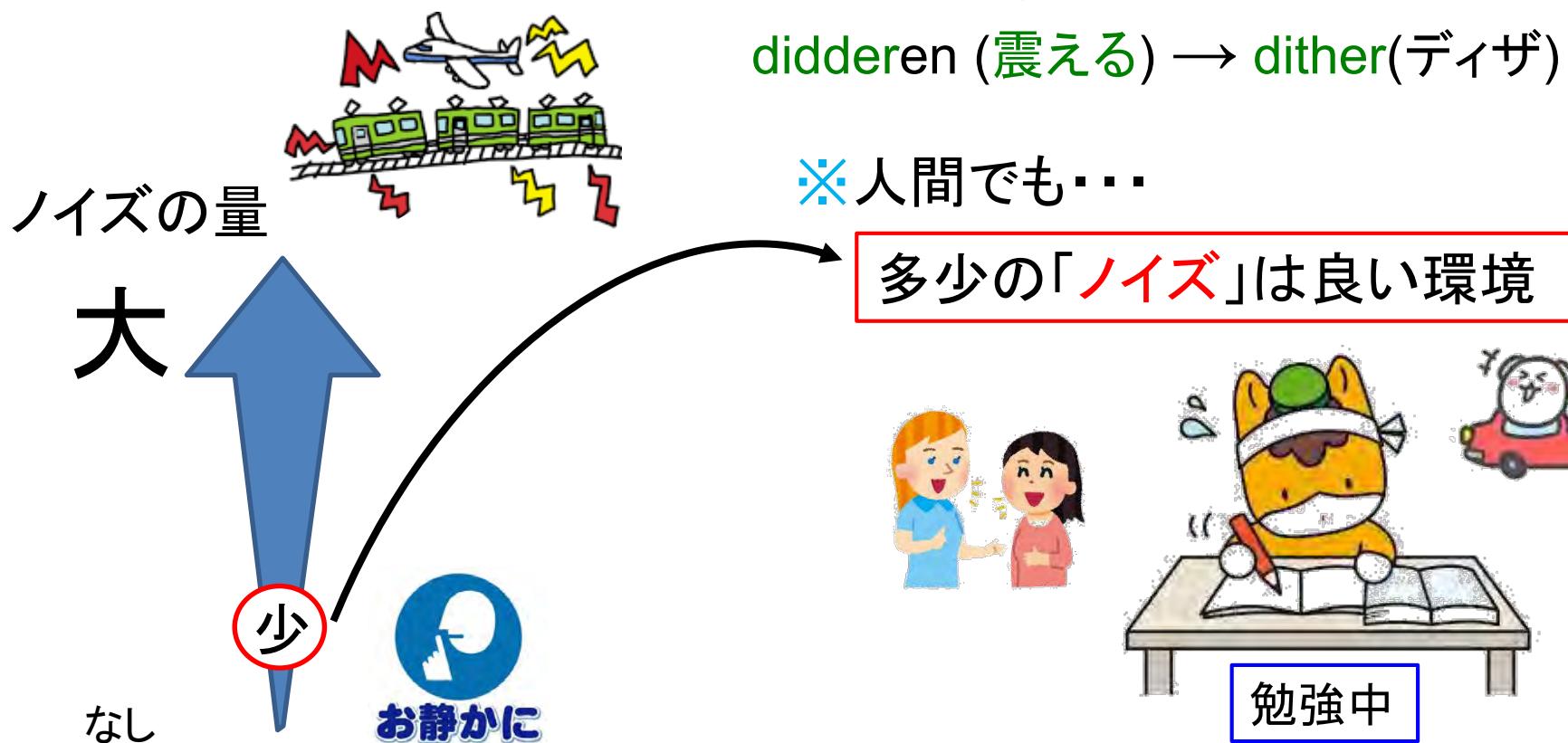

# デジタルディザ信号

## <dither(ディザ)の起源>

✓ 第二次世界大戦の頃

爆撃機には計算機が使用 ➡ 地上より飛行機上の方がうまく動作

理由: 振動の刺激が誤差を減少

didderen (震える) → dither(ディザ)

# 回路も人間も皆同じ

「完全に静かな場所では集中できない」

Philip E. Vernon

心理学者(英)

多少の「ノイズ」は良い環境

# Q & A

Q1.XORを用いていたが、他の論理回路(AND、OR)ではどうか

A1.他の論理回路では確認していない。XORではディザ信号を加えることはノイズを加えることに相当するため、考えやすい。

Q2.周期的な三角波や正弦波を入力していたが、ランダムにしたらどうか。

A2.ランダムのときは確認していない。リミットサイクル低減に繋がると思うが扱いにくいと考える。ランダムでの検証は今後の課題としたい。

# EMI低減化のための スイッチングノイズ・スペクトラム拡散技術 を用いたDC-DC変換回路

群馬大学大学院 工学研究科 電気電子工学専攻

通信処理システム第2研究室 小林研究室

○定村宏 大門 孝幸 進藤 崇之 小林 春夫(群馬大学)

名野 隆夫 鈴木達也 河井 周平 飯島 隆(三洋電機)

## 発表内容

1. 研究背景と目的

2. DC-DC変換回路の原理と特徴

3. DC-DC変換回路におけるノイズパワー・スペクトラム

拡散方式「**Pseudo Random digital Modulation**」

**PRM**方式の提案

4. **PRM**方式の特徴と効果

5. 結論

## 発表内容

### 1. 研究背景と目的

2. DC-DC変換回路の原理と特徴

3. DC-DC変換回路におけるノイズパワー・スペクトラム

拡散方式「**Pseudo Random digital Modulation**」

**PRM**方式の提案

4. **PRM**方式の特徴と効果

5. 結論

## 研究背景と目的

- 近年の携帯機器の普及

- 端末の多機能化

- 小型・高効率

- 複数電圧源の利用(マルチ電源)

- 低電圧化

## スイッチング電源の特徴

### ◆ メリット

- 高効率

- 出力電圧が連続可変

- 大電流 output

### ◆ デメリット

- 外付けコイルが必要(小型化が困難)

- ノイズが大きい

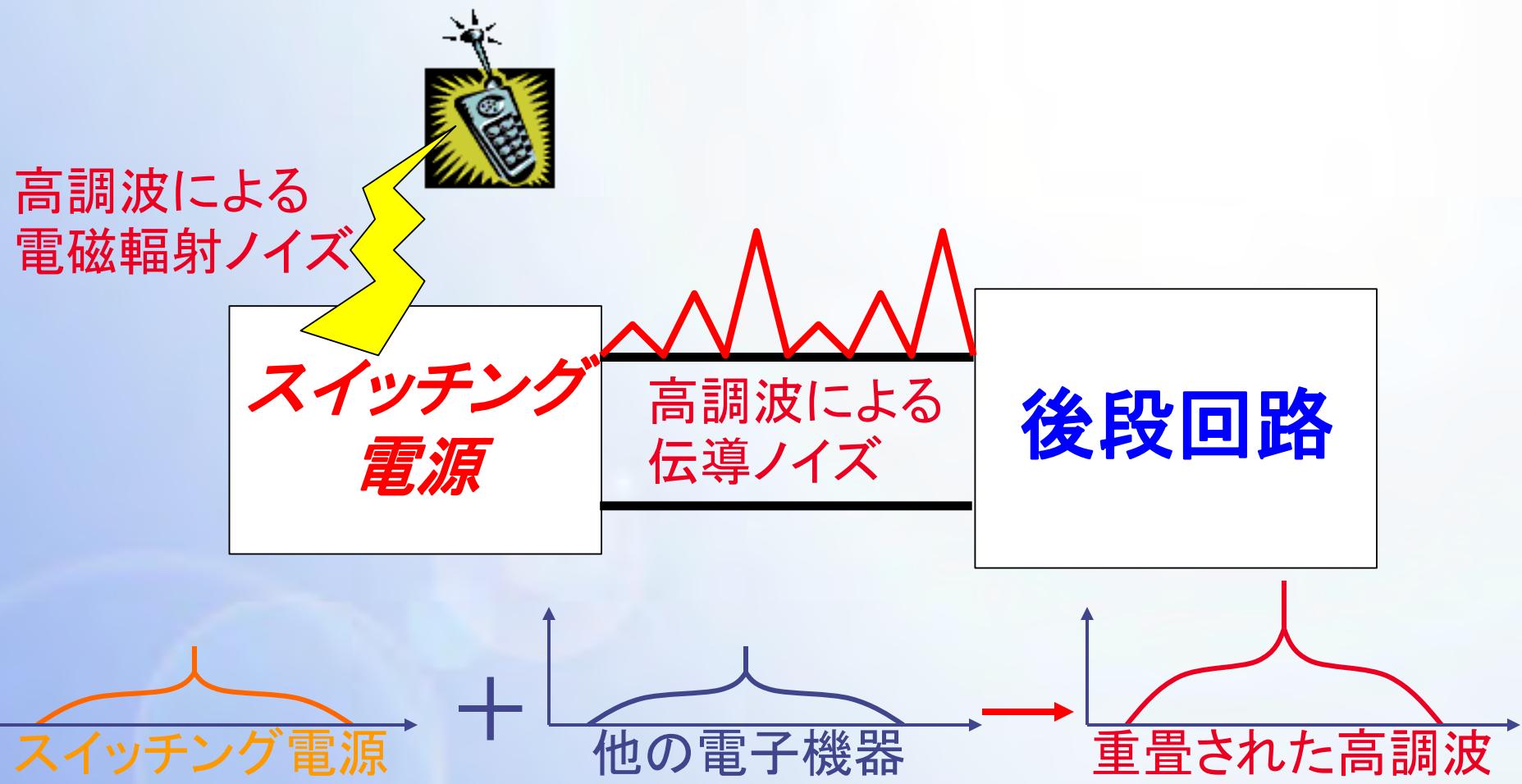

# 研究背景と目的

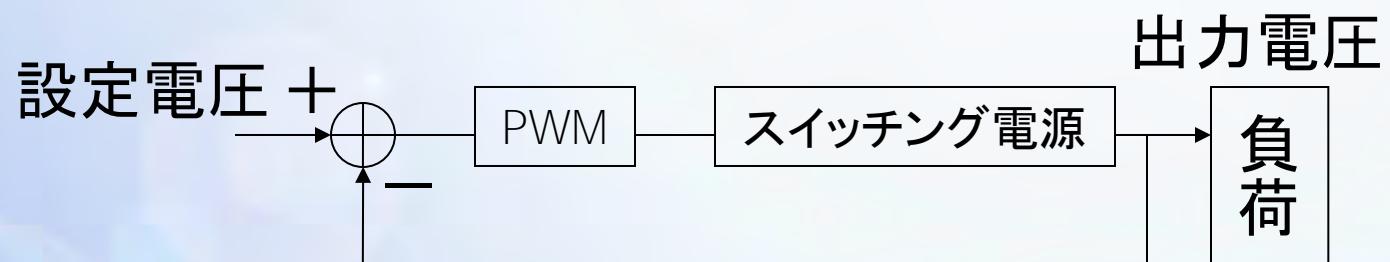

◆ DC-DC変換回路の問題点

「スイッチング・ノイズ 高調波ノイズに着目」

スイッチングノイズパワーのスペクトラム拡散技術による

**EMI(電磁障害)低減手法の新提案**

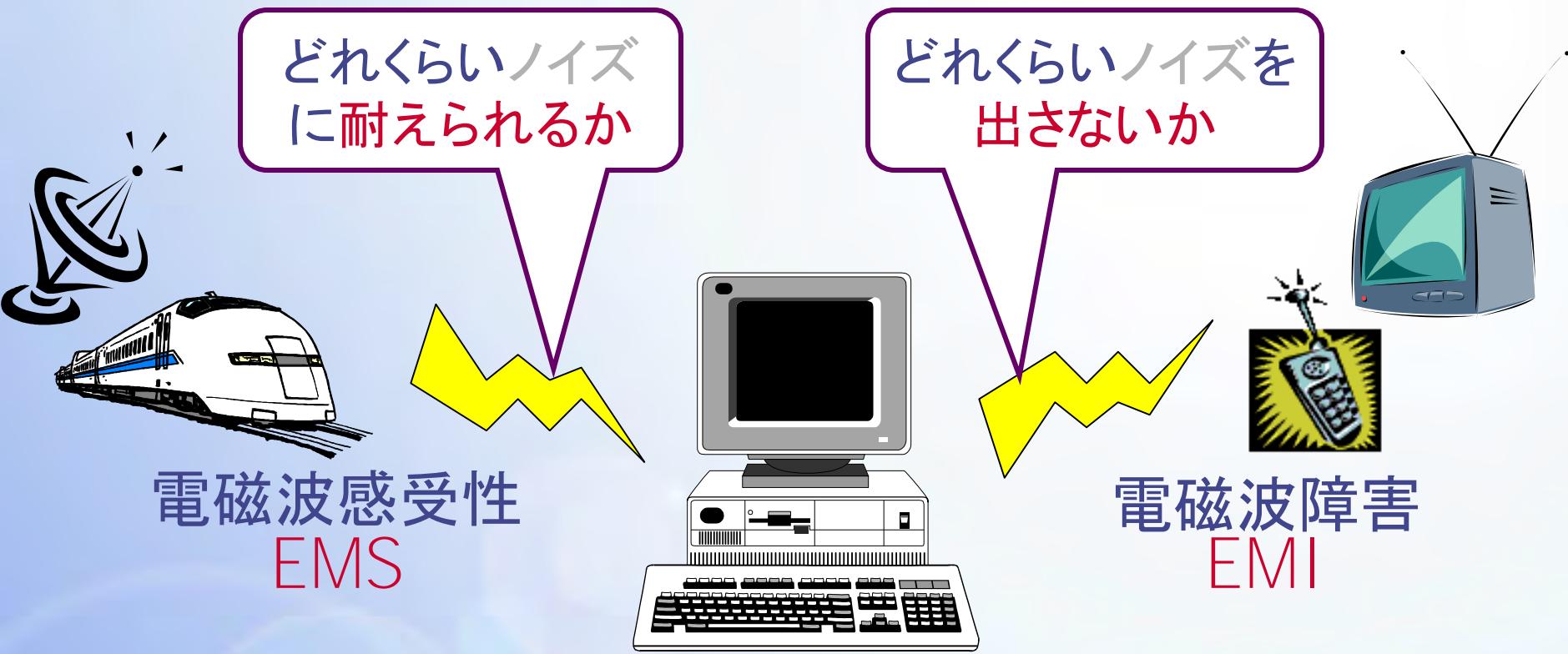

# EMI (ElectroMagnetic Interference) とは

$$\text{EMC} = \text{EMS} + \underline{\text{EMI}}$$

電磁環境両立性

# EMCが問題にされる場合

- ◆ EMS(電磁波感受性) :

微小信号を扱っている電子機器

(携帯電話、テレビ、オーディオ など)

- ◆ EMI(電磁波妨害) :

高調波ノイズや電磁波を発しやすい電子機器

(スイッチング電源、マイクロプロセッサ など)

# スイッチング電源によるEMIの影響

# 発表内容

1. 研究背景と目的

## 2. DC-DC変換回路の原理と特徴

3. DC-DC変換回路におけるノイズパワー・スペクトラム

拡散方式「Pseudo Random digital

Modulation」

PRM方式の提案

4. PRM方式の特徴と効果

5. 結論

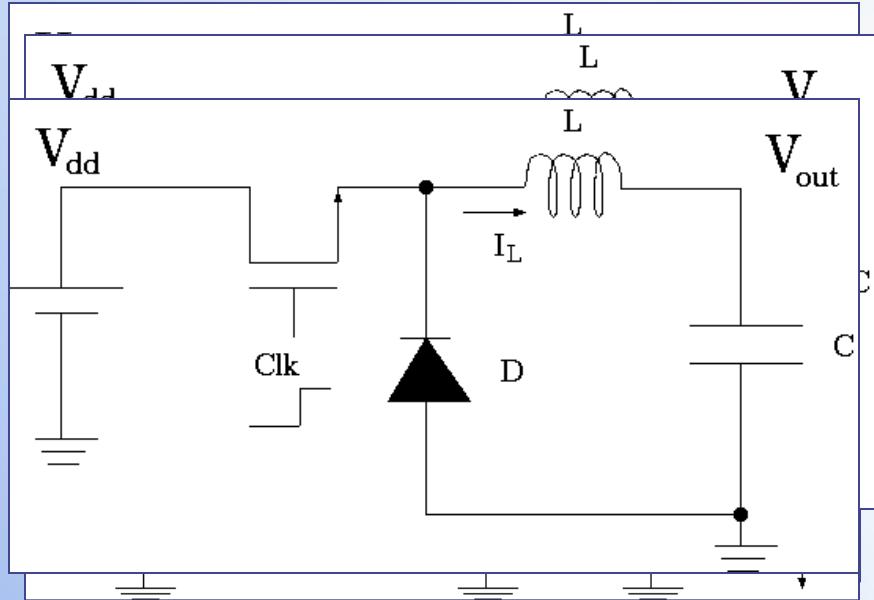

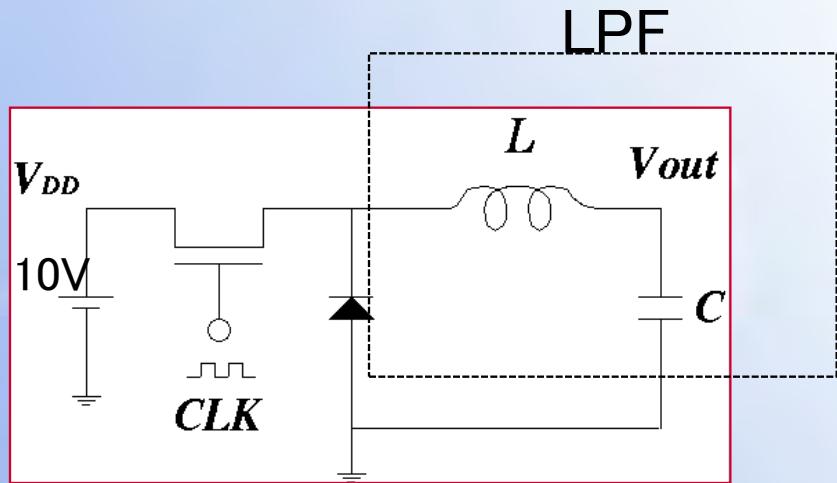

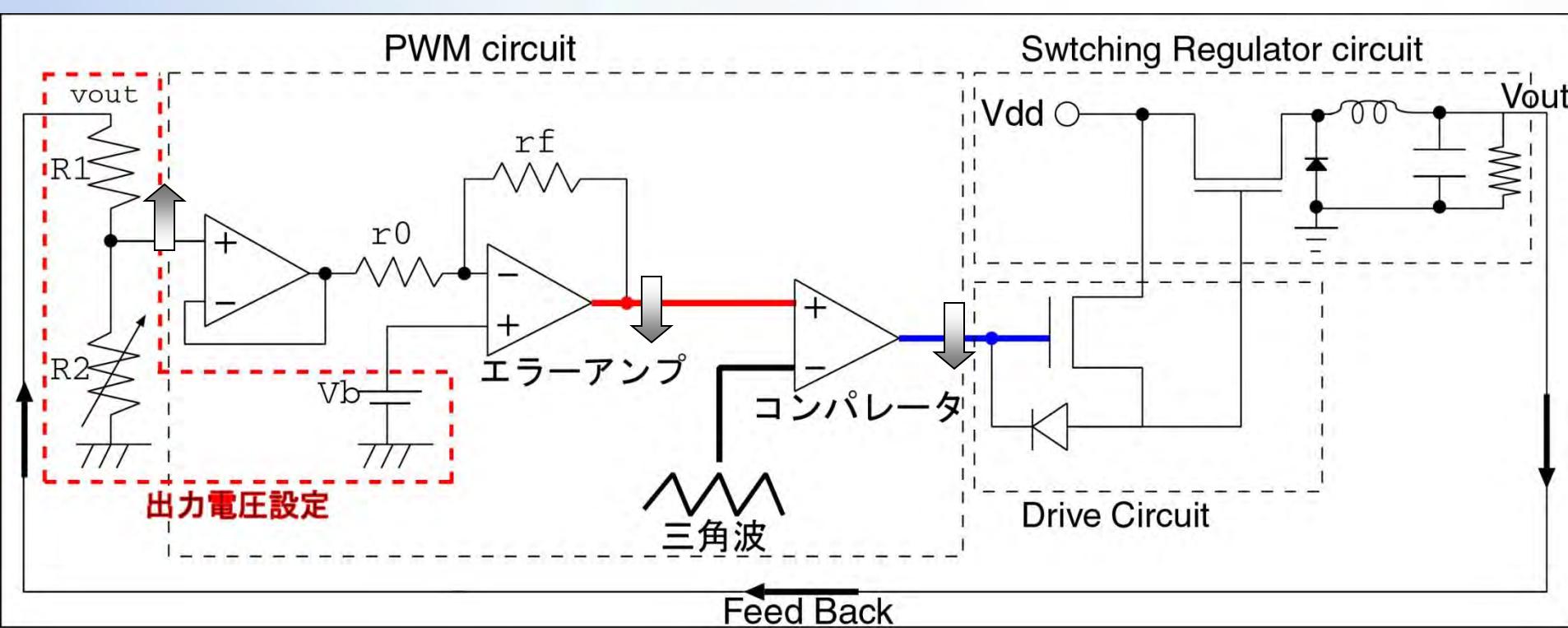

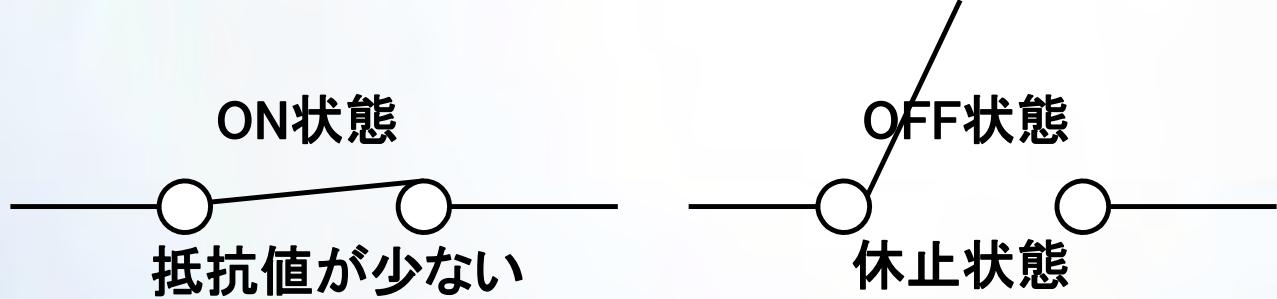

# DC-DC変換回路の原理と特徴(1)

◆ Clk=ONのとき

$$\Delta I_L = \frac{V_{dd} - V_{out}}{L} \cdot T_{on}$$

◆ Clk=OFFのとき

$$\Delta I_L = -\frac{V_{out}}{L} \cdot T_{off}$$

ONのときの電流の変化量=OFFのときの電流の変化量

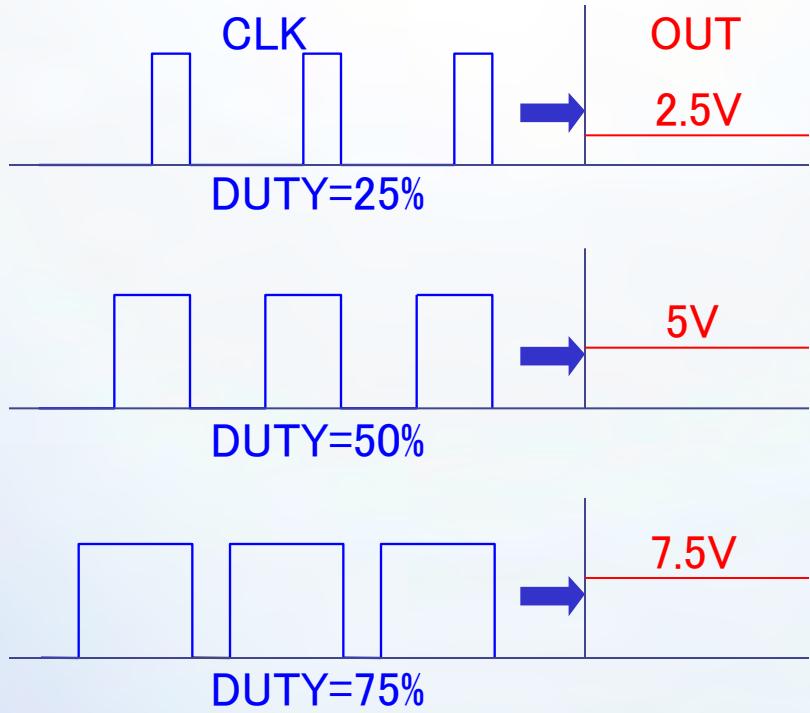

$$V_{out} = \frac{T_{on}}{T} \cdot V_{dd}$$

T: クロック周期

出力電圧はクロックデューティ(比率)によって決定

# DC-DC変換回路の原理と特徴(2)

- ・入力電源電圧 $V_{dd}$

- ・CLKでスイッチング

- ・LCローパス・フィルタ(LPF)で平滑化

- ・出力電源電圧 $V_{out}$

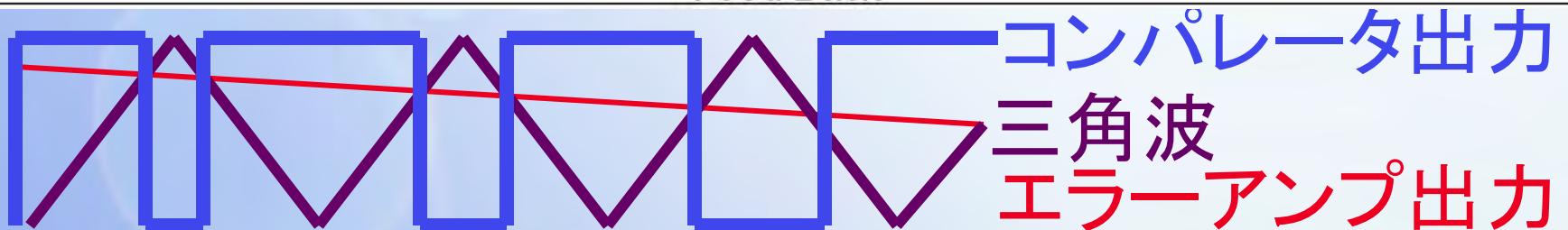

# PWM(パルス幅変調)制御方式

DC-DC電源回路の

駆動クロックデューティ(比率)を変調

PWM入力信号

PWM出力信号

## PWM制御方式を用いたDC-DC変換回路

# PWM制御 の特徴

## メリット

- ◆ スイッチでON/OFF

- ➡ 電力効率が良い

- ◆ 歸還制御

- ➡ 負荷によらず出力電圧が安定

## デメリット

- ◆ 電源周波数に同期

- ◆ 矩形波を発生

- ➡ 高調波ノイズが特定周波数に集中

- ➡ 高調波ノイズが大きい

# DC-DC変換回路の特徴と現状のまとめ

**EMI(電磁妨害)規格を満たすために

シールド等による対策が必要**

EMI規格を満たす回路を提案

## 発表内容

1. 研究背景と目的

2. DC-DC変換回路の原理と特徴

3. DC-DC変換回路におけるノイズパワー・スペクトラム

拡散方式「**Pseudo Random digital Modulation**」

**PRM**方式の提案

4. PRM方式の特徴と効果

5. 結論

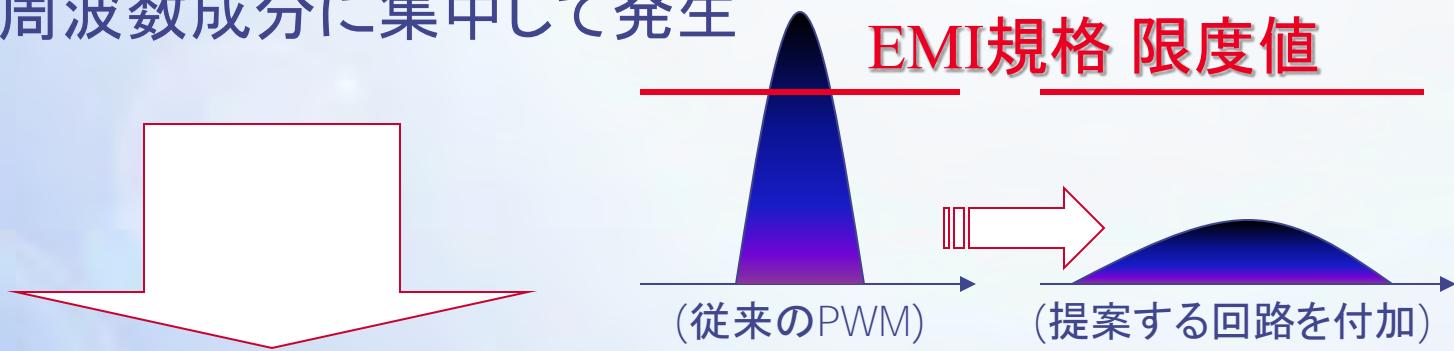

# 今回提案するスイッチング方式

従来DC-DC変換回路 + デジタル制御回路の付加

スイッチングノイズパワー・高調波ノイズパワーが

特定周波数成分に集中して発生

高調波ノイズパワーとスイッチングノイズパワーの

周波数成分を拡散しEMIの低減を実現

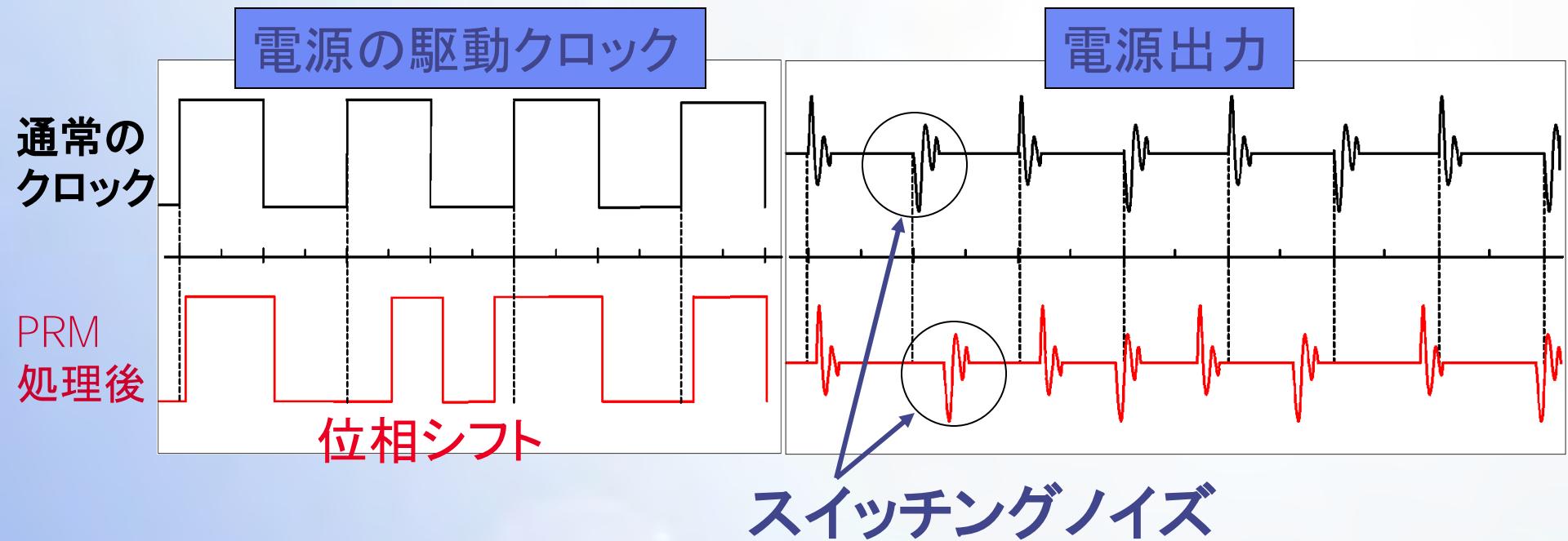

# 提案する疑似ランダム変調(PRM)の原理

DC-DC変換回路

・電流微分  $V = L \frac{di}{dt}$  の影響

スイッチングノイズ大

・矩形波を用いたスイッチング制御

高調波ノイズ大

ノイズパワーを疑似ランダム拡散

University

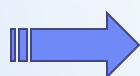

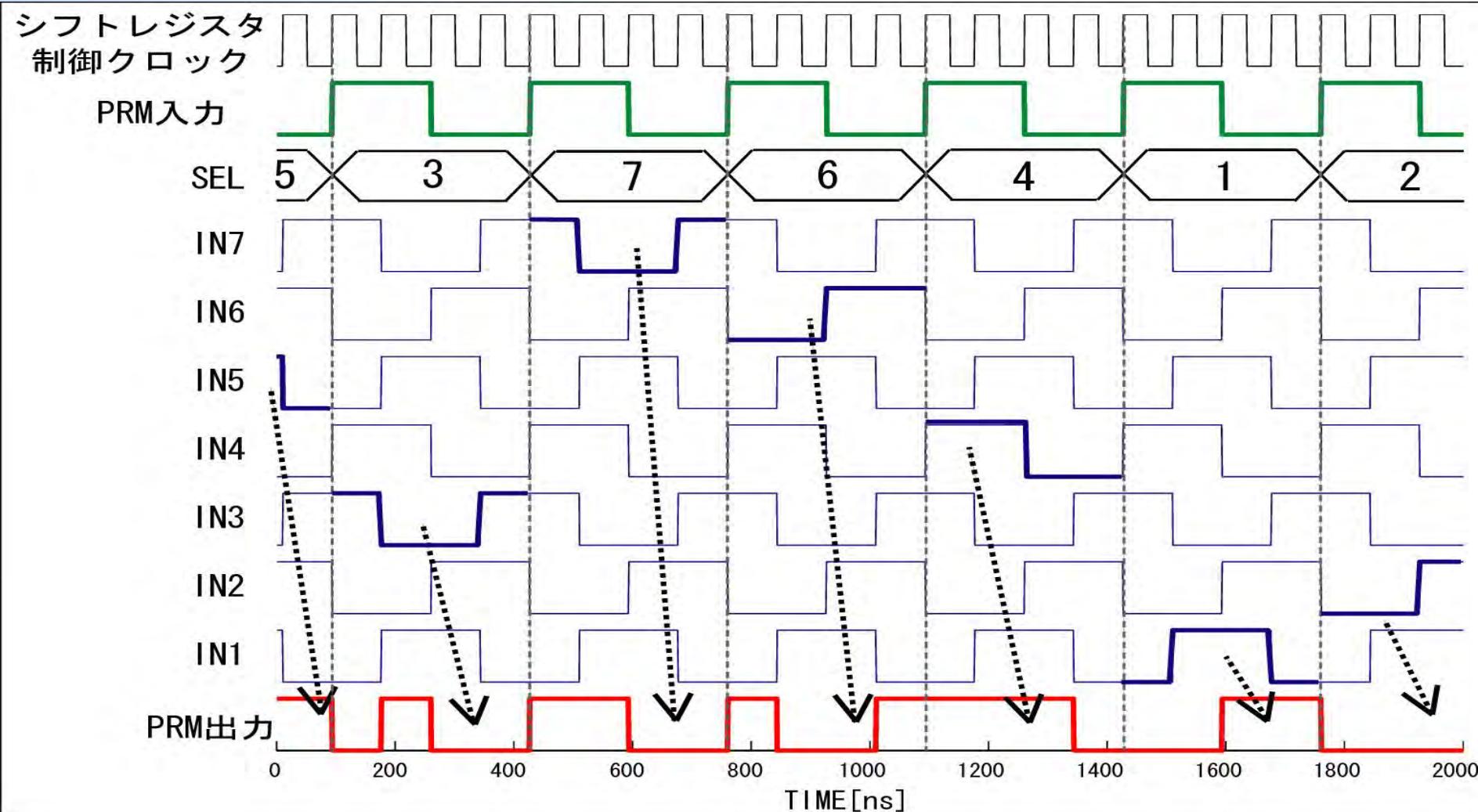

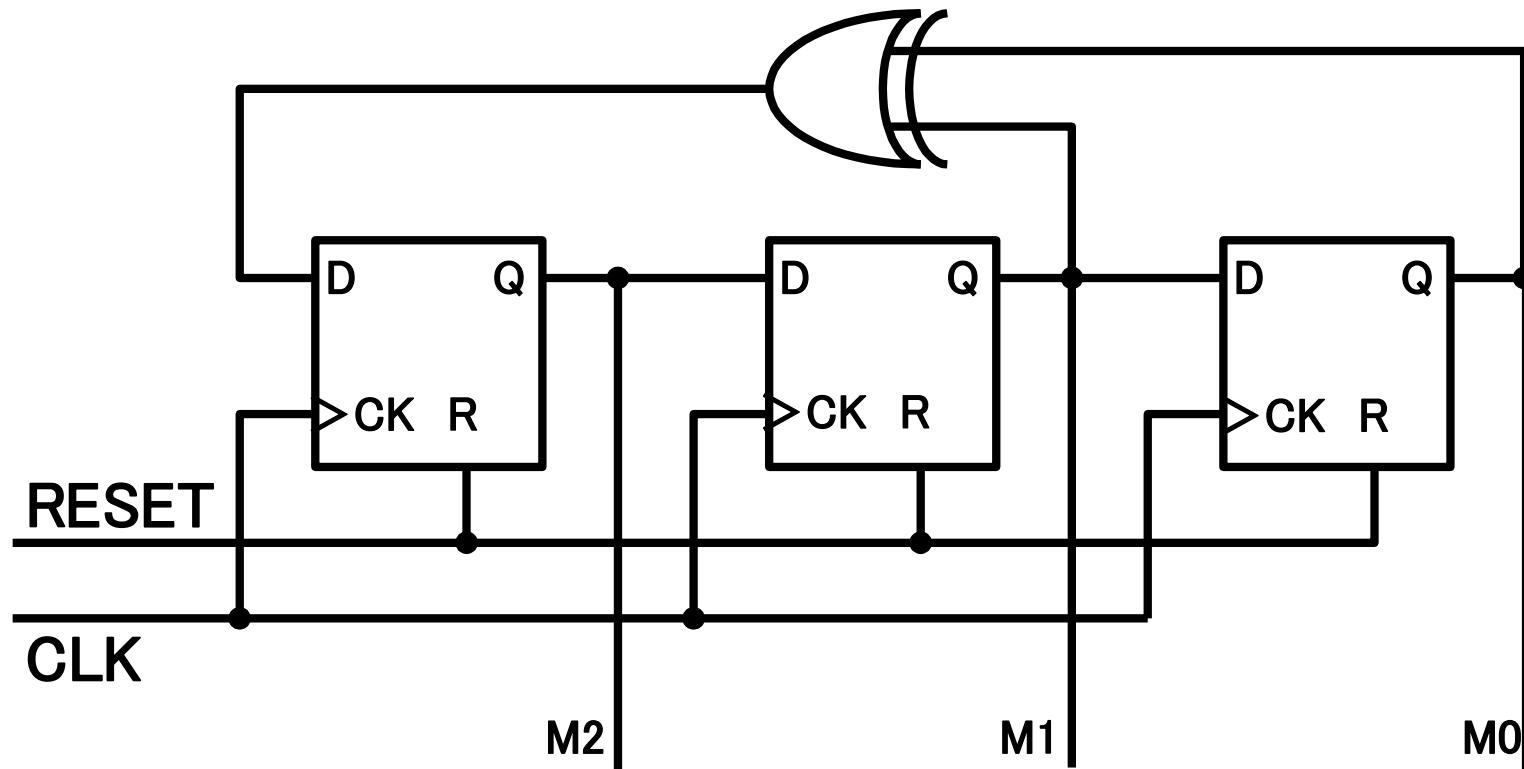

# 疑似ランダム変調PRM回路の提案

3bitのM系列を用いた場合

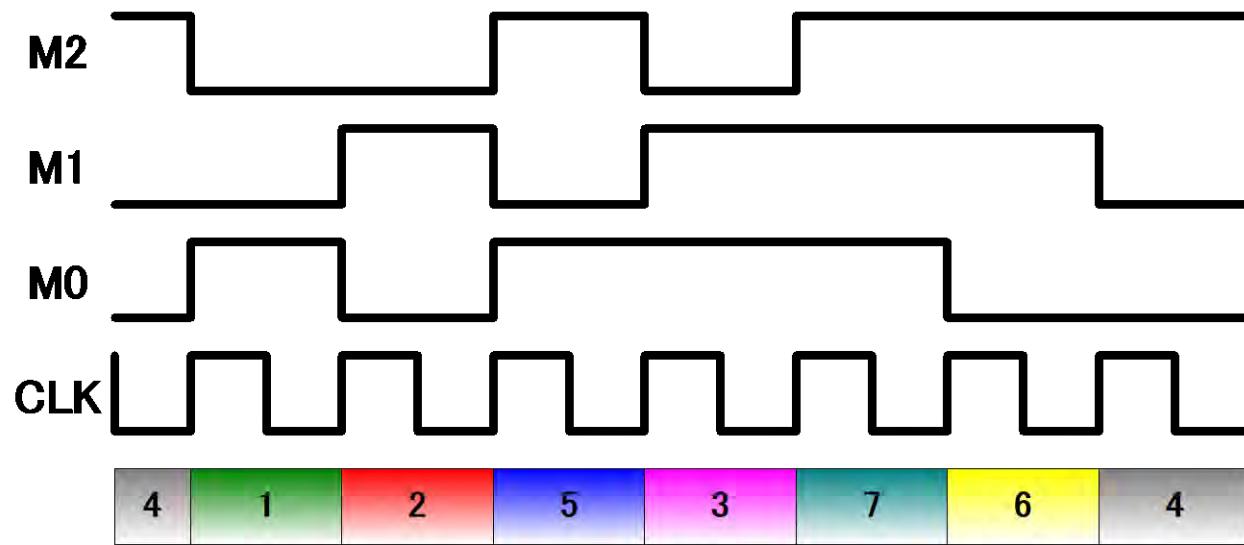

# PRMタイミングチャート

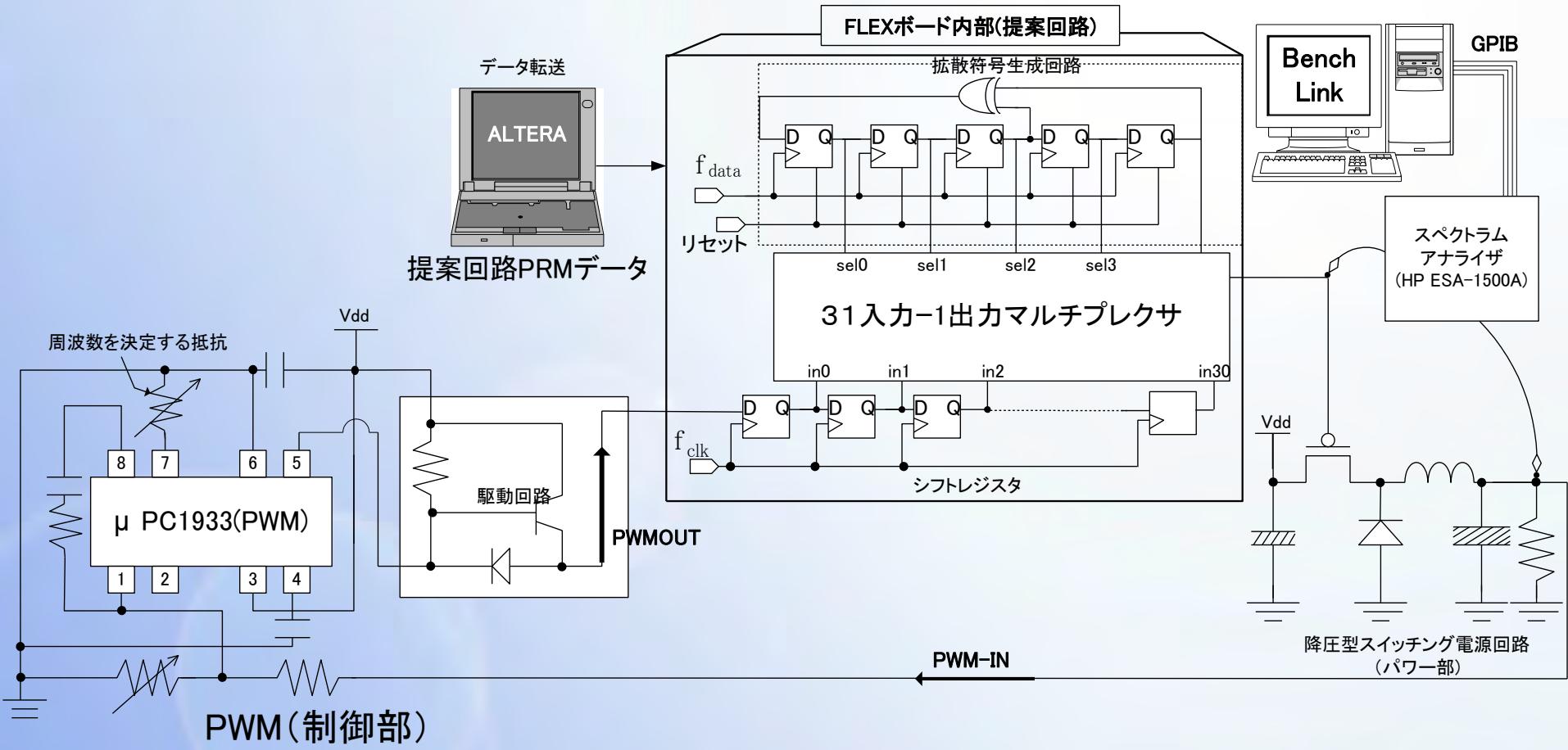

# PRMを用いたDC-DC変換回路の構成

提案するPRM回路

DC-DC変換

回路出力

PRM

出力

パワー系

DC-DC変換回路

PWM

出力

パルス幅変調器

制御系

従来回路(変更不

要)

$V_{OUT}$

Gunma University

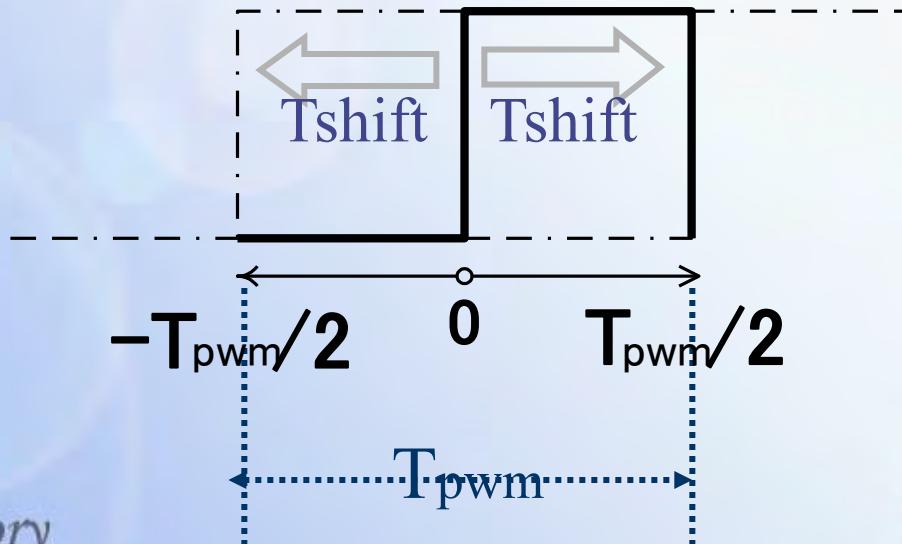

# 位相シフト量の最適値(1)

・位相シフトが大きすぎると

出力リップル大となり

電源出力が不安定

## 提案回路の出力クロック

・位相シフトが微小であると

十分に拡散されない

位相シフト量の最適値を実測により算出

# 位相シフト量の最適値(2)

実測結果から得られた最大位相シフト量Tshiftの最適値は

$$T_{shift} = \frac{T_{pwm}}{2}$$

$T_{pwm}$ =PWMクロックの一周期

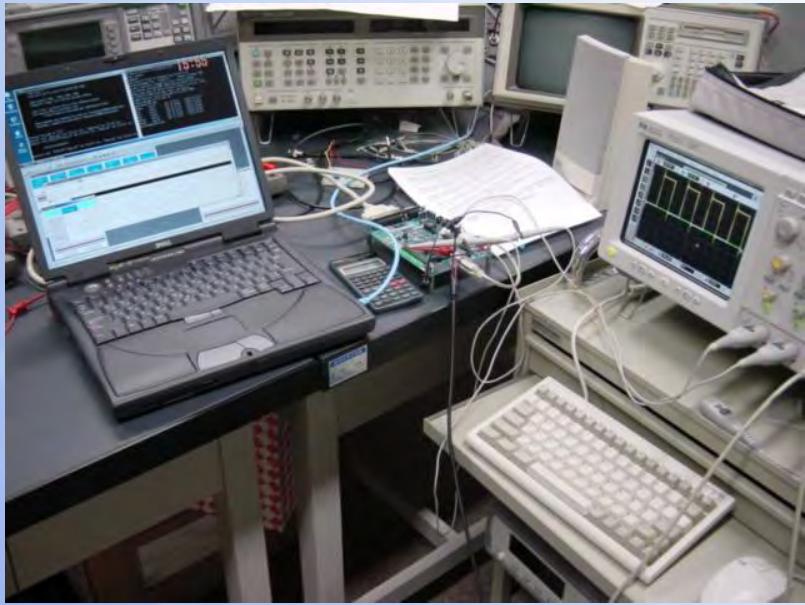

# 試作・評価環境

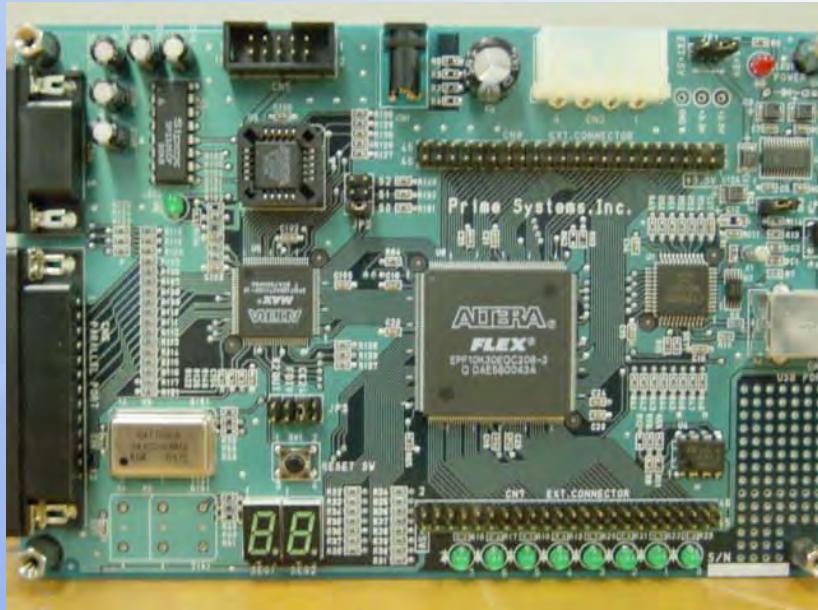

# FPGA設計環境と設計仕様

## 使用した評価ボード

テクノロジ:FLEX10K30EQC208 - 3

(アルテラ社)

## 設計仕様

| 項目            | 仕様     |

|---------------|--------|

| スペクトラム拡散方式    | 直接拡散   |

| シフトレジスタ制御クロック | 6MHz   |

| PWM入力         | 187kHz |

| PN符号制御クロック    | 187kHz |

| 電源電圧          | 3.3V   |

| PN符号          | M系列    |

| 符号長           | 31     |

| DFFの数         | 37     |

# 提案するPRMタイミングチャート(実測)

ロジックアナライザを用いて実測上で確認

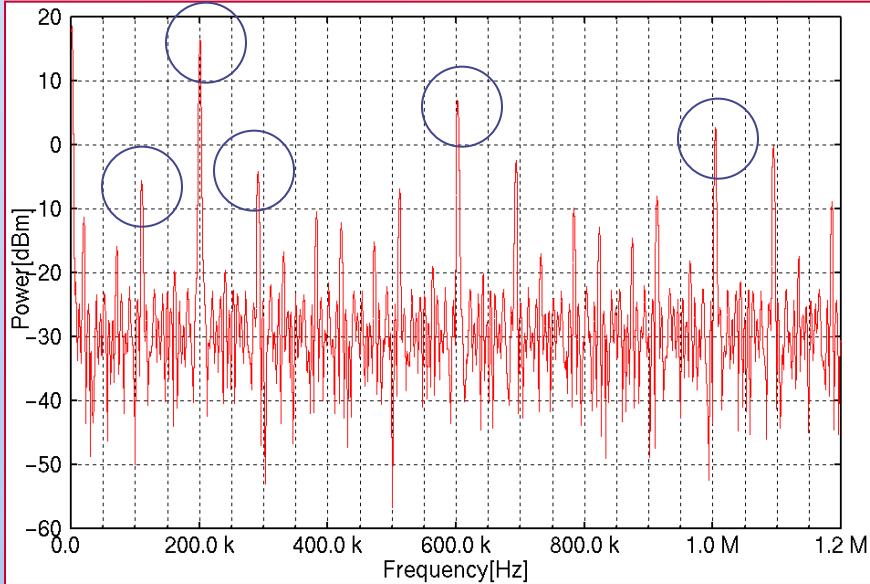

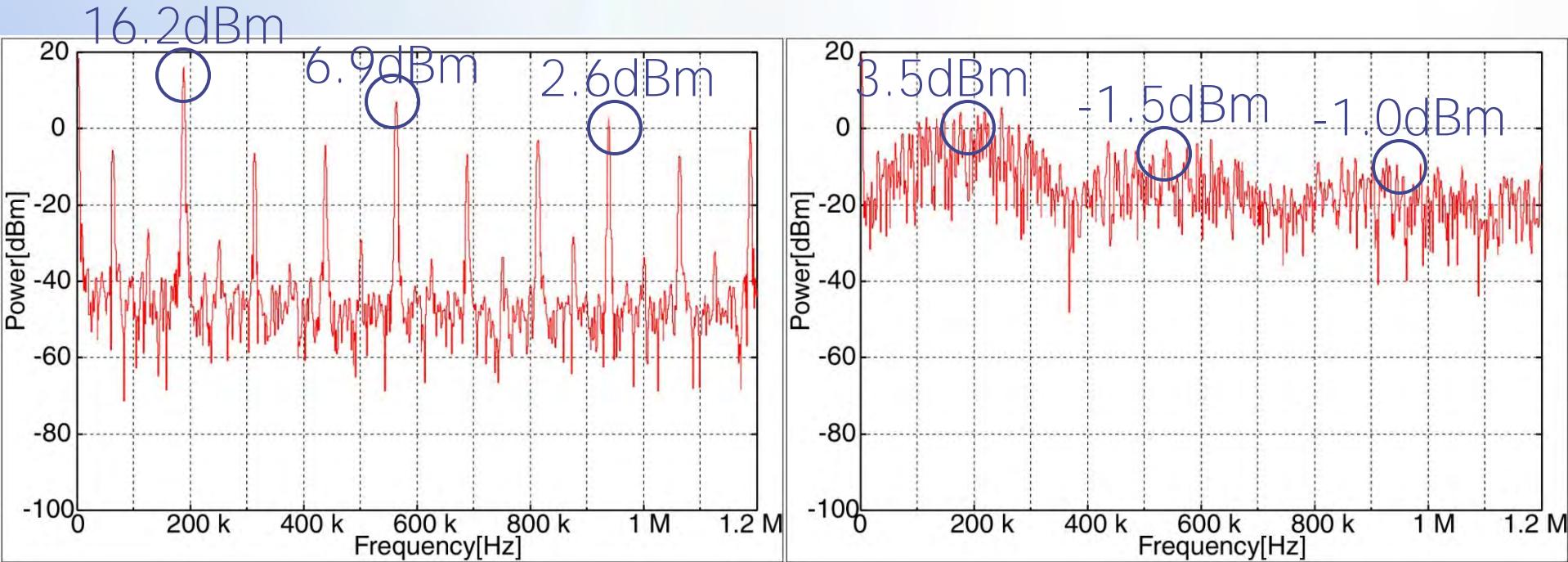

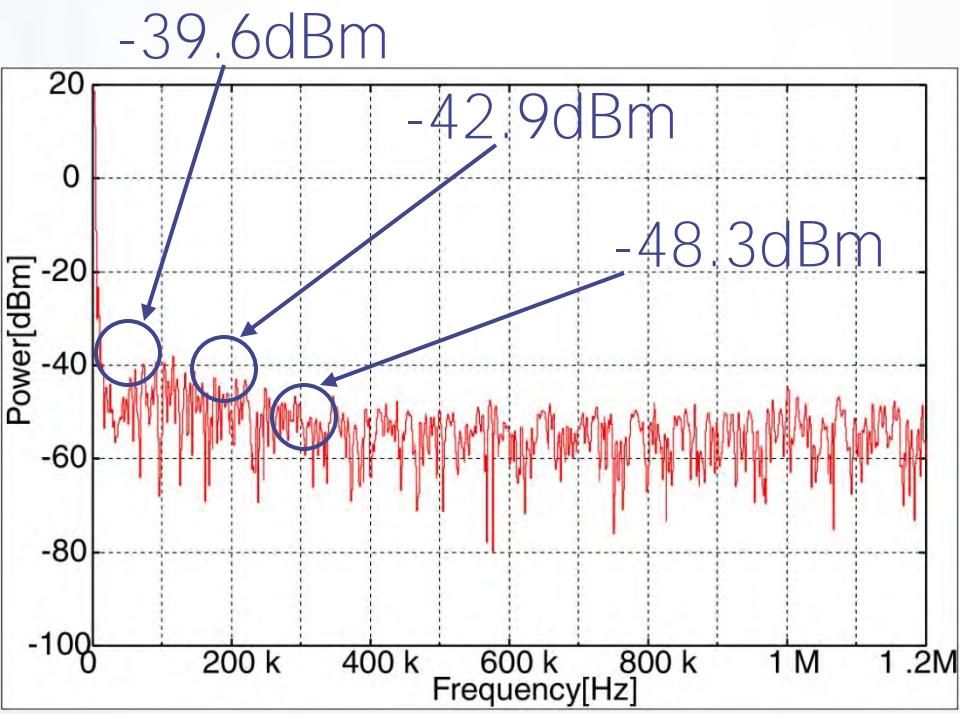

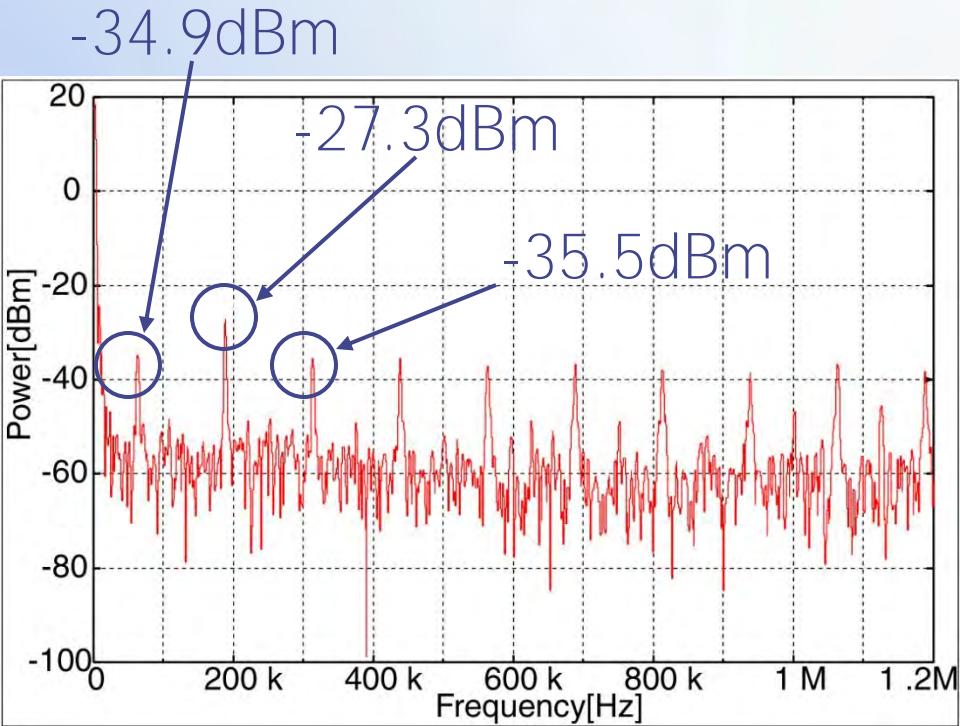

# 駆動クロックの実測パワースペクトラム

通常のクロックの

パワースペクトラム

(従来)

最大ピーク12.7dBm減少

5bitM系列PRM出力クロックの

パワースペクトラム

(新手法)

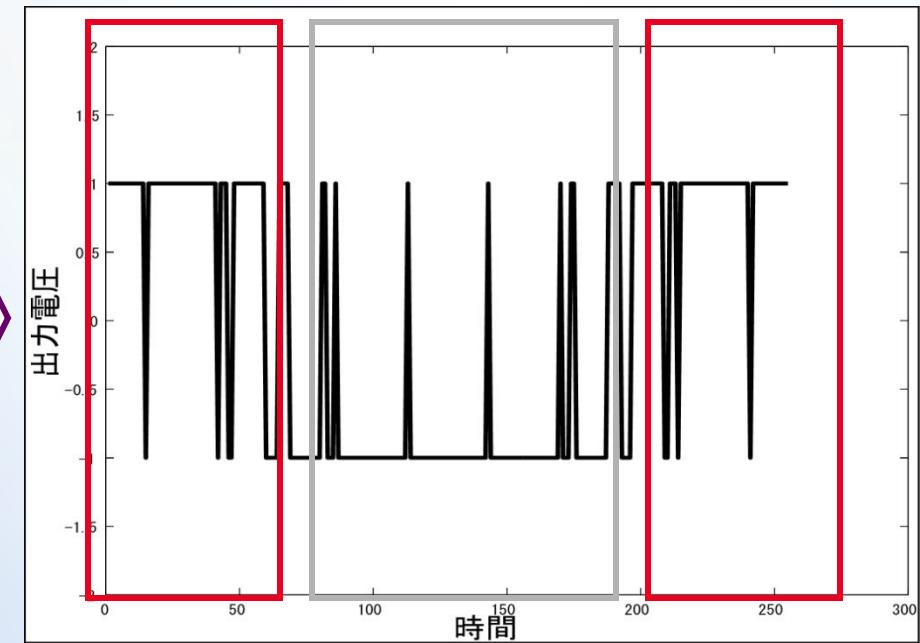

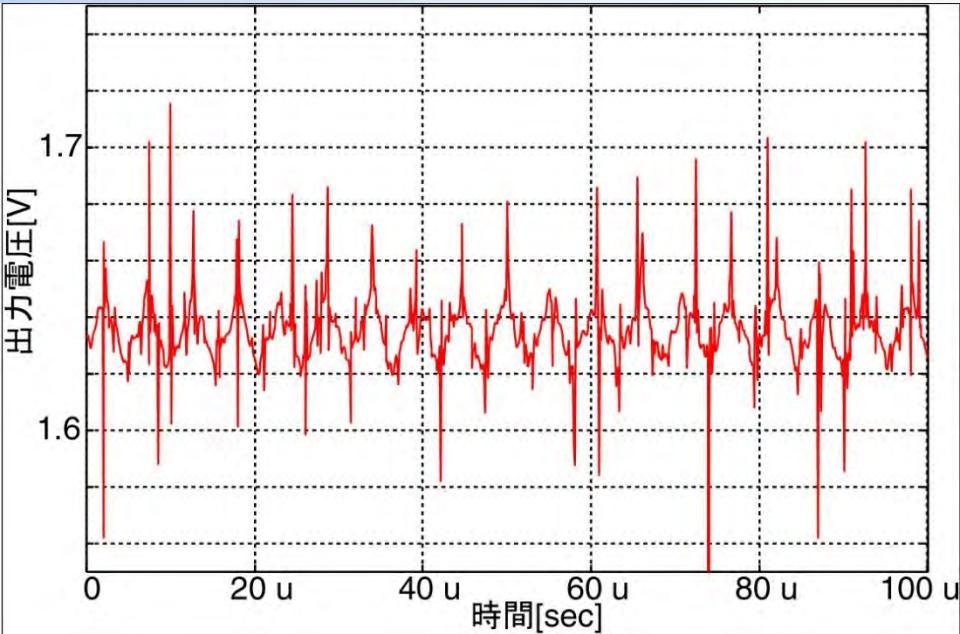

# DC-DC変換回路出力電圧波形

入力電圧Vdd=3.3 クロックデューティ=50%

通常のクロックを用いた場合

(従来)

提案するPRMを用いた場合

(新手法)

# DC-DC変換回路 実測パワースペクトラム

最大ピーク12. 3dBm低減

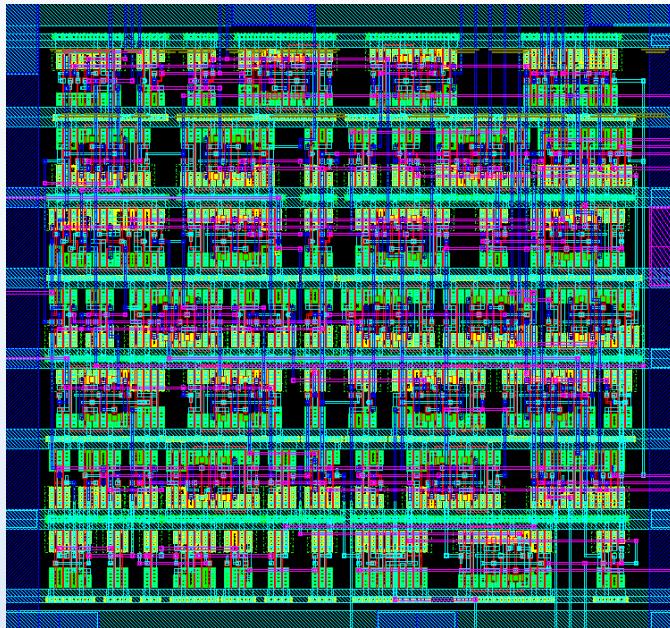

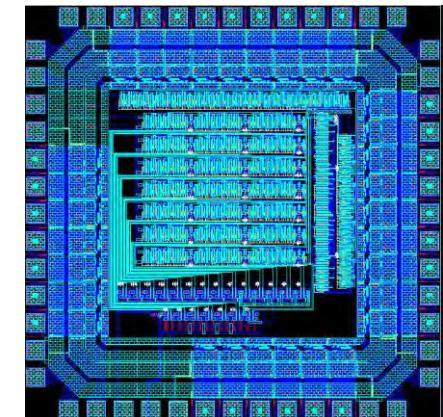

# 提案するPRMの試作

## FPGA設計

- ALTERAツールで設計

- FPGA評価ボードによる計測

## セミカスタム設計

- VDECツールで設計

- セルレイアウト設計

二つの手法で設計

## 発表内容

1. 研究背景と目的

2. DC-DC変換回路の原理と特徴

3. DC-DC変換回路におけるノイズパワー・スペクトラム

拡散方式「**Pseudo Random digital Modulation**」

**PRM**方式の提案

4. **PRM**方式の特徴と効果

5. 結論

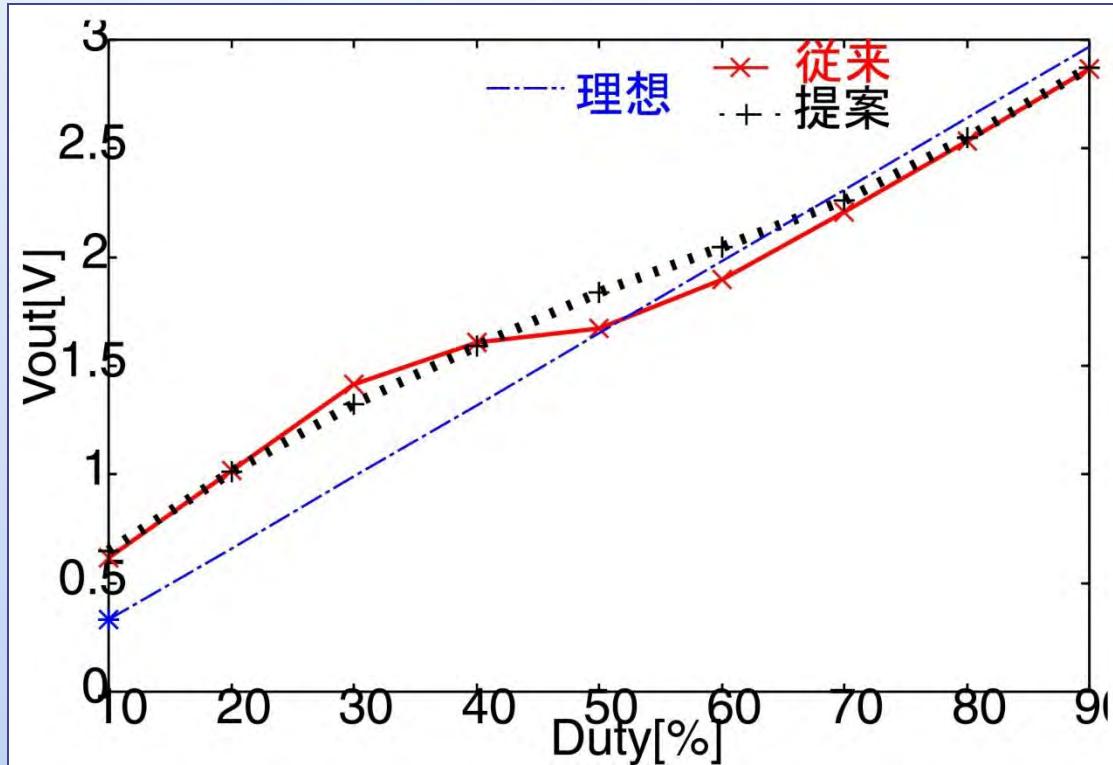

# クロックデューティー出力電圧特性

理想の出力電圧にほぼ一致

提案回路の変調による出力電圧への影響はほとんど無い

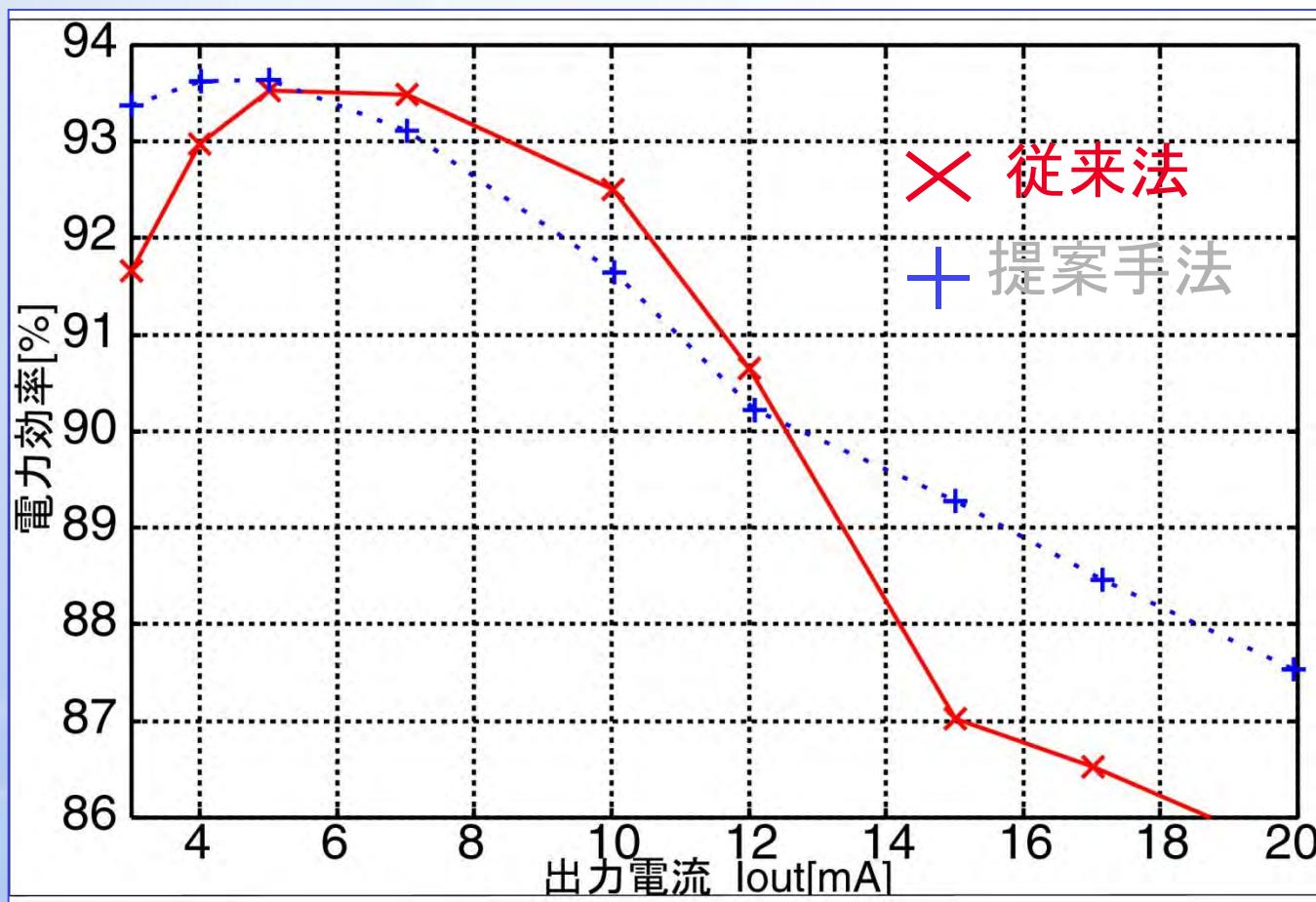

# 効率特性への影響

提案回路による効率への影響はほとんど無い

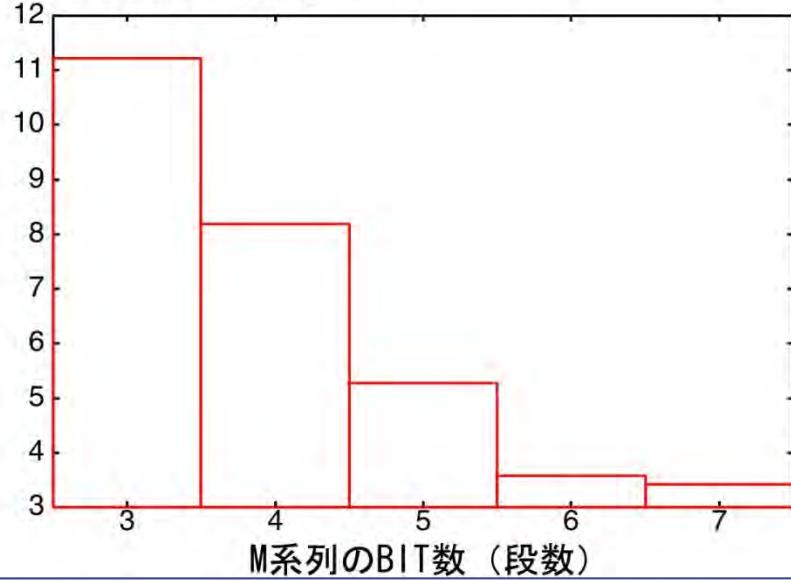

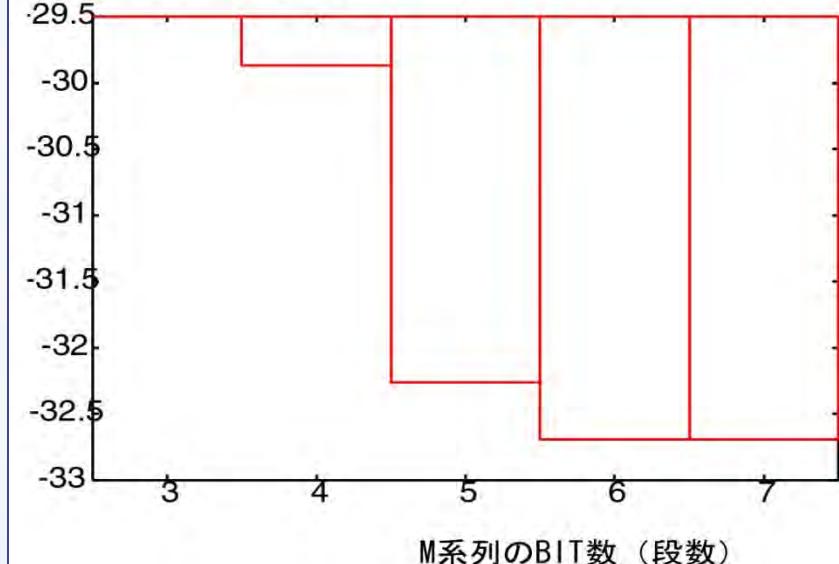

# 最大ノイズパワー - M系列のBIT数 特性

最大ノイズパワー [dBm]

最大ノイズパワー [dBm]

駆動クロックの最大ノイズピーク

電源出力の最大ノイズピーク

拡散度・回路規模の面から5,6bit が妥当

## 結論

- ◆ DC-DC変換回路のノイズパワー・スペクトラム拡散技術を提案

- 簡単なデジタル回路付加でEMI低減を実現

- 低成本、低消費電力

- 温度変化、経時変化の影響なし

- 従来回路の設計変更不要

- 昇圧型スイッチング電源にも適用可

FPGAで試作し

実測上で動作確認をした

|       |           |

|-------|-----------|

| 最大ピーク | 12.3dBm減  |

| 基本波   | 5.7dBm 減  |

| 2次高調波 | 15.6dBm 減 |

| 3次高調波 | 12.8dBm 減 |

# スイッチング電源の ノイズスペクトル拡散技術の発明者

スイッチング電源のスペクトル拡散技術の最初の考案は鹿児島大学 田中哲郎先生と認識している。

ご自身ではこの技術を Random Switching と呼んでいる。

田中先生が(当時)九州大学 原田耕介先生の大学院生のときに提案された。(大分大学 鍋島隆先生より)

同じ技術で、デジタルプロセッサのクロック分野でスペクトル拡散クロックがヒューレットパッカード社から提案されてから何十年も経つ。

が、田中先生はこの技術の電源回路への応用として考えられたのではなく別の発想から思いつかれたような印象である。

# デジタル技術を用いた アナログ回路の特性向上技術

- Digital-Assisted Analog Circuit -

計測制御工学特論

小林春夫

# 背景

- 半導体技術の進展によるCMOSの微細化

デジタル回路は大きな恩恵

アナログ回路への恩恵少ない

低電圧化、特性ばらつき大

- デジタル技術の助けにより

アナログ回路の特性向上を図る技術が重要

# ノイズのスペクトラム拡散技術

- 特定周波数成分にノイズパワーが集中すると不都合な場合が多い。

- ノイズパワーの周波数拡散を行う。

(Spread-Spectrum Technique)

ノイズパワーの周波数ピークは下がる。

トータルのノイズパワー量は同じ。

# SSC (Spread-Spectrum Clocking)

デジタル・プロセッサ

クロックのタイミングを意図的に揺らがせ、

周波数拡散を行ない、EMIの問題を軽減

広く用いられている手法

# I、Q経路ダイナミック・マッチングによる 高周波信号発生器の低スプリアス化

群馬大学 電気電子工学科

大槻 純 塙 昊 小林 春夫 小室 貴紀 宮本 幸治

# 発表内容

1. 問題設定

2. I,Q経路ミスマッチによるSFDR劣化

3. ダイナミック・マッチングによる

SFDR向上手法の提案

4. まとめ

# 1. 問題設定

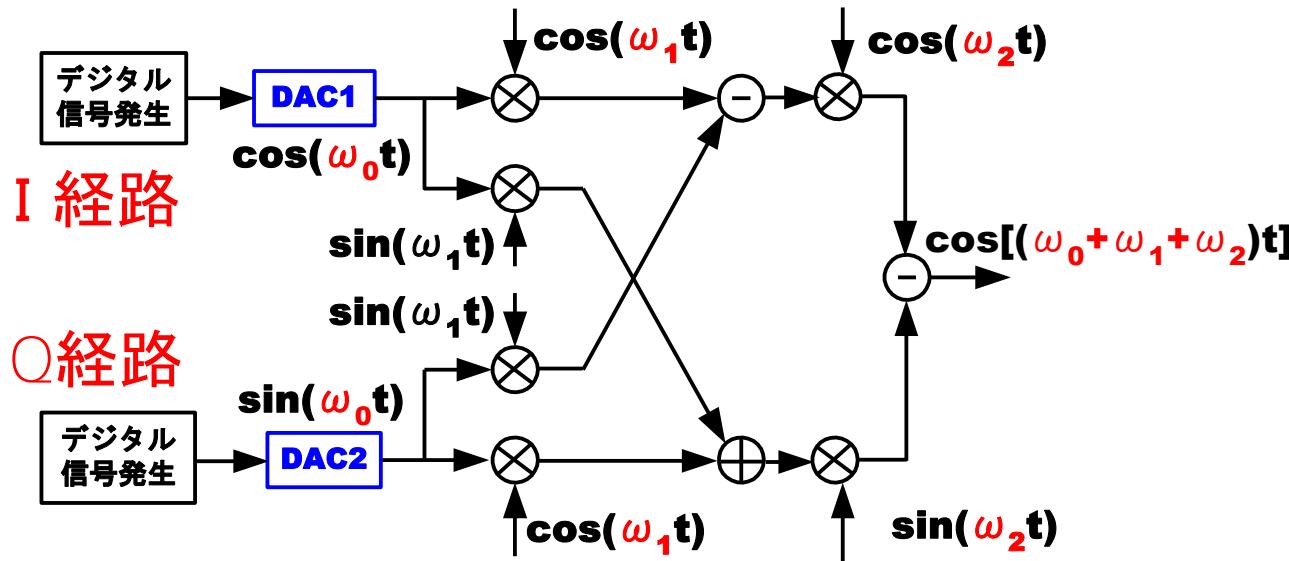

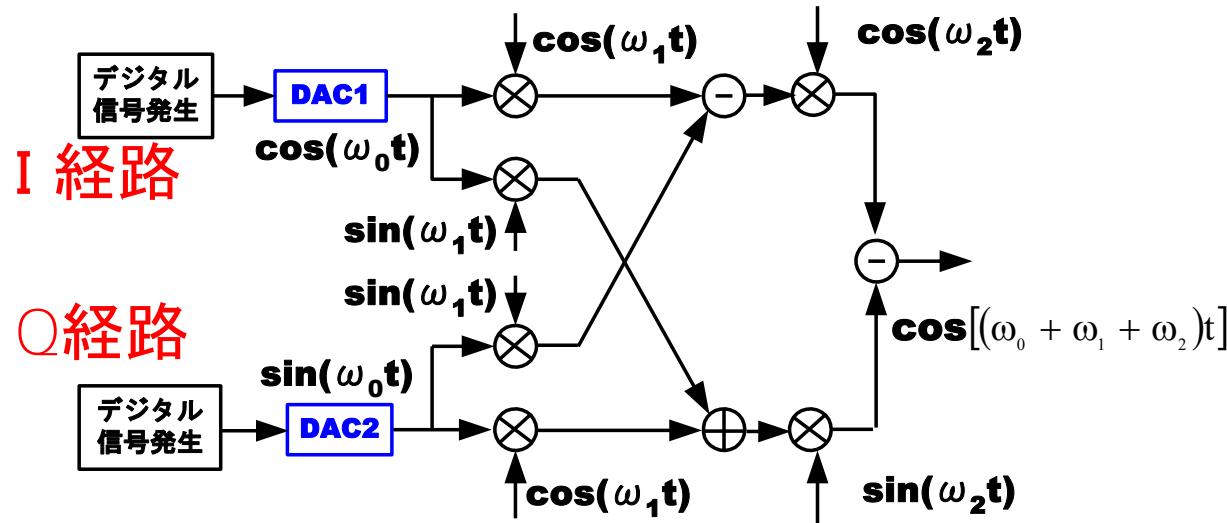

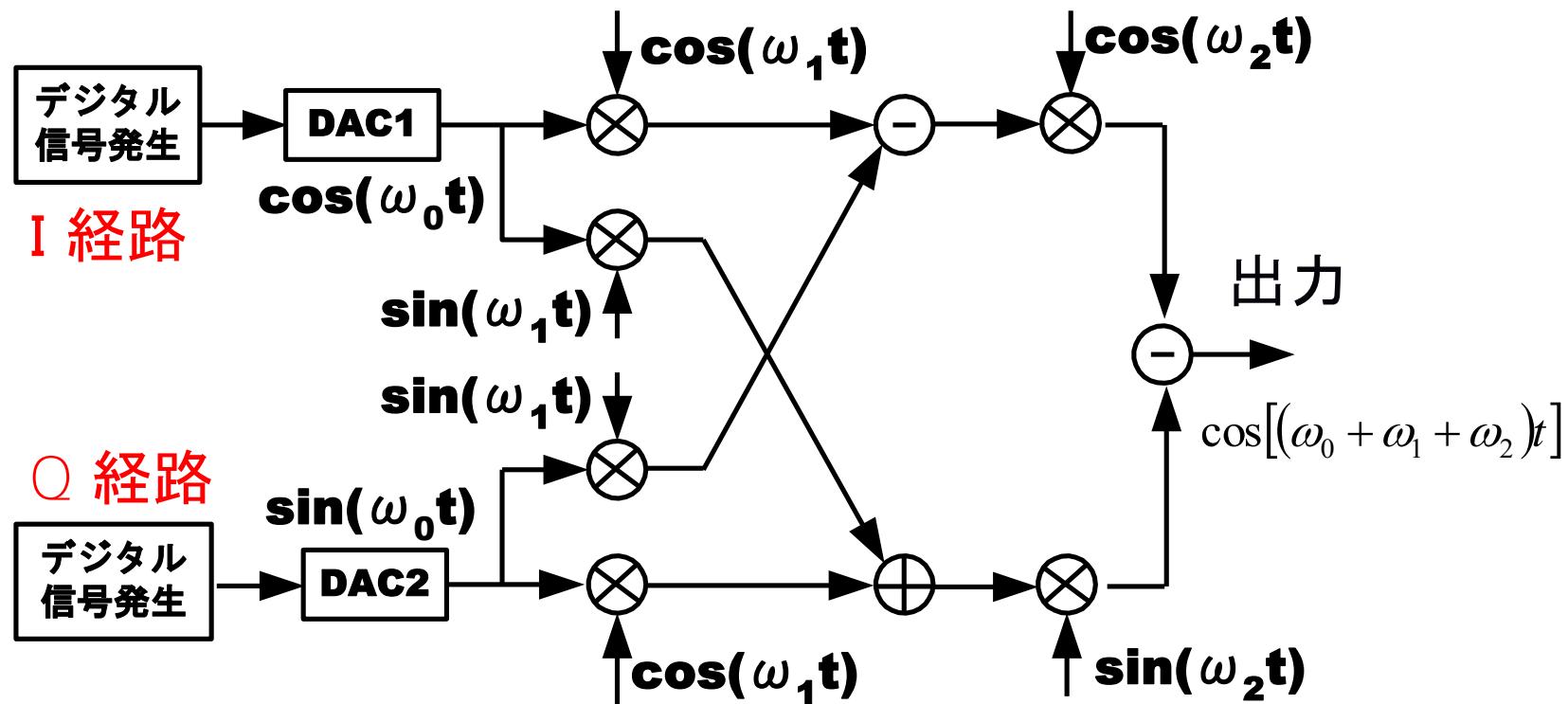

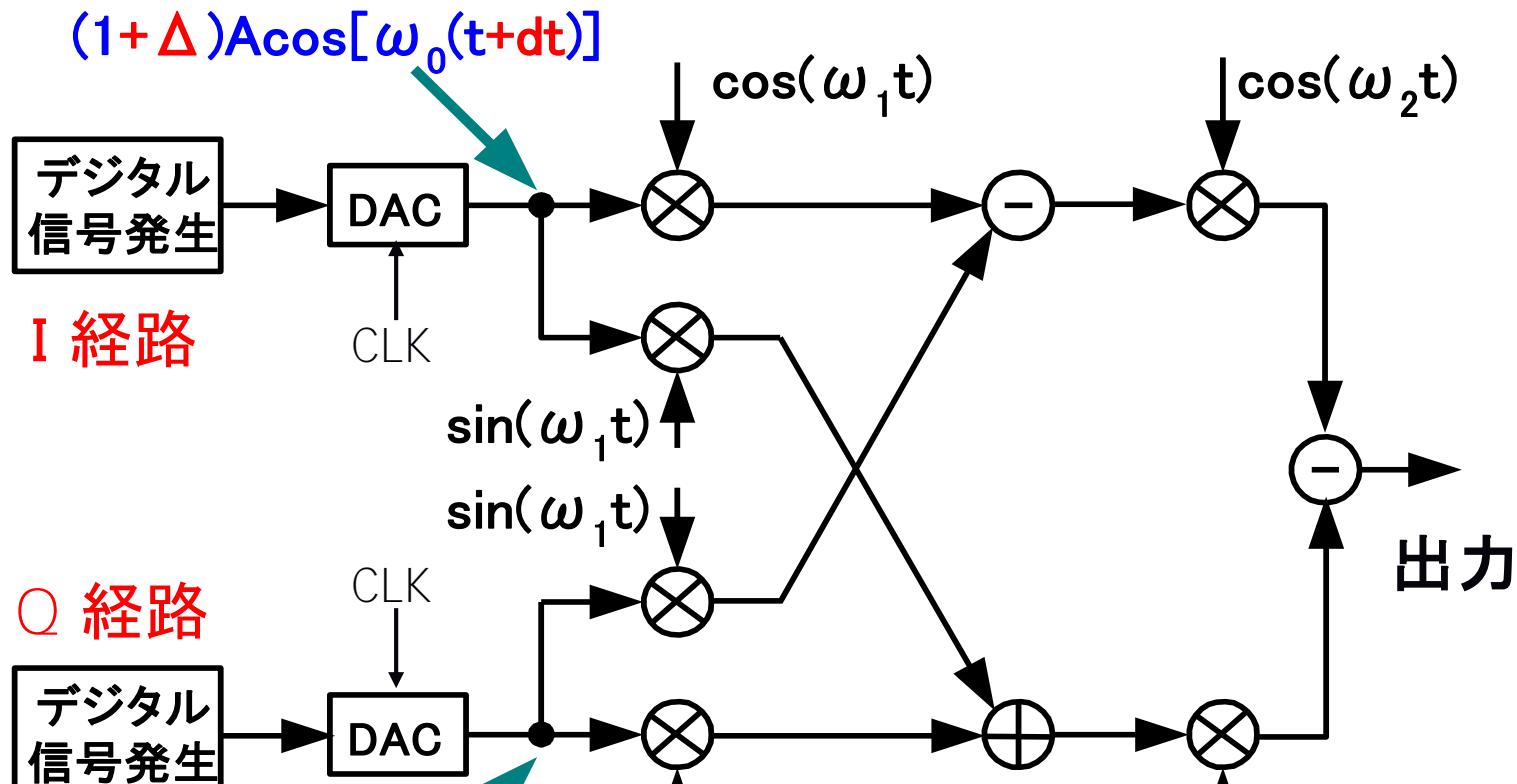

# 2ステップ・トランスマッター・アーキテクチャ

## ● アプリケーション

- ◆ 携帯電話の送信部の信号発生器

- ◆ 計測器の任意波形発生器

## ● ベースバンド・デジタル信号( $\omega_0$ )

⇒ DAC、LO、Mixer

⇒ 高周波のアナログ信号(  $\omega_0^+$      $\omega_1^+$      $\omega_2$  )

Up Conversion

# 信号発生器の周波数領域性能指標 - SFDR (Spurious Free Dynamic Range)

SFDR =

$$10 \log_{10} \left( \frac{\text{信号パワー}}{\text{最大スプuriousパワー}} \right) [\text{dB}]$$

- 信号周波数領域以外の妨害波に対する規格

- この**SFDR**の値ができるだけ大きくなるように設計する

# 信号発生器の問題点 -- I、Q 経路のミスマッチ

DA 変換器

- 素子回路(DAC, LO, Mixer)のミスマッチにより

⇒ イメージ信号が発生される(SFDR劣化)

⇒ 妨害波となる。

- アナログ回路の特性を合わせるのは困難

- ◆ 特にDAC回路の規模が大

- 従来式改善法: 可変アナログ・バンドパス・フィル

- ◆ コスト、サイズ、消費電力が大

# 新しい改善法の提案

- **I, Q** 経路(例. **2ch DAC**特性)ミスマッチを調べる。

ミラー信号によるSFDR劣化の確認。

- ミスマッチの影響を軽減する手法を提案。

**I, Q** 経路間**ダイナミック・マッチング法**により

ミラー信号を周波数領域で拡散する手法を提案。

- **MATLAB**によるシミュレーションを用いて

提案手法の有効性を確認。

## **2. I、Q 経路ミスマッチによる SFDR劣化**

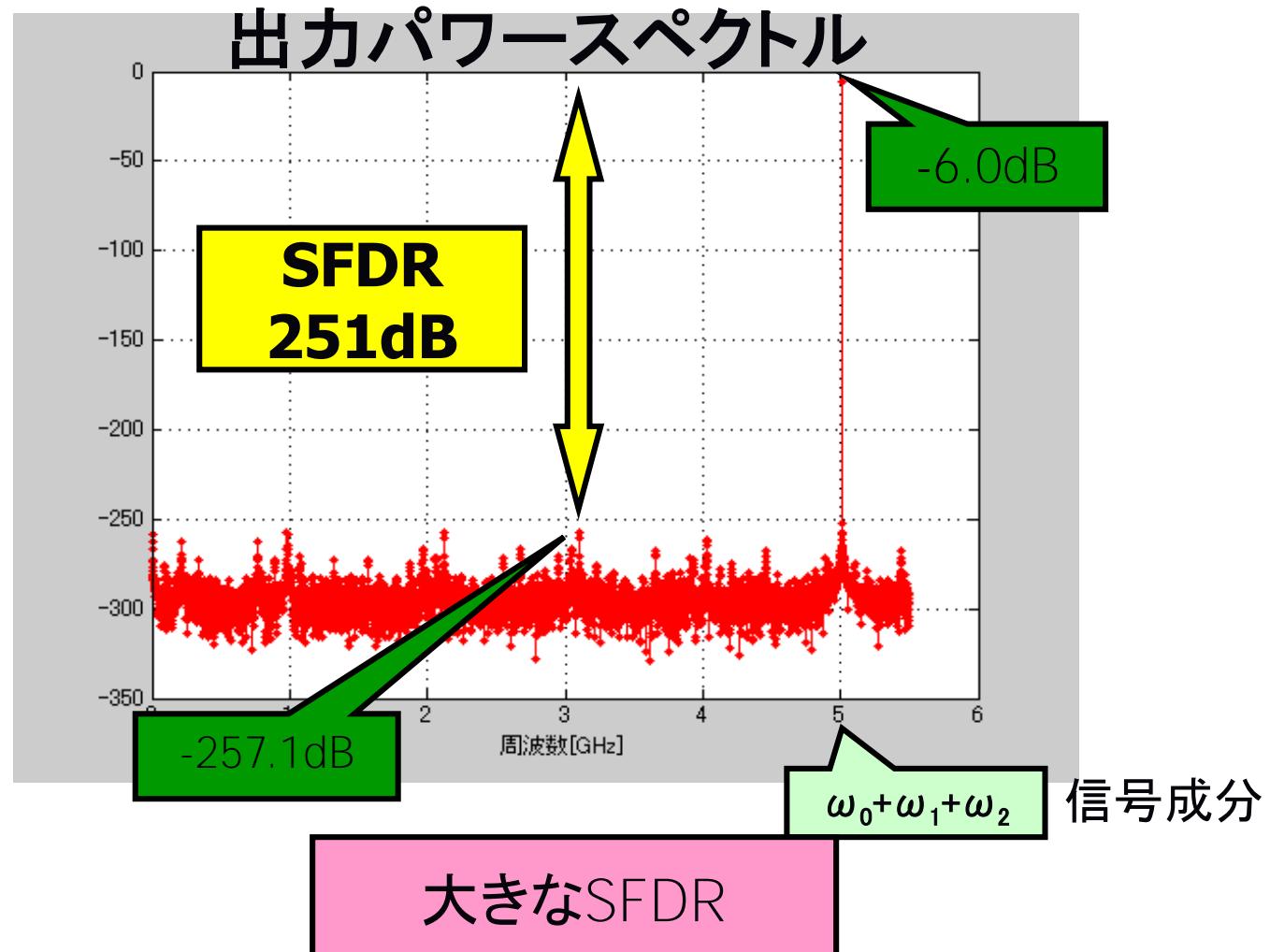

# ミスマッチがない場合

$$\frac{\omega_0}{2\pi} = 15\text{MHz} \quad \frac{\omega_1}{2\pi} = 1\text{GHz} \quad \frac{\omega_2}{2\pi} = 4\text{GHz}$$

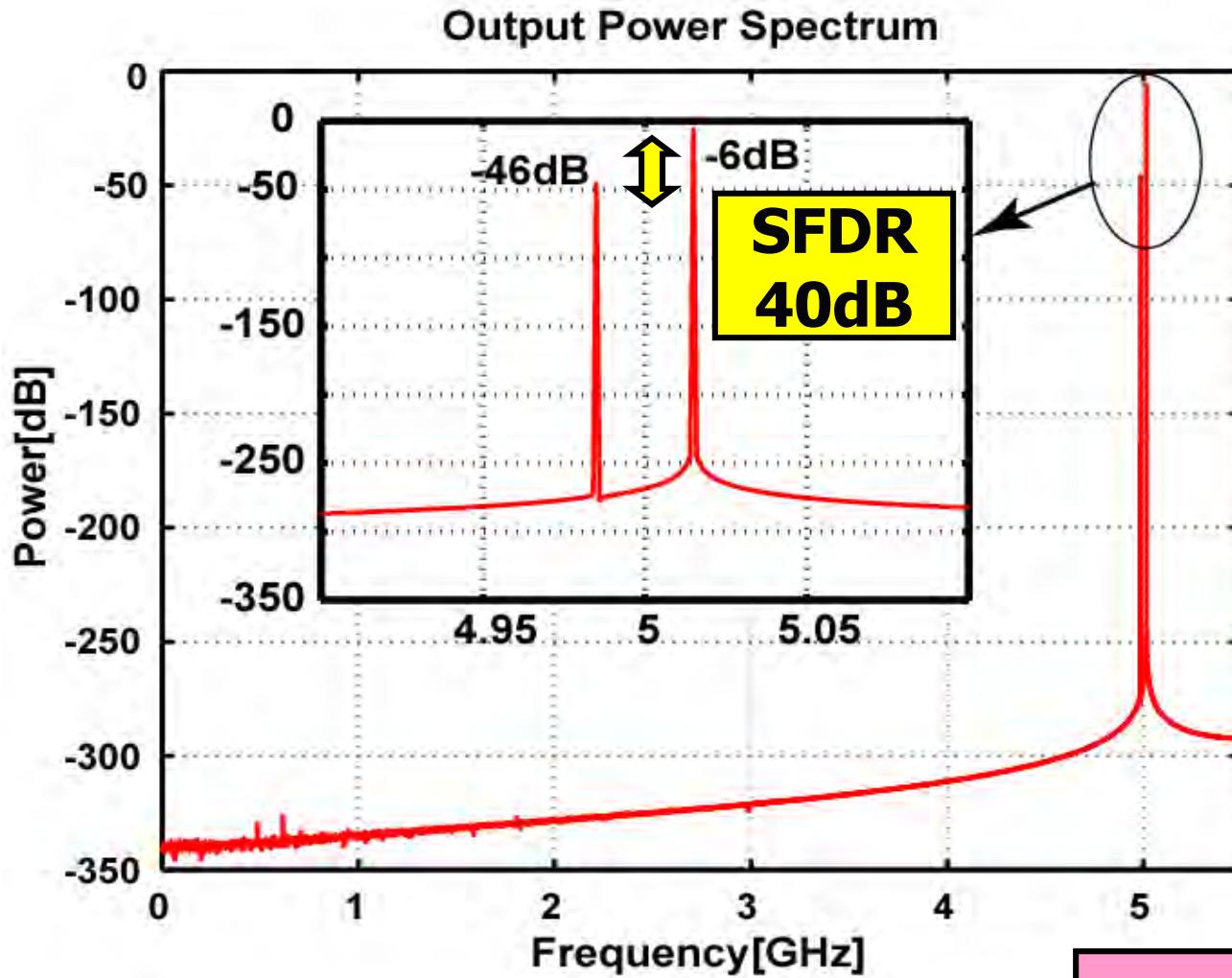

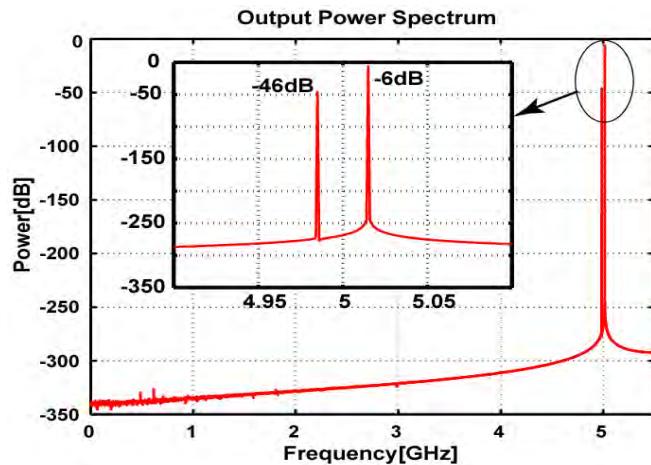

# ミスマッチがない場合の出力スペクトル

# 一段目のLOのゲイン・ミスマッチ

$$= 0.01$$

# 一段目のLOのゲイン・ミスマッチ

SFDRが大きく劣化

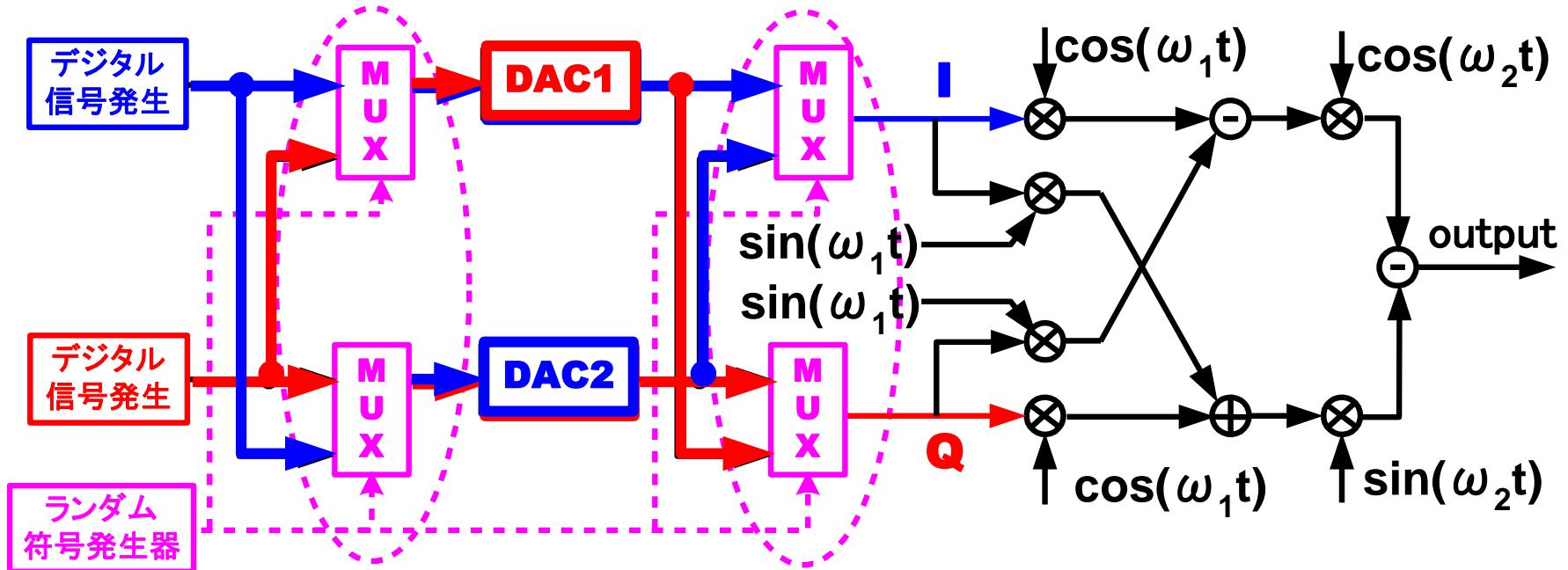

# DACのゲイン・ミスマッチ、タイミング・スキュー

$$(1 + \Delta) A \cos[\omega_0(t + dt)]$$

$$= 0.01$$

$$\omega_0 dt = 6.28 \times 10^{-3}$$

# DACのゲイン・ミスマッチ、タイミング・スキュー

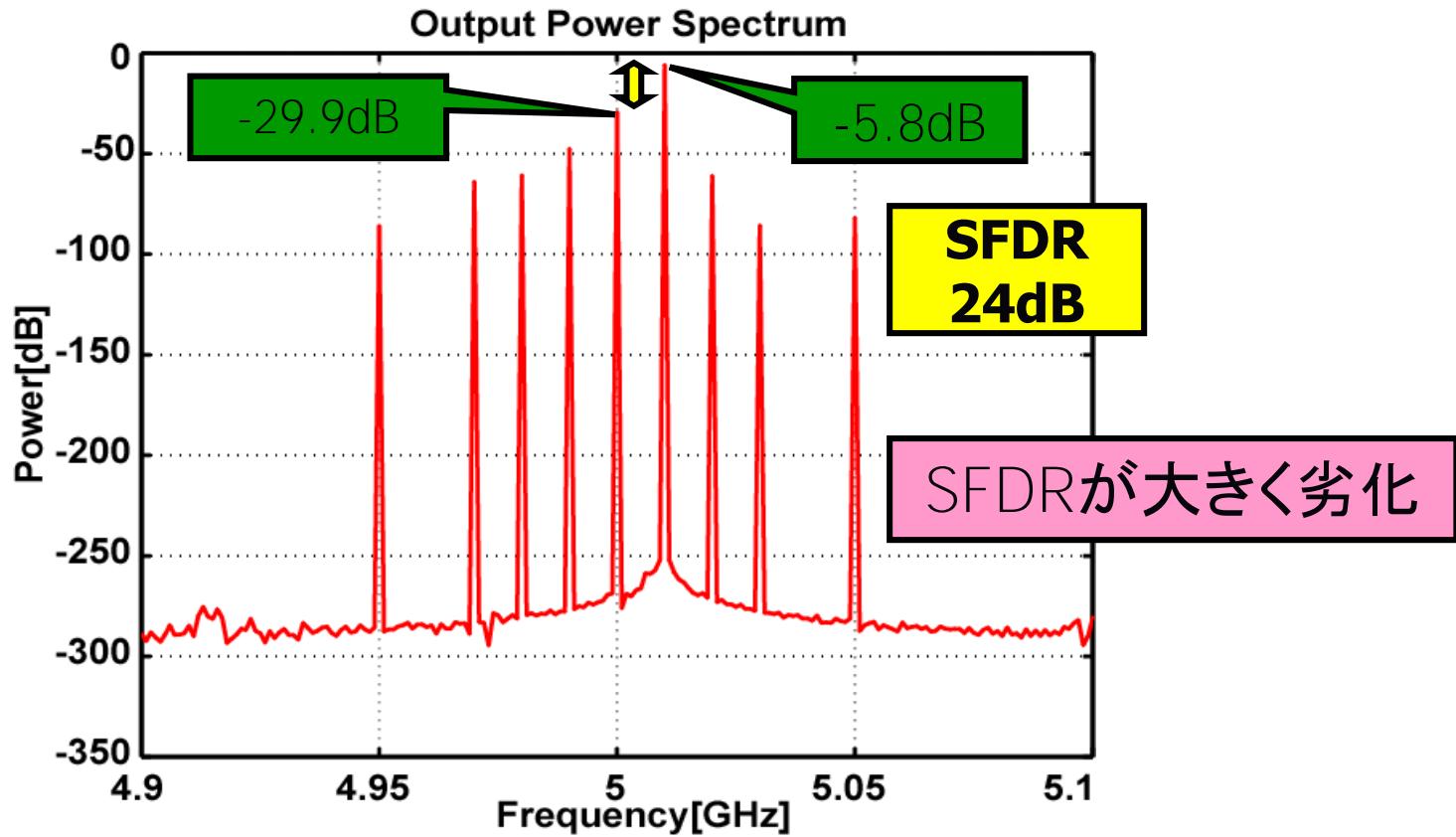

SFDRが大きく劣化

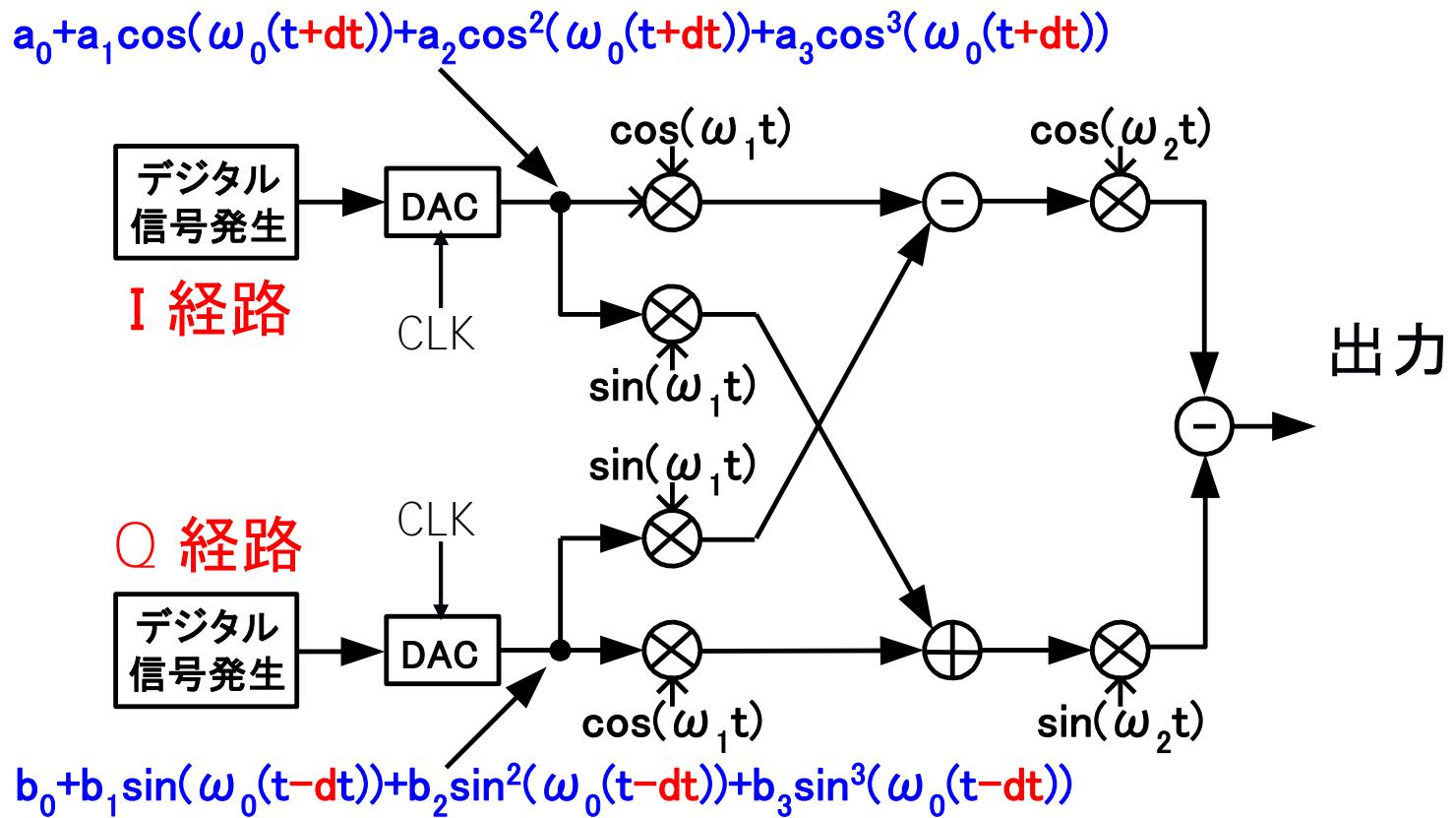

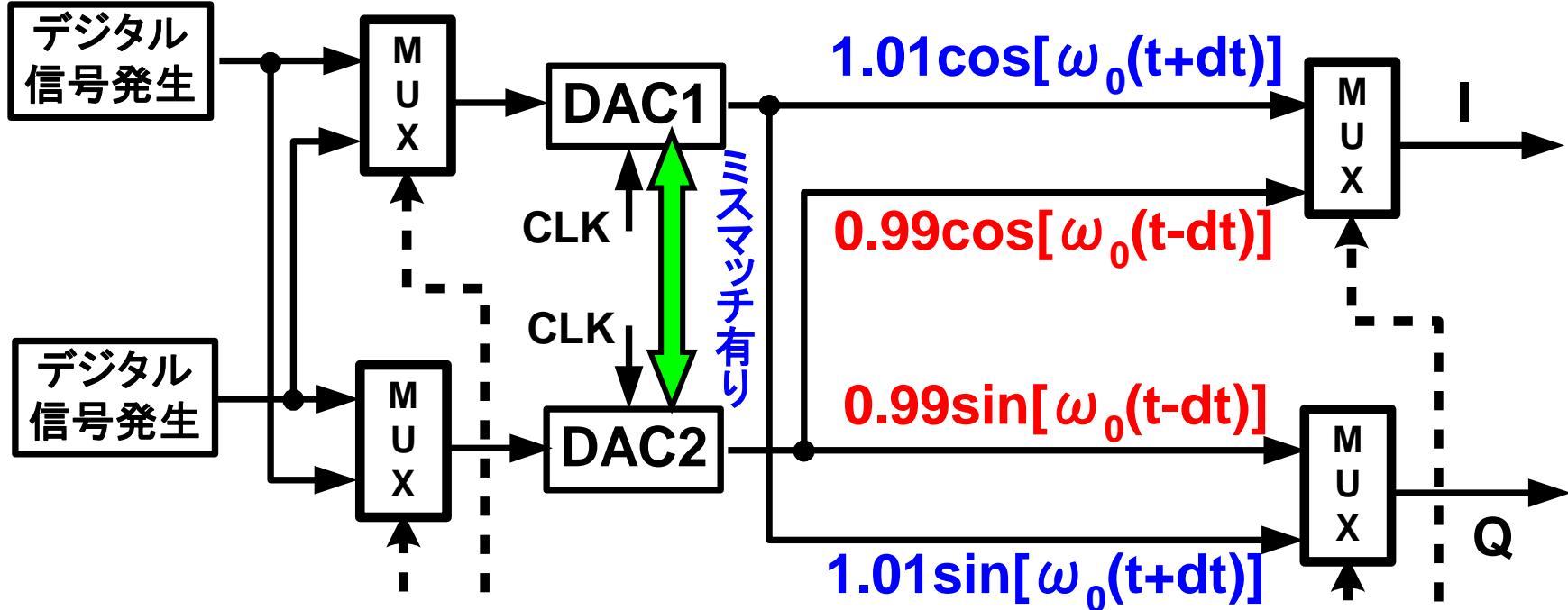

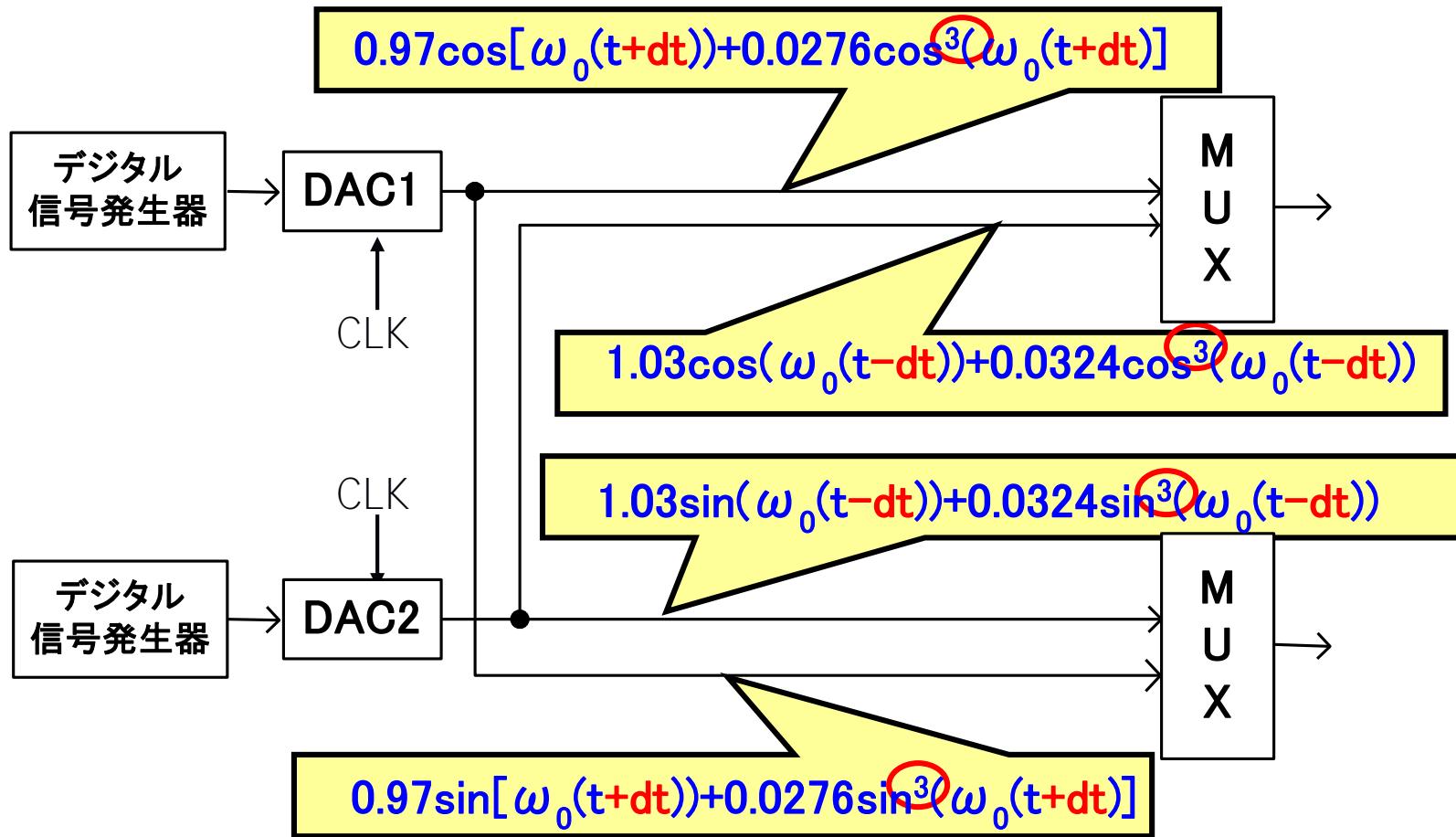

# DACのゲイン、二次歪、三次歪のミスマッチ タイミング・スキュー

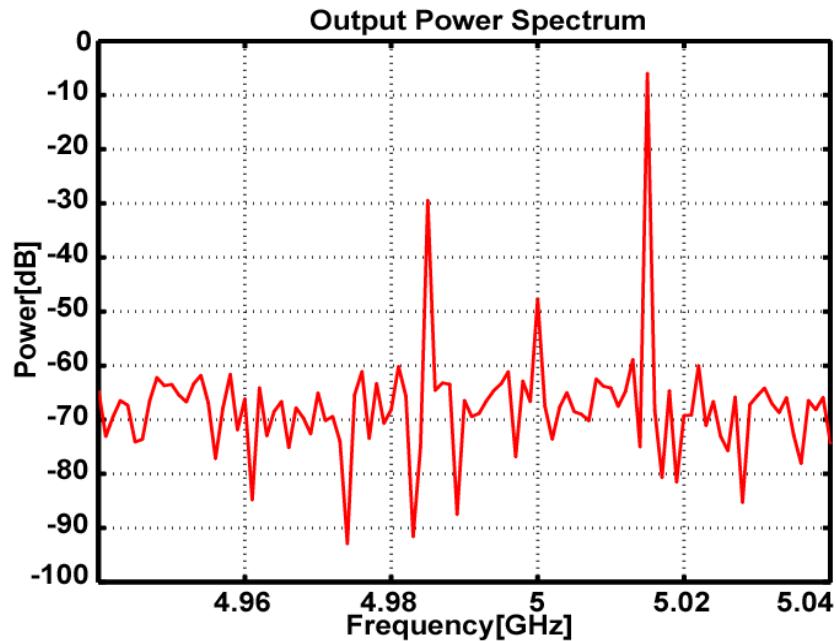

# DACのゲイン、二次歪、三次歪のミスマッチ タイミング・スキュー

多くのスプライアスが発生！

従来式改善法：複雑なアナログフィルタが必要

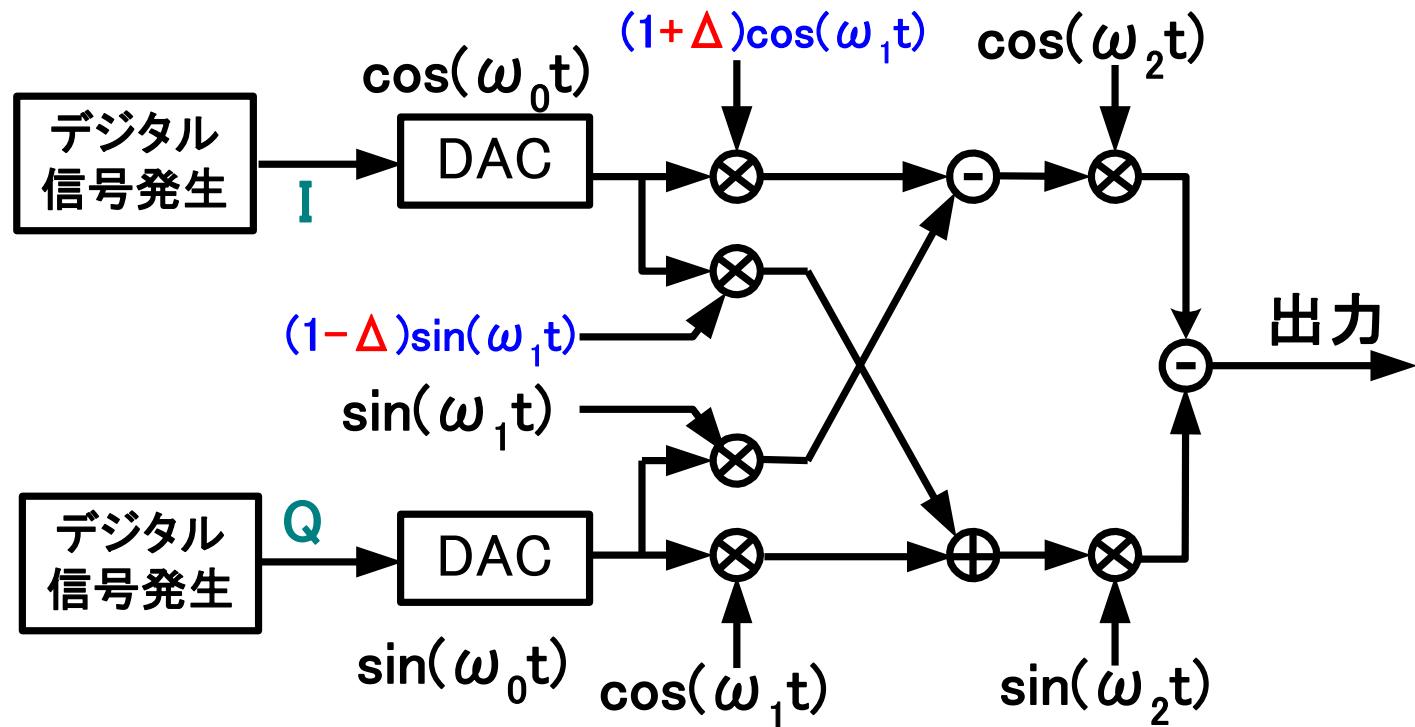

### **3. ダイナミック・マッチングによる SFDR向上手法の提案**

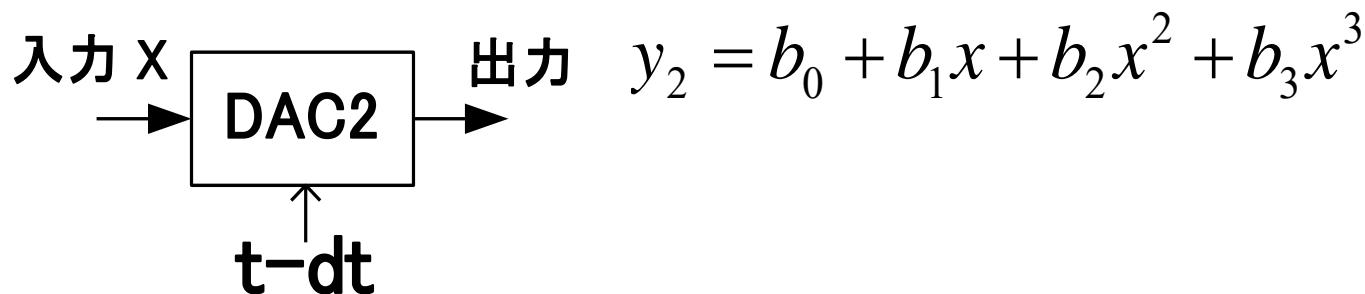

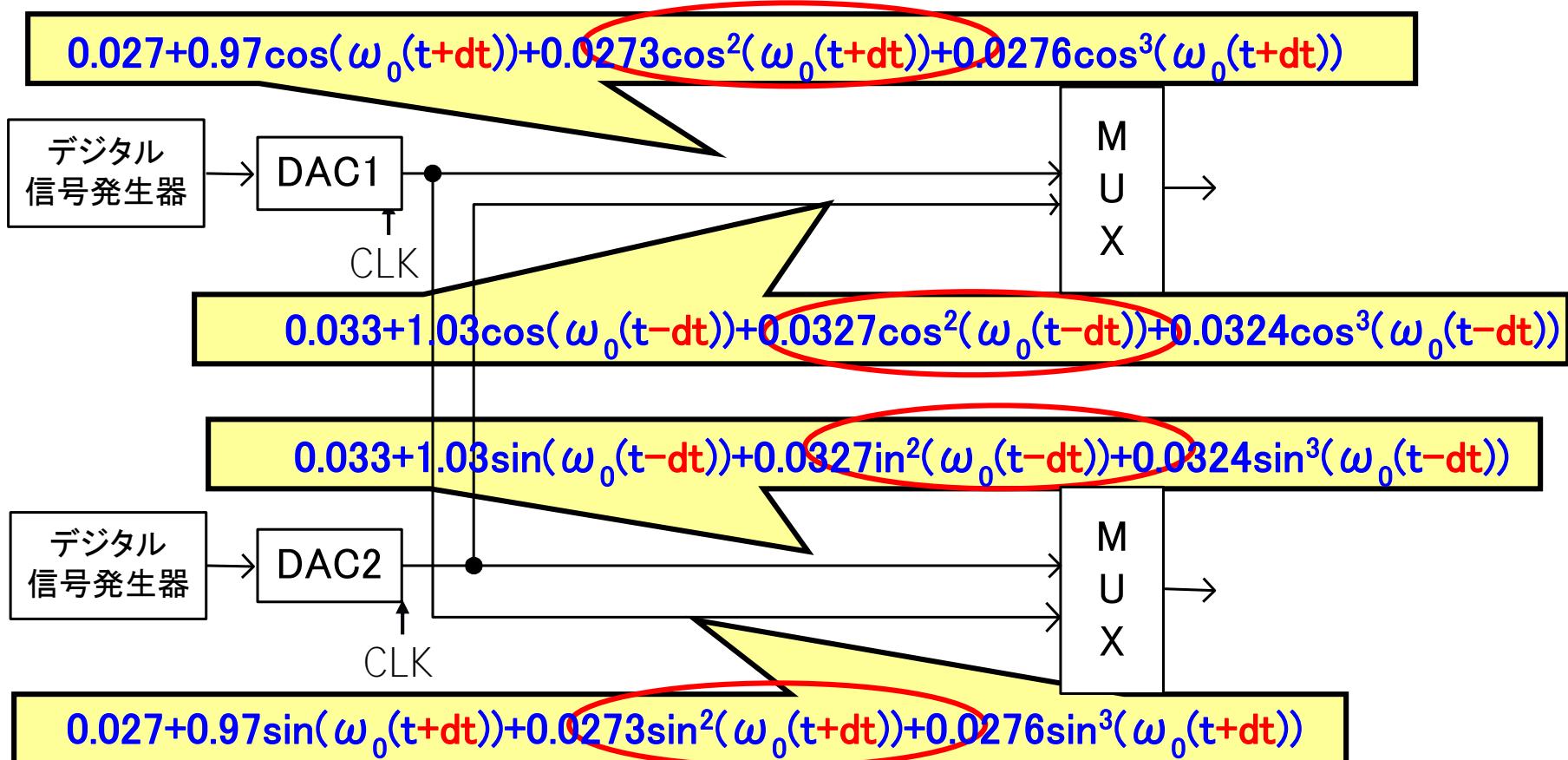

# 2ch DA変換器の入出力特性ミスマッチ

オフセット  $a_0 \neq b_0$  , ゲイン  $a_1 \neq b_1$

二次歪  $a_2 \neq b_2$  , 三次歪  $a_3 \neq b_3$

タイミング・スキュー  $dt \neq 0$

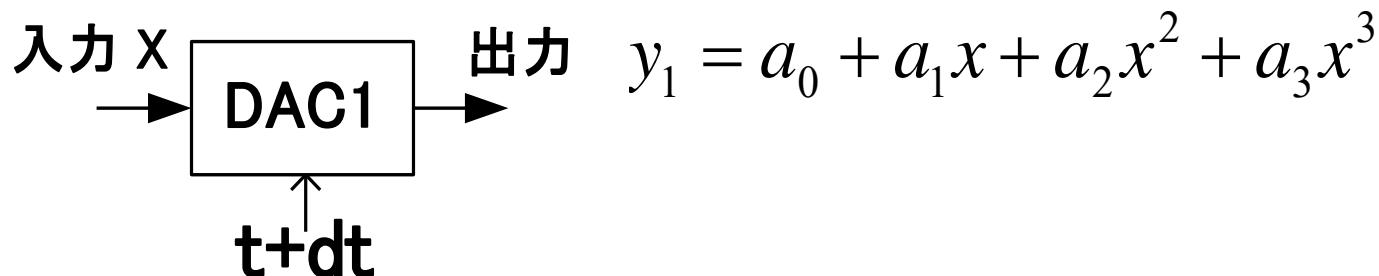

# 2ch DAC に対しダイナミック・マッチングを用いた回路の提案

- 2Ch DACの前後にMUXを加える。

- デジタル信号よりMUXをコントロールする。

- DAC1,2はI,Q経路に交互で用いられる。

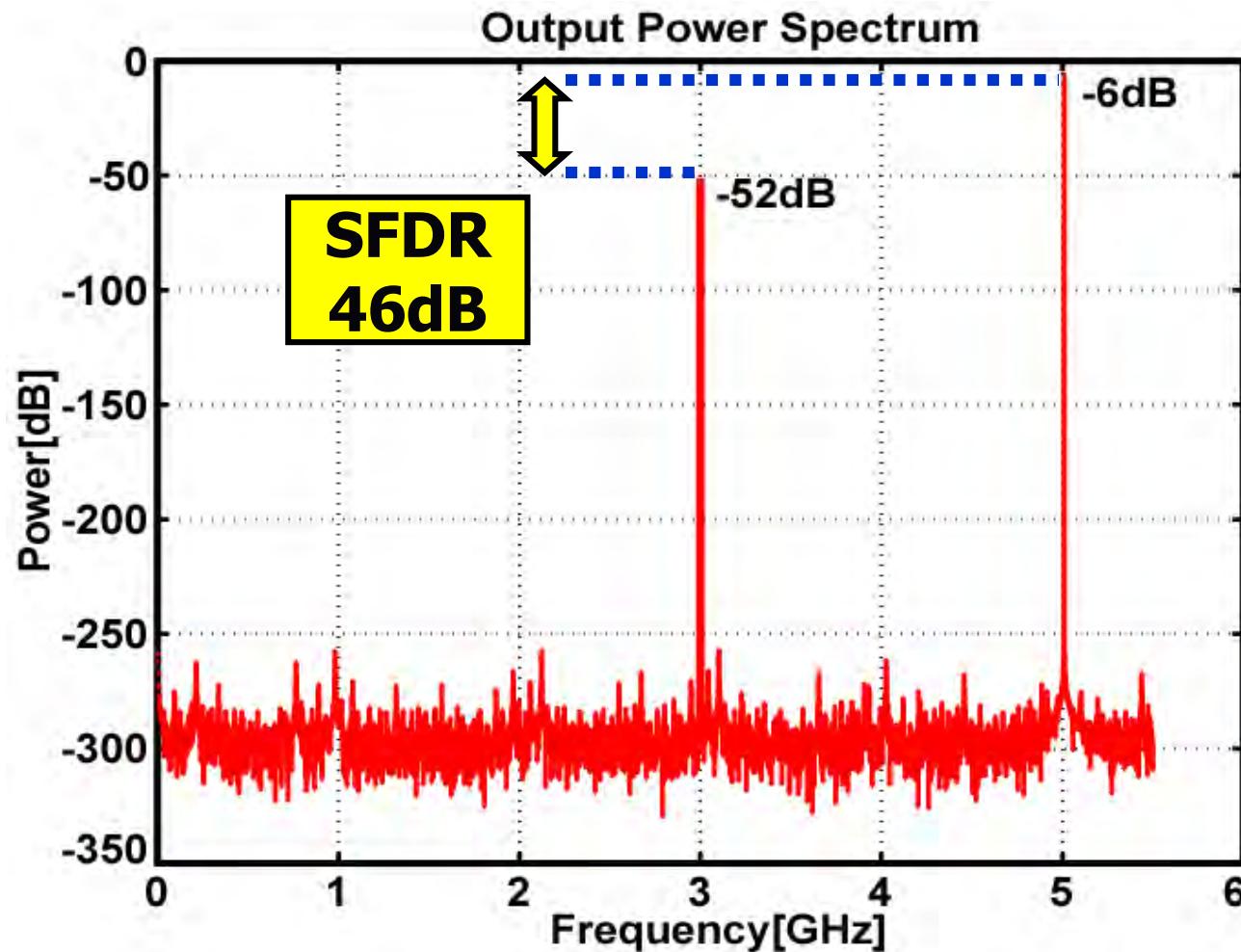

# DACのゲイン・ミスマッチ、タイミング・スキューの場合

選択信号

① 1サイクル毎に切り換える場合

② 擬似ランダムに切り換える場合

# 1サイクル毎にMUXを切り換える場合

出力パワースペクトル

SFDRは改善しない

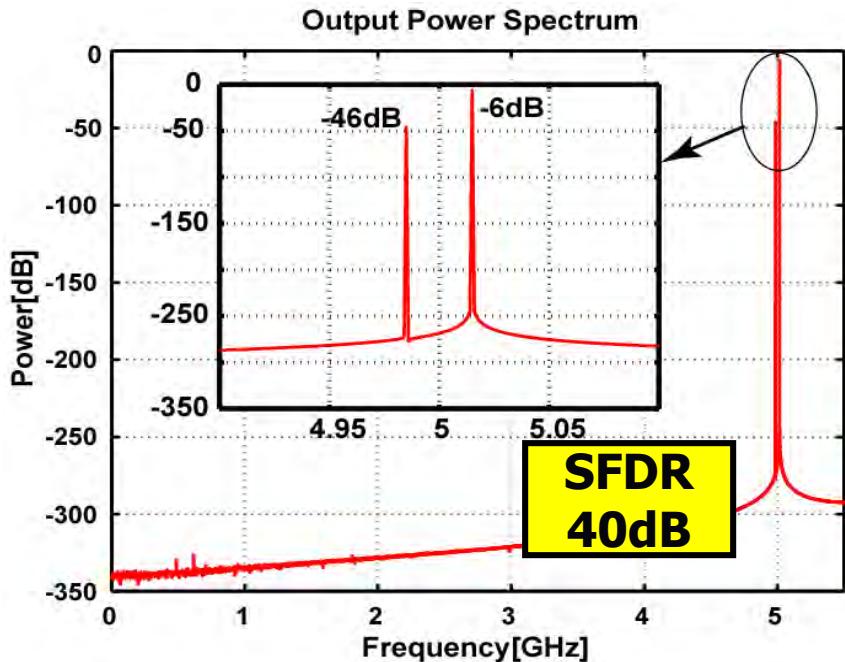

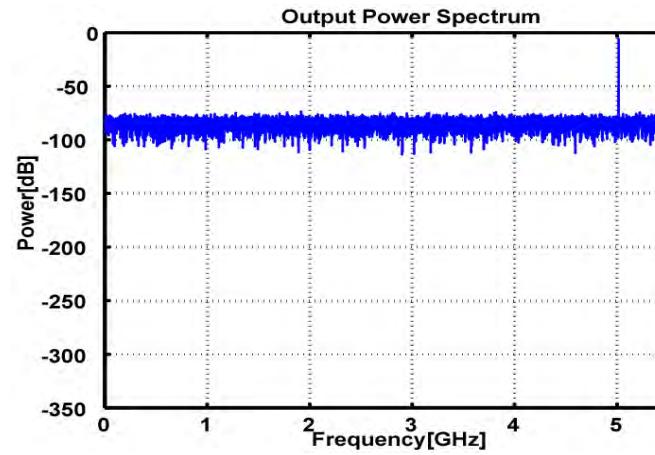

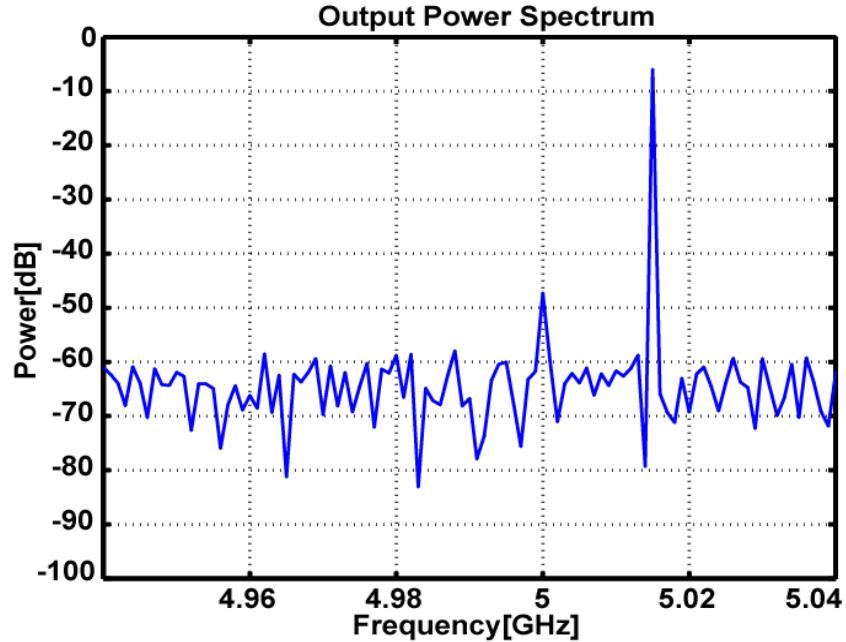

# 擬似ランダムにMUXを切り換える場合

ミスマッチがある場合

提案手法を用いる場合

SFDRが27dB向上

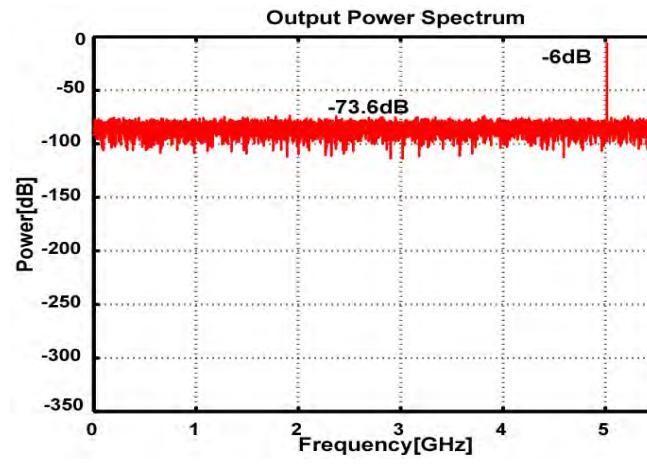

# 10bit DACの量子化ノイズも考慮する場合

量子化

ノイズ

無し

量子化

ノイズ

あり

ミスマッチがある場合

提案手法を用いる場合

量子化ノイズはノイズフロアを上昇させるのみ。

提案手法を用いる場合、**DAC**量子化ノイズに影響されない。

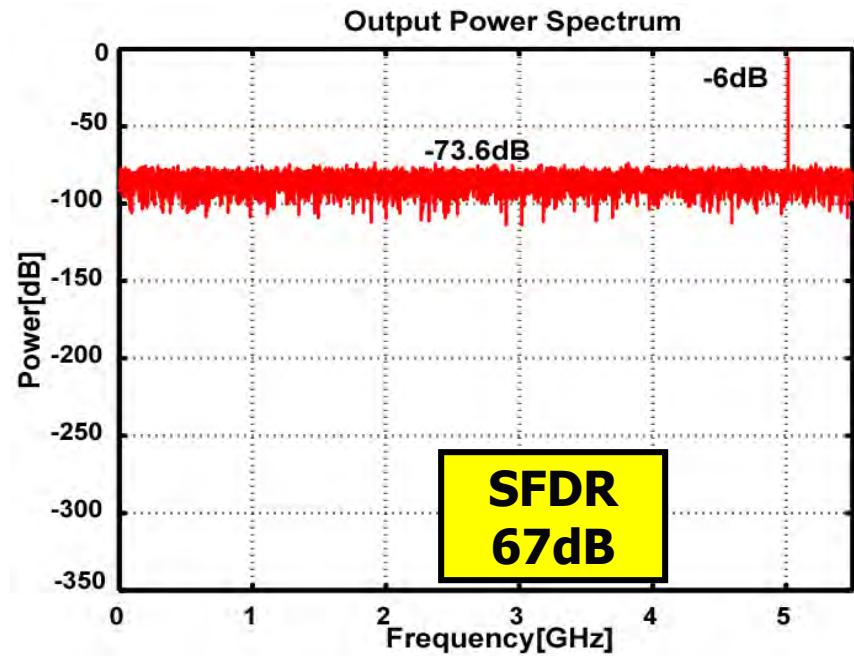

# 提案手法の効果

- DACのミスマッチがある場合 SFDR = 40dB

- 1サイクル毎に切り換えるMUX SFDR = 40dB

- 擬似ランダムで切り換えるMUX SFDR = 67dB

**MUX**を擬似ランダムに切り換えることで

**SFDR**は大きく向上

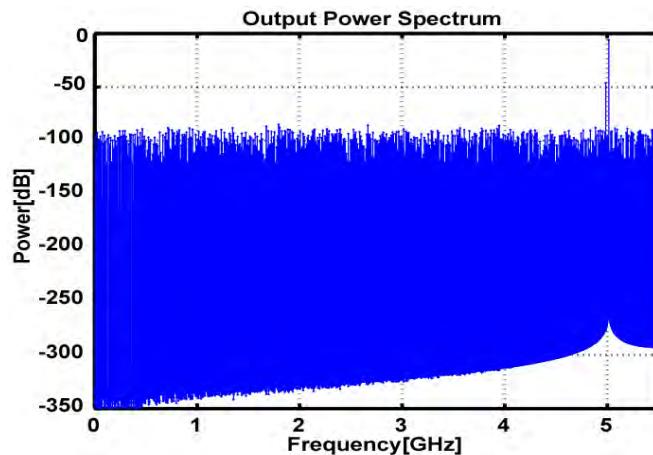

# DACのゲイン、三次歪のミスマッチ、タイミング・スキーがある場合

# DACのゲイン、三次歪、タイミング・ミスマッチの場合

ミスマッチがある場合

**SFDR=23.5dB**

提案手法を用いる場合

**SFDR=41.3dB**

提案手法でSFDRが17.8dB向上

# 二次歪のミスマッチも加えた場合

# 二次歪のミスマッチも加えた場合

## 出力パワースペクトル

SFDRは改善しない

# 差動出力DAC

差動回路の場合

$$V_{sig} = V_{sig+} - V_{sig-}$$

ここで、 $V_{sig+} = a_0 + a_1x + a_2x^2 + a_3x^3$

$V_{sig-} = a_0 + a_1(-x) + a_2(-x)^2 + a_3(-x)^3$ とおくと、

$$V_{sig+} - V_{sig-} = 2a_1x + 2a_3x^3$$

となる。

二次歪は差動構成でキャンセルされる。

三次歪が主要歪

# ランダム信号発生回路

M系列発生器回路

# M系列発生器のタイミング・チャート

# まとめ

2ステップ構成の送信機・任意波形発生器で

- I, Q経路ミスマッチによるスプリアス発生を確認

- ダイナミック・マッチング手法で

- ✓ I, Q経路DACのゲインと三次歪のミスマッチ、タイミングスキーによりSFDR劣化が改善

- ✓ 二次歪の影響は改善できない

差動出力DACを用いれば二次歪なし

提案手法の有効性が示された

簡単なデジタル手法でアナログ回路の性能を改善した

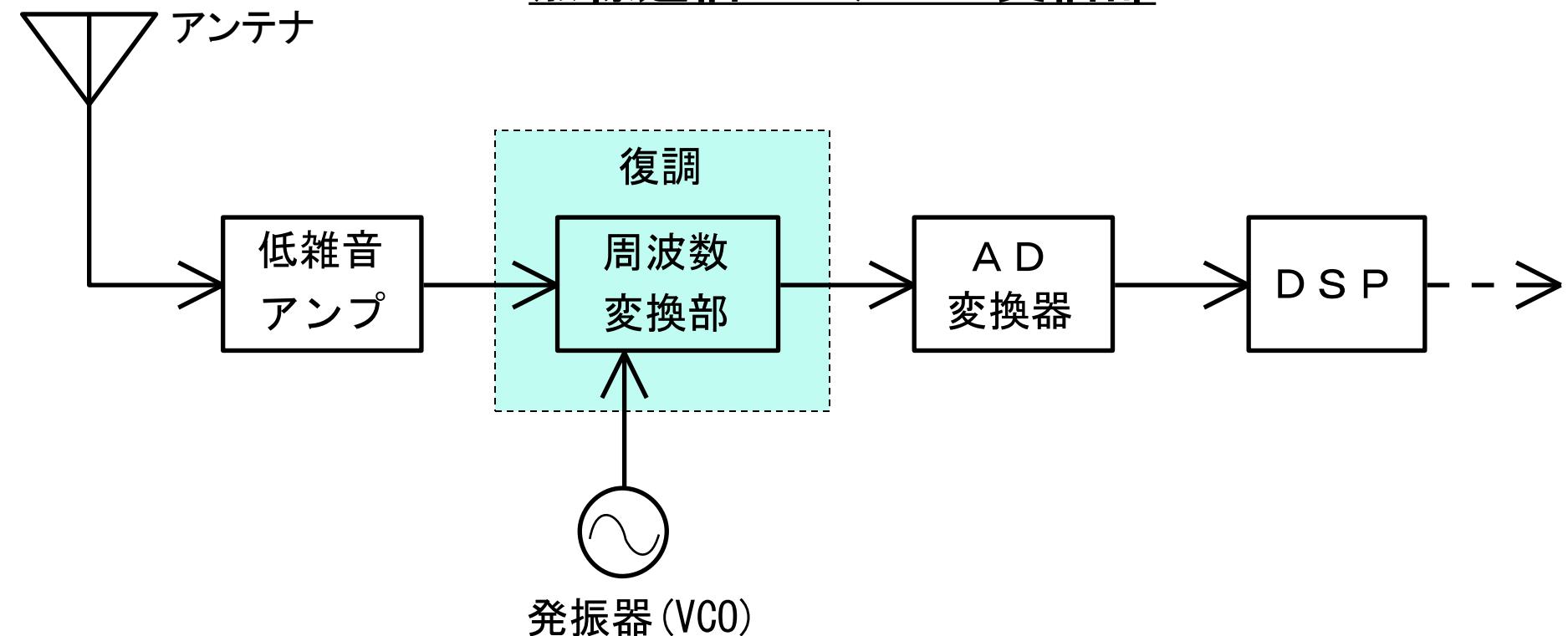

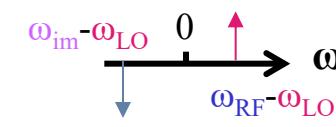

# 1. CMOS RF回路

## 無線通信システムの受信部

高い周波数の入力信号を低い周波数に変換

# (a) 周波数変換部アーキテクチ

- Weaver Architecture

- Hartley Architecture

- Low IF Architecture

解析、CMOS回路の設計

シミュレーションを行った。

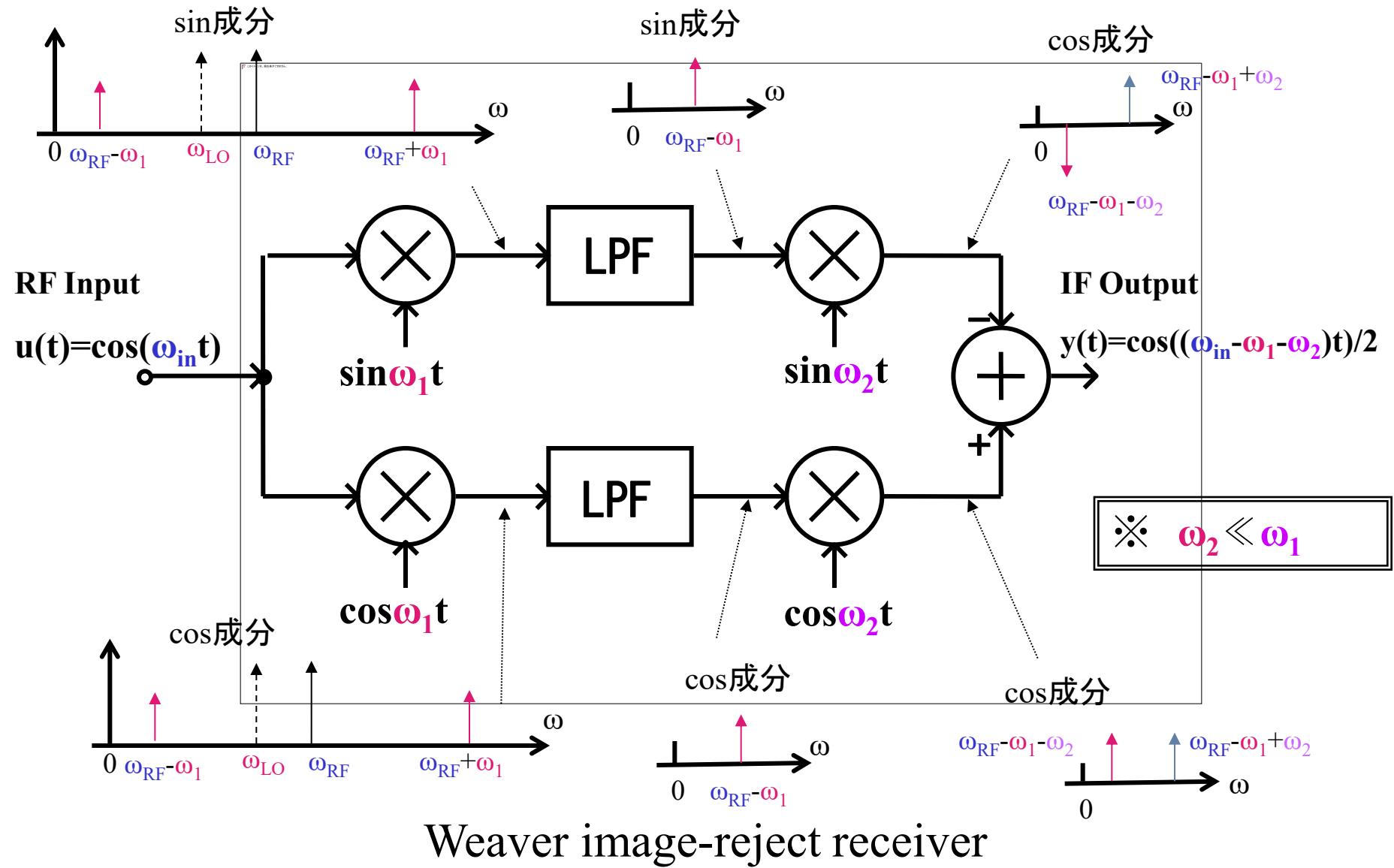

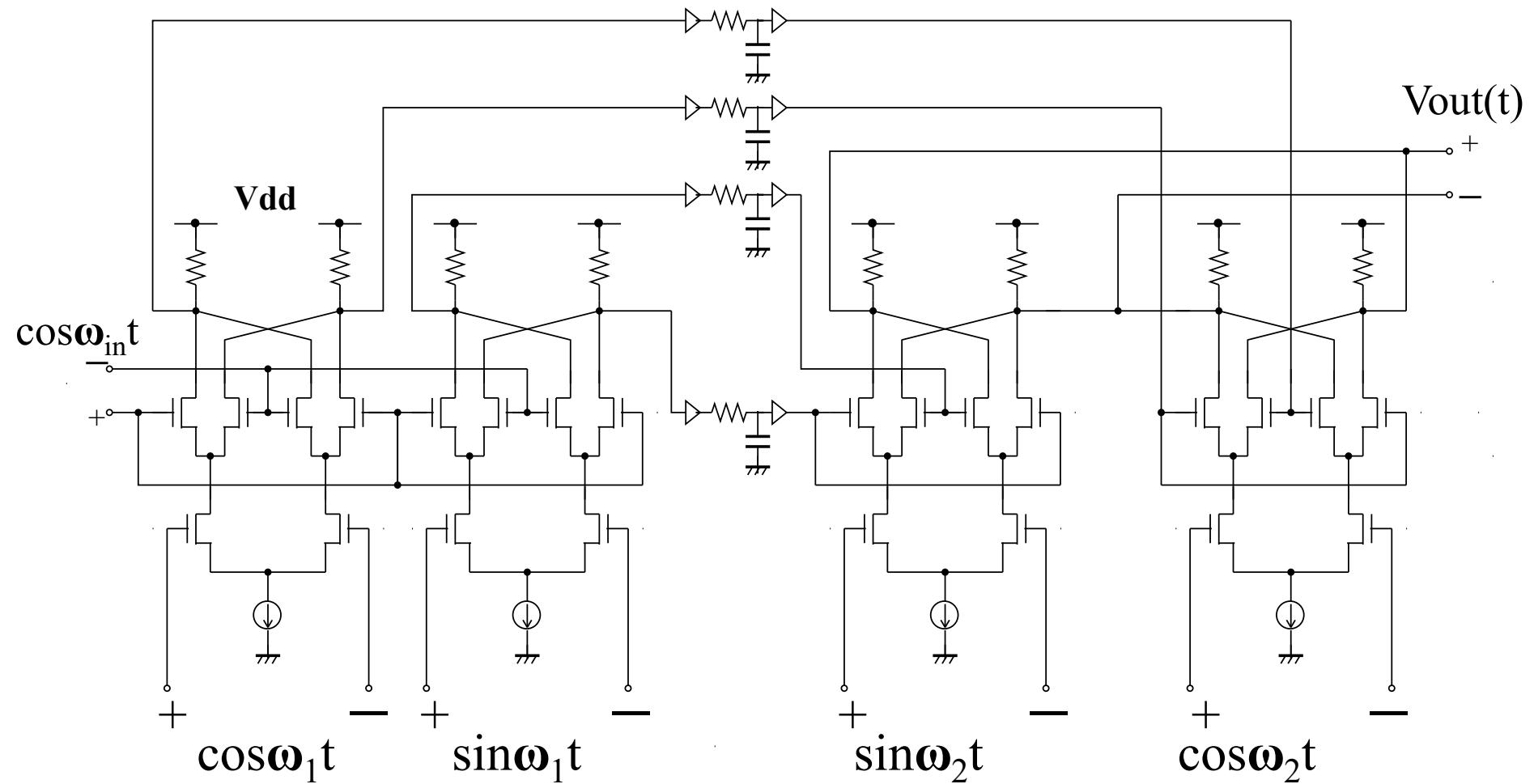

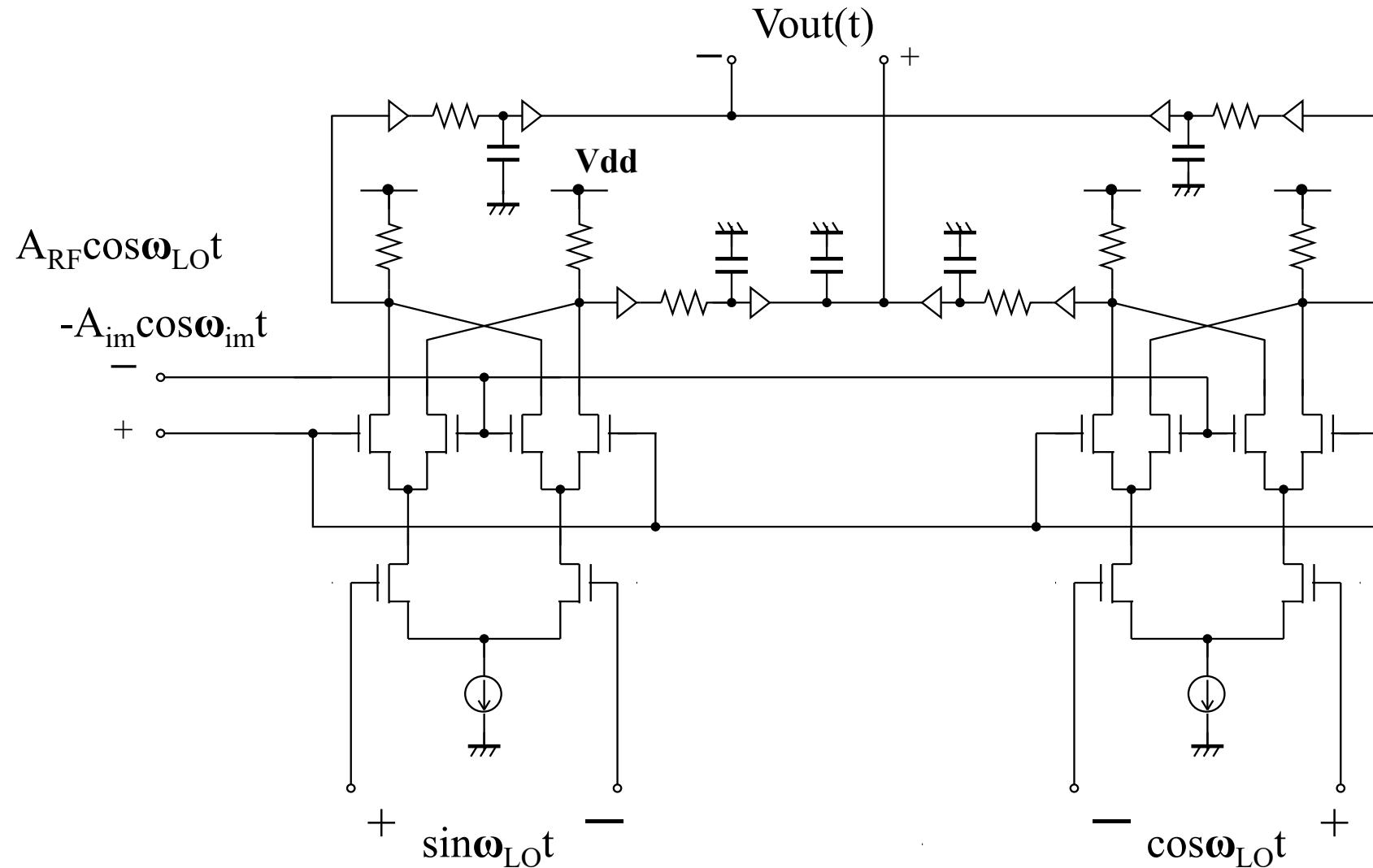

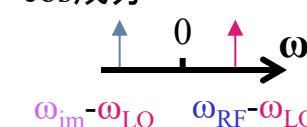

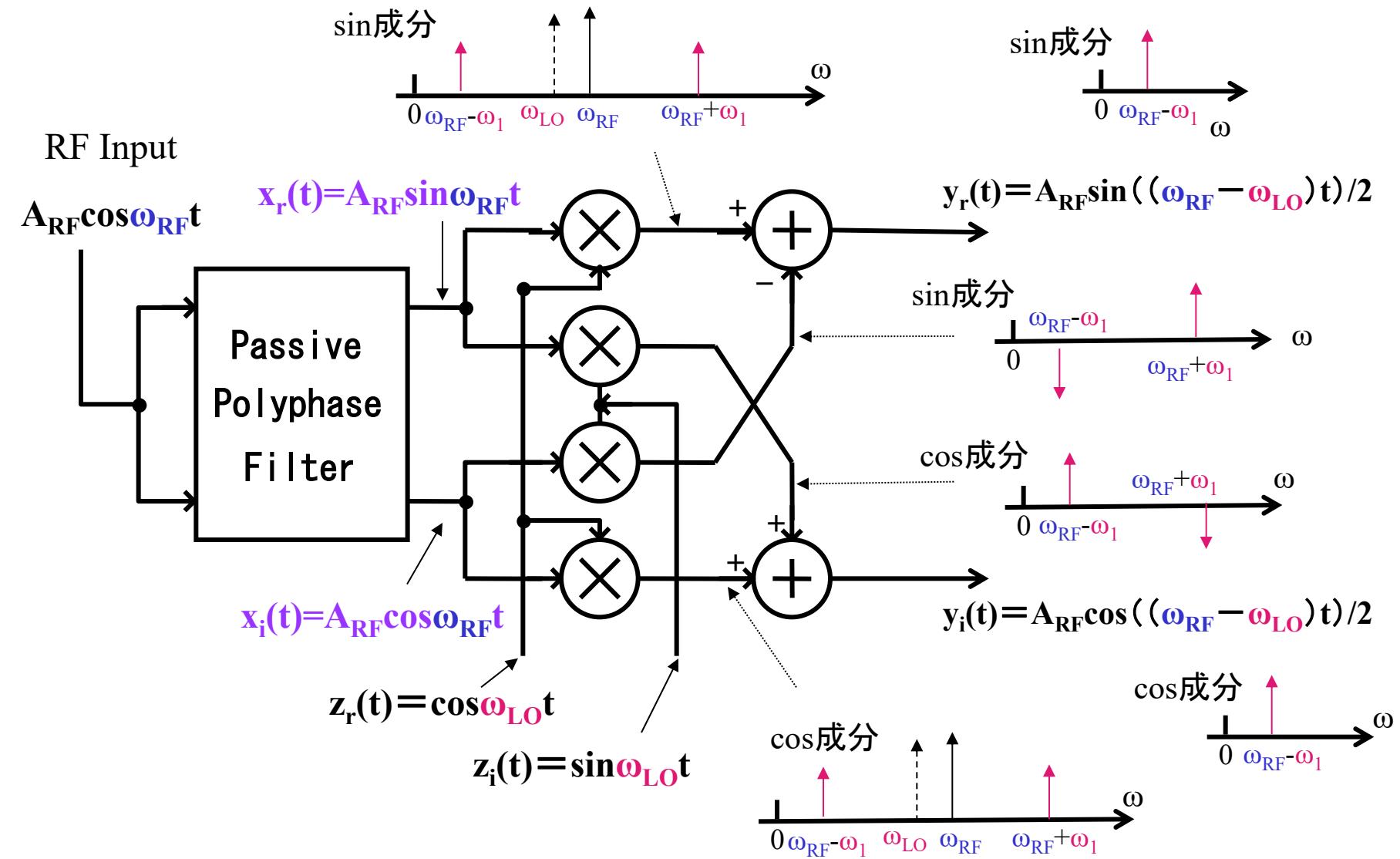

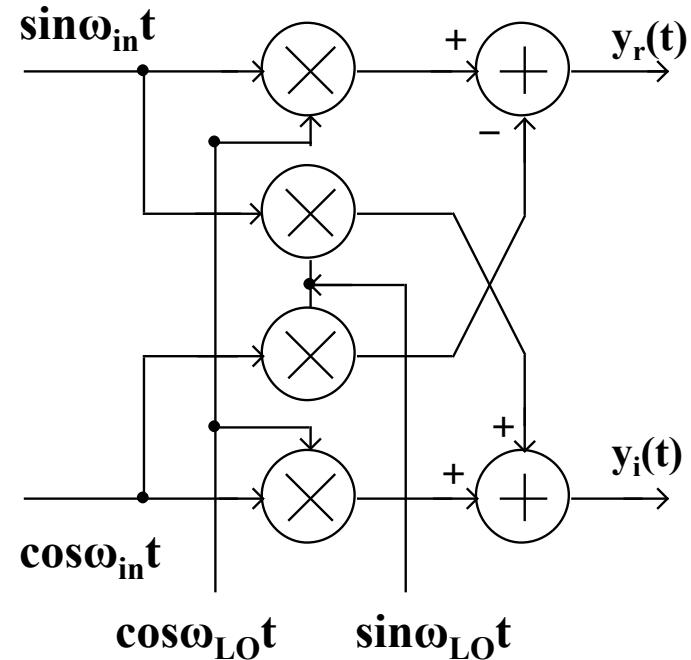

# Weaver Architectureの解析

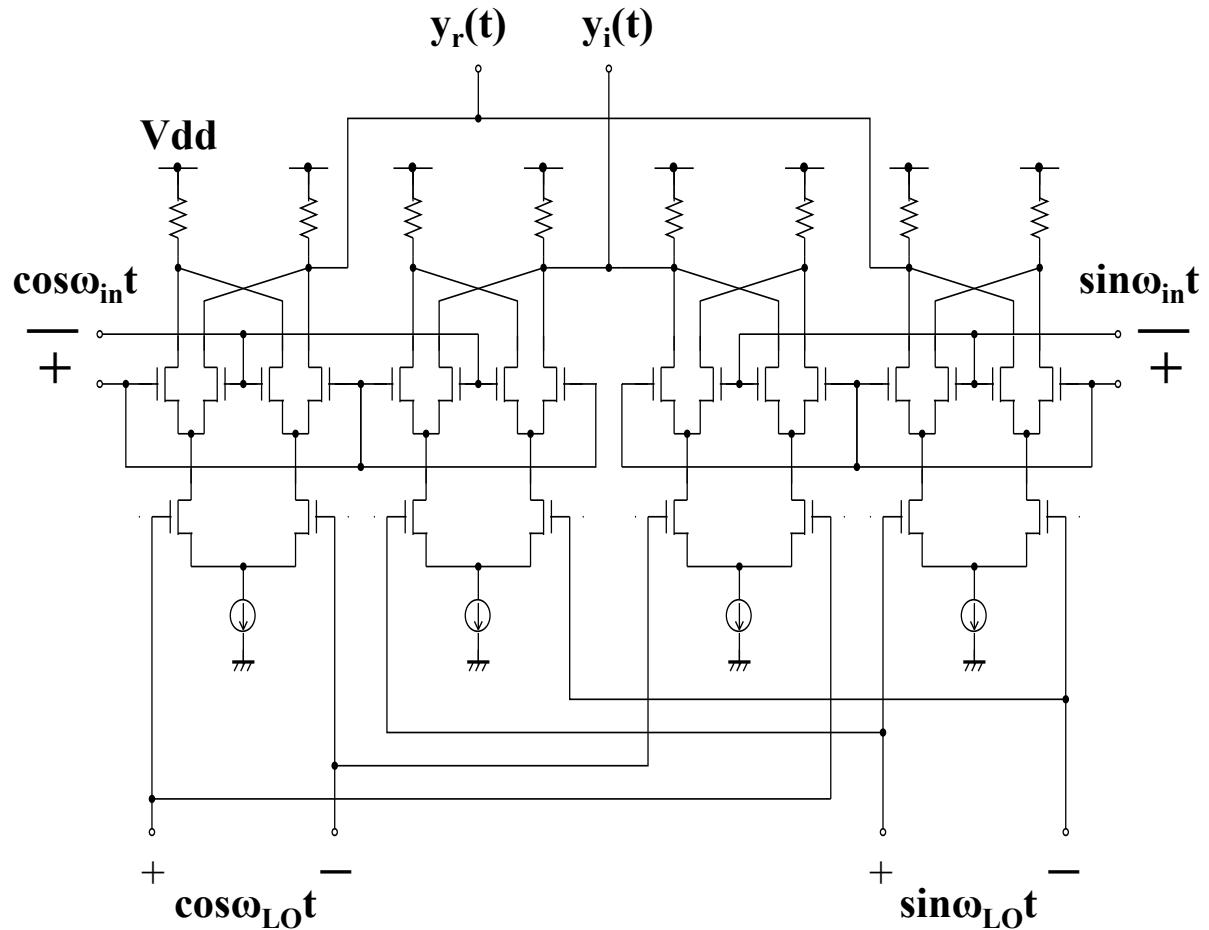

# CMOS回路の設計

ギルバート乗算器を利用

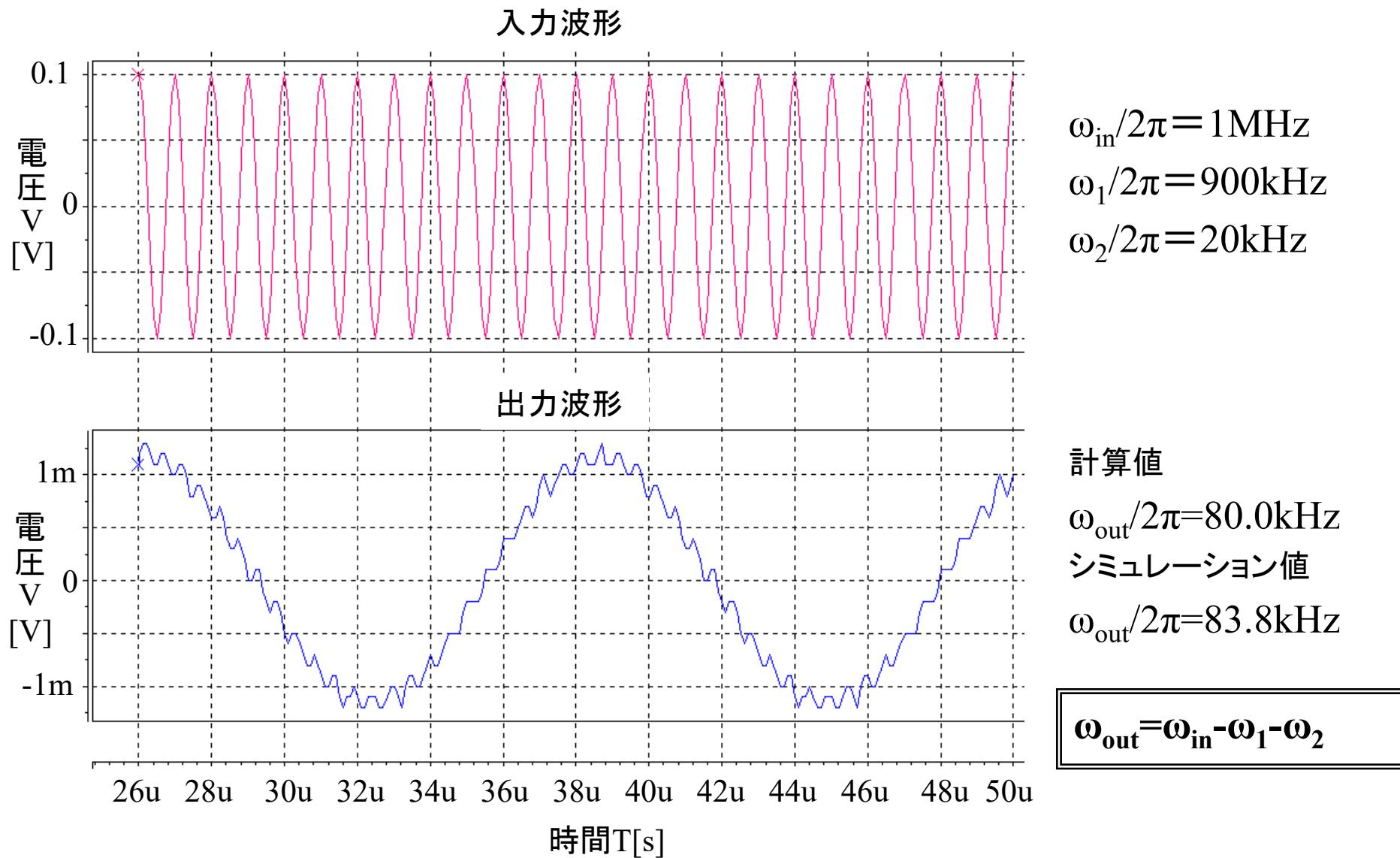

# 時間領域シミュレーション結果

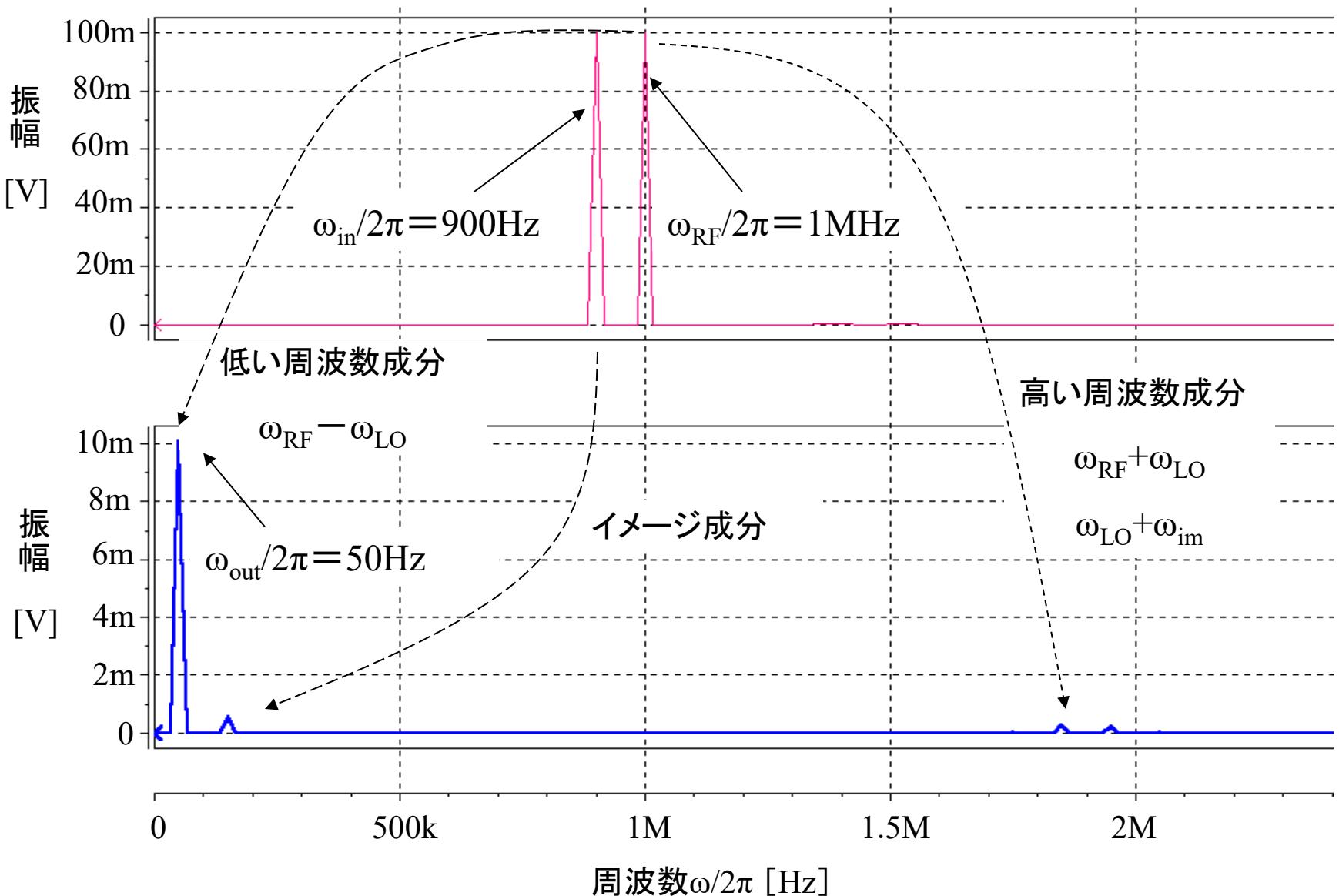

# 周波数領域シミュレーション結果

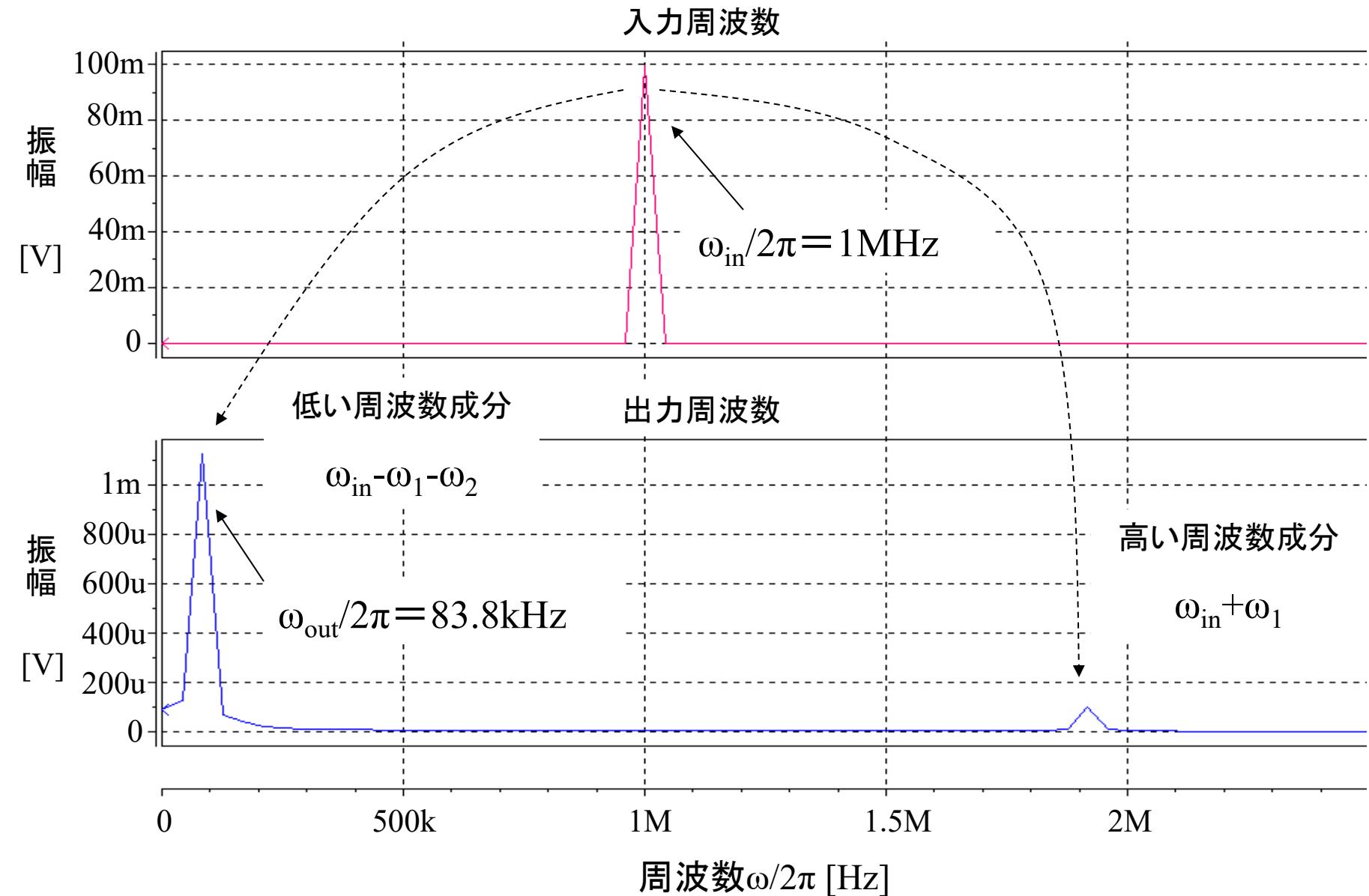

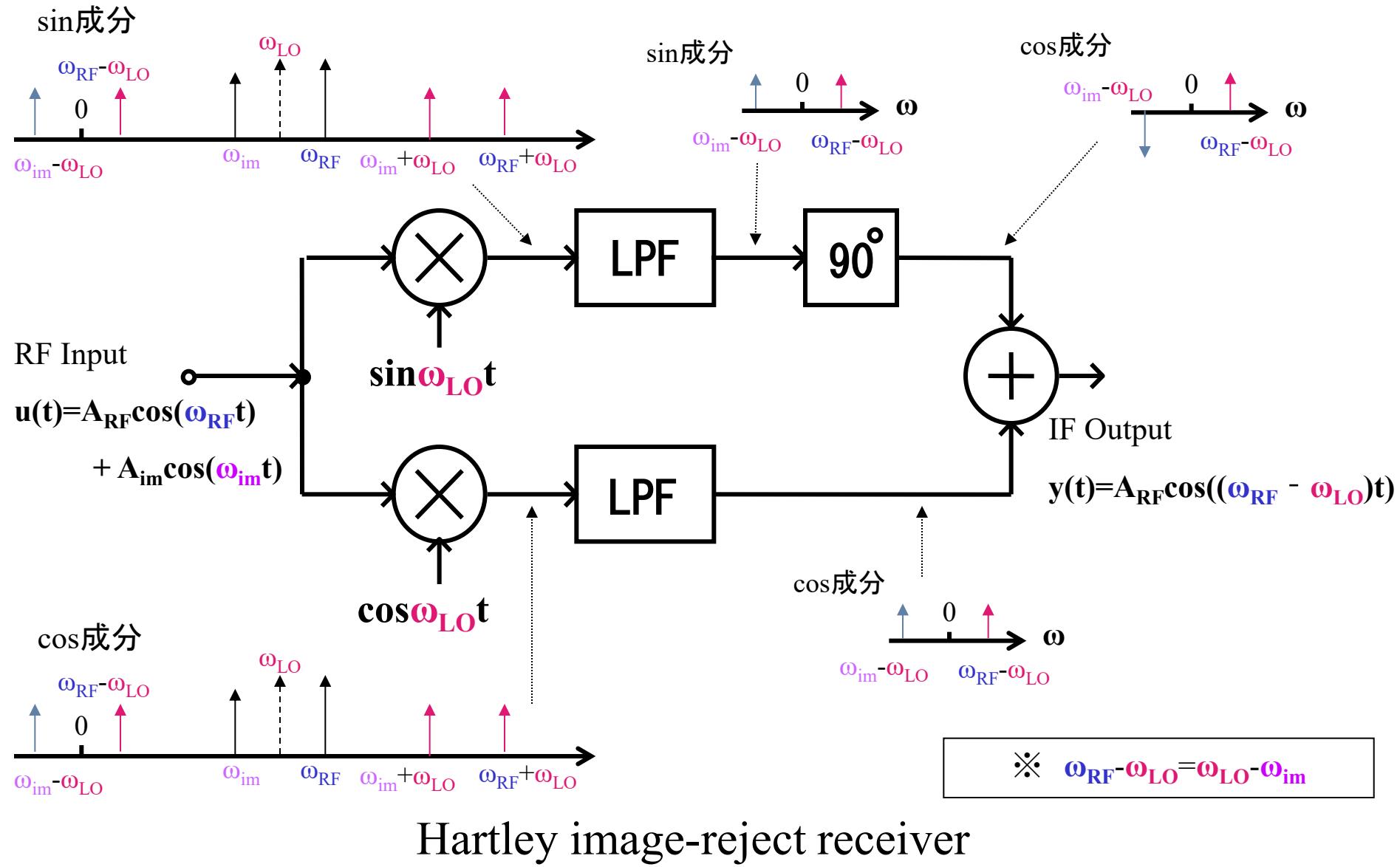

# Hartley Architectureの解析

# CMOS回路の設計

ギルバート乗算器を利用

# 時間領域シミュレーション結果

# 周波数領域シミュレーション結果

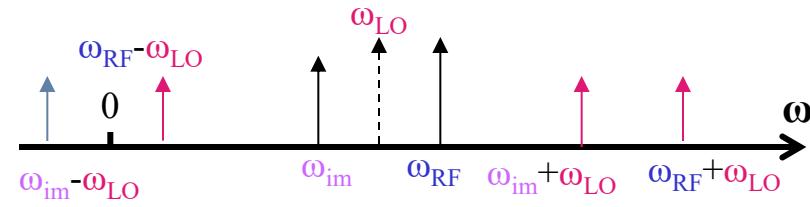

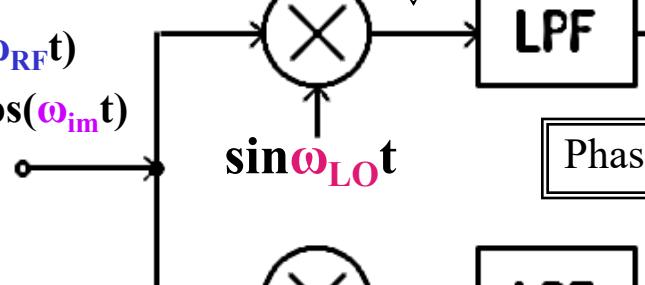

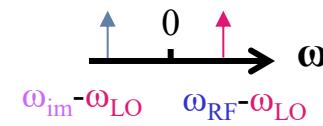

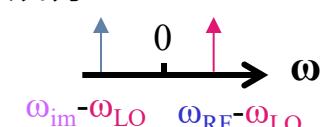

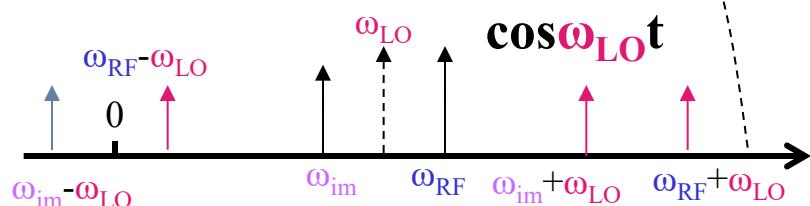

# Hartley Architectureの解析2

sin成分(正の領域)

RF Input

$$u(t) = A_{RF} \cos(\omega_{RF} t) + A_{im} \cos(\omega_{im} t)$$

sin成分

$$\because \omega_{RF} - \omega_{LO} = 1/RC$$

sin成分

IF Output

$$y(t) = -A_{RF} \sin((\omega_{RF} - \omega_{LO})t - \pi/4)$$

cos成分(正の領域)

\*実信号は0で対象の周波数領域を持つ

cos成分

$$\because \omega_{RF} - \omega_{LO} = \omega_{LO} - \omega_{im}$$

sin成分

Image-reject receiver with split phase shift stages

# アーキテクチャをCMOS回路で設計

ギルバート乗算器を利用

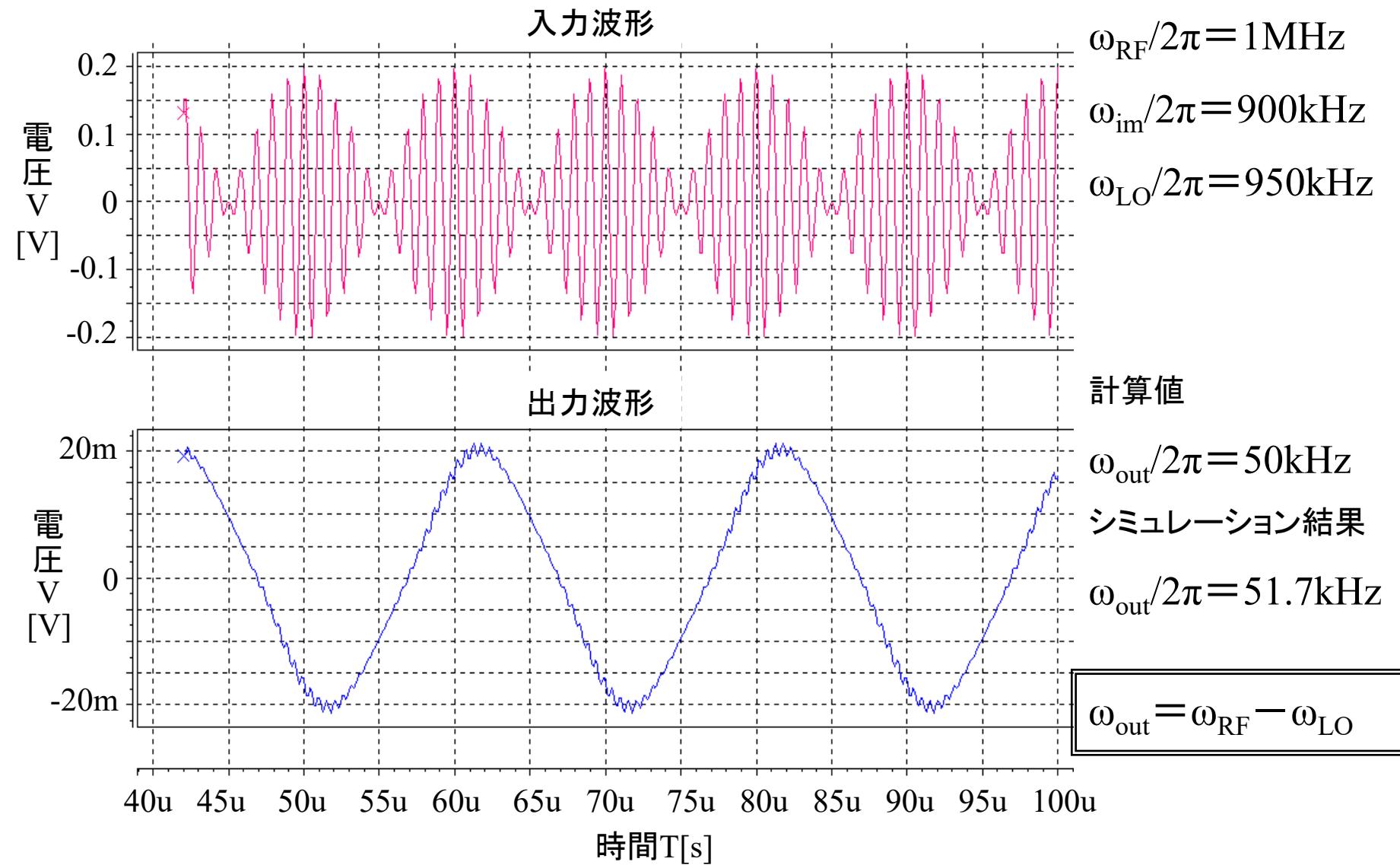

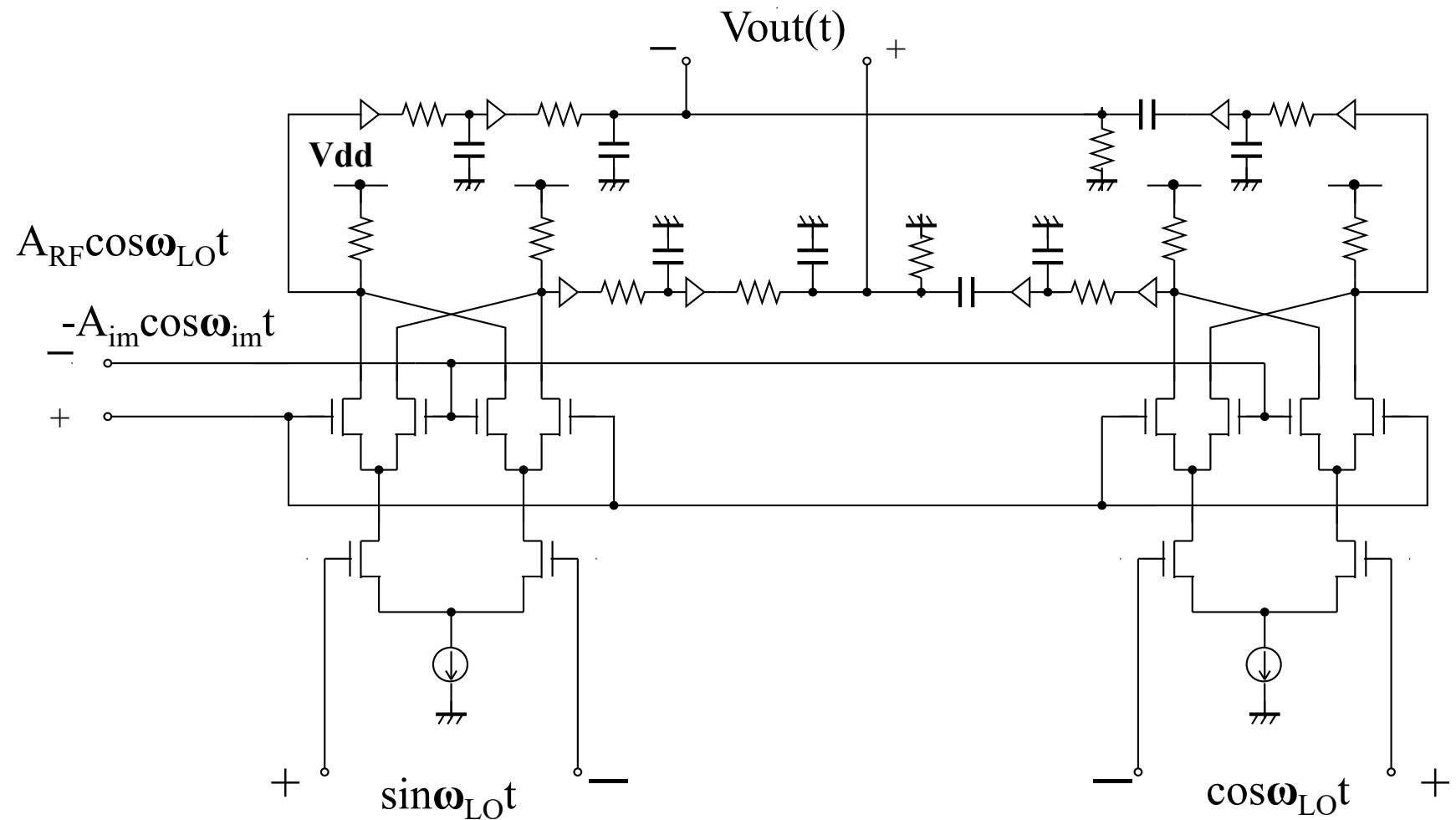

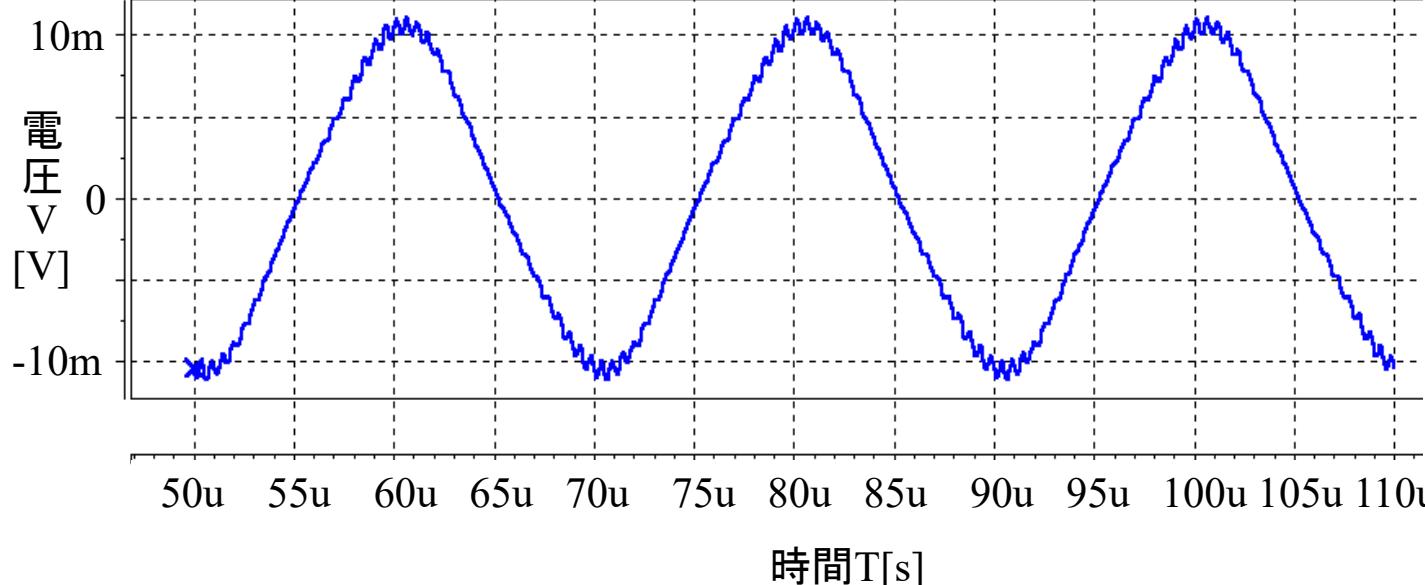

# 時間領域シミュレーション結果

入力波形

$$\omega_{RF}/2\pi = 1 \text{ MHz}$$

$$\omega_{im}/2\pi = 900 \text{ kHz}$$

$$\omega_{LO}/2\pi = 950 \text{ kHz}$$

計算値

$$\omega_{out}/2\pi = 50 \text{ kHz}$$

シミュレーション結果

$$\omega_{out}/2\pi = 50 \text{ kHz}$$

$$\omega_{out} = \omega_{RF} - \omega_{LO}$$

出力波形

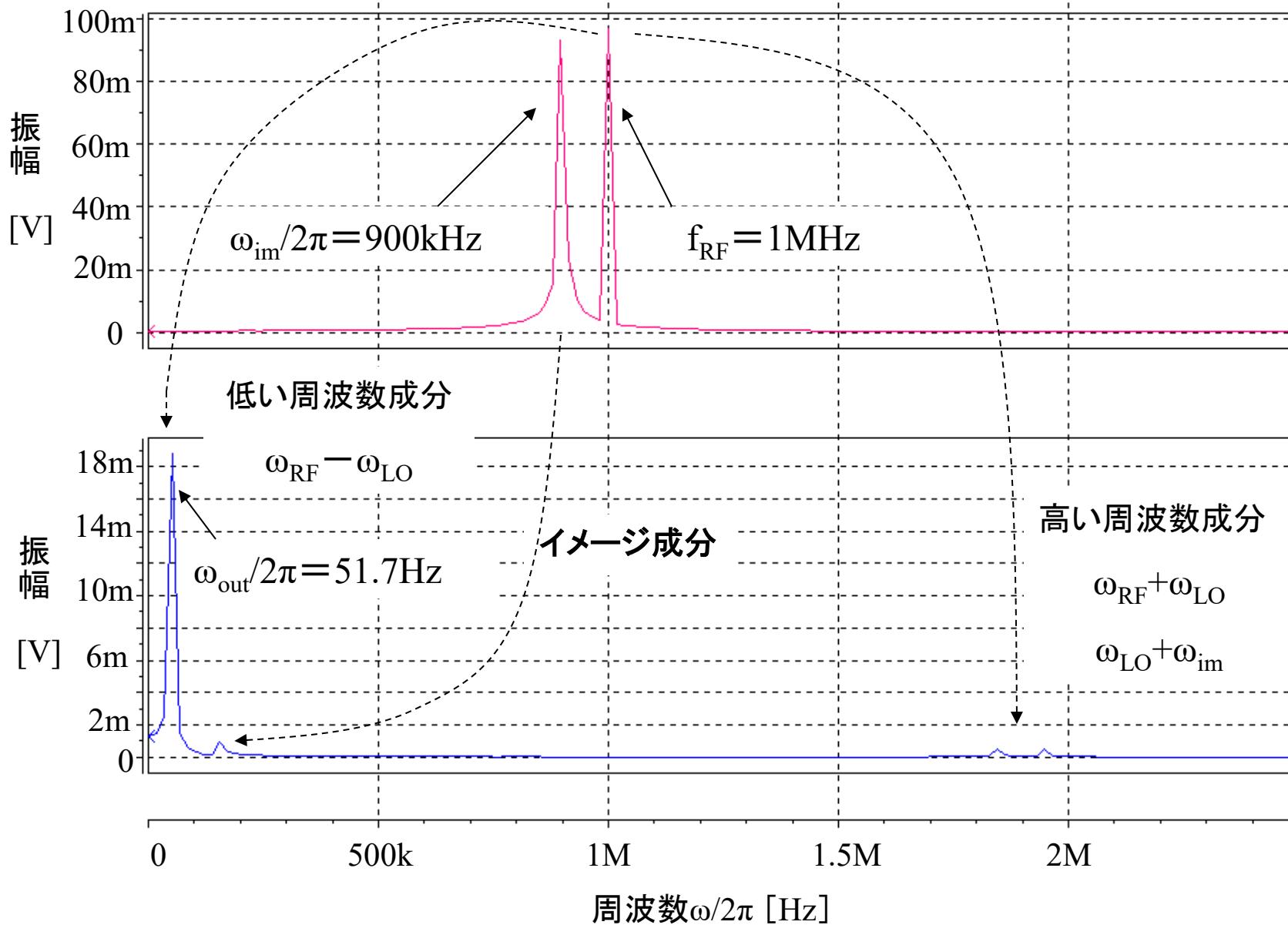

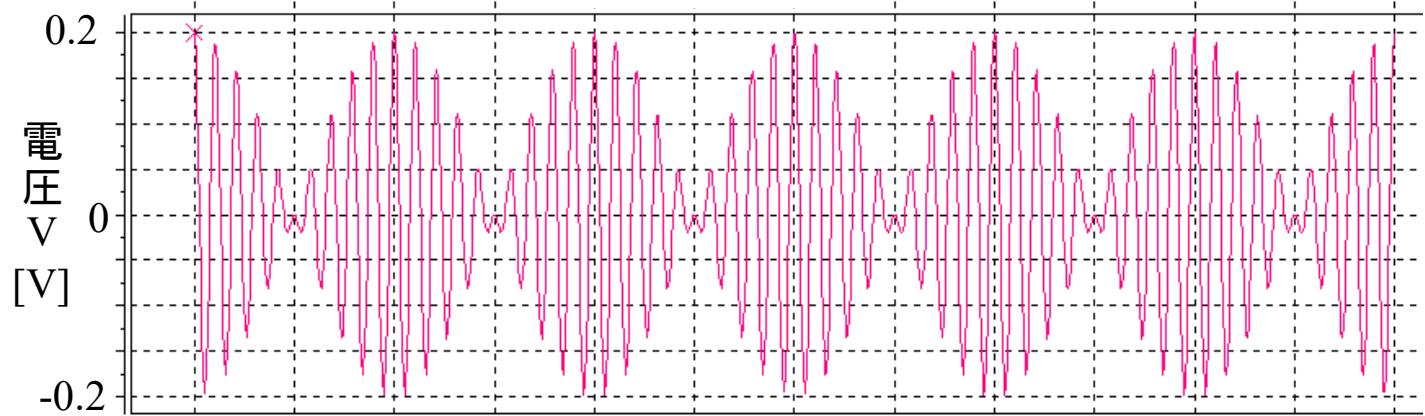

# 周波数領域シミュレーション結果

# Low IF Architectureの解析

# CMOS回路の設計

Complex mixer部分

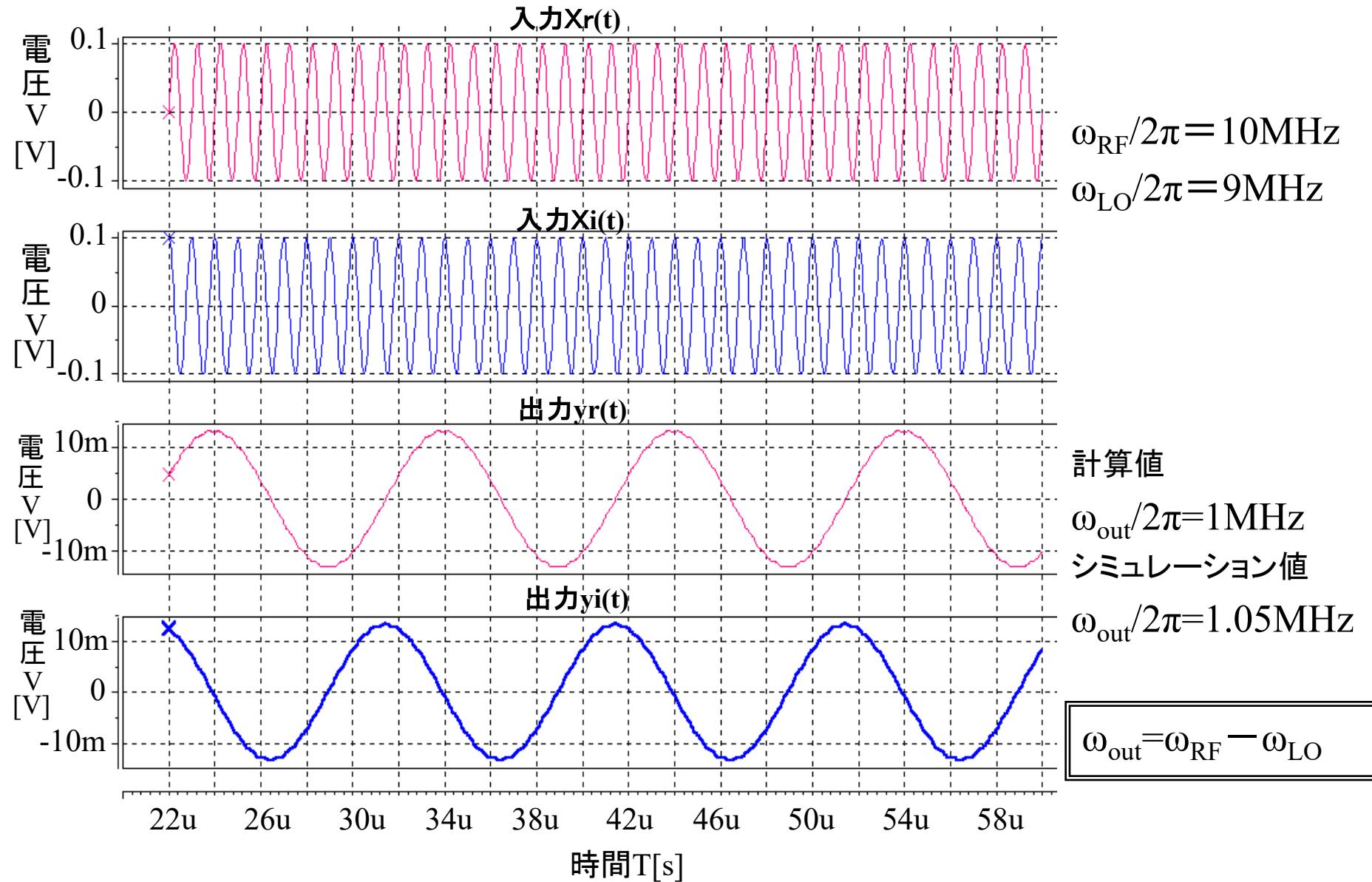

# 時間領域シミュレーション結果

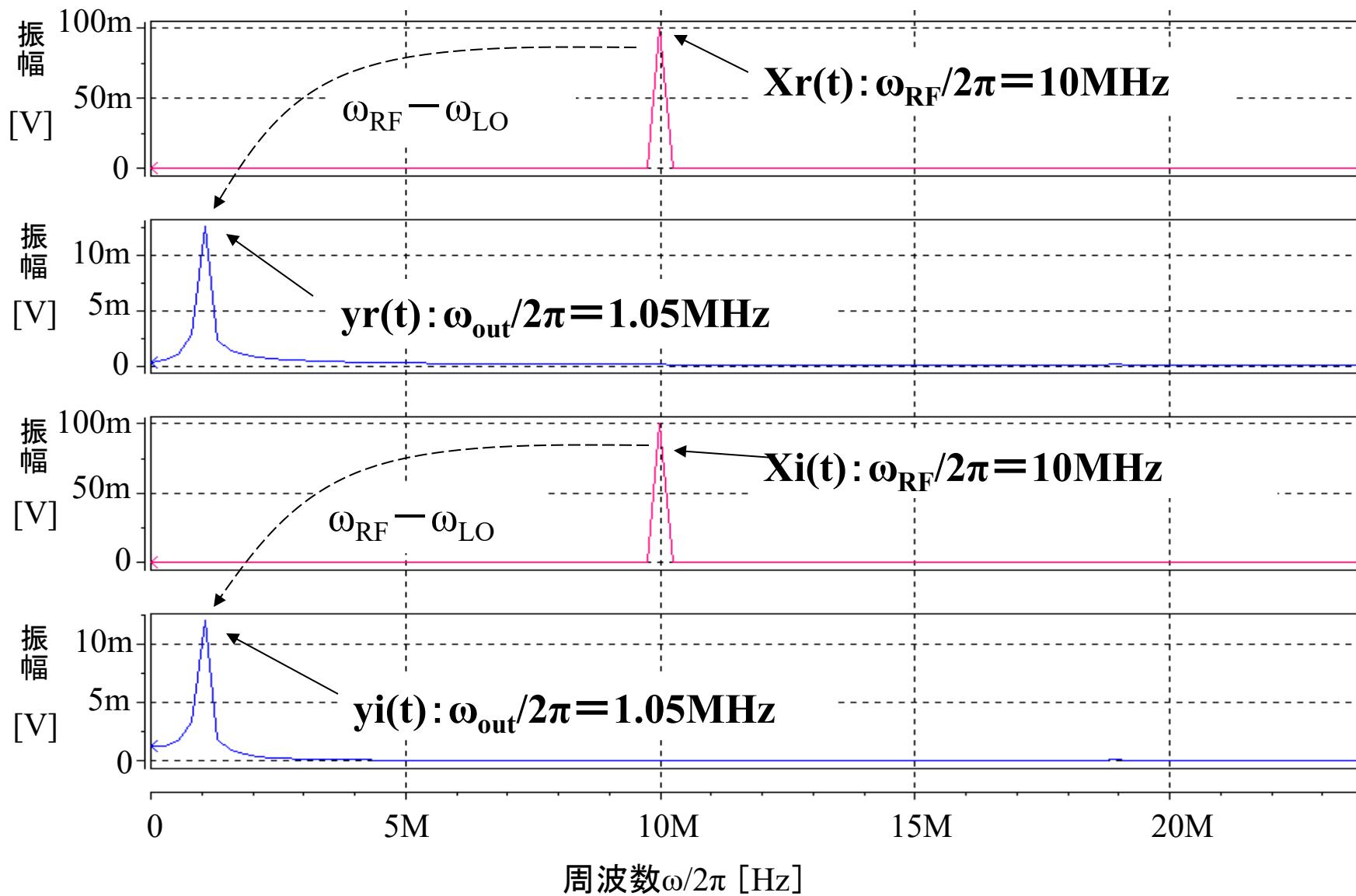

# 周波数領域シミュレーション結果

自然はゆらぎを好むが無駄を嫌う

アルバート・aignシュタイン

# 関係WEB

元ソニー、群馬大学客員教授 萩原良昭先生

<https://kbaweb.ei.st.gunma-u.ac.jp/warehouse/nikkei-2007-2-6.pdf>

<https://kobaweb.ei.st.gunma-u.ac.jp/news/pdf/2017/2017-9-5hagiwara.pdf>

[https://kobaweb.ei.st.gunma-u.ac.jp/news/pdf/2017/Dr\\_hagiwara.pdf](https://kobaweb.ei.st.gunma-u.ac.jp/news/pdf/2017/Dr_hagiwara.pdf)