# 半導体デバイスモデリング技術 後半

2020年7月7日 群馬大学 非常勤講師 岡部裕志郎

## 内容

#### § 5. 各素子のモデル2

- 5-1. **MOSトランジスタ**

- 5-2. 抵抗R

- 5-3. 容量C

#### § 6. 1/fノイズ

デバイス自体からのノイズ

#### § 7. 特性テスト

コーナーモデルと統計モデル、ミスマッチ

#### § 8. 注意点

# § 5. 各素子のモデル2

5-1. MOS (<u>M</u>etal <u>O</u>xide <u>S</u>emiconductor) トランジスタ

## ■MOSトランジスタの特徴

|         | MOS       | バイポーラ |

|---------|-----------|-------|

| 駆動方式    | 電圧        | 電流    |

| 用途      | デジタル、アナログ | アナログ  |

| 増幅率     | 中→高*      | 高     |

| 完成時間TAT | 1~2ケ月     | 2週間   |

| マスク枚数   | 30枚       | 10枚   |

| 値段      | 高価→安価*    | 安価    |

| ミスマッチ   | 大         | 小     |

| 消費電力    | 少         | 多     |

| 速度      | 高         | 低     |

| 微小信号    | 問題無し      | 苦手    |

<sup>\*</sup>微細化で高性能、安価となった

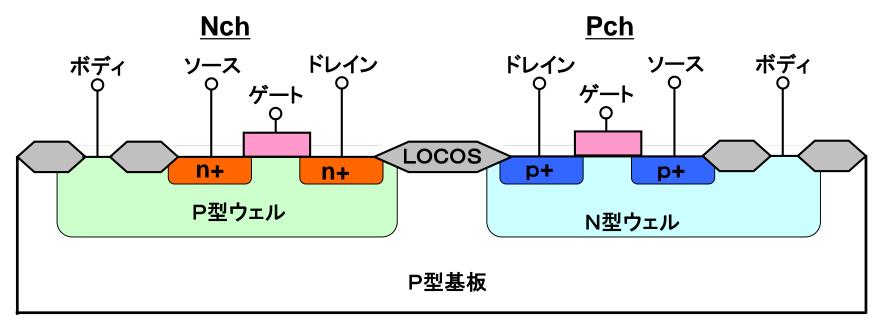

## ■ CMOSトランジスタ

CMOS: Complementally (補正する) MOS N/Pchの補正で消費電力を低下。

\*電圧駆動

#### 特徴

- 高集積のため微細化されたMOS

- •ゲート長0.1μm以下が主流。

- ・ソース/ドレインは対称構造。

- •最近ではアナログ用途に使用されている。

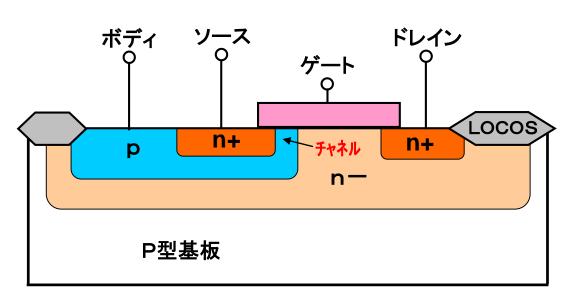

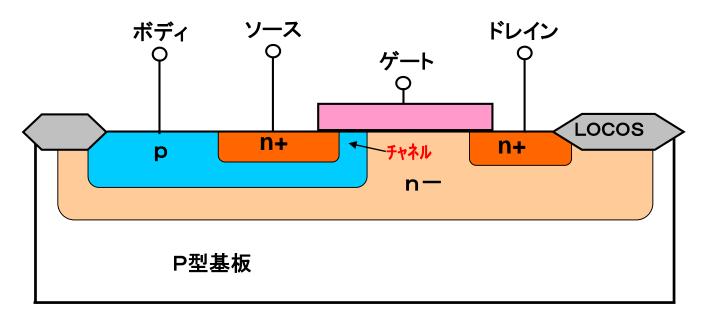

## ■ DMOSトランジスタ

Diffused(チャネル領域を拡散で作る)MOS(パワーMOS)

高耐圧、大電流用途のためドレインドリフト領域(n-)が広い。

1)LDMOS(Laterally Diffused MOS)

電流が横方向に(Laterally)流れる。

高速スイッチング。 回路出力段に使用

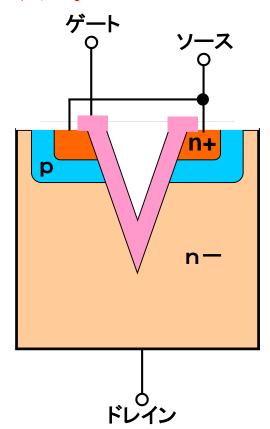

#### 2)VDMOS

電流が縦方向に (Vertically)流れる。

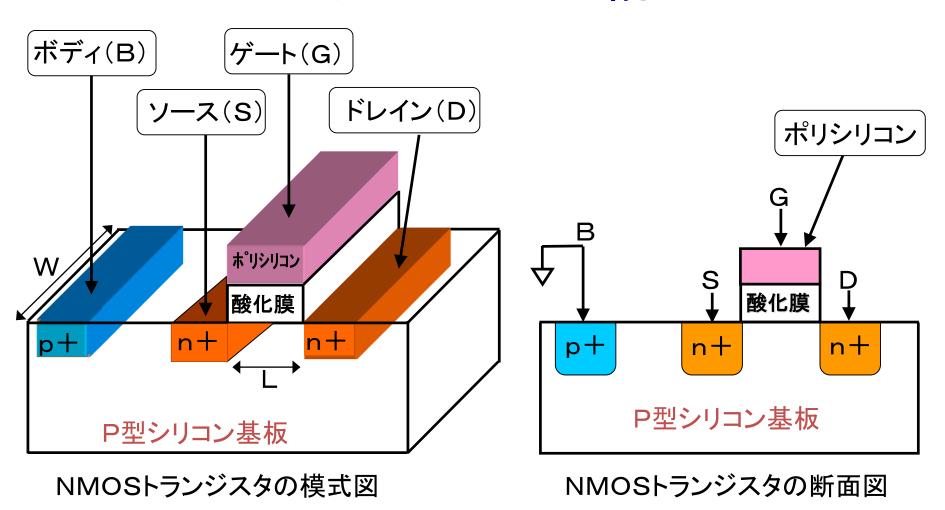

## ■CMOSトランジスタの構造(Nch)

出典: CMOS OPアンプ回路実務設計の基礎、CQ出版社、吉澤著。

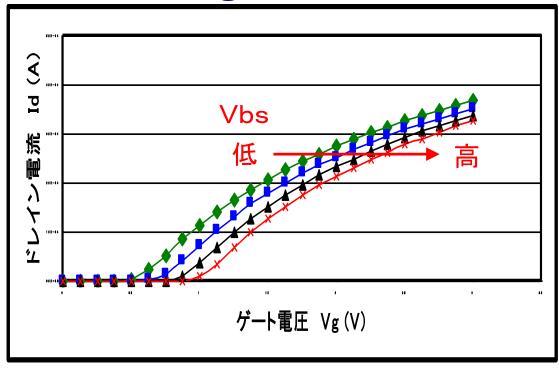

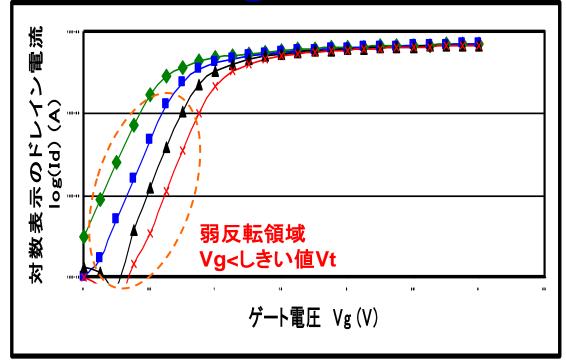

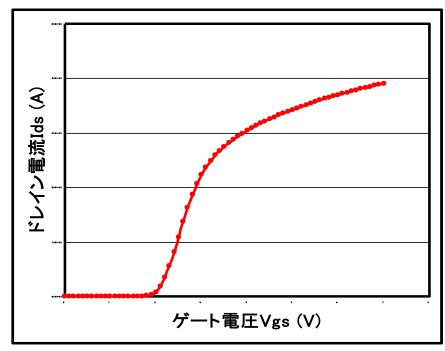

## MOSのId-Vg特性(基板電圧Vbs依存性)

高Vbs ↓ 高Vg側へ移動

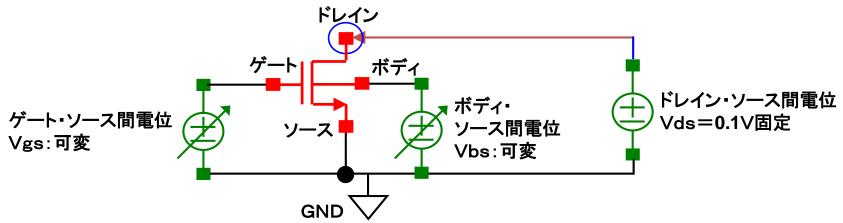

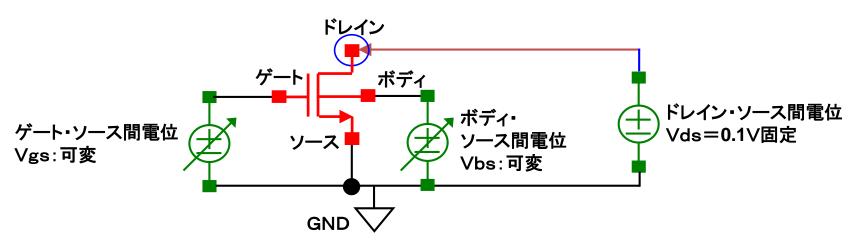

## ■MOSのId-Vg特性(弱反転領域)

Vg=OVでも 微小電流が流 れている。

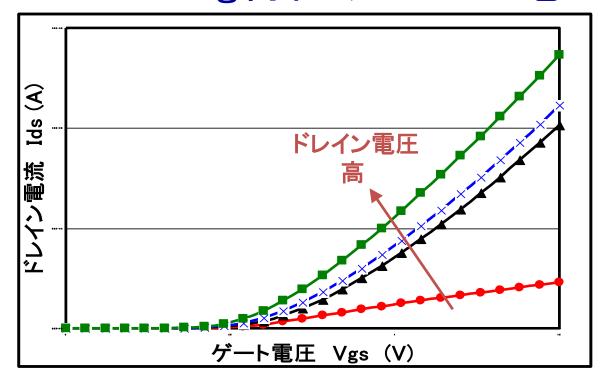

## ■MOSのId-Vg特性(ドレイン電圧依存性)

高ドレイン 電圧 ↓ 電流増える

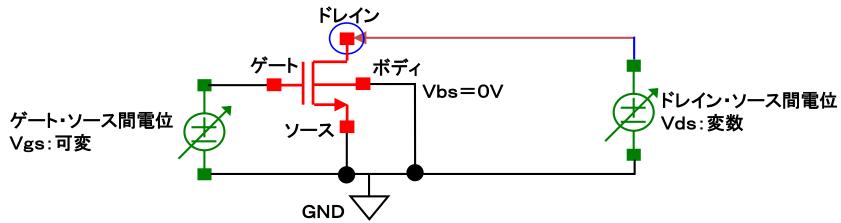

# ■MOSのId-Vg特性(ドレイン電圧依存性)

高Vd ↓ 電流増える

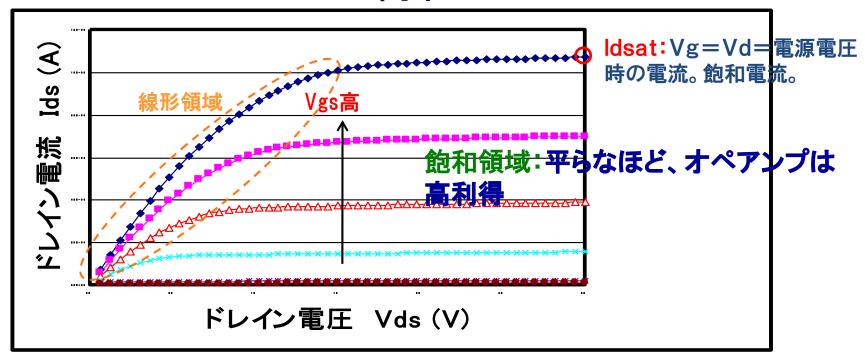

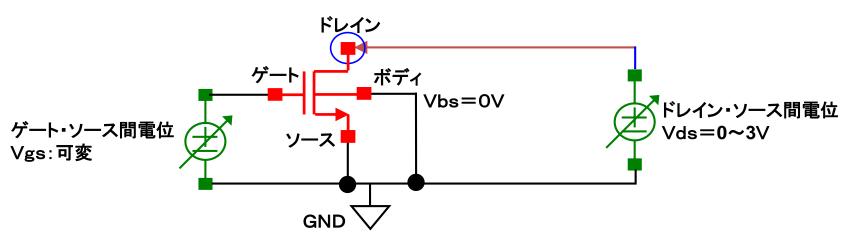

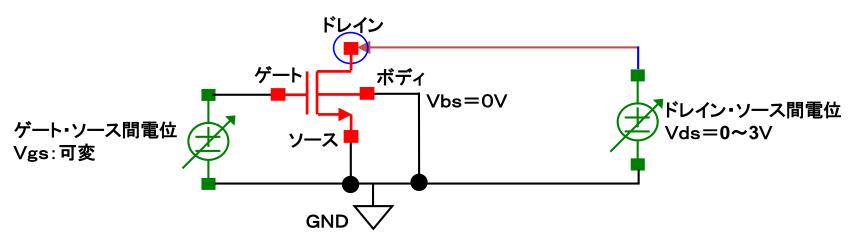

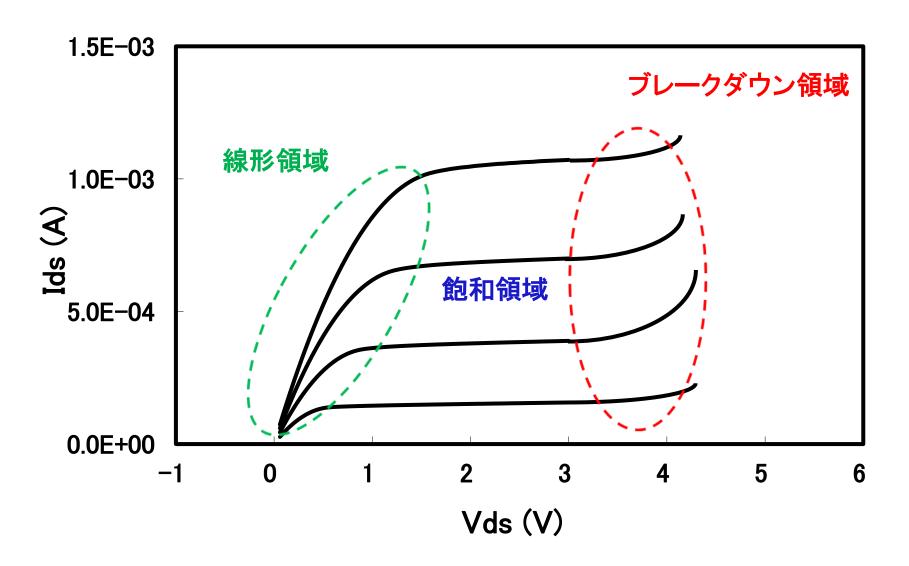

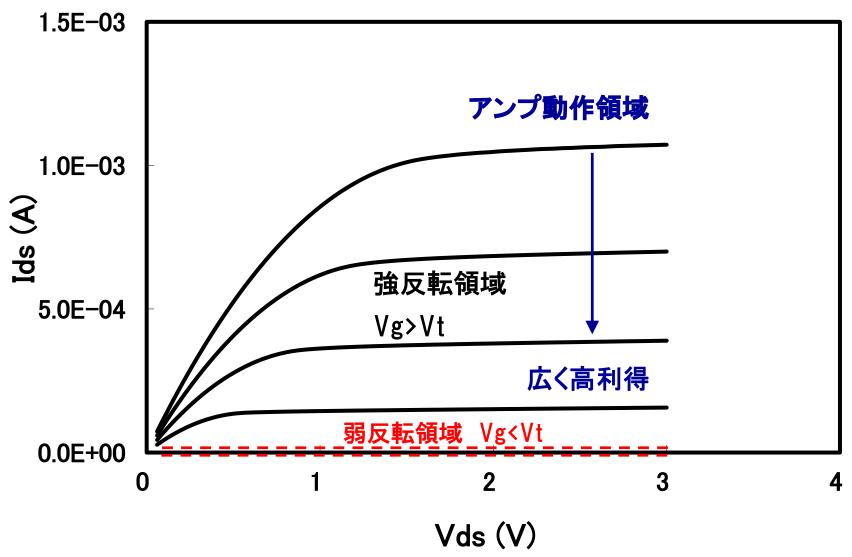

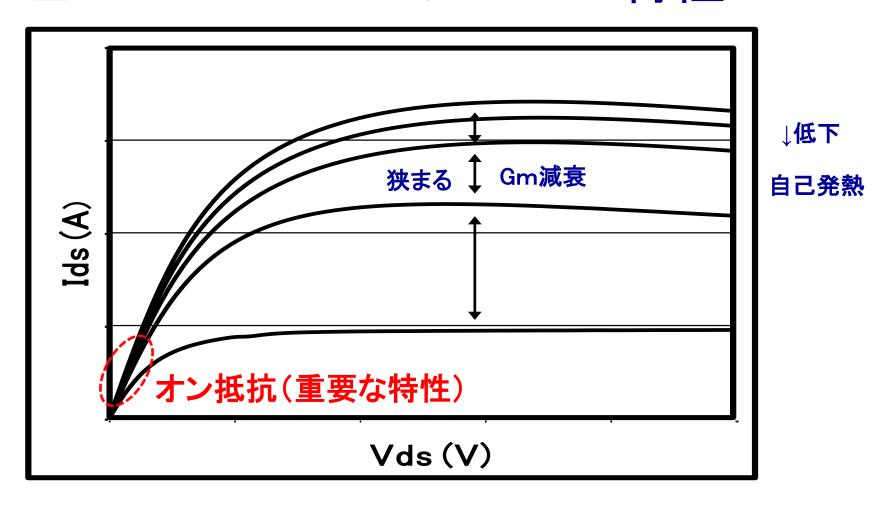

## ■MOSのIdーVd特性

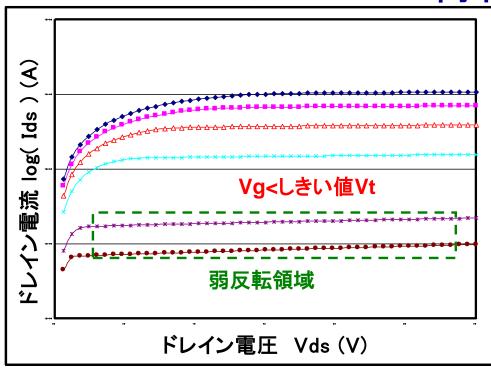

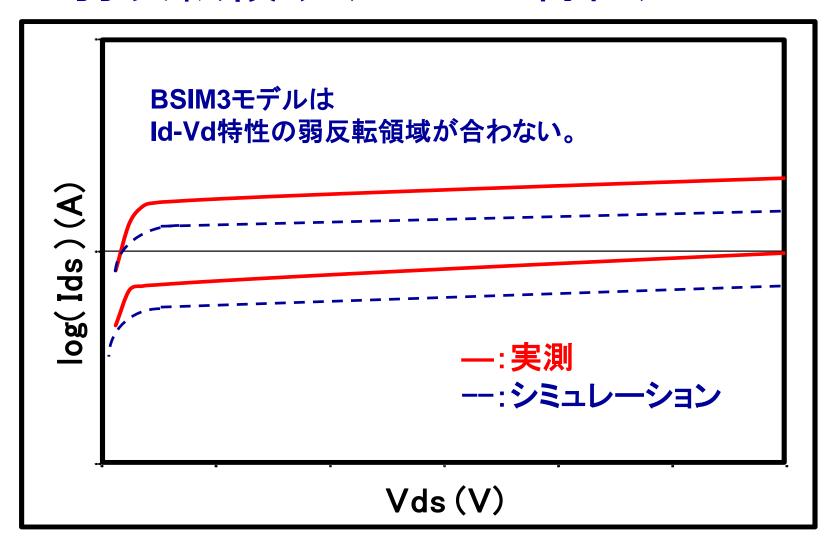

## MOSのIdーVd特性(弱反転領域)

ゲート電圧が低くても 飽和領域 (平坦部)がある。

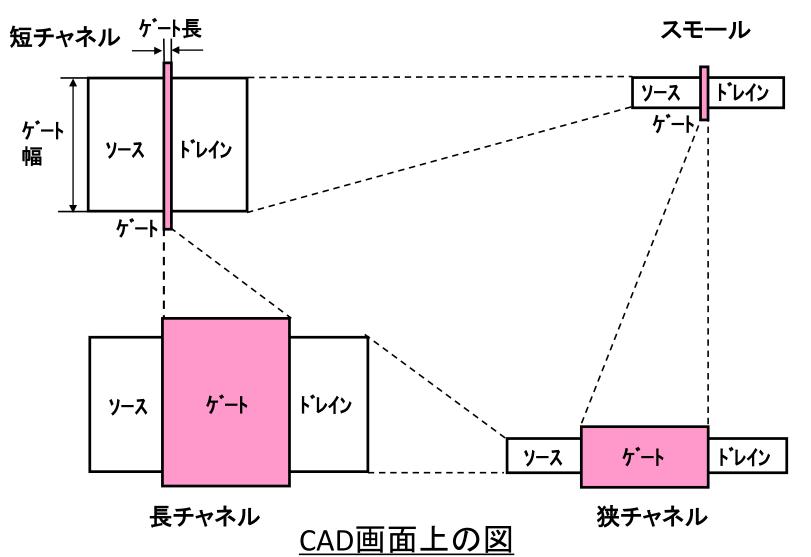

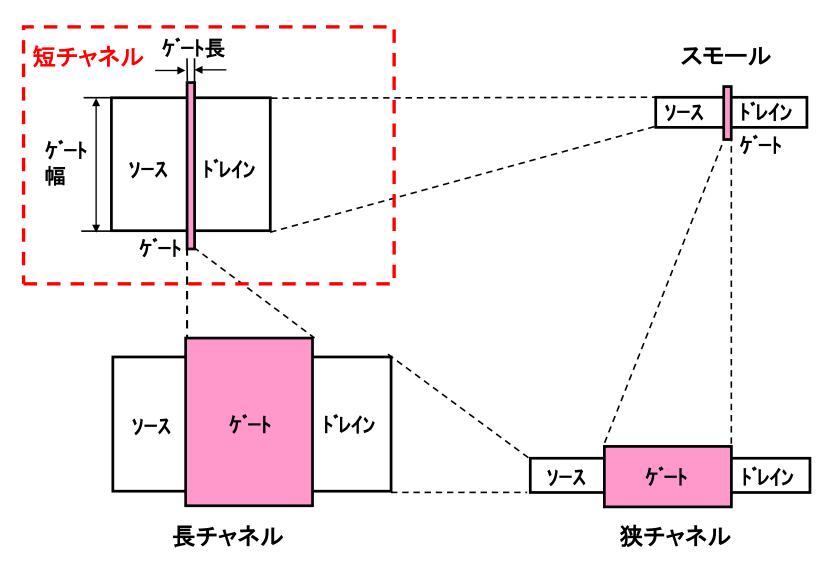

# ■スケーリング

必要な回路特性を得るため、ゲート幅やゲート長を振ること。

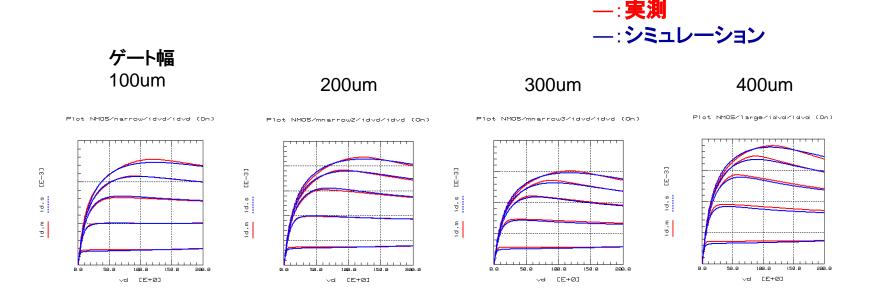

## ■スケーリング対応

#### MOSモデルはスケーリングが必須

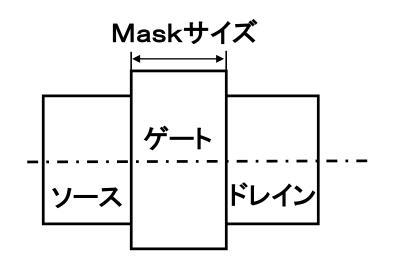

## ■変換差

#### 1. ゲート長変換差

#### 変換差=Maskサイズ一実効ゲート長(完成)

#### \*基準はMaskサイズ

CAD平面図

完成品の断面摸式図

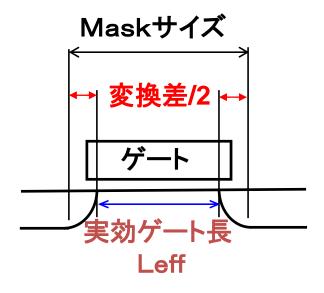

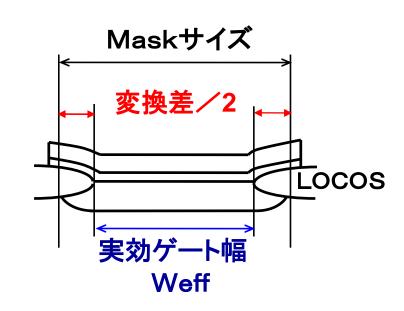

## ■ゲート幅変換差

#### 実効ゲート幅 = Maskサイズ - 変換差

CAD平面図

完成品の断面摸式図

\*拡散層サイズ=ゲート幅

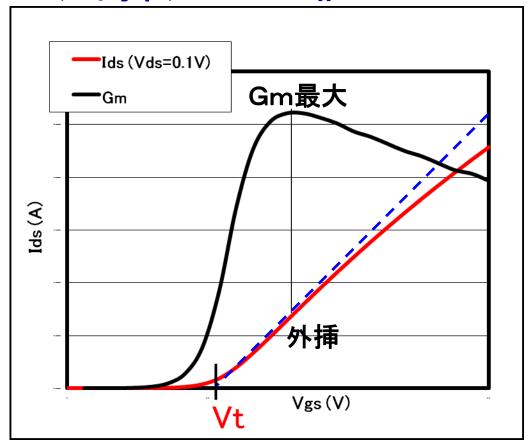

## ■(外挿)しきい値Vt

条件の例)

ゲート長:最小サイズ

ドレイン電圧:0.1V

温度:27℃

Gm(コンダクタンス) = DId/DVg

プロセス、寸法、バイアス条件、温度、定義等の条件によりVtは異なる。

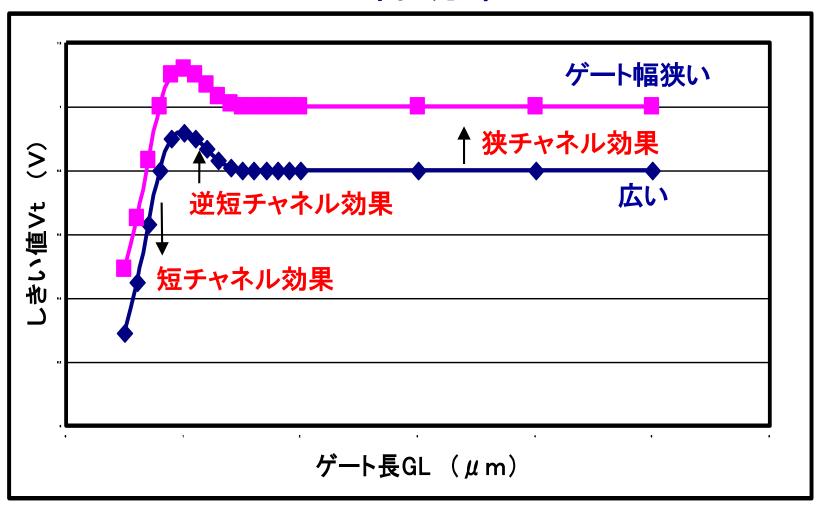

### ■短チャネル化とVt

Vtは、デバイスサイズによって変わる。

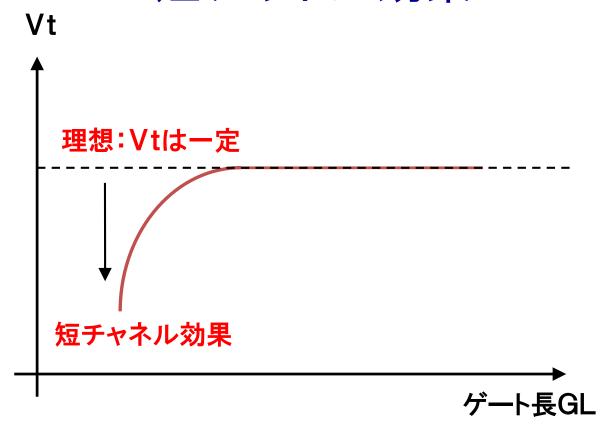

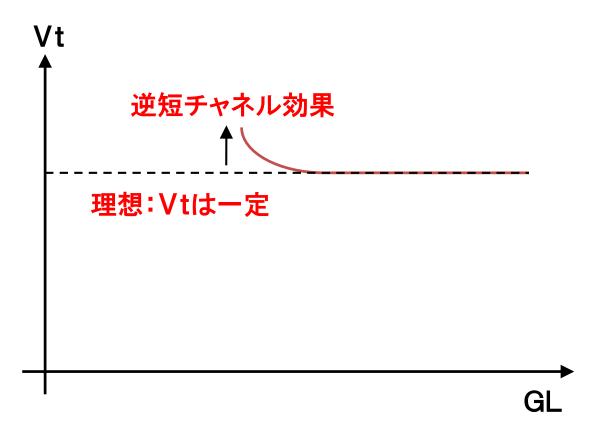

## ■短チャネル効果

#### ゲート長GLが短くなると、Vtが下がる現象

ドレインの影響で反転する電荷が減るため。 微細化の妨げ → 短チャネル効果の抑制 → ポケットインプラ等で対策

## ■逆短チャネル効果

#### GLが短くなると、Vtが上がる現象

ポケットインプラ等の効果による。 短チャネル効果より弱い。

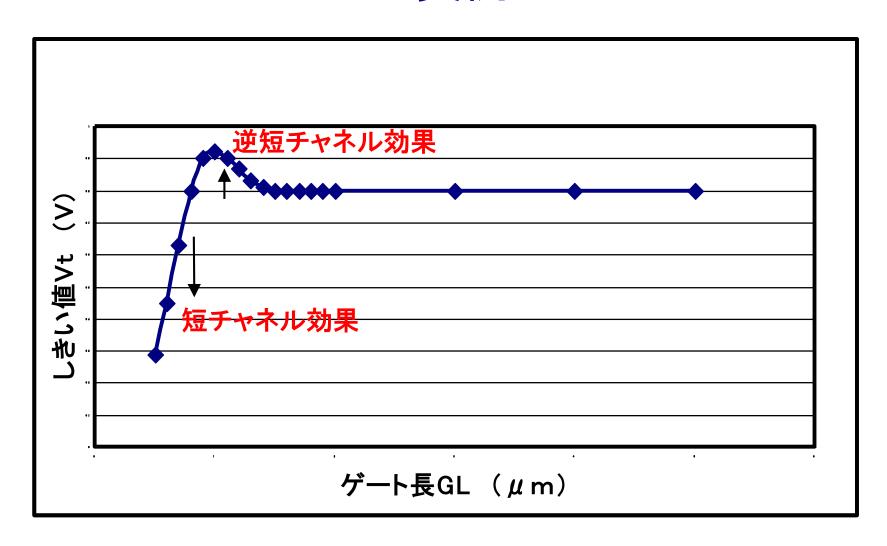

## ■実例

#### 逆短チャネル効果より短チャネル効果は強い

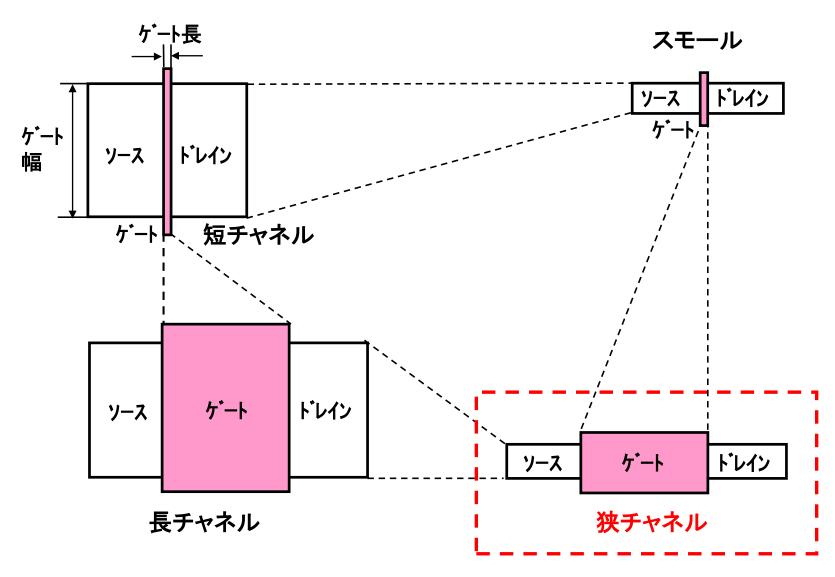

### ■狭チャネル化とVt

\* Vtは、デバイスサイズによって変わる。

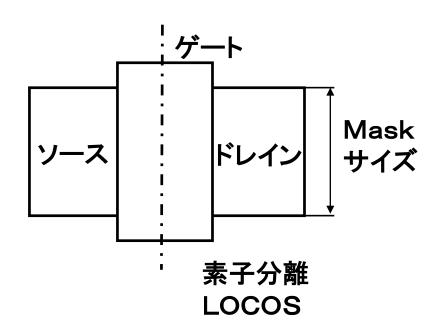

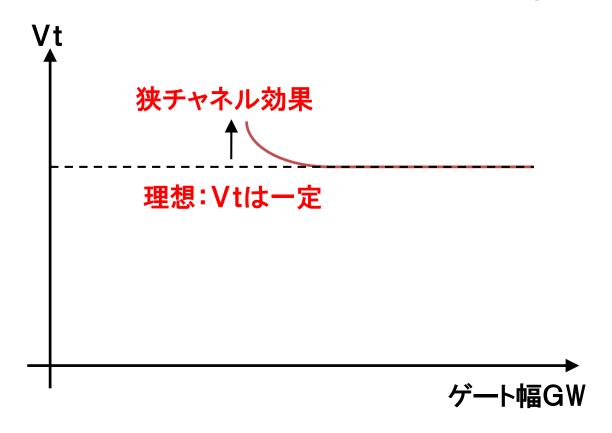

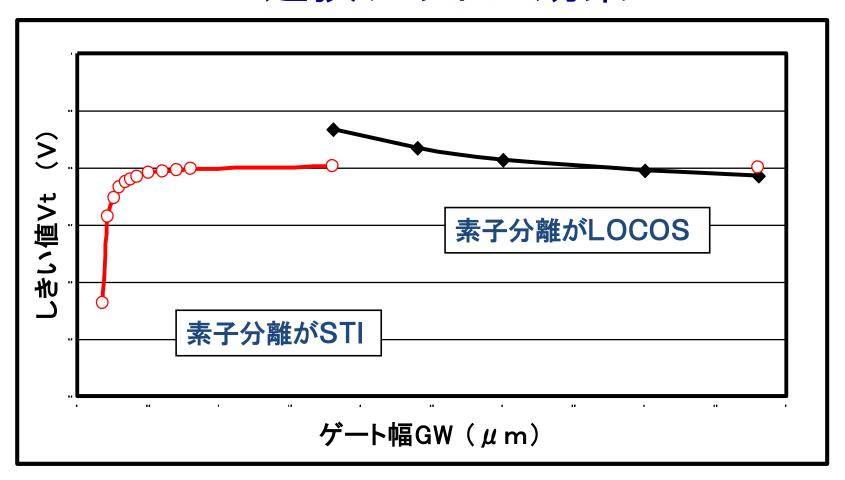

## ■狭チャネル効果

ゲート幅GWが狭くなると、Vtが上がる現象

\*LOCOS下の空乏層の影響が強くなるため

## ■逆狭チャネル効果

#### GWが狭くなると、Vtが下がる。

素子分離がSTI(Shallow Trench Isolation)の場合。

# ■各効果

素子分離はLOCOS

## ■各MOSモデルの特徴

・しきい値に基づいた電荷モデル

(電位の基準はソース) BSIM3,4モデル

- \* Vds=0で順・逆特性が非対称のため不連続になりやすい

- **電荷基準モデル**(電位の基準は基板)

EKVモデル、BSIM6モデル

- \*物理モデルのため、しきい値パラメータがない。

- •表面電位モデル(電位の基準は基板)

HiSIMモデルシリーズ(HiSIM2,HiSIM-HV等)

\*物理モデルのため、しきい値パラメータがない。

## ■BSIMモデルシリーズ

#### BSIM3

**しきい値電圧を基にした**物理モデル ゲート長GL>0.1μmを保障 最初のCMC標準モデル

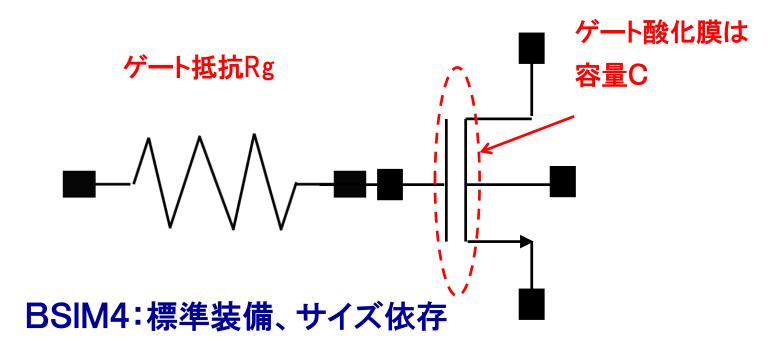

#### BSIM4

BSIM3V3.2を拡張したモデル RF-MOSFET用にゲート抵抗をモデル化

#### -BSIM6

電荷を基にした物理モデル BSIM4の物性とモデルパラメータをサポート CMC標準モデル

# ■BSIM3モデル

#### 表.1 各CMOSモデル式の特徴

| モデル式  | ゲート長          | DC特性の精度                     | 高周波      |

|-------|---------------|-----------------------------|----------|

| BSIM3 | >0. 1 $\mu$ m | 高<br>(Id-Vd特性の弱反転領域を<br>除く) | 要マクロモデル化 |

| EKV   | >0. 1 $\mu$ m | 高(特にId-Vd特性の弱反転<br>領域)      | <b>↑</b> |

| BSIM4 | >0. 05μm      | 全領域で高い                      | 内蔵       |

| BSIM6 | <0. 1μm       | <b>↑</b>                    | <b>↑</b> |

| HiSIM | <0. 1μm       | <b>↑</b>                    | <b>↑</b> |

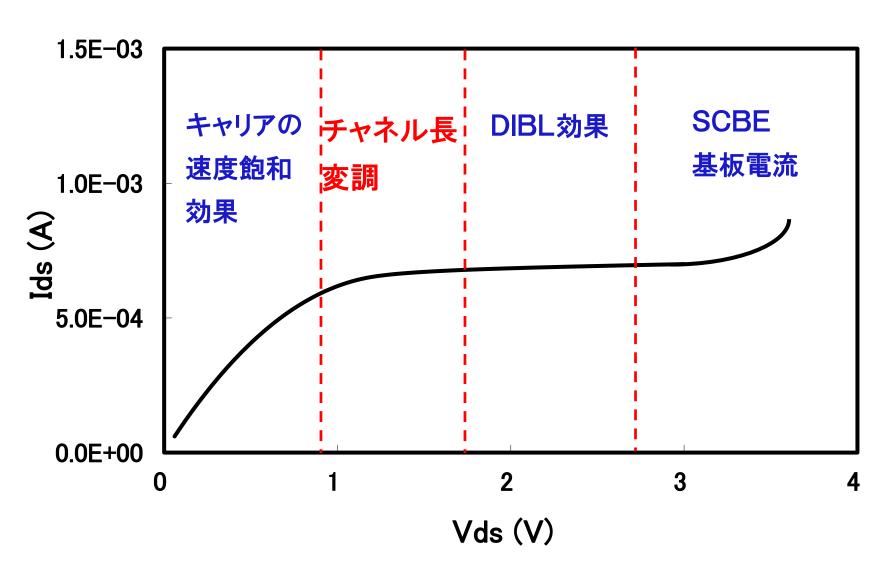

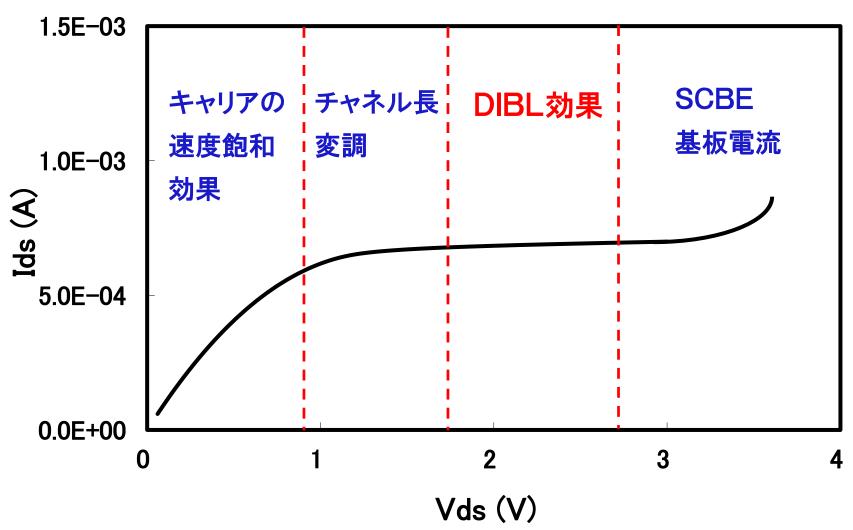

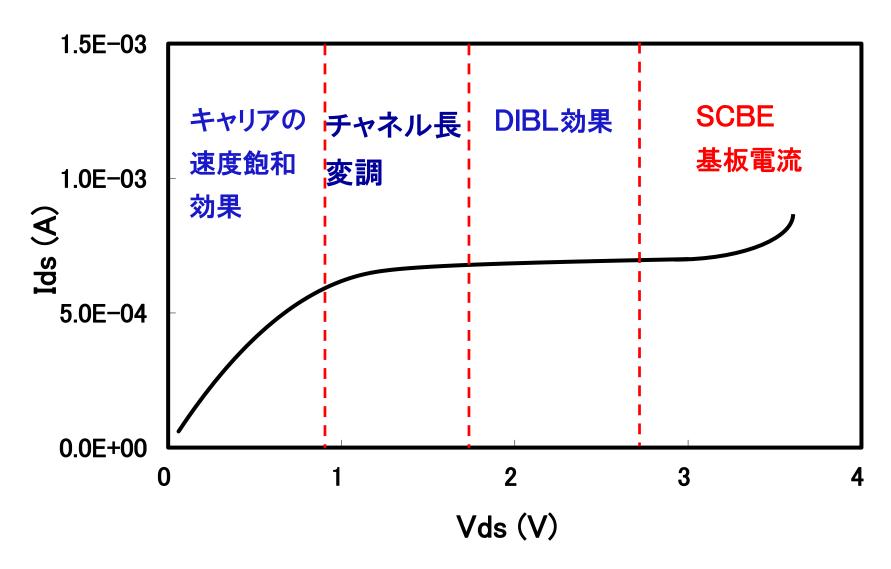

## ■IdーVd特性の各領域

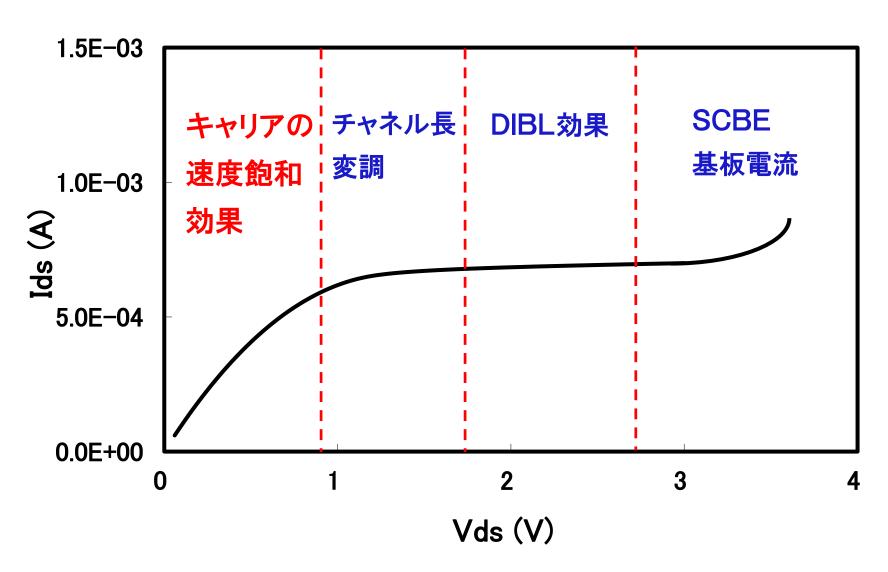

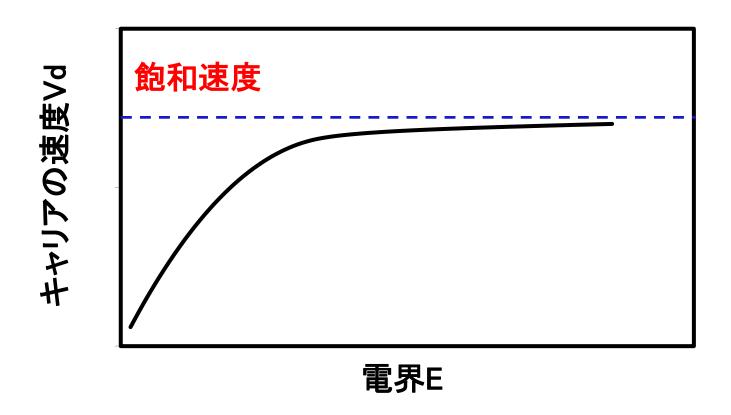

## ■キャリアの速度飽和効果1

## ■キャリアの速度飽和効果2

実測した電子の飽和速度は6E4(m/s)。

キャリアの速度飽和で電流も飽和する。

## ■キャリアの速度飽和効果3

#### 注意

デバイスの名著:

「電流が飽和する原因はチャネル長変調による」 これは、40年前頃のデバイスを対象にしている (最小ゲート長>10μm)

最近のMOSは微細化されため(最小ゲート長く0.35μm)、 キャリアの速度飽和により電流が飽和する。

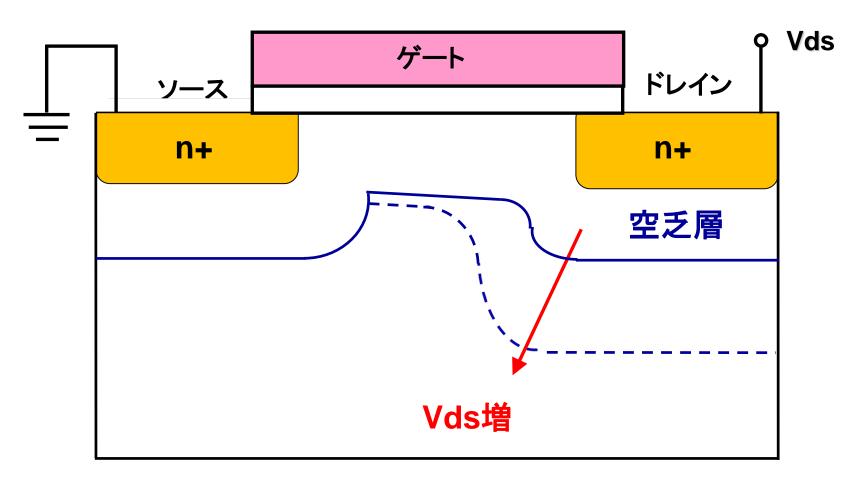

# ■チャネル長変調

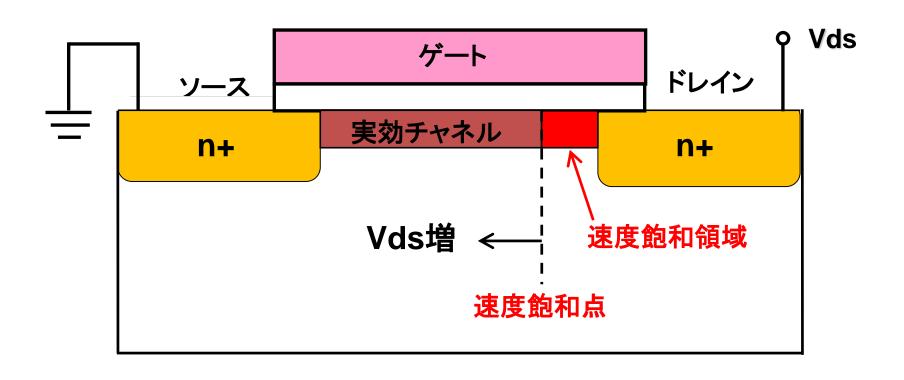

## ■チャネル長変調2

実効的なチャネル長はドレイン電圧で変化する。

Vds増 → 速度飽和領域大 → 実効チャネル長短 → ドレイン電流増加

## ■DIBL効果

## (Drain Induced Barrier Lowering)

#### ドレイン電圧で、しきい値Vtが低下する効果

Barrier: Onするための障壁のことで、低いほどOnしやすい

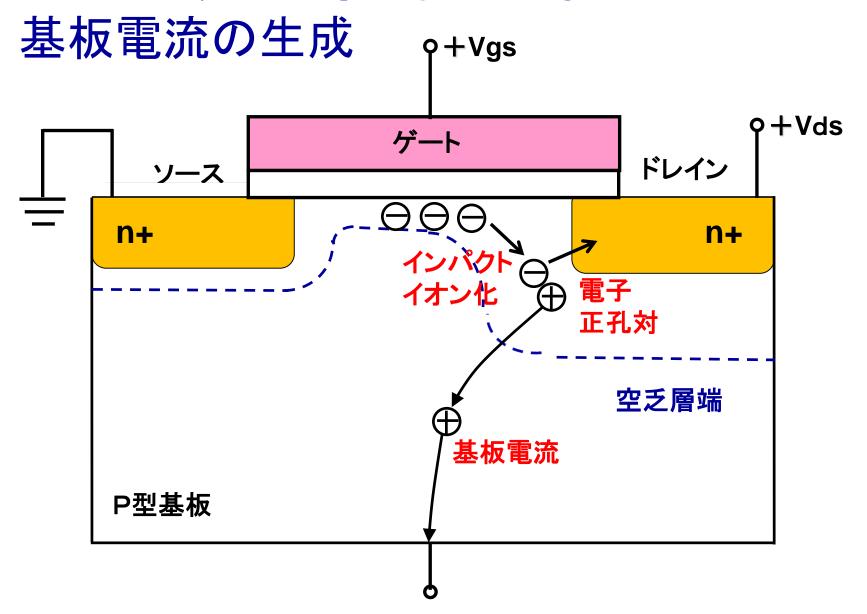

## ■SCBE(Substrate Current Body Effect) 基板電流

### ■インパクト・イオン化による

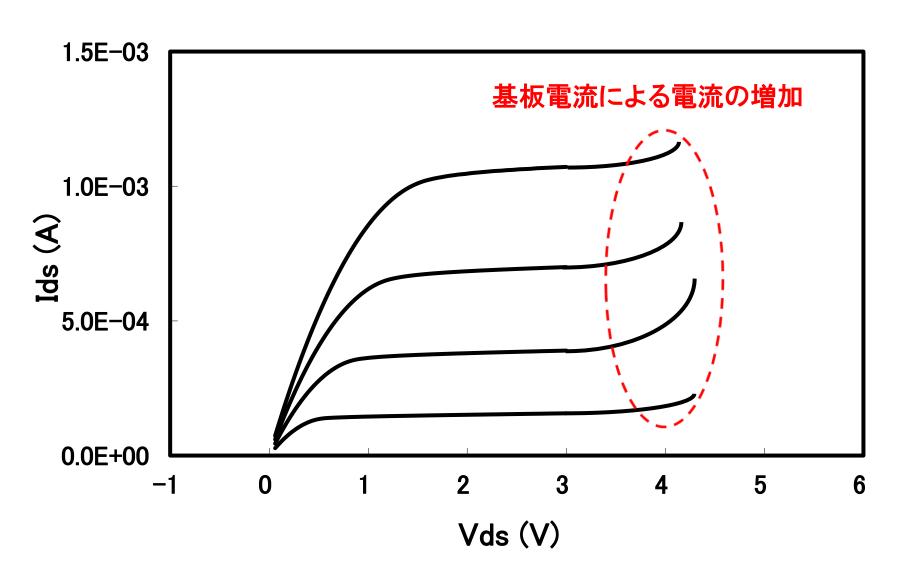

# ■基板電流によるドレイン電流の増加

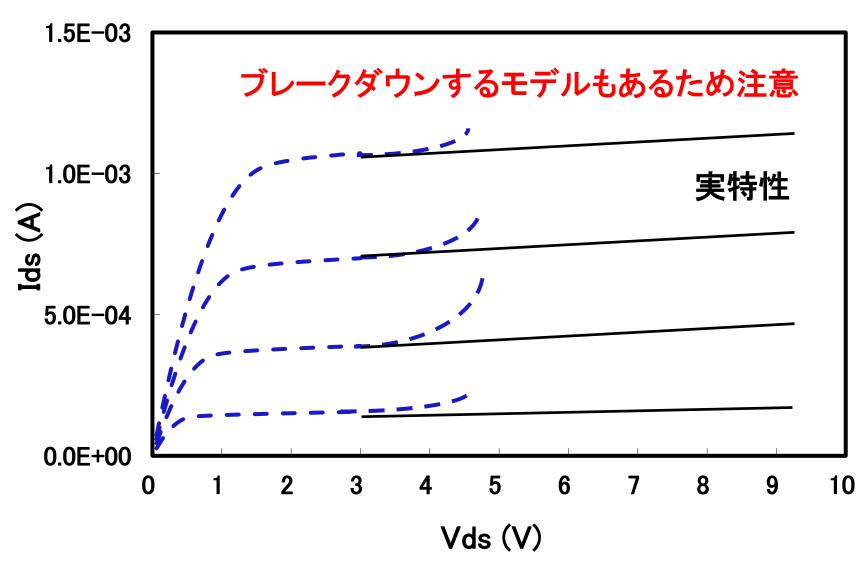

### ■低電圧範囲で抽出したモデルを高電圧で使用(Nch)

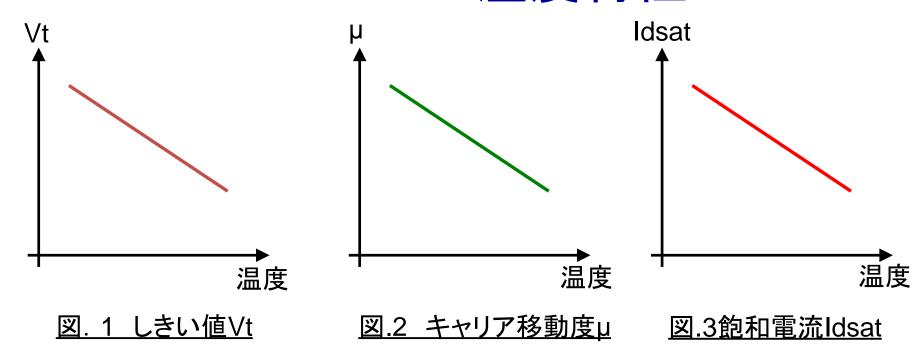

### ■MOSの温度特性

#### 温度にほぼ線形に依存する

#### 高温で電流が少ないため、熱に対して安定。

発熱→電流減る→発熱減る→ある温度で安定する。

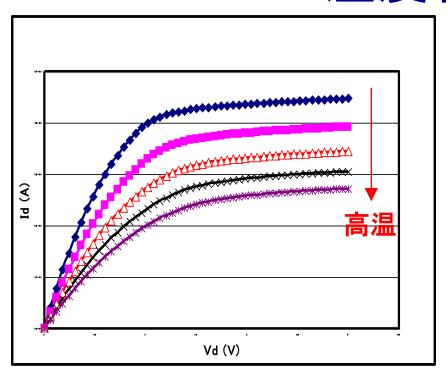

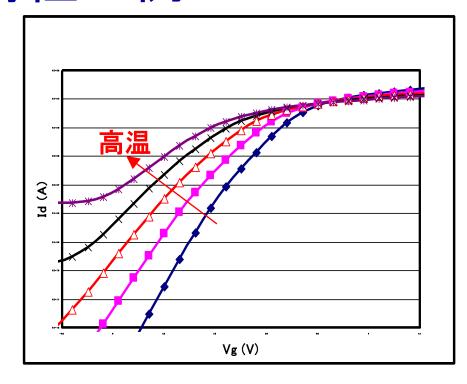

## ■MOSの温度特性の例

図.1 Id-Vd特性

図. 2 Id-Vg特性(Log表示)

高温で、

- ①飽和電流Idsatは低下する(図.1)

- ②漏れ電流Ileakは増える(図. 2)

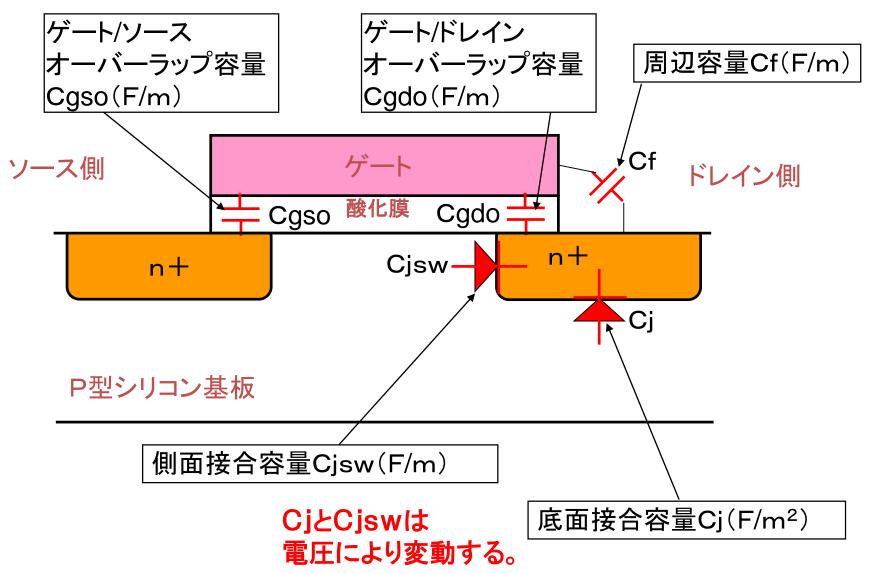

# ■CMOSの容量(ゲート容量以外)

## ■CMOSの接合容量と抽出1

• MOSはスケーリングするため、

容量モデルも可変式

・ 底面部と側面部の和が接合容量

接合容量Ctotal(F) = 底面接合容量Cj(F/m²) x PN接合底面積(m²)

+

側面接合容量Cjsw(F/m) x PN接合周囲長(m)

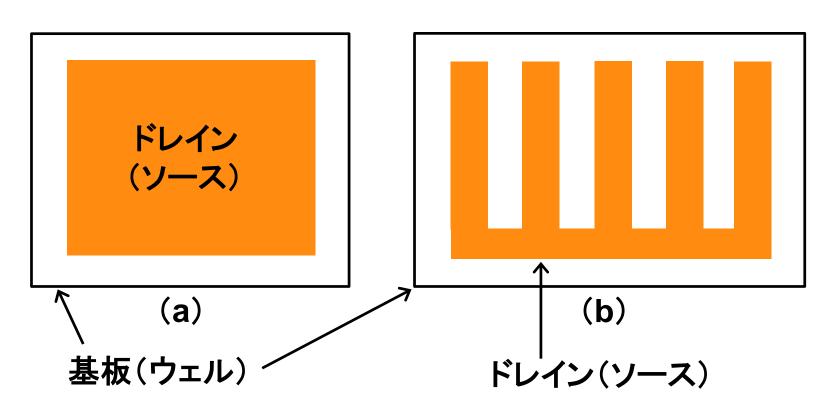

# ■CMOSの接合容量と抽出2

面積が同じで周囲長の異なるレイアウトから 抽出する。

## ■CMOSの接合容量と抽出3

面積が同じ→底面部の接合容量は同じ

$$Ca = Carea + Csw1$$

(1)

$$Cb = Carea + Csw2$$

(2)

- ① 式(1)-式(2)より面積部分の容量を分離

- ② Csw1ーCsw2は、周囲長の差によるため、 側面部接合容量Cjswを抽出

- ③ 式(1)又は式(2)から底面接合容量Cjを抽出

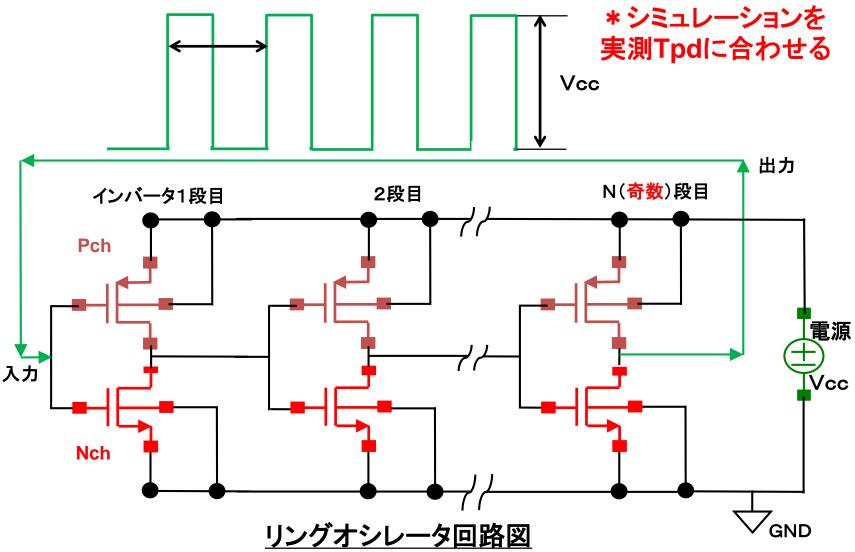

# ■過渡特性(容量パラメータチェック)

スイッチング時間Tpd=1/(2\*N\*発振周波数)

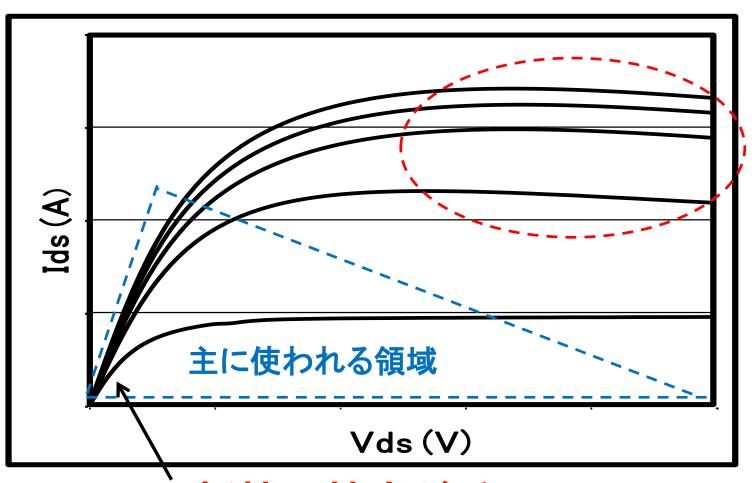

# ■弱反転領域(Id-Vd特性)

# ■弱反転領域(Id-Vd特性)

対策:①Vg>1.5 \* Vtとする。②EKV, BSIM4モデルを使う。

# ■EKVモデル

### 表.2 各CMOSモデル式の特徴

| モデル式  | ゲート長          | DC特性の精度                     | 高周波      |

|-------|---------------|-----------------------------|----------|

| BSIM3 | >0. 1 $\mu$ m | 高<br>(Id-Vd特性の弱反転領域を<br>除く) | 要マクロモデル化 |

| EKV   | >0. 1μm       | 高(特にId-Vd特性の弱<br>反転領域)      | <b>↑</b> |

| BSIM4 | >0. 05μm      | 全領域で高い                      | 内蔵       |

| BSIM6 | <0. 1μm       | <b>↑</b>                    | <b>↑</b> |

| HiSIM | <0. 1μm       | <b>↑</b>                    | <b>↑</b> |

# ■EKVモデル

#### 特徴

- ▪開発者: C. C. Enz, F. Krummenacher, E. A. Vittoz

- •1995年、EKV\_\_Ver2. 6完成

- •弱反転領域が高精度

- ・パラメータ数16ケ

- •低電圧•低消費電力回路向き

- •Vt、βのミスマッチモデルを標準装備

### 現状と実績

- -CMCで世界標準から除外(2005年)。

- ・使用実績が少ない。

- •使用時は万一のシミュレータのバグに注意。

# ■BSIM4モデル

### 表.3 各CMOSモデル式の特徴

| モデル式  | ゲート長          | DC特性の精度                     | 高周波      |

|-------|---------------|-----------------------------|----------|

| BSIM3 | >0. 1 $\mu$ m | 高<br>(Id−Vd特性の弱反転領域を<br>除く) | 要マクロモデル化 |

| EKV   | >0. 1 $\mu$ m | 高(特にId-Vd特性の弱反転<br>領域)      | <b>↑</b> |

| BSIM4 | >0. 05μm      | 全領域で高い                      | 内蔵       |

| BSIM6 | <0. 1μm       | <b>↑</b>                    | <b>↑</b> |

| HiSIM | <0. 1μm       | <b>↑</b>                    | <b>↑</b> |

## ■BSIM4モデル式

### <u>特徴</u>

- BSIM3Ver3. 2モデル式を基本

- •RF-MOS用

- ・パラメータ数~340ケ

- -CMCより世界標準に認定(2000年)

#### BSIM3からの主な改良点(標準装備)

- ①ゲート抵抗とゲートフィンガー数

- ②1/fノイズモデル

- ③弱反転領域、リーク電流の精度向上

# ■ゲート抵抗

RF-MOSモデルにはゲート抵抗が必須。

BSIM3:無し

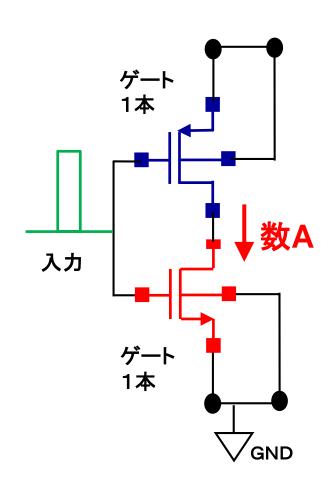

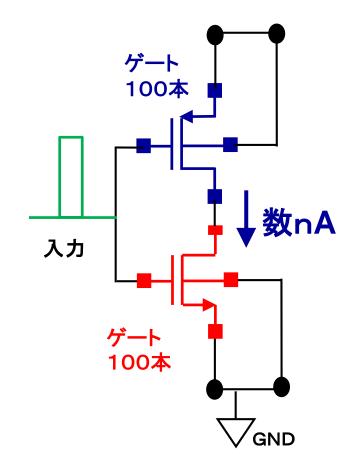

# ■BSIM4ゲート抵抗とフィンガー

デフォルト(ゲート本数NF=1)では、ゲート幅GW>1mmのインバータで貫通電流がアンペアオーダーになる。

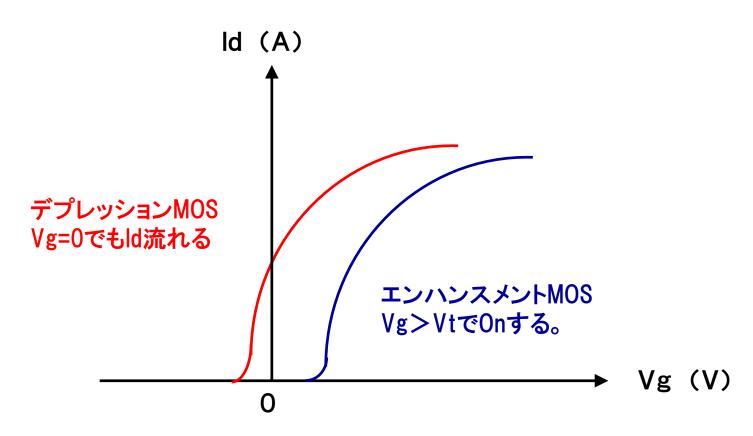

## ■BSIM4モデル精度(DC)

- •BSIM3より弱反転領域の精度が向上

- デプレッションMOSにも適応可。

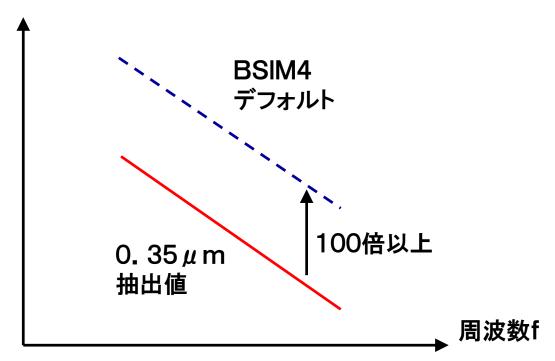

# ■BSIM4モデルの1/fノイズ

ノイズ強度 Sid

\* デフォルト値では、ノイズが強くなる GL<0. 1 μ mのデバイスを想定しているため。

# ■BSIM6モデル

### 表.4 各CMOSモデル式の特徴

| モデル式  | ゲート長          | DC特性の精度                     | 高周波      |

|-------|---------------|-----------------------------|----------|

| BSIM3 | >0. 1 $\mu$ m | 高<br>(Id-Vd特性の弱反転領域を<br>除く) | 要マクロモデル化 |

| EKV   | >0. 1 $\mu$ m | 高(特にId-Vd特性の弱反転<br>領域)      | <b>↑</b> |

| BSIM4 | >0. 05μm      | 全領域で高い                      | 内蔵       |

| BSIM6 | <0. 1μm       | <b>^</b>                    | <b>↑</b> |

| HiSIM | <0. 1μm       | <b>↑</b>                    | <b>↑</b> |

## ■BSIM6モデル式

#### 特徵

- 1. 電荷を基にした<mark>対象型MOSFETモデ</mark>ル

- ・電荷を中心にモデル式を導出

- -BSIM4の物性とモデルパラメータをサポート

- ・BSIM4に比べ、速度、精度はあまり向上していない対称性の向上程度の改良

- パラメータ数 314ケ以上

#### 2. CMC標準モデル

·2013年~

#### 3. Verilog-Aコード供給

# ■HiSIMモデル

### 表.5 各CMOSモデル式の特徴

| モデル式  | ゲート長          | DC特性の精度                     | 高周波      |

|-------|---------------|-----------------------------|----------|

| BSIM3 | >0. 1 $\mu$ m | 高<br>(Id−Vd特性の弱反転領域を<br>除く) | 要マクロモデル化 |

| EKV   | >0. 1 $\mu$ m | 高(特にId-Vd特性の弱反転<br>領域)      | <b>↑</b> |

| BSIM4 | >0. 05μm      | 全領域で高い                      | 内蔵       |

| BSIM6 | <0. 1μm       | <b>↑</b>                    | <b>↑</b> |

| HiSIM | <0. 1 μ m     | 1                           | <b>↑</b> |

# ■HiSIMモデル

### 特徴

- ・広島大とSTARCで共同開発された純和製モデル

- (<u>Hi</u>roshima Univ. <u>S</u>TARC <u>I</u>GFET <u>M</u>odel)

- STARC: 株式会社半導体理工学研究センター

- ・CMCで世界標準モデルに認定(2011年春)。

- •GL<0. 1  $\mu$  mの微細MOS用

- 表面ポテンシャルモデル

- ・弱反転、RF等、全領域で精度が高い。

- ・パラメータ数200ケ程度

- •HiSIM2に名称変更

#### <u>\* 長所</u>

線形領域から飽和領域への移行を自動的に記述している。あらゆるモデルが原理に従って記述できる。

62

# ■表面電位と電荷基準モデル

収束性を向上させコンパクトモデルとして実用化するために、 チャージシートモデル\*を改良、様々な微細デバイスプロセスに よる物理現象を取り入れてできたのが、表面電位(Surface Potential)モデル

### HiSIMシリーズ

\* 反転層は限りなく薄く、チャネルの厚さによって電位は変化しないと仮定したモデルのこと

ソース・ドレインにおける反転電荷に注目し、面積密度関数として表していくのが電荷基準(Charge Based)モデル

BSIM3,4,6、EKVモデル

# LDMOSトランジスタ

#### Nch-LDMOSの構造

#### 特徵

- チャネル領域を拡散で作る。

- ・高耐圧、大電流(>1A)用途のためドレインドリフト領域(n-)が広い。

- → ソース/ドレイン非対称

- ・電圧制御素子のため駆動電力が小さい

- ・スイッチング特性が良い(高速) → デジタル用。

- ・動作領域(SOA)が広い

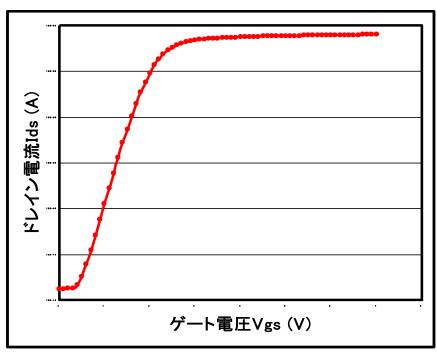

# ■ NchLDMOSのIdーVg特性

#### 特徴

- 1)Vtが高い: 2.0V以上

- 2)ソース/バックゲートがショートされている

- →高速化

### ■ NchLDMOSのIdーVd特性

回路出力段に多く使用される。スイッチング用。 ゲート幅は数cmのものもある。

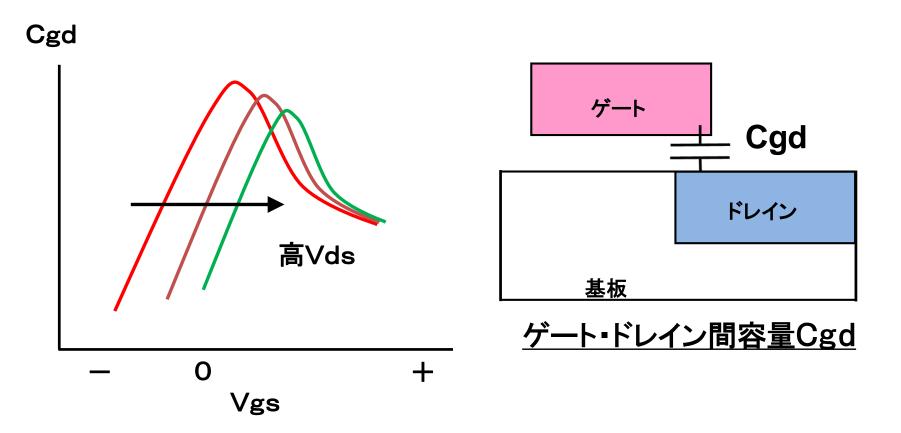

## ■ ゲート・ドレイン間容量Cgdのミラー効果

Cgdはミラー効果で(1+利得)倍に大きくなる。 数十倍になる場合もあるため、正確なモデル化が必要。

Cgd:入力容量

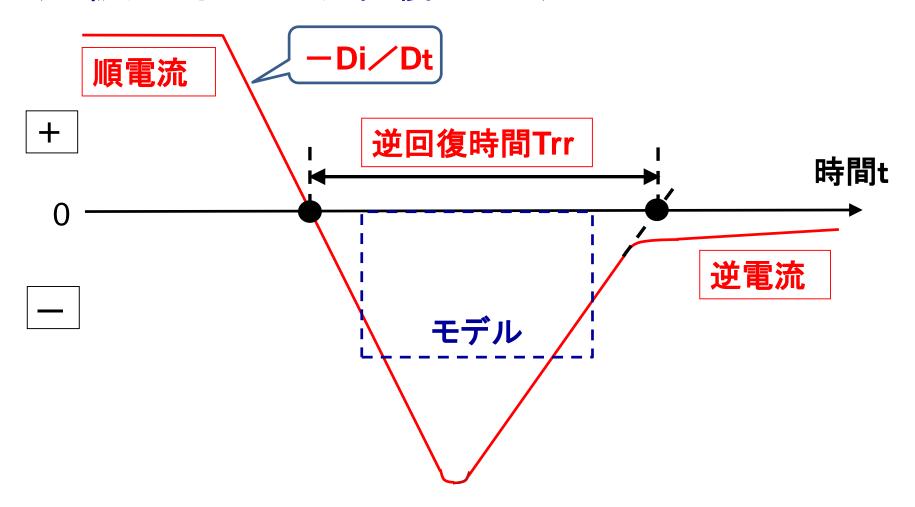

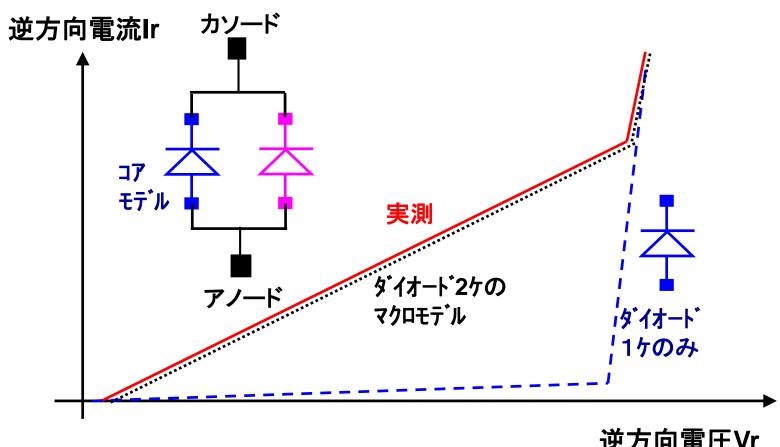

### ■ダイオードの過渡特性 (基板ダイオードの逆回復モデル)

順方向電流が流れた状態でステップ的に逆方向電圧をかけると、一時的に逆方向に電流が流れる。

# ■LDMOSモデル式

### 表.1 各LDMOSモデル式の特徴

| モデル式         | DC             | ミラー容量       | ばらつき        |

|--------------|----------------|-------------|-------------|

| BSIM3<br>マクロ | 〇(収束性が<br>不安定) | モデル化<br>難しい | モデル化<br>難しい |

| HiSIM_HV     |                |             |             |

## ■ LDMOS用モデル

### HISIM\_HV

(<u>Hi</u>rosima Univ. <u>S</u>TARC <u>I</u>GFET <u>M</u>odel for a High Voltage device.)

広島大とSTARCで作られた世界標準モデル。純日本製。 2007年、CMCで世界標準モデルに認定。

<u>HiSIM\_\_HVを使った250V Nch\_\_LDMOSの抽出データ</u>

### ■マクロモデル(サブ・サーキットモデル)

逆方向電圧Vr

複数のSPICEモデルを組み合わせたモデル。 等価回路や数式を追加することもある。

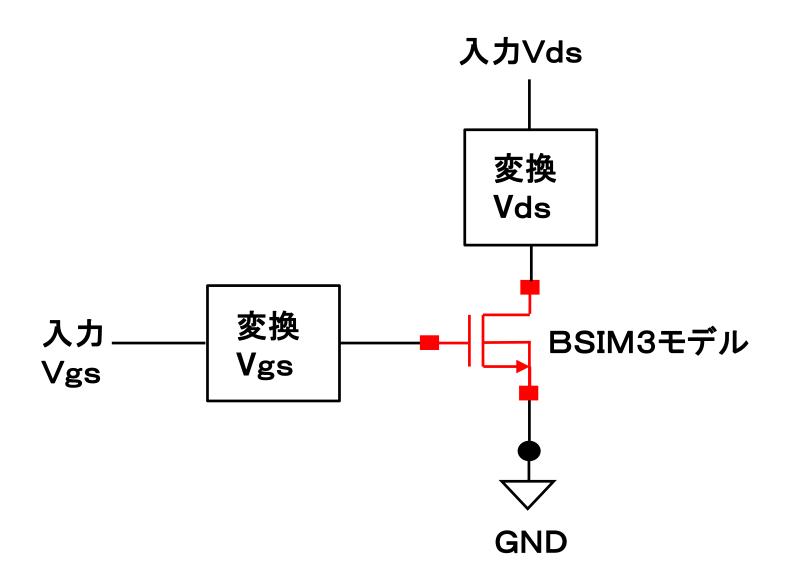

# BSIM3\_マクロモデルの例(DC)

#### ■ LDMOS用モデル

#### HISIM\_HV

(<u>Hirosima Univ. STARC IGFET Model for a High Voltage</u> device.)

#### 特徵

- •HiSIMを基本として、対象構造、非対称構造の両方に対応

- •2008年CMCでLDMOS世界標準モデルに認定

- •表面ポテンシャルモデル

- パラメータ数~250ケ

- ・ミラー容量のシミュレーション可能

- ・収束性が高い

- ・統計、コーナーモデルが容易に作成できる

## ■LDMOSモデル注意点

自己発熱領域も合わせると収束しにくい

On抵抗の精度が重要

# § 5. 各素子のモデル2

5-2. 抵抗R

\* Spectreのモデル式

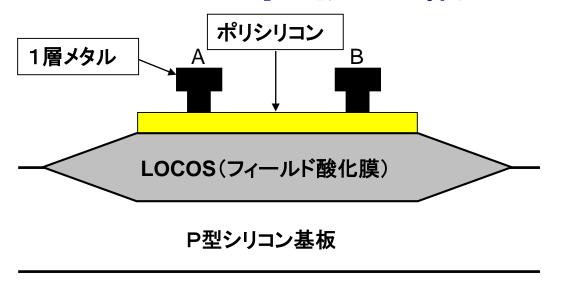

### ■ 抵抗の構造と特徴

シート抵抗Rsは、 20~30Ω/口 寄生容量が小さく、 電圧で抵抗値は変化 しにくい。 高周波回路向き。 温度で変化しやすい。

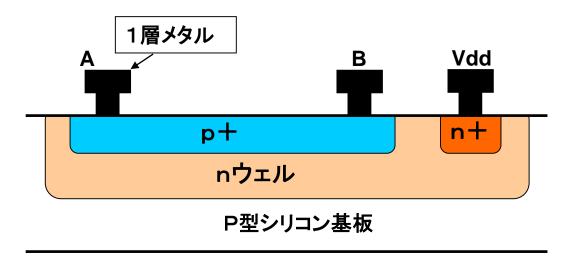

#### ポリシリコン抵抗

シート抵抗Rsは、 N+;20~30Ω/ロ P+;50~100Ω/ロ Vdd電圧が高いと 抵抗値が増加する。 バイアス回路用。

Vdd:拡散層下の接合の電位

P+拡散抵抗

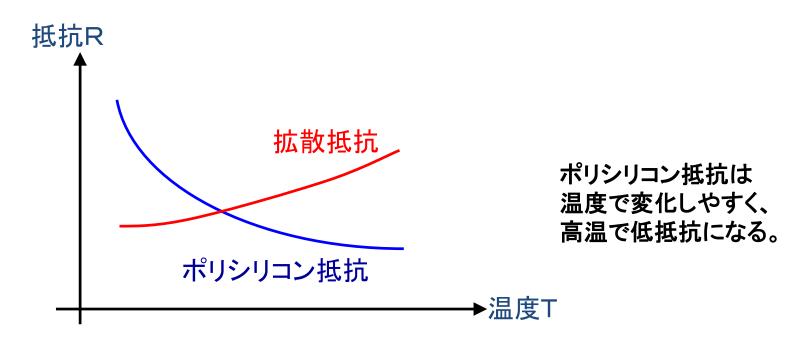

#### ■抵抗の温度特性

抵抗値は温度と電圧で変化する。

抵抗值R=R(常温27°C)\*[1+TC1\*T+TC2\*T^2]

T(℃):温度-27

TC1:1次の温度係数 TC2:2次の温度係数

\* Spectreの場合。

なおHSPICEでは常温が25℃。各シミュレータでの常温の定義に注意。77

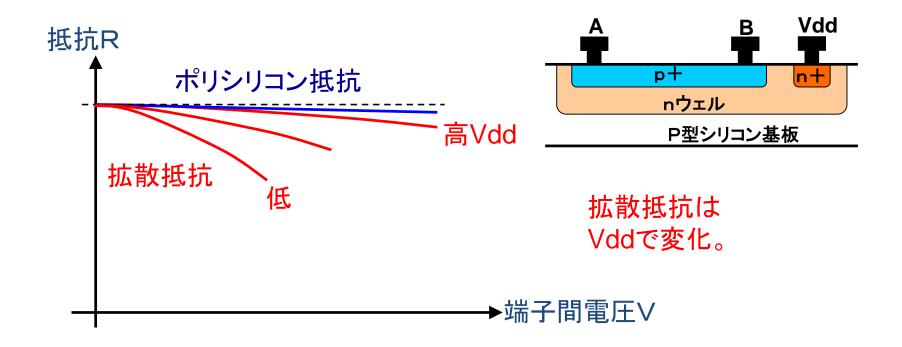

#### ■抵抗の電圧特性

抵抗値は温度と電圧で変化する。

抵抗值R=R(0.1V時)\*[1+VC1\*V+VC2\*V^2]

V: 端子間電圧

VC1:1次の電圧依存係数 VC2:2次の電圧依存係数

#### ■抵抗の温度特性、電圧特性モデル

#### 抵抗值=(温度特性)\*(電圧特性)

抵抗值R = R(室温, 0.1V時)

T(°C):温度-27(常温)

V(V): 端子間の電圧

TC1、TC2: それぞれ1次、2次の温度係数

VC1、VC2:それぞれ1次、2次の電圧依存係数

\* Spectreの場合。常温が25℃の回路シミュレータもあ

ることに注意。

# § 5. 各素子のモデル2

5-3. 容量C

\* Spectreのモデル式

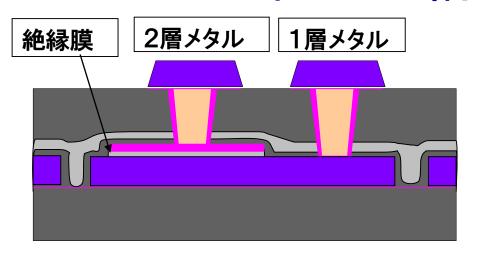

#### ■容量の構造と特徴

単位容量:1fF/um<sup>2</sup>程度 メタルのため容量は高精度。 高周波回路向き。

メタル・絶縁膜・メタル(MIM)

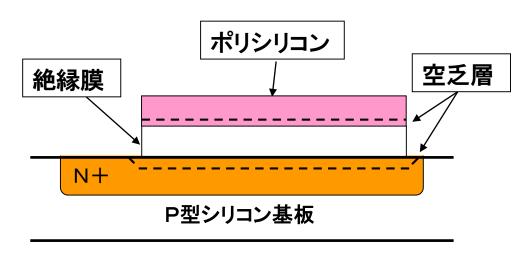

単位容量が数fF/um<sup>2</sup>のため 面積が小さい。 空乏層が電圧で広がる影響で 容量値が変わる。

ポリ・絶縁膜・拡散層

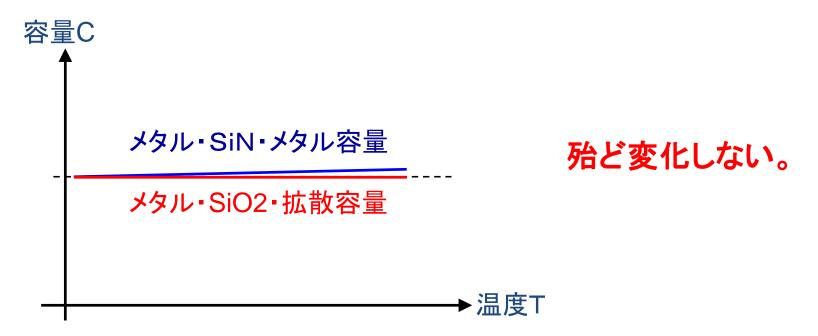

### ■容量の温度特性

容量値C=C(27°C)\*[1+TC1\*T+TC2\*T^2]

T(°C): 温度-27

TC1:1次の温度係数 TC2:2次の温度係数

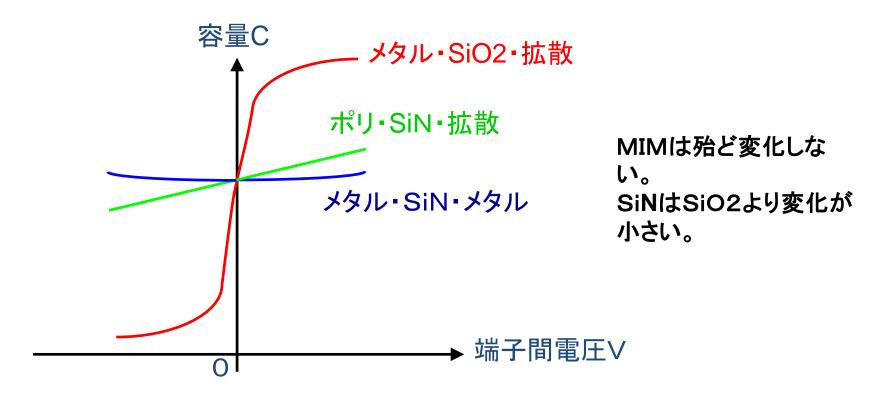

### ■容量の電圧特性

容量值C=C(0.1V時)\*

$[1+VC1*V+VC2*V^2+VC3*V^3+VC4*V^4]$

V(V): 端子間電圧

VC1~VC4:それぞれ1次~4次の電圧依存係数

#### ■容量の温度特性、電圧特性モデル

#### 容量值=(温度特性)\*(電圧特性)

容量値C = C(室温, 0.1V時)

\*[1+TC1\*T+TC2\*T^2]

\* [1+VC1 \* V+VC2 \* V^2+ VC3 \* V^3 + VC4 \* V^4]

T(°C):温度-27、 V(V):端子間電圧

TC1、TC2: それぞれ1次、2次の温度係数

VC1~VC4:それぞれ1次~4次の電圧依存係数

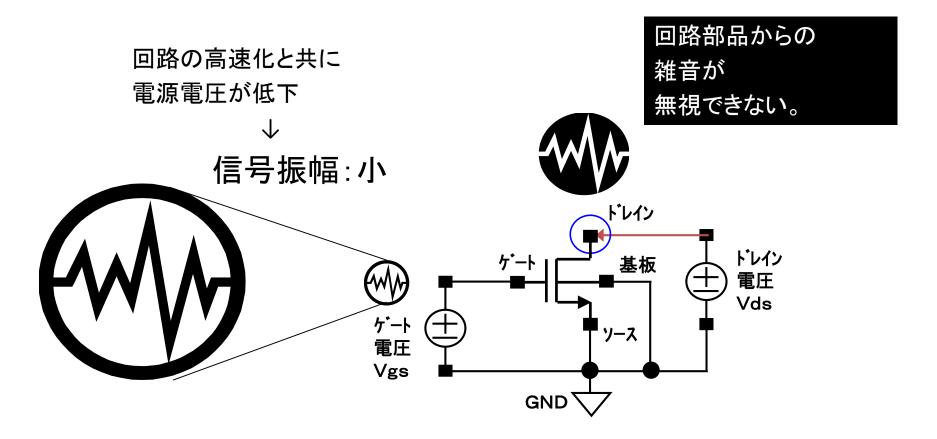

## § 6. 1/f/イズ

デバイス自体からのノイズ

### ■ノイズ(雑音)とは

(処理対象となる情報以外の)不要な情報のこと。

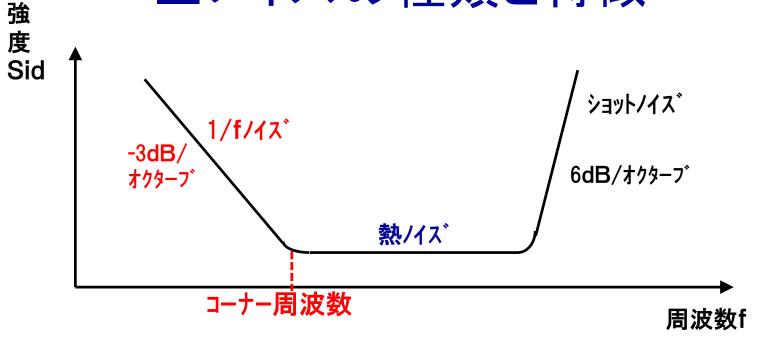

## ■ノイズの種類と特徴

#### 図 ノイズ強度の周波数特性

<u>・1/</u>fノイズ

強度∝1/周波数f (唯一モデル化される)

- 熱ノイズ

抵抗体内の電子の不規則な熱振動によって生じる

・ショットノイズ

不連続な電流によって引き起こされる

\*コーナー周波数: 500KHzM~1MHz(サブミクロンMOS)

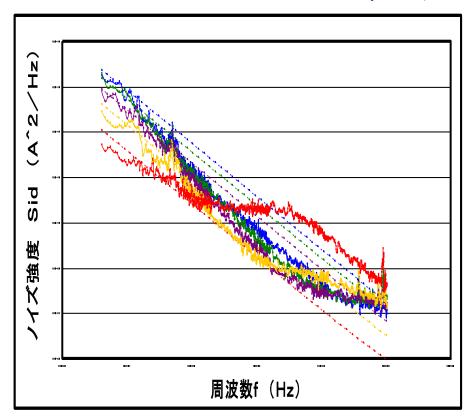

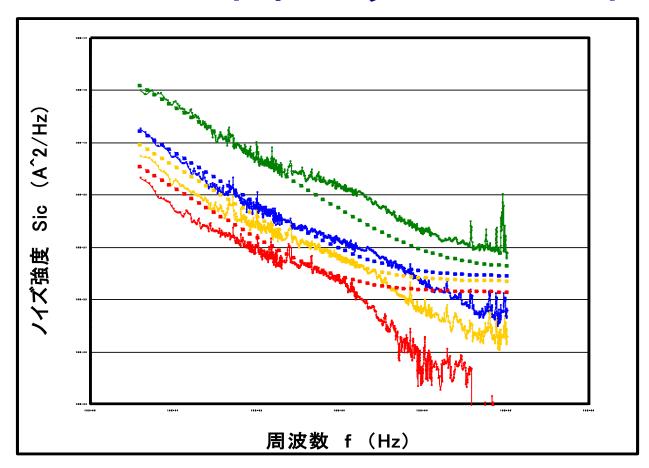

### ■MOSの1/fノイズ

図.1 NchMOS

MOSの1/fノイズは強い。 (Si界面で発生するため)

電流が多いほどノイズは強い。

#### ・・・シミュレーション値

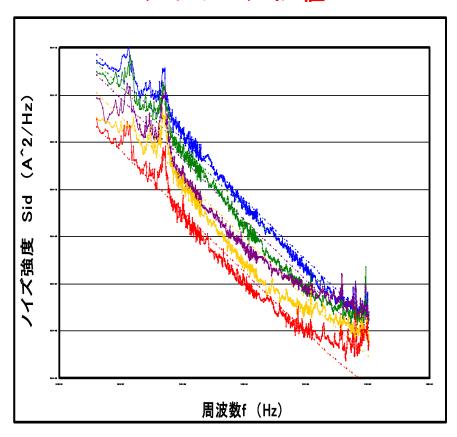

図.2 PchMOS

PchはNchの約1/3のノイズ強度 (サイズと電圧が同一の場合)

## ■NPNバイポーラの1/fノイズ

バイポーラのノイズ強度はMOSの約1/10~1/100程度。 (Nデバイス同士で電流が同じ場合。表面から深いPN接合内で発生するため)

・・・シミュレーション値

### § 7. 特性テスト

コーナーモデル、 統計モデルとミスマッチ

#### ■特性テスト

製造工程のばらつきにより、デバイス特性は変動する

回路動作への影響は?

特性の変動をモデル化する

コーナー、統計モデル

シミュレーションによる動作検証

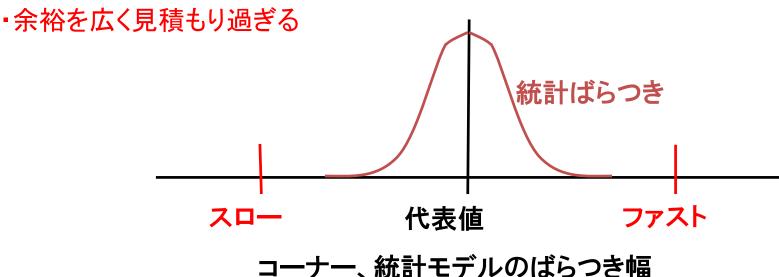

### ■コーナーモデル、統計モデル

#### § 1. コーナーモデル(スロー、ファスト)

- ・極限の場合の回路特性値(コーナー)

- •短時間で計算できる。

#### § 2. 統計モデル

- ・パラメータ値を確率的に変動させる(モンテカルロ法)

- 繰り返しのため時間がかかる

- ・実物に近いバラツキ幅を見積もれる

## ■コーナーモデル、統計モデルの特徴

|     | コーナーモデル | 統計モデル   |

|-----|---------|---------|

| 時間  | 短       | 長       |

| 精度  | 低       | 高       |

| 手 法 | _       | モンテカルロ法 |

| 特性  | 極限      | 確率的     |

| 用途  | デジタル回路  | アナログ回路  |

\*必要に応じて選択する。

## **■** コーナーモデル

#### 最悪、最良状態を表すモデル。<u>最悪状態が重視される。</u>

|      | スローモデル             | ファストモデル            |

|------|--------------------|--------------------|

| 状態   | ワースト;最悪            | ベスト;最良             |

| 回路速度 | 遅                  | 早                  |

| 電流   | 少                  | 多                  |

| 容量   | 大                  | 小                  |

| しきい値 | 高                  | 低                  |

| ゲート長 | 長                  | 短                  |

| 条件   | 各要素の最悪同士<br>の組み合わせ | 各要素の最良同士<br>の組み合わせ |

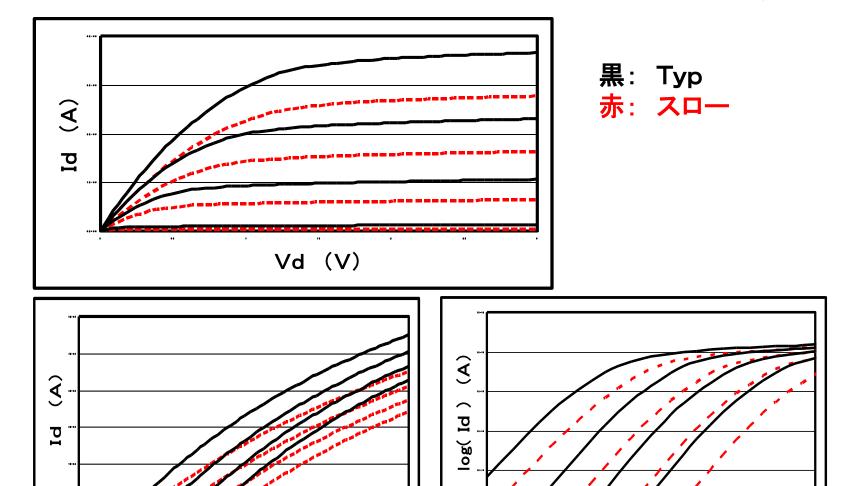

### ■コーナーモデルの例(スロー:重要)

Id-Vgでは基板バイアスを振った

Vg (V)

Vg (V)

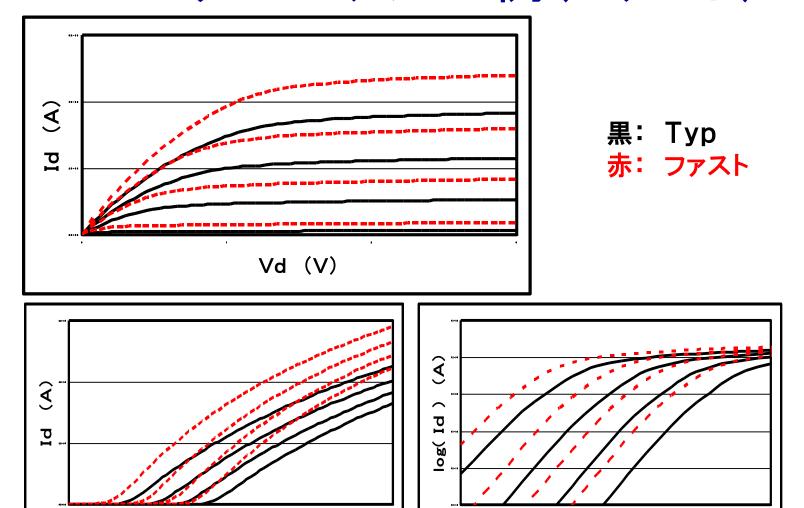

## ■コーナーモデルの例(ファスト)

Id-Vgでは基板バイアスを振った

Vg (V)

Vg(V)

### ■統計モデル

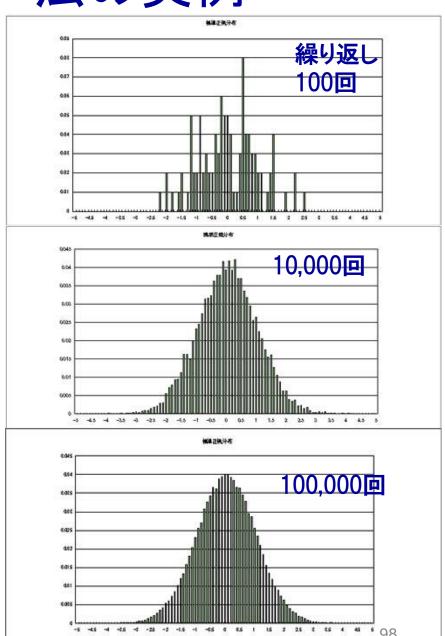

#### モンテカルロ法

- •F1レースで有名なモンテカルロのルーレットで勝つための計算方法として考案された。

- -確率論的問題を解析するための手法。

- ・対象となる条件式に、コンピュータで発生させた大量の

- 乱数をあてはめる操作を繰り返すことによって近似解を求める。

- 解析的な手法では解けない問題でも、解の値に接近できる。

#### 計算手法

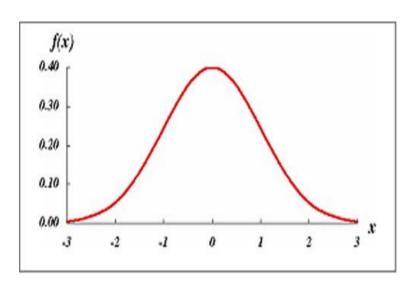

ある変数をバラつかせる場合、 変動幅内で発生する確率を 正規分布として計算させる。

正規分布

### ■モンテカルロ法の実例

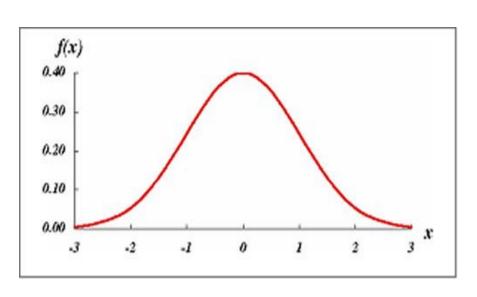

正規分布

標準偏差 σ ±3σで全体の99.7%を カバーする。

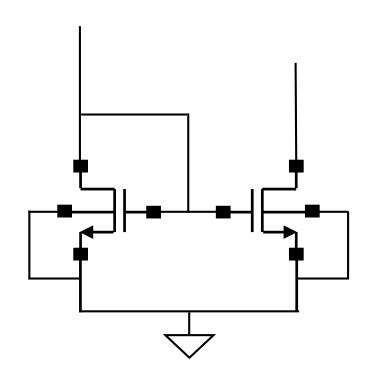

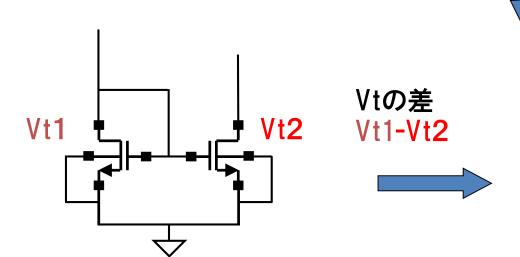

#### ■統計モデルとミスマッチ

隣接したデバイスは**完全に同一の特性ではない!**

両者の違い(ミスマッチ)を考慮して設計する。

カレントミラー回路

統計モデル内に ミスマッチをモデル化する。

\*MOSは微細化でミスマッチが 顕著になる。

\*アナログ回路用

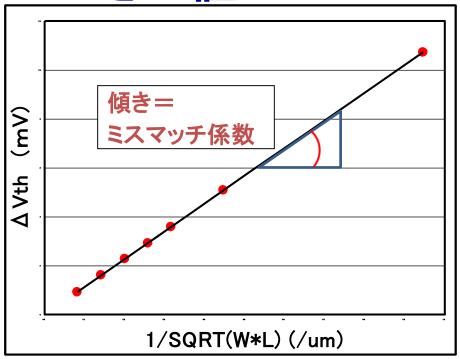

#### ■しきい値Vtのミスマッチ(Mis-Match)

#### Pelglomの式 ΔVt=A/√(W\*L)

A:ミスマッチ係数 ≒ゲート酸化膜厚

# § 8. 注意点

### ■回路シミュレータ

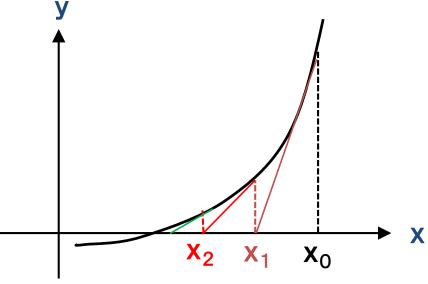

#### ニュートン・ラプソン法の計算方法

任意の関数 f(x) について、f(x)=0 となる点x を求める。 図のように適当な初期値  $X_0$  においてf(x) に接線を引けば、接線の方程式は

$$Y - f(X_0) = f'(X_0)(X - X_0)$$

(1)

であり、したがってこの接線と X 軸との交点 X1 は Y= 0 とおいて

$$X1 = X_0 - f(X_0) / f'(X_0)$$

(2)

で与えられる。

次に  $x_1$  でのf(X) への接線と X 軸との交点を  $X_2$  とする、という操作を繰り返すと、 交点はf(X) = 0の解に近付く。

i番目の繰り返しでは、

$$x_{i+1} = x_i - f(x_i) / f'(x_i)$$

(3)

になるので、適当な値 $\epsilon$  (収束半径) を決めておき、 $| x_{i+1} - x_i | < \epsilon$  になったら、 $x_{i+1}$ を解とみなす。

### ■確認事項1

#### ・シミュレーション

基本的に、設計者の予測を確認するものである。 設計者はシミュレーション結果が妥当なものか、 判断する必要がある。

#### ・回路シミュレータの役割

意図した特性、性能を実現し得るかの確認、プロセスパラメータの変動等による特性の変動評価など。

#### ・大切なこと

自分で結果の予測を行い、シミュレーション結果が 異なった場合はすぐに原因を考えてみる。

\*バイポーラ、MOS等、能動素子の影響は強い。

### ■確認事項2

・完全(Perfect)なモデルはない

(抽出時点での最上品:Best)

- <u>・シミュレーション結果はモデルに依存</u> (不良原因の半分はモデルにある)

- <u>・シミュレーション結果を都合良く解釈しない</u> (実物と比較、検討する)

- ・精度の高いモデルと回路設計の経験 (アナログ回路設計に必須なもの)

- モデルの理解が回路の設計技術を向上させる (できる人は皆、モデルも知っている)

以上、ご清聴ありがとうございました。