## 高性能デジタル電源用AD変換器とDPWM回路

木村 圭吾, 森 偉文樹, 山田 佳央, 小林 春夫 小堀 康功 † , 清水 一也, 光野 正志, 傘 昊

群馬大学工学部電気電子工学科 〒 376-8515 群馬県桐生市天神町 1-5-1

$tel: 0277-30-1788 \quad fax: 0277-30-1707 \quad e-mail: \\ \textbf{k\_haruo@el.gunma-u.ac.jp}$

†群馬大学大学院工学研究科 ルネサステクノロジ先端アナログ回路工学講座

# ADC and DPWM Generator for Digitally Controlled DC-DC Converters

Keigo KIMURA , Ibuki MORI , Yoshihisa YAMADA , Haruo KOBAYASHI Yasunori KOBORI  $\dagger$  , Kazuya SHIMIZU , Masashi KONO , Hao SAN Electronic Engineering Department, Faculty of Engineering, Gunma University 1-5-1 Tenjin-cho Kiryu Gunma Japan 376-8515

† Advanced Analog Circuit Lab., Graduate School of Engineering, Gunma University

要約— This paper describes two techniques for digitally controlled DC-DC converters. The first one is proposal to use distributed arithmetic multiplication-accumulation circuit to alleviate the successive approximation (or pilelined) ADC latency problem. The second one is new architecture of high-resolution digital PWM (DPWM) generator; its time resolution is determined by the difference of two gate delays while that of the conventional DPWM is by the gate delay itself. The proposed DPWM circuit can achieve fine time resolution with small circuit and low power. Design example of 10ps time resolution with 80ns cycle time (i.e., 13bit resolution) is shown to demonstrate the effectiveness of the proposed DPWM architecture.

キーワード: デジタル制御、電源、PWM、分散型積和演算、ビットシリアル

Keywords: Digital Control, DC-DC Converter, PWM, Distributed Arithmetic, Bit Serial

#### I. はじめに

近年の LSI の超大規模化・超微細化、マイクロプロセッサの性能向上によるスイッチング時間の高速化、LSI の低電力化による電源電圧の動作マージン減少や半導体微細化による電圧変動量の増加、またこれらを用いたシステム製品の低消費電力化要求等のため、これらを動作させる電源回路への要求はますます厳しくなってきている。この難しい要求を満たすための解の一つとして、デジタル回路と DC-DC コンバータを 1 チップ集積し最短距離で接続、1 つのシステムとして高度に管理、監視した動作特性の細かい調整を可能とするデジタル制御電源が急速に関心を集めてきている [1]-[6].表 1 にデジタル電源とアナログ電源の比較を示す.

この論文ではデジタル電源の高性能化のための AD 変換器と DSP 演算方式の工夫、およびキーコンポーネントであるデジタル PWM(Digital Pulse Width Mod-

ulation: DPWM) 生成回路の、従来に比べて高時間分解能を実現する方式を提案する.

表 1: アナログ電源とデジタル電源の比較

| <b>ペー・                                    </b> |           |                |

|------------------------------------------------|-----------|----------------|

| 項目                                             | アナログ      | デジタル           |

| 制御性                                            | 単純制御      | 複雑制御           |

|                                                | 高精度制御     | PWM:低分解能       |

| 機能性                                            | 高速応答・単純機能 | 特性改善・多機能       |

| 利用度                                            | 機種限定      | 高い汎用性          |

| 変更                                             | 困難        | プログラム変更可能      |

| 開発期間                                           | 長時間       | 短時間            |

| 制御精度                                           | 出力電圧誤差    | PWM 分解能に依存     |

| 信頼性                                            | 温度・経年変化   | 自動修正           |

| 消費電力                                           | 小さい       | 大きい ( 高速 DSP ) |

| 外部 IF                                          | 通常無し      | 通信(監視)機能あり     |

| コスト                                            | 安い        | 高い             |

|                                                |           |                |

#### II. デジタル電源の構成と DPWM

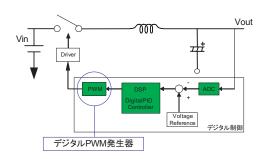

デジタル制御電源の構成を図1に示す。電源スイッチング制御部を(アナログ制御方式ではなく)ADC, DSPとデジタルPWMのデジタル信号処理システムで実現している。その動作は出力電圧(または出力電流)をAD変換してフィードバックし、基準電圧値と比較してその差を打ち消すようにデジタル信号処理回路で制御アルゴリズムを実行し、PWM信号を出力してスイッチをオンオフ制御する。アナログ電源ではコンパレータと鋸波(三角波)を用いてアナログ的にPWMを発生させていたが、デジタル電源はデジタル的にPWM信号を生成する。

図 1: デジタル制御電源の構成.

Fig.1: Block diagram of digitally controlled DC-DC converter.

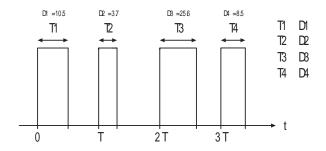

デジタル PWM 信号発生器はデジタル入力 Din に比例したデューティー比の PWM 信号を発生する回路である (図2). デジタル電源回路ではデジタル PWM の入出力データは単調性を満たしていれば線形性はさほど要求されないが, 充分な制御性能をだすためにはシミュレーション等の結果により分解能は12ビット以上必要であることがわかっている.

#### III. AD 変換器と分散型積和演算

デジタル電源での AD 変換器には逐次比較近似型もしくはパイプライン型が多用されている。両方の方式ともたとえば 12bit 分解能の場合最初の 1 クロックで MSB からデジタル値が得られるが、LSB までのデータが得られるまで 12 クロック(以上)必要である。 AD 変換器はデジタル制御のフィードバックループの中で用いられるので、スループットだけでなくレイテンシー(latency, 遅延)が問題になる。(レーテンシーが大きいとたとえばフィードバックループの不安定性につながる。) そこで 1 2 ビット全てのデータが得られた後

図 2: デジタル PWM 信号. この発生回路のデジタル入力と出力 PWM 信号デューティー比は比例関係にある

Fig.2: Digital PWM signal.

でデジタル制御演算を行うのではなく、上位のビットが得られた時点で演算を開始することを提案する.

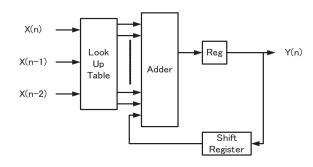

分散型積和演算とは、定係数の積和演算を ROM 等のルックアップ・テーブルを用いてビットシリアルに計算する手法のことで、乗算器を用いずに積和演算を行うことができる。この回路は米国プリンシトン大学で考案されたのでプリンシトン乗算器ともよばれる [7]. 図3に示すようにルックアップテーブル、加算器、レジスタ、シフトレジスタの四つで構成される。X(n),X(n-1),X(n-2)はデジタル入力であり、事前にルックアップテーブル内のメモリに入力に対する計算結果を記憶させておきデータを出力させる。 X(n),X(n-1),X(n-2) の最上位ビットからデータを入力させ、1 クロックごとに 1 ビット左シフトを行ないながら累積加算を行う、X(n),X(n-1),X(n-2) の最下位ビットまで計算が終われば Y(n) にデータを出力させる。

図 3: 分散型積和演算回路構成.

${\bf Fig.3:\ Block\ diagram\ of\ distributed\ arithmetic\ logic.}$

この方式を用いればビットシリアル演算を行うので 逐次比較 AD 変換器 (またはパイプライン AD 変換器) の MSB のデータが得られた時点から、たとえばデジ タル PID 等の演算を開始することができる. 逐次比較 AD 変換器で LSB の出力結果が得られるまで計算を待つ必要がないので、レーテンシーの問題が軽減できる.

IV. 高時間分解能 DPWM 発生回路の設計 目標仕様:

1周期: 80ns

(AD 変換器は 12.5MS/S(=1/80ns) で動作.)

**分解能**: 13bit

時間分解能:  $10ps (= 80ns/2^{13})$

使用可能なクロック:  $f_{clk}$  100MHz,  $f_s$  12.5MHz

米 TI 社のデジタル制御 IC (UCD9K,2005) が時間 分解能 150[ps] である. また、デジタル電源での ADC と DPWM はデジタル制御が充分な精度をもって動作 するためには 12bit(以上) 必要であることが我々の経 験からわかっている.

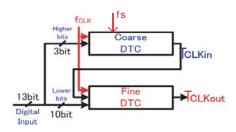

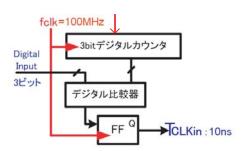

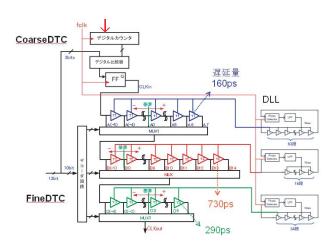

DPWM 全体回路構成: デジタル PWM 全体回路構成を図 4 に示すように設計する. 13 ビットのデジタル信号を入力とし、CLKout を PWM 出力信号である. タイミングの基準クロックとして fclk=100[MHz]を与え、Coarse DTC (粗い時間分解能の DTC) と Fine DTC (細かい時間分解能の DTC) で構成する. DTC とは Digial-to-Time Converter の略で、デジタル入力から時間出力を得るものである. 13 ビットのデジタル入力に号を上位 3 ビットと下位 10 ビットに分け、上位をCoarse DTC に下位を Fine DTC に入力する.

Coarse DTC は基準クロックで動作する 3 ビットのデジタル・カウンタで構成し、その出力 CLKin を Fine DTC に入力する. Fine DTC ではゲート遅延やマルチプレクサ等によってアナログおよびデジタルの両方の回路を用いて 10bit のタイミング信号を生成する.

図 4: DPWM 回路の全体構成図.

Fig.4: Block daigram of whole DPWM circuit.

Coarse DTC の仕様: AD 変換器のサンプリングクロック  $f_s(=12.5 \mathrm{MHz})$  を入力基準タイミングとして時

間分解能 10ns で遅延させた信号  $CLK_{in}$  を出力する.

1周期: 80ns (=1/12.5MHz)

分解能: 3bit (デジタル 3bit データで与える.) 出力  $CLK_{in}$  の時間分解能: 10ns (= $80ns/2^3$ )

外部からの基準クロック  $f_{clk}$ : 100MHz

Fine DTC の仕様: 入力信号を  $CLK_{in}$  とし、その立ち下がリタイミングから時間分解能  $10 \mathrm{ps}$  で遅延させた信号  $CLK_{out}$  を出力する.

1周期: 10ns

分解能: 10bit (デジタル 10bit データで与える.) 出力  $CLK_{out}$  の時間分解能: 10ps (=10ns/ $2^{10}$ )

外部からの基準クロック  $f_{clk}$ : 100MHz

Coarse DTC の構成と動作: Coarse DTC を図 5 に示すように構成する.  $f_s$ =12.5MHz でリセットされ  $f_{clk}$ =100MHz で動作するデジタルカウンタと, その出力と上位 3 ビットの値を比較するデジタル比較器およびリタイミング用のフリップフロップからなる. デジタルカウンタ出力値と 3 ビットデジタル入力が一致したとき  $CLK_{in}$  が High から Low になる. すなわちここでの時間分解能は  $1/f_{clk}$ =10ns である.

図 5: Coarse DTC の構成.

Fig.3: Coarse DTC configuration.

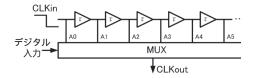

Fine DTC の従来の構成と問題点: 従来の Fine DTC は図 6 に示すような構成をとるものが多い. Coarse DTC からの出力  $CLK_{in}$  を入力とし,バッファ遅延線を通して遅らせた信号を作り出す. マルチプレクサで下位 10 ビットのデジタル入力に対応した遅延信号を選択して CLKout として出力する. ここでの時間分解能はバッファ遅延 au である. すなわち,従来の Fine DTC (図 6) では最小時間分解能がバッファ遅延(ゲート遅延)au できめられてしまい半導体のプロセス性能に依存する. この構成で高時間分解能を得るためにはゲート遅延を微小にしていく必要があり,例えば分解能 10

図 6: 従来の Fine DTC 部の構成. デジタル Din が "2" のとき、出力  $CLK_{out}$  に A2 が選択される.

Fig.6: Conventional fine DTC circuit.

ビットを実現させるためには  $2^{10}-1=1023$  個のバッファが必要となり回路規模が大きくなる. また使用テクノロジを決めれば 消費電力  $\times$  ゲート遅延量 = 一定であるので、このように回路規模が大きく、バッファーつあたりの遅延量が大きい構成では相乗効果で Fine DTC の消費電力は非常に大きくなる. しかし本提案では、一つのゲート遅延  $\tau$  よりも小さな時間分解能を達成でき、かつバッファ数を大幅に削減できる Fine DTC の構成を提案する. これにより消費電力と回路規模を大幅に削減できる.

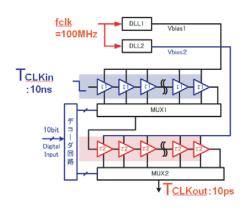

#### V. Fine DTC 新アーキテクチャの提案

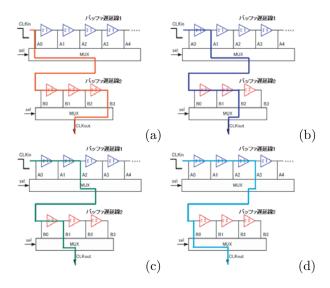

従来の構成と問題を受けて Fine DTC の新規提案を行う。時間分解能が (「ゲート遅延  $(\tau)$ 」ではなく)「2つのゲート遅延の差  $(\tau_1-\tau_2)$ 」である、より高時間分解能 PWM 回路が実現できる構成について記述する。提案 Fine DTC の構成: 提案する Fine DTC の構成を図 7 に示す。これはバッファ遅延線を 2 つ用いているところに特徴がある。それぞれバッファ遅延線 1 、2

図 7: 提案する Fine DTC の構成. Fig.7: Proposed fine DTC circuit.

のゲート遅延値  $\tau_1$ ,  $\tau_2$  は基準クロックと DLL (Delay Locked Loop) によって遅延量を自動制御・調整する.

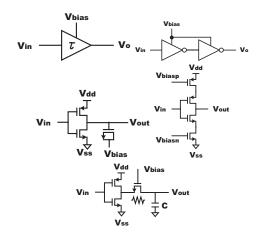

$\tau_1$ ,  $\tau_2$  のゲート遅延量の関係を最適に設定する。下位のデジタル入力に応じて 2 つのマルチプレクサで経路を選択し「 2 つのゲート遅延差」の時間分解能を実現する。選択アルゴリズムはデコーダ回路部に与える。バッファ回路は例えばバイアス制御インバータ回路を2 段縦続接続させて実現できる (図 8).

図 8: バイアス制御バッファ回路.  $V_{bias}$  によりバッファ遅延を制御する. (上) シンボル, 2 段接続バイアス制御インバータ回路による実現例 (下) 実現回路例.

Fig.8: Bias controlled buffer circuits.

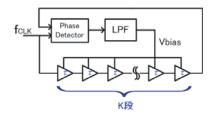

図 9 に示すように DLL 内のバッファ遅延線もこの バッファから成る回路を用いる. DLL が所定の周波数 felk にロックしたとき,K 段のバイアス制御バッファ回路 の出力信号は入力信号に比べてちょうど 1 周期 (1/felk) だけ遅れているので, そのバッファ遅延  $\tau$  は,

$$\tau = \frac{1}{K \cdot f_{clk}} \tag{1}$$

となる. このときのバイアス電圧 Vbias (図 9) をバッファ遅延線 1 または 2 (図 7) に供給すればそれを構成するバッファ遅延も式 (1) の値にすることができる.

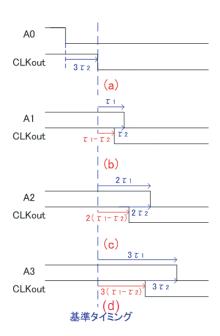

また、マルチプレクサは内部の各パス間に遅延差のないように等長配線レイアウト設計する必要がある. 提案 Fine DTC の動作 : 提案する Fine DTC の動作は、バッファ遅延線 1 でゲート遅延  $au_1$ 、バッファ遅延線 2 では  $au_2$  のバッファを使用する.その関係が  $au_1 > au_2$  となるように調整し、時間分解能  $\Delta au (= au_1 - au_2)$  を実現する 2 つの遅延線からの信号のマルチプレクサでの選択方法とタイミングチャートを図 10、図 11、図 12 に示

図 9: バッファ遅延  $\tau$  を自動調整する DLL 回路構成. Fig.9: DLL circuit to adjust the buffer delay

す. 図 11 より、バッファ遅延線 2 のバッファ数を N 個 (図 10 の場合は N=3) とすると、 $\tau_1$  と  $\tau_2$  の関係は次のように決まる。これよりバッファ遅延線を多段用意することによって、バッファ単体の遅延量が大きくなっても、全体の時間分解能は高精度にすることが出来る。

$$\tau_1 = (N+1)\Delta\tau, \qquad \Delta\tau = \tau_1 - \tau_2$$

$$\tau_2 = \frac{N}{N+1}\tau_1 \qquad (2)$$

となる. この  $\tau_1$  と  $\tau_2$  の関係は  $\mathrm{DLL}(\boxtimes 9)$  によって固定し, それぞれのバッファ回路図 8 のように, バイアス制御により制御される.

なおバッファ遅延  $\tau_1$  をつくるための DLL1 内のバッファの個数を  $K_1$ , バッファ遅延  $\tau_2$  をつくるための DLL2 内のバッファの個数を  $K_2$  とすると式 (1),(2) から次の 関係が得られる.

$$\frac{K_1}{K_2} = \frac{N}{N+1}. (3)$$

3 段バッファ遅延線を用いた Fine DTC: さらに3 段バッファ遅延線を用いて Fine DTC を構成することを検討した。その全体 DPWM 回路を図13に示す。2 段、3 段、4 段バッファ遅延線構成をと比較した結果、回路規模・消費電力化の観点から3 番構成が最も効率が良いという結果を得ている。また、多段構成にすると経路選択アルゴリズムが複雑になるが、回路規模の観点から最適・システマテックなアルゴリズムを拡張ユークリッド互除法をベースにして開発した。(これに関しては別途報告予定である[8]。)

Fine DTC 部の設計結果の比較:

- (i) 従来の1段バッファ遅延線 Fine DTC ( 図 6): バッファ総数 1024 個、遅延  $\tau = 10ps$ .

- (ii) 提案 2 段バッファ遅延線 Fine DTC (図 7): バッファ 総数 82 個. 初段目バッファ遅延線 遅延  $\tau_1 = 160ps$ ,

バッファ個数 38 個. 2 段目バッファ遅延線 遅延  $\tau_2 = 290ps$ , バッファ個数 44 個.

(iii) 提案 3 段バッファ遅延線 Fine DTC (図 13): バッファ総数 37 個. 初段目バッファ遅延線 遅延  $\tau_1=160ps$ , バッファ個数 12 個. 2 段目バッファ遅延線 遅延  $\tau_2=730ps$ , バッファ個数 15 個. 3 段目バッファ遅延線 延線 遅延  $\tau_3=290ps$ , バッファ個数 10 個.

#### VI. まとめと今後の課題

この論文ではデジタル制御電源の高性能化のために次のことを行った。(i) 逐次比較 AD 変換器のレーテンシーを軽減するために後段の DSP で MSB からビットシリアルに積和演算を行える分散型積和演算方式を用いることを提案した。(ii) 高時間分解能 PWM 生成回路の新アーキテクチャを提案した.時間分解能が「ゲート遅延」で決まっていた従来のデジタル PWM から,「2つ以上のゲート遅延の差」で時間分解能が決まる新しい構成を考案した.これにより高時間分解能が得られ回路規模・消費電力も小さくできる。

謝辞 有意義なご討論をいただきましたルネサスソリューションズ, ルネサステクノロジ, 三洋半導体, 日本テキサスインスツルメンツ, 東光の方々に感謝します.

### 参考文献

- [1] 「デジタル制御を得て電源の進化が始まる」EETimes Japan, pp.42-53 (2006 年 2 月).

- [2] 曾根元隆、「スイッチング電源におけるデジタル・DSP 制御の展望」アナログ・電源フォーラム(電源編)、日経エレクトロニクス、東京(2006年6月).

- [3] D. Freeman「デジタル電源の応用展開」アナログ・電源フォーラム(電源編), 日経エレクトロニクス, 東京 (2006 年 6 月).

- [4] K. Wang, et.al, "All Digital DPWM/DPFM Controller for Low Power DC-DC Converters," IEEE Applied Power Electronics Conference and Exposition (APEC), Dallas, TX (Mar. 2006).

- [5] J. Chen, et.al., "DPWM Time Resolution Requirements for Digitally Controlled DC-DC Converters," IEEE APEC, Dallas, TX (Mar. 2006).

- [6] K. Leung, et.al., "Design and Implementation of a Practical Digital PWM Controller," IEEE APEC, Dallas, TX (Mar. 2006).

- [7] A. Peled, B. Liu, "A New Hardware Realization of Digital Filters," IEEE Trans. Acoust., Speech, Signal Processing, vol. ASSP-22, pp.456-462 (Dec. 1974).

- [8] 木村圭吾、森偉文樹、他 "デジタル制御電源用 高時間分解能 DPWM 回路",電子情報通信学会 第20回 回路とシステム(軽井沢)ワークショップ(2007年4月).

図 10: 提案する Fine DTC 部の動作. (a) A0, B3 を選択. (b) A1, B2 を選択. (c) A2, B1 を選択.(d) A3, B0 を選択. Fig.10: Operation of the proposed fine DTC.

図 12: 提案する Fine DTC 部のタイミングチャート. (a) A0, B3 を選択. (b) A1, B2 を選択. (c) A2, B1 を選択. (d) A3, B0 を選択.

Fig.12: Timing chart of the proposed fine DTC.

```

(A0, B3)···基準

+ A T

(A1, B2) \cdots \underline{\tau} 1 \underline{\tau} 2 = \underline{\Delta} \underline{\tau}

+ A T

(A2, B1) \cdots 2 \tau 1-2 \tau 2 = 2 \Delta \tau

+ A T

(A3, B0)

3 \tau 1 - 3 \tau 2 = 3 \Delta \tau

+ A T

(A1, B3) \tau 1 = 4 \Delta \tau

(A2, B2) 2 \tau 1 - \tau 2 = \tau 1 + \Delta \tau

(A3, B1) 3\tau 1-2\tau 2 = \tau 1+2\Delta \tau

(A4, B0) 4 \tau 1-3 \tau 2 = \tau 1+3 \Delta \tau

(A2, B3) 2\tau 1 (\tau 1=4\Delta \tau)

(A3, B2) 3 \tau 1 - \tau 2 = 2 \tau 1 + \Delta \tau

(A4, B1) 4 \tau 1-2 \tau 2 = 2 \tau 1+2 \Delta \tau

(A5, B0) 5 \tau 1-3 \tau 2 = 2 \tau 1+3 \Delta \tau

```

図 11: 提案する Fine DTC 部の経路と各遅延量. Fig.11: Algorithm of the proposed fine DTC.

図 13: 3段バッファ遅延線を用いた提案 DPWM 発生回路. Fig.13: Proposed DPWM generator with three-delay-line fine DTC.