# AD変換器でのサンプリング・クロック・ジッタの 測定とその誤差補正技術の検討

清水 一也, 小林 春夫, 益子 耕一郎 †

群馬大学工学部電気電子工学科 〒 376-8515 群馬県桐生市天神町 1-5-1 tel:0277-30-1788 fax:0277-30-1707 e-mail:k\_haruo@el.gunma-u.ac.jp

#### Measurement and Error Correction of Sampling Clock Jitter in ADC

Kazuya SHIMIZU , Haruo KOBAYASHI, Koichiro MASHIKO† Electronic Engineering Department, Gunma University, 1-5-1 Tenjin-cho Kiryu 376-8515 † Semiconductor Technology Academic Research Center (STARC), Yokohama 222-0033.

要約 - This paper proposes a technique to reduce sampling clock jitter effects in high speed ADCs. First, we measure the sampling clock jitter each cycle using an on-chip time digitizer circuit, where its reference timing is (i) the previous rising timing edge of the sampling clock itself, or (ii) high frequency signal generated by PLL from the sampling clock; note that jitter of high frequency signal is small. Next, we correct the ADC output based on measured sampling clock jitter with DSP. We describe its basic concept and circuit configuration.

キーワード: AD 変換器, サンプリング, ジッタ, タイムデジタイザ回路, 信号補間

**Keywords:** ADC, Sampling, Jitter, Time-to-Digital Converter, Interpolation

### I. はじめに

近年のプロセス技術の微細化、アーキテクチャ・回路構成の工夫により AD 変換器の性能向上・低消費電力化が著しい. しかしながら高周波入力信号を AD 変換する場合、サンプリング・クロックのジッタによる時間軸の誤差が振幅の誤差となる精度劣化の問題が顕在化してくる [1]. 入力信号のスルーレートが大きい高周波信号や大振幅信号においてサンプリング・クロック・ジッタの影響は大きくなり AD 変換器の SNR が大きく劣化してしまう. また SoC (System-on-Chip) 上では AD 変換器に直接ジッタの少ないクロックを供給することが難しくなってきている.

そこでこの論文では ADC のクロック・ジッタの影響を軽減する手法として新たなアーキテクチャを提案する. クロックジッタをオンチップ上で測定し, その値をもとに AD 変換後のデジタルデータを時間補間・間引きにより等時間間隔のデータを得るという方式である. AD 変換システムでサンプリング・クロックのジッタを測定して, それをもとにデジタル誤差補正する提案は(筆者らが知る限り)これまでない. その理由として,「クロック・ジッタを測定するためにはジッタのない基準クロックが必要で, ジッタのない基準クロック

があればそれを ADC のサンプリングクロックにすればよい」という矛盾があるためである. しかしながら, 上記矛盾を解決した 2 つの方法を提案する.

- (i) クロックの各周期を毎回デジタル的に計測する. すなわち 1 つ前の立ち上がリタイミングから現時点での立ち上がリタイミングをタイムデジタイザ回路で測定する. サンプリング・クロックの一つ前の立ち上がリタイミングが基準クロックになる.

- (ii) 外部から供給されるクロックを SoC 上で PLL で逓倍周波数信号を発生する. 高周波信号になるほどジッタが小さくなるのでそれを基準クロックとして使用して低周波のサンプリング・クロックのジッタをタイムデジタイザで測定する.

オンチップ・タイムデジタイザの時間分解能は近年  $10 \mathrm{ps}\text{-}1 \mathrm{ps}$  程度にまでなってきているので [2]-[6], これらの技術を利用することを想定する. (i), (ii) の場合も、測定したジッタ値(デジタル値で与えられる)とそのときの AD 変換出力をもとに DSP でデジタル補正を行う. そのデジタル補間アルゴリズムも DSP 分野では様々提案されている [7, 8, 9].

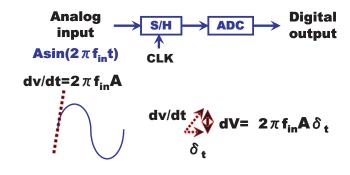

II. AD 変換器, クロック発生回路とジッタ クロック・ジッタとはクロックの立ち上がり・タイミ

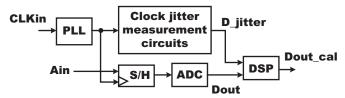

図 1: 提案する AD 変換システムでのクロックジッタの測定 と補正の構成.

Fig.1: Prposed ADC system with jitter measurement and correction.

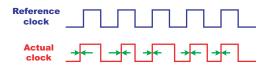

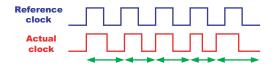

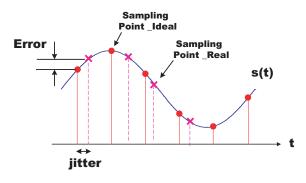

ングの基準タイミングからの揺らぎである。細かくは 図 2 の上図のような基準 (理想) タイミングとの時間 差ジッタや、図 2 の下図のような各周期の長さのジッタ に分類されるが、ここでは「実際のクロックの各立ち上がリタイミングの基準タイミングからの時間差」を 考える。図 3,4 のように信号 s(t) をサンプリング周波

#### **■ Time Interval Error**

#### Cycle to cycle jitter

図 2: クロックジッタの説明.

Fig.2: Explanation of clock jitter.

数  $f_s$  でサンプリングする場合について考える. クロックジッタ  $_t$  がある場合, サンプリング値に振幅誤差 V が生じる.

$$V = \frac{ds(t)}{dt} \times \quad t.$$

正弦波入力の場合は次のようになり、s(t) の周波数  $f_{in}$  が高くなり振幅 A が大きくなるにつれ (すなわち入力信号のスルーレートが大きくなるにつれて)振幅誤差 V が大きくなることがわかる.

$$s(t) = A\sin(2 \quad f_{in} \quad t)$$

$$\frac{ds(t)}{dt} = 2 \quad f_{in}A\cos(2 \quad f_{in} \quad t).$$

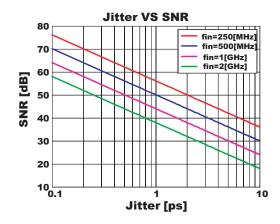

クロックジッタの影響による  ${

m AD}$  変換器の  ${

m SNR}$  を計算すると信号成分は  ${

m A^2/2}$  であることに注意すると次

のようになる (図 5,[1]).

$$SNR_{jitter} = -20 \log(2 \quad f_{in} \quad t) [dB].$$

一方, クロック発生の立場からみると, 高周波クロッ

図 3: サンプリングの際のクロックジッタによる誤差.

Fig.3: Error due to clock jitter at sampling.

図 4: AD 変換器でのクロックジッタによる誤差.

Fig.4: Error due to clock jitter in ADC.

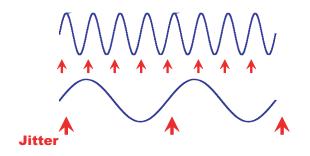

クではチップ内では正弦波に近い波形になり、高周波になるほどまた大振幅になるほど(すなわちスルーレートが高いほど)ジッタが小さくなることが知られている(図 6). 高周波信号のジッタの標準偏差はその周波数の平方根に反比例する. これは熱雑音の影響による(クロックの論理「0」と「1」のスレショルドを横切る)タイミングのずれが小さくなる、アラン分散の考え方等で説明がされている.

すなわち以下のように、サンプリング回路とクロック発生回路ではジッタに対して双対の関係にある.

- サンプリング回路

- :スルーレートの大きい高周波信号,大振幅信号 ジッタによる誤差:大

- クロック発生回路

図 5: ADC のクロックジッタ, 入力周波数と SNR の関係. Fig.5: Clock jitter, input frequency and SNR in ADC.

:スルーレートが大きい高周波クロック,大振幅 クロック 発生ジッタ:小

図 6: 低周波と高周波信号のクロックジッタの比較 (スルーレートが大きいほどジッタは小さい).

Fig.6: Jitter in high and low frequency signals (smaller jitter for high frequency singal).

## III. 提案するジッタ測定と補正の構成

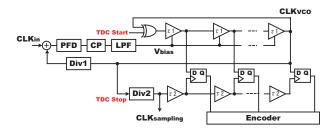

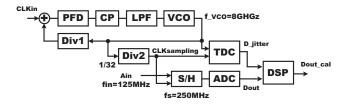

図 1 のように、クロック  $CLK_{in}$  を入力して PLL によってサンプリングクロックを生成する。クロックジッタ測定回路によって、そのサンプリングクロックのジッタを測定し、 $D_{jitter}$  を得る。また、サンプリングクロックを用いて入力信号を AD 変換し、Dout を得る。そして、後段の誤差補正回路によって、測定したジッタ値と AD 変換出力を用いて信号補間をして、デジタル信号処理によって誤差補正を行う。

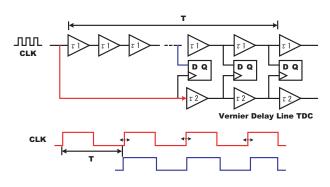

## IV. 提案ジッタ測定手法 1

最初にクロックの各周期を毎回デジタル的に計測する、 すなわち1つ前の立ち上がリタイミングから現時点で の立ち上がリタイミングをタイムデジタイザ回路で測 定する手法を提案する(図7). AD 変換器のサンプリング・クロック *CLK* を入力する. バッファ遅延によってクロックの周期Tだけ遅らせた, ディレイラインの上のパスを基準クロックとして, サンプリング・クロックの周期のばらつきジッタを測定する. 時間の測定にはタイムデジタイザを用いる. タイムデジタイザ内のそれぞれのバッファの1段あたりの遅延は, PLL もしくは DLL を用いてロックさせることで調節可能である. このようにして, 遅延Tを正確に作るとことによって, 1 周期前のクロックの立ち上がりを基準として, 次の周期の立ち上がりタイミングのずれを計測する. これにより自分自身のクロックで自分自身のジッタを測定することが可能である.

図 7: 提案するクロックジッタの測定法 1.

Fig.7: Proposed clock jitter measurement method 1.

#### IV. 提案ジッタ測定手法 2

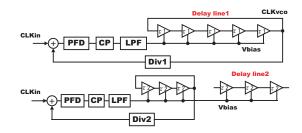

もう1つのジッタ測定法として図8に示す方法を提 案する. 前述のように高周波信号(クロック)発生回 路においては、信号のスルーレートが大きい高周波ク ロックや大振幅クロックでは発生ジッタが小さくなる. この特徴を生かして、外部から与えられるジッタを含 んだ低周波クロック  $CLK_{in}$  から PLL によって高周波 のクロック  $CLK_{VCO}$  をつくり、そのクロックを分周 して、低周波のサンプリングクロック  $CLK_{sampling}$  を つくる [10]. クロック  $CLK_{vco}$  は PLL 内高周波信号な のでジッタの少なくなりこれを基準タイミング信号と し、低周波の比較的ジッタの多いサンプリングクロック  $CLK_{sampling}$  のジッタを TDC を用いて測定する. そ れによって TDC の時間分解能でサンプリングクロッ ク $CLK_{sampling}$ のジッタのデジタル値が得られる. そ のジッタのデジタル値と入力信号が AD 変換されて得 られた  $D_{out}$  を用いてデジタル信号処理のによるジッ タ補正を行う (5節参照). これによりジッタによるサ ンプリング値の電圧誤差を補正してジッタによる影響 を軽減することができる.

後段で誤差補正を行なうので、ある仕様の AD 変換器を実現する場合に抑えなければならないクロックジッタ値を、TDC の基準クロックとして用いる VCO 出力の高周波クロック  $CLK_{VCO}$  で満たせばよいことになり、サンプリングクロックのジッタに対する要求を緩和することができる (6節参照).

図 8: 提案するクロックジッタの測定法 2.

Fig.8: Proposed clock jitter measurement method 2.

[10] に示されているように、AD 変換器システムでは AD 変換器だけでなくそのクロック発生回路も考慮して設計することが重要になってくると思われる.

## V. ジッタによる誤差のデジタル補正

測定したジッタ値をもとにした, ジッタによる AD 変換器出力の誤差のデジタル補正の問題設定は次のようになる.

「サンプリング周期を T,n 番目のサンプリング時のジッタ  $\delta_t(n)$  のタイムデジタイザによるデジタル測定値を  $D_{jitter}(n)$ , このときの AD 変換器出力を  $D_{out}(nT+\delta_t(n))$  とする。このとき n=0,1,2,3,..., の  $\{\delta_t(n),D_{out}(nT+D_{jitter}(n))\}$  のデータから  $\{D_{out}(nT)\}$  をデジタル信号処理により推定する。」

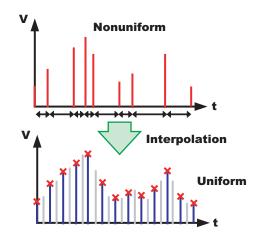

これは非一様な時間間隔でサンプリングされたデータの信号処理であるが(図9)、その手法は複数提案されている[7][8][9]. 例えば、我々は複数の非等間隔の点から等間隔の点に信号補間をして等間隔のサンプリングデータを得る方法を検討した[6].

# VI. 提案手法によるクロックジッタによる誤 差改善の見積もり

入力正弦波信号の振幅を A とし、ADC の分解能を n[bit] すると、 $(1/2)LSB = A/2^{n+1}$  となる.このとき、電圧誤差が (1/2)LSB になるときのジッタの値を求める.入力 周波数はナイキスト周波数までとすると  $(f_{in} \leq f_s/2)$ 、

図 9: ジッタによる非一様時間間隔信号の補間による一様時間間隔信号推定.

Fig.9: Nonuniform time interval signal due to jitter and estimation of uniform signal.

入力信号の傾きの最大値は次のようになる.

$$\frac{dV}{dt}_{max} = 2\pi \cdot f_{in} \cdot A.$$

このときジッタ値を  $_t$  とすると、電圧誤差は次のようになる.

$$dV_{max} = 2\pi \cdot f_{in} \cdot A \cdot t$$

.

となる. これが (1/2)LSB 以下になればよい.

$$_{t}<\frac{A}{2^{n+1}\boldsymbol{\cdot}\ 2\pi\boldsymbol{\cdot}\ f_{in}\boldsymbol{\cdot}\ A}=\frac{1}{2^{n+2}\boldsymbol{\cdot}\boldsymbol{\pi}\boldsymbol{\cdot}\ f_{in}}.$$

ここで、具体的な AD 変換器の仕様として  $10[\mathrm{bit}]$ 、 $250[\mathrm{MS/s}]$  の場合を考える。  $f_{in}{=}125\mathrm{MHz}$  として上式より計算すると許容ジッタは次のようになる。

250[MHz] のクロックにおいてジッタをこの値に抑えることは現実的に非常に困難である.

次に提案手法 2 で具体的な数値を入れた図 11 について考える. VCO の発振周波数を 8[GHz], 分周器の分周比を 1/32, これより AD 変換器のサンプリングクロックの周波数は 250[MHz] となる. 入力周波数はナイキスト周波数までなので 125[MHz] としている. VCO出力の周波数を 8[GHz] としているのでそのクロックの周期は 125[ps] になる. 今回提案する手法を用いて後

段でデジタル信号処理によって誤差補正を行うことを考えると、高周波クロックにおいてジッタ値を 0.62[ps] 以内に抑えればよいことになる。ジッタの標準偏差 $_t$  が近似的に次の関係にある。

$$t = \frac{1}{\sqrt{f}}$$

.

これより.

$$_{VCO}/~_{sampling} = 1/\sqrt{32} = 0.177$$

となる. この関係を用いると等価的に 250[MHz] の場合はクロックジッタは,

$$0.62[ps]/0.177 = 3.5[ps]$$

程度となり、クロックジッタに対する要求を緩和する ことができるためより実現に近づく.

図 10: AD 変換器システムでのジッタの測定と補正(具体的数値を入れた場合).

Fig.10: Jitter measurement and correction with specific frequencies.

図 11: AD 変換器システムでのジッタの測定 (タイミング チャート).

Fig.10: Jitter measurement with specific frequencies (timing chart).

## VII. まとめと今後の課題

この論文ではクロックジッタによる AD 変換器の精

度劣化を改善する方法を提案した. クロックジッタをサンプル毎に測定しその値をもとに AD 変換器の出力データをデジタル誤差補正する. SoC での AD 変換器のクロックジッタの測定のためには外部からジッタの少ない基準クロックを与えることはできない. この問題を解決してオンチップでのクロックジッタを測定する方法を 2 つ提案した.

- (i) クロックの各周期を毎回デジタル的に計測する. すなわち1つ前の立ち上がリタイミングから現時点での立ち上がリタイミングをタイムデジタイザ回路で測定する.

- (ii) 外部から供給されるクロックを SoC 上で PLL で逓倍周波数信号を発生する. 高周波信号になるほどジッタが小さくなるのでそれを基準クロックとして使用して低周波のサンプリング・クロックのジッタをタイムデジタイザで測定する.

「AD 変換器の性能限界はデバイスの進歩ではなくクロックジッタで決まる」と言われてきて久しい. しかしながら、この論文で提案したように高性能タイムデジタイザ回路によりクロックジッタを各サンプリング毎に高精度でデジタル値として測定して、AD 変換器出力データと合わせて DSP でデジタル誤差補正する手法により「AD 変換器のジッタによる性能限界」を越えられる可能性がある.

ここでの提案手法の実現のための重要な技術はタイムデジタイザ回路である。平均遅延値の DLL 等での制御、遅延ばらつきのデジタル校正、ジッタが少なく高時間分解能のものを少ない回路量で実現することが極めて重要である。

今後は具体的な PLL やタイムデジタイザの回路構成について検討を行い、チップ試作・測定により本提案の検証を行なっていく. また非一様サンプリングデータに対する高速・高精度なデジタル信号処理についてさらに検討を行う.

微細 CMOS アナログ回路設計では、内部特性を"計測"し、その値に基づき"制御"、"信号処理"するというチップ内計測制御技術が重要になってくると思われる。今回の提案技術はその一つに位置すると考えている.

謝辞 有意義なご討論をいただきました堀田正生氏,松 浦達治氏,近藤守氏,阿部彰氏,高井伸和氏,傘昊氏に 謝意を表します.

# 参考文献

- [1] H. Kobayashi, et. al., "Sampling Jitter and Finite Aperture Time Effects in Wideband Data Acquisition Systems", *IEICE Trans. on Fundamentals*, vol. E85-A, no. 2, pp.335-346 (Feb. 2002).

- [2] J. Jansson, A. Mantyniemi, J. Kostamovaara, "A CMOS Time-to-Digital Converter With Better Than 10ps Single-Shot Precision", *IEEE JSSC*, vol.41, no.6, pp.1286-1296, (June 2006).

- [3] K. Nose, M. Kajita, M. Mizuno, "A 1ps-Resolution Jitter-Measurment Macro Using Interpolated Jitter Oversampling", *IEEE JSSC*, vol.41, no.12, pp.2112-2121 (Dec 2006).

- [4] J.Rivoir, "Fully-Digital Time-to-Digital Converter for ATE with Autonomous Calibration", *IEEE Interna*tional Test Conference, Santa Clara, (Oct. 2006).

- [5] Jochen Rivoir, "Statistical Linearity Calibration of Time-to-Digital Converters Using a Free-Running Ring Oscillator", 15th Asian Test Symposium, pp.45-50 (2006).

- [6] 清水一也, 元澤篤史, 林海軍, 小室貴紀, 小林春夫, "タイムデジタイザを用いた非同期サンプリング AD 変換器と信号処理", 電子情報通信学会 第19回回路とシステム軽井沢ワークショップ, pp.75-80 (2006年4月).

- [7] F. Marvasti, "Application of Nonuniform Sampling to Nonlinear Modulation, A/D and D/A Techniques", in *Nonuniform Sampling Theory and Practise*, Kluwer Academic Publishers, pp.647-687 (2001).

- [8] J. J. Benedetto, P. J. S. G. Ferreira, Modern Sampling Theory: Mathematics and Applications, Birkhauser, (2001).

- [9] S. Bagchi, S. K. Mitra, "The Nonuniform Discrete Fourier Transform and its Applications in Signal Processing", Kluwer Academic Publishers (1999).

- [10] 堀田正生, "ナノ CMOS 時代のアナログ回路設計の課題",電気学会電子回路研究会資料 ECT-06-38 (2006年3月).

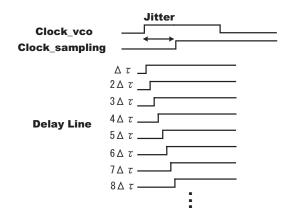

## 付録: タイムデジタイザ回路

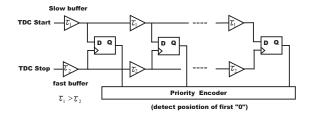

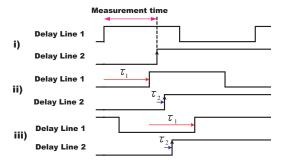

2 つのパルス間の正確な時間間隔を測る機能を CMOS IC 内に実現するタイムデジタイザ回路は, 10ps より細かな分解能・精度のものがすでに実現されている [2]-[5]. まず基準クロックで動作するカウンタによって大まかな時間間隔を推定し, 次にバッファ遅延  $(\tau_1)$  により非常に分解能の高いディレイラインを構成し, 細かな時間間隔を測定する. 図 12, 13 のようにバーニアディレイラインを用いたタイムデジタイザの構成によりさらに高時間分解能  $(\tau_1 - \tau_2)$  を得ることができる.

タイムデジタイザのスタート信号とストップ信号の 間のパルス間隔を遅延線の上と下のバッファの遅延時

図 12: バーニアディレイラインを用いたタイムデジタイザ 回路の構成.

Fig.12: Vernier delay line time-digitizer.

図 13: バーニアディレイラインを用いたタイムデジタイザ 回路のタイミングチャート.

Fig.13: Timing chart of vernier delay line time-digitizer.

間の差  $(\tau_1 - \tau_2)$  の時間分解能で検出することができる。プロセス技術の微細化に伴い時間分解能が向上していくと考えられる。また高い線形性をえるための補正技術も開発されている [4][5][6].

次に遅延時間  $\tau_1, \tau_2$  のバッファは、図 14 に示すように PLL, DLL のバイアス電圧を使用して遅延時間を自動調整することで実現できる.

図 14: 遅延  $\tau_1$ ,  $\tau_2$  のバッファの PLL による実現.

Fig.14: Automatic control of buffer delay  $(\tau_1, \tau_2)$  by PLL.

高時間分解能でジッタが少なく回路規模・消費電力が 小さいタイムデジタイザ回路の様々なアプリケーションのために、我々はそのアーキテクチャ・回路の研究を 行っており、結果は順次報告していきたい.