#### Fast Testing of Linearity and Comparator Error Tolerance of SAR ADCs

#### T. Ogawa, H. Kobayashi, S. Uemori, Y. Tan, S. Ito, N. Takai, T.J.Yamaguchi

Gunma University

- Research purpose

- SAR ADC

- Fast testing of SAR ADC DC linearity

- Testing of comparator-error tolerance in non-binary SAR ADC

- Conclusion

- Research purpose

- SAR ADC

- Fast testing of SAR ADC DC linearity

- Testing of comparator-error tolerance

in non-binary SAR ADC

- Conclusion

## Research purpose

- Successive Approximation Register (SAR) ADCs

- Widely used

- low sampling rate, high resolution

- Testing time is long Costly

- BIST for fast DC linearity testing

- BIST for SAR ADC redundancy check in cooperation with ATE

ATE : Automatic Test Equipment

BIST : Built-In-Self -Test

- Research purpose

- SAR ADC

- Fast testing of SAR ADC DC linearity

- Testing of comparator-error tolerance

in non-binary SAR ADC

- Conclusion

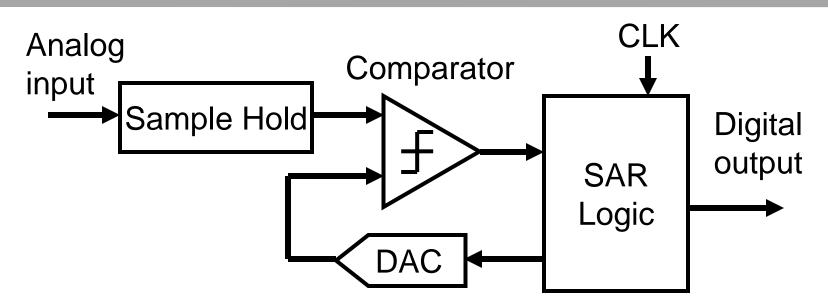

## SAR ADC Block

SAR ADC is digital centric.

- $\rightarrow$  Suitable for fine CMOS implementation.

- •Small chip area

- Low power

- •Not use OP-amp

#### SAR ADC Principle Operation - Binary search case -

- Research purpose

- SAR ADC

- Fast testing of SAR ADC DC linearity

- Testing of comparator-error tolerance

in non-binary SAR ADC

- Conclusion

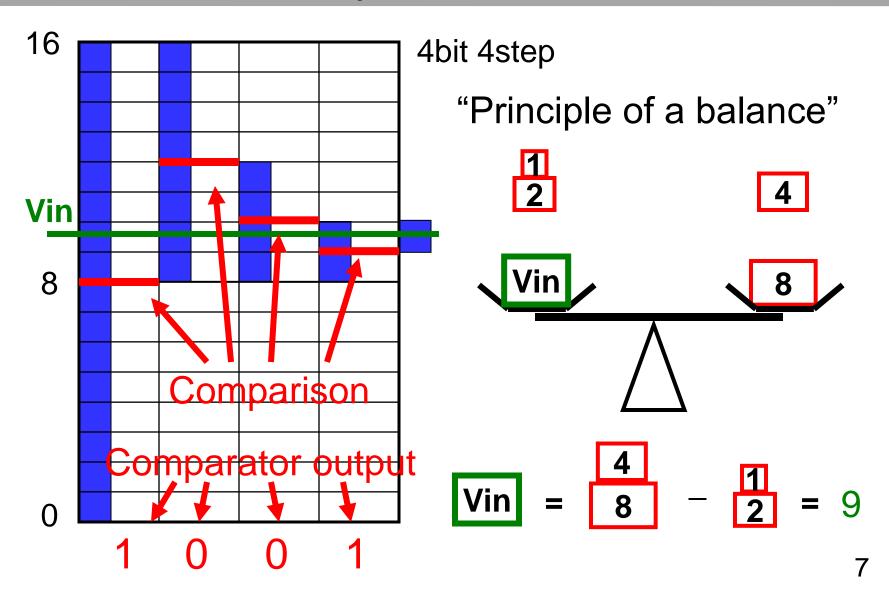

# Testing time of SAR ADC

- High resolution (10bit)

- Low sampling speed (1MS/s)

- DC linearity testing time 10 bit  $\rightarrow$  1024 LSBs

- 10 points / 1LSB

10240 points x 1us = 10 msec

x3 Temperature change

x3 Vdd change

1\$ chip  $\rightarrow$  1sec testing time is reasonable.

Mass volume  $\rightarrow$  Even 1msec testing time reduction is significant cost reduction.

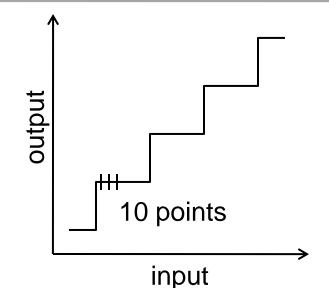

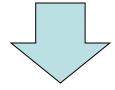

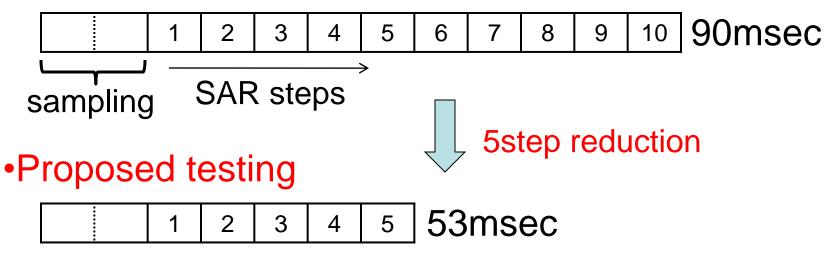

### Fast testing of SAR ADC DC linearity

- DC linearity is the important testing item.

- Testing time reduction

- ➡ cost reduction

• The number of SAR conversion steps reduction during DC linearity testing.

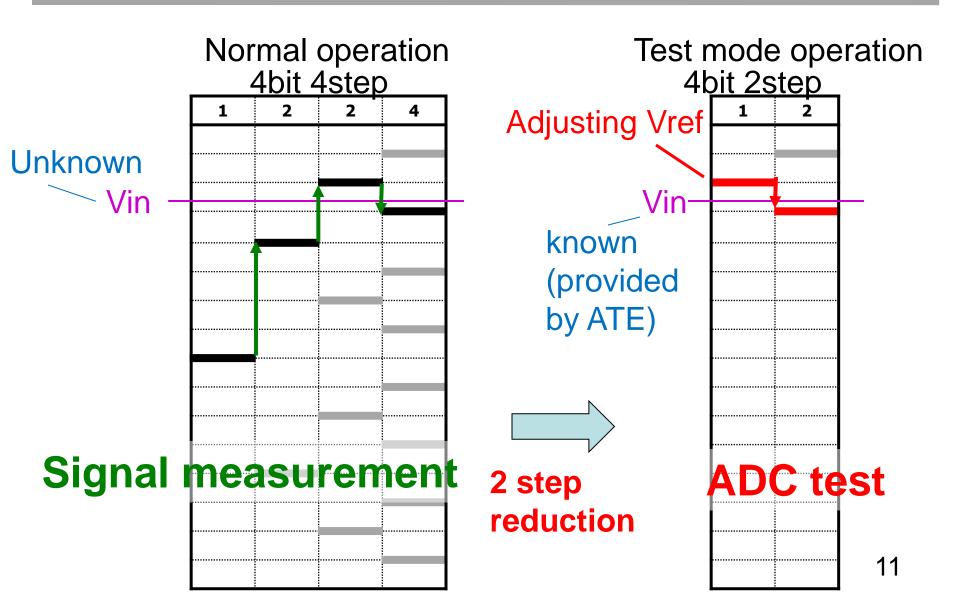

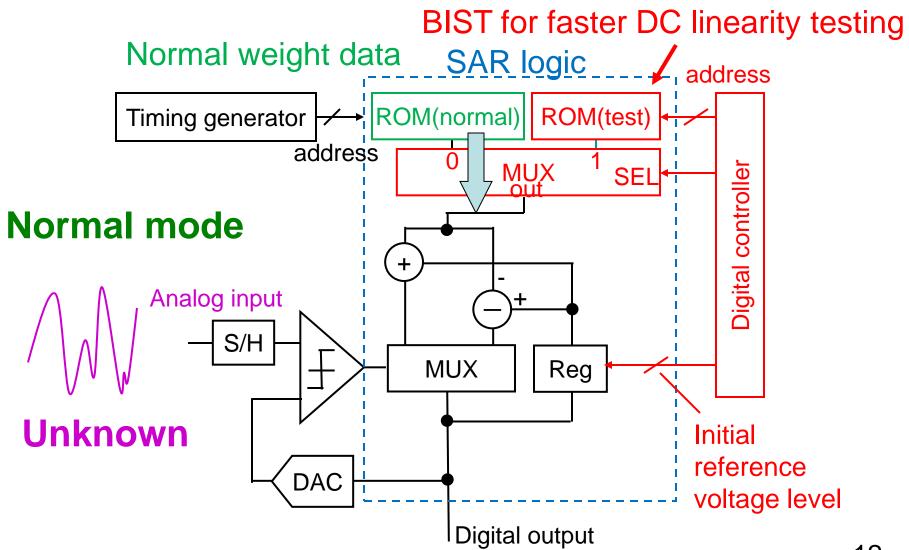

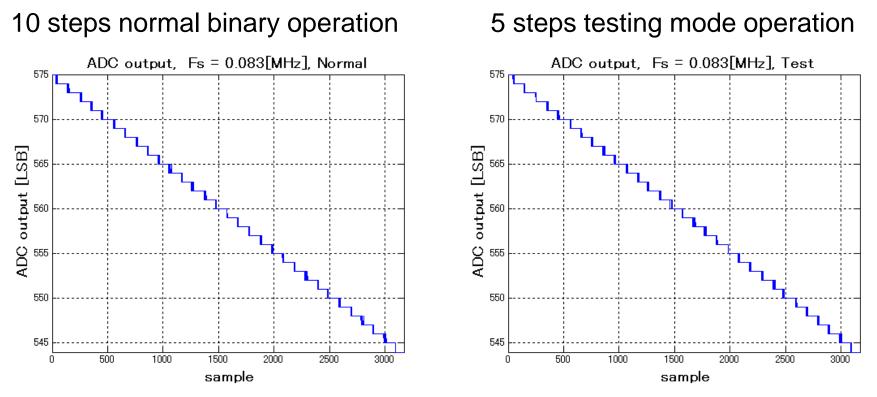

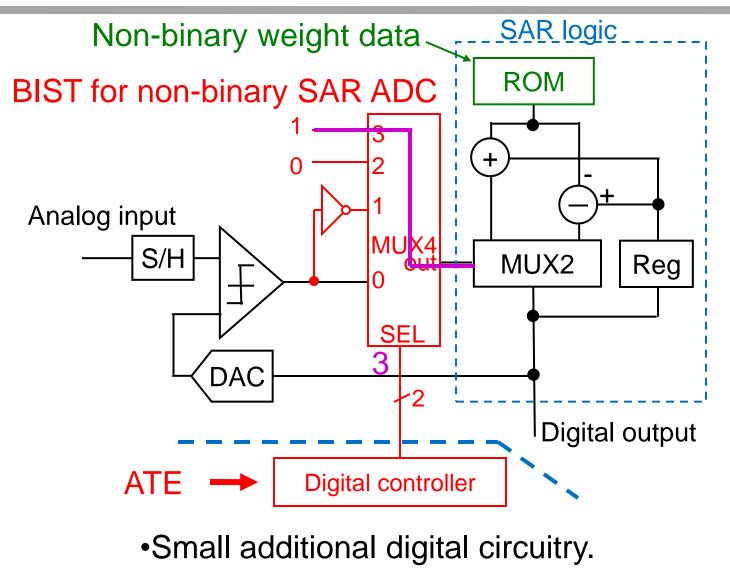

### Operation of SAR ADC with BIST

### SAR ADC Implementation with BIST

### SAR ADC Implementation with BIST

#### Measurement results of 10bit SAR ADC chip

Results are equivalent. The basic concept is validated.

# Testing time reduction

- •Time of setup, settling : 10 msec

- •Normal

•Data transfer and processing : 10 msec

Conventional: 110 msec

Proposed : 73 msec

33% reduction

- Research purpose

- SAR ADC

- Fast testing of SAR ADC DC linearity

- Testing of comparator-error tolerance in non-binary SAR ADC

- Conclusion

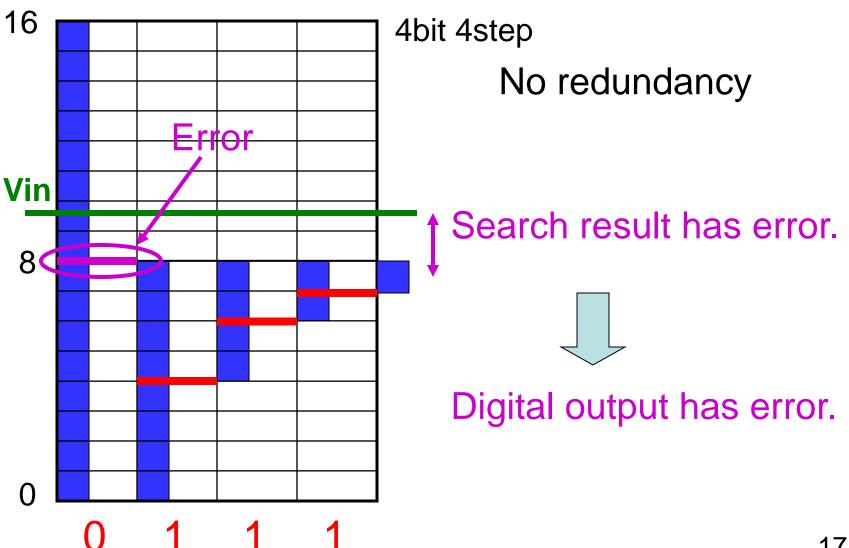

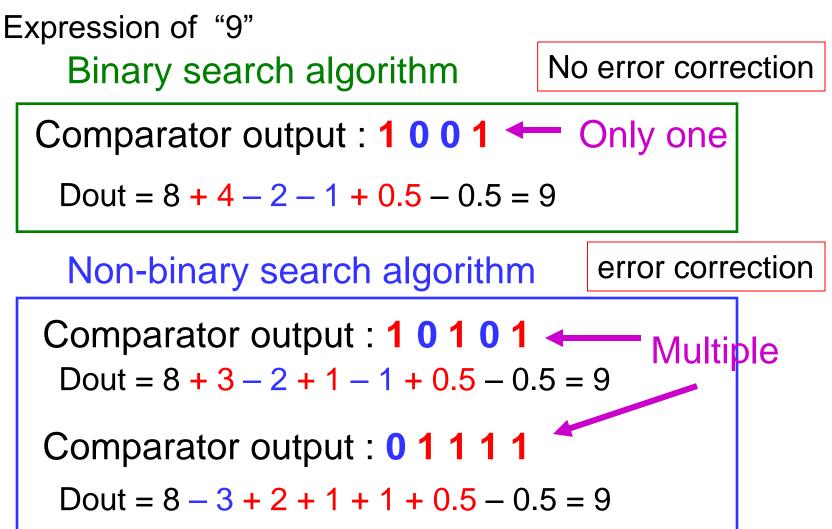

### Problem of binary search algorithm

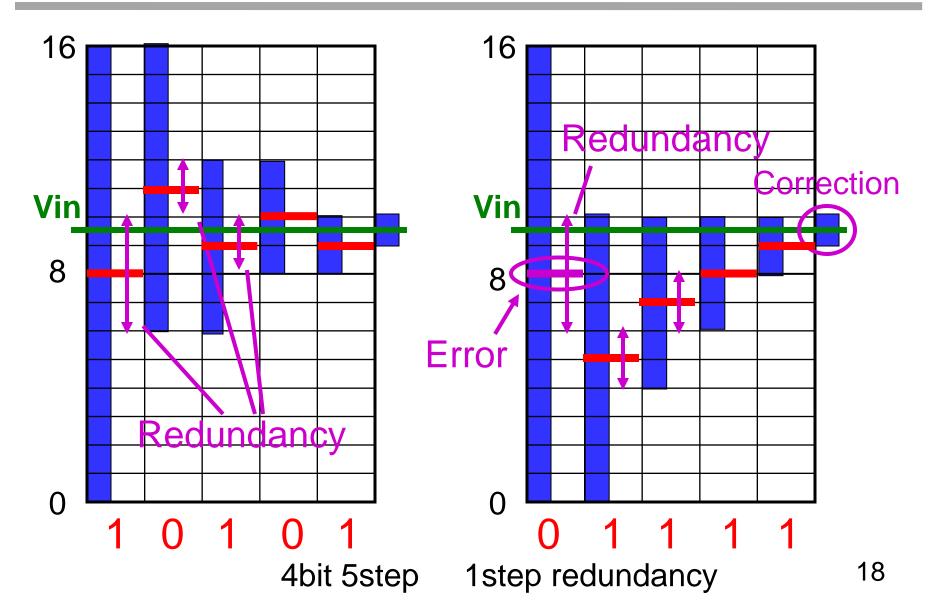

## Non-binary search algorithm

### Principle of error correction

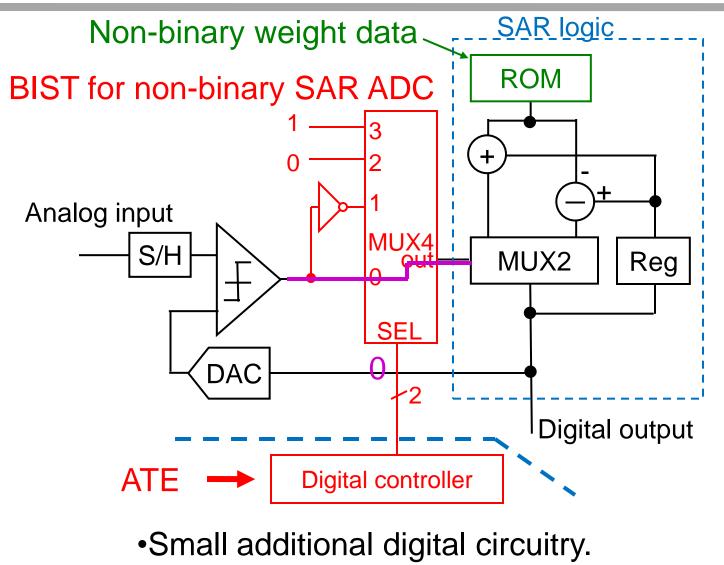

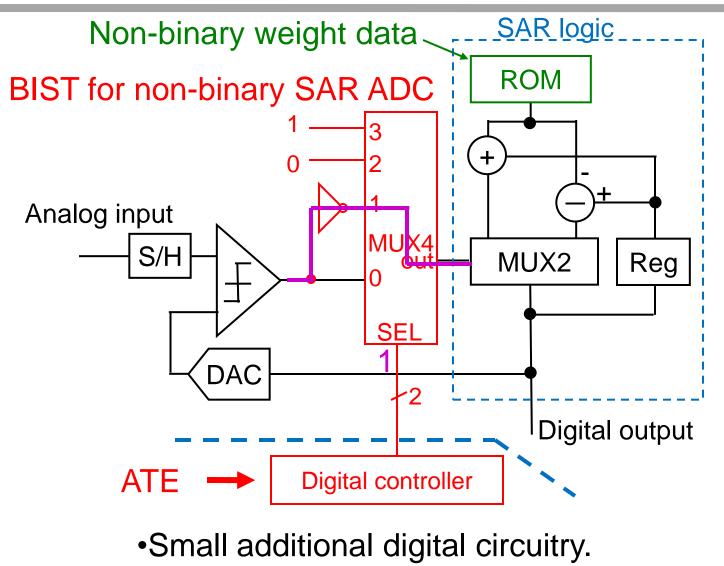

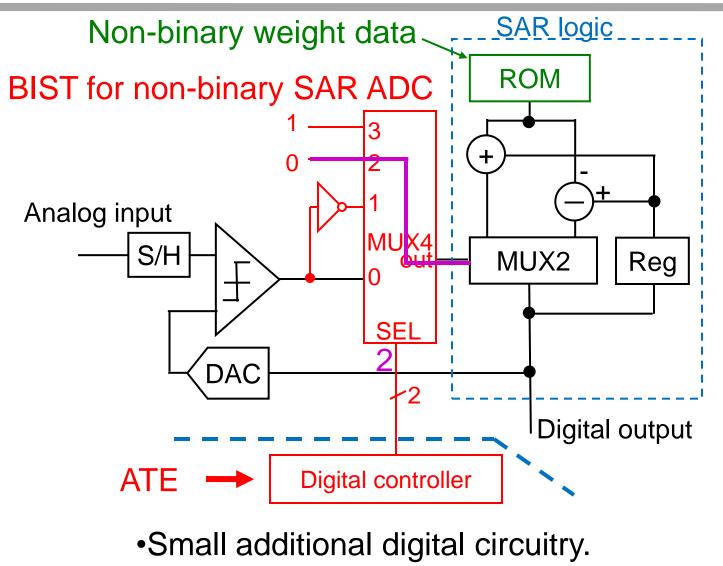

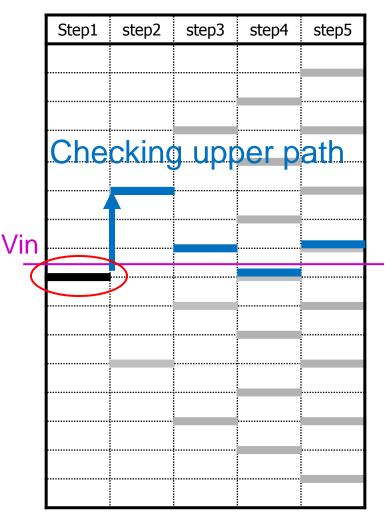

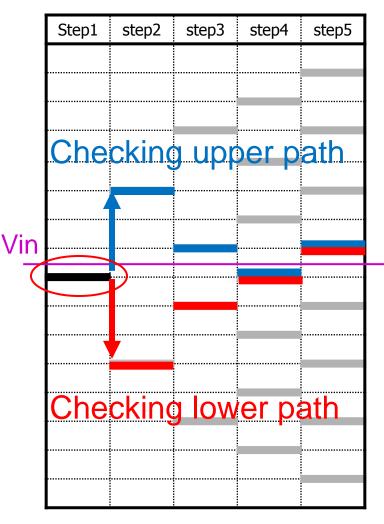

#### Comparator-error tolerance testing in non-binary SAR ADC

In a non-binary SAR ADC, this comparatorerror tolerance testing is difficult.

- Proposed simple BIST can check comparator-error tolerance.

- Output patterns are multiple. Expression of "9"

Error

01111: Comparator error path

10101: Correct path

#### Not controllable.

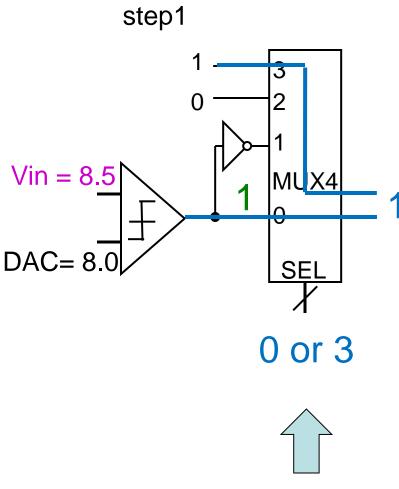

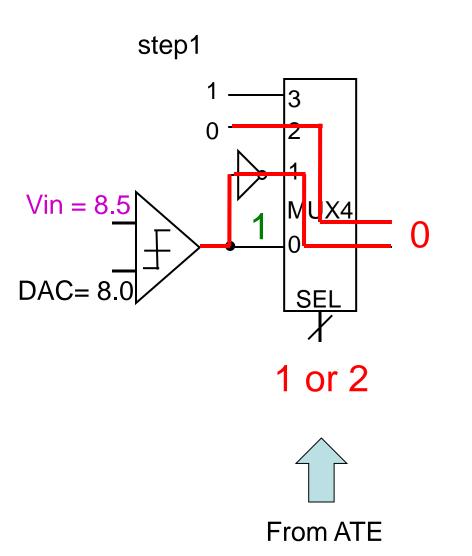

#### Operation of BIST to test error-tolerance in non-binary SAR ADC

From ATE

#### Operation of BIST to test error-tolerance in non-binary SAR ADC

- Research purpose

- SAR ADC

- Fast testing of SAR ADC DC linearity

- Testing of comparator-error tolerance

in non-binary SAR ADC

- Conclusion

## Conclusion

We have proposed BIST for testing SAR ADCs.

- SAR ADC DC linearity testing time reduction.

Measurement results validate the basic concept.

- Comparator-error tolerance check BIST in non-binary SAR ADCs.

- Small additional circuitry in cooperation with ATE.