# 冗長アルゴリズムSAR ADC の テスト容易化技術

小川智彦 小林春夫 〇伊藤聡志, 上森聡史 丹陽平 高井伸和 山口隆弘

群馬大学 電気電子工学専攻

## 発表内容

- 研究背景

- SAR ADC

- ・ 非2進アルゴリズム

- 提案テスト方法

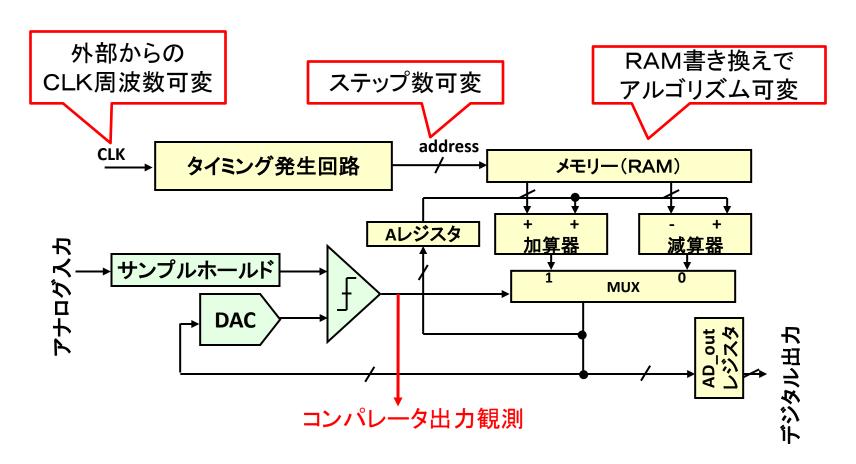

- 再構成可能な非2進SAR ADC

- まとめ

## 発表内容

- 研究背景

- SAR ADC

- 非2進アルゴリズム

- ・提案テスト方法

- 再構成可能な非2進SAR ADC

- ・まとめ

## 研究背景

- アナログ・デジタル混載SOCのコスト削減

- → アナログ部のテスト容易化が重要

### アナログテスト容易化技術

- アナログ回路ごと、性能仕様項目ごとに 個別対応しなければならない。

- 冗長性をもつ and/or 自己校正を行う アナログ回路はテストがより複雑になる。

## 研究目的

●非2進冗長アルゴリズムSAR ADCのテスト技術を検討

内部のDAC出力の整定時間の推定手法の提案

→ 回路スピード余裕の値を知る

- 低速ATEからの遅いクロックでSAR ADCが 実クロックスピードでの動作可能かどうかを推定可

- 電源電圧、温度変動に対するテスト工数削減 (低電源電圧、高温度ではスピード低下するが、 そのテストが省略でき得る)

- 再構成可能な SAR ADC で歩留まり向上・低消費電力化

- ※ ATE: Automatic Test Equipment LSI試験装置

## 発表内容

- 研究背景

- SAR ADC

- 非2進アルゴリズム

- ・提案テスト方法

- 再構成可能な非2進SAR ADC

- ・まとめ

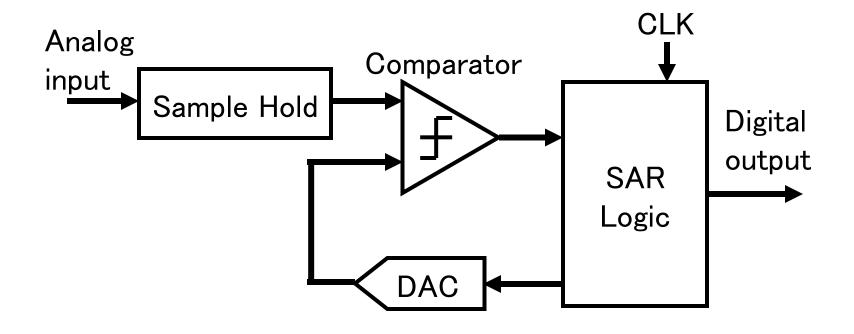

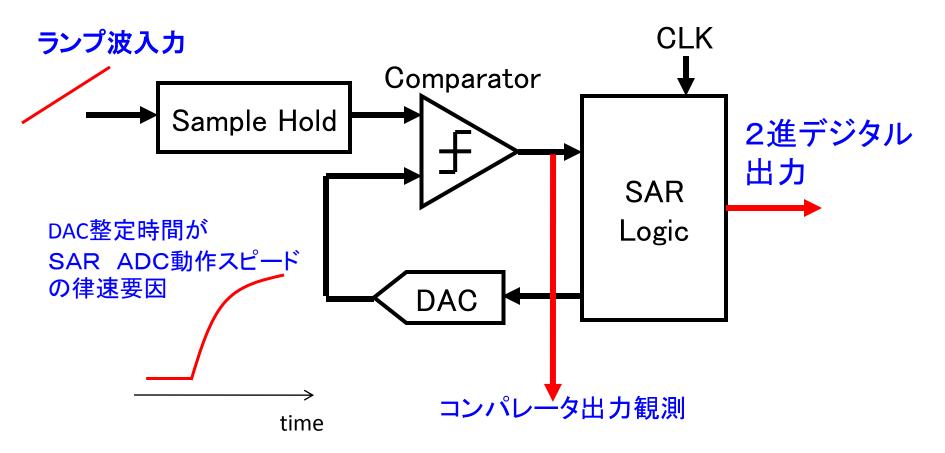

### SAR ADCの構成

デジタル回路中心, オペアンプ不要.

→ 微細CMOSでの実現に適している.

※SAR: Successive Approximation Register 逐次比較近似

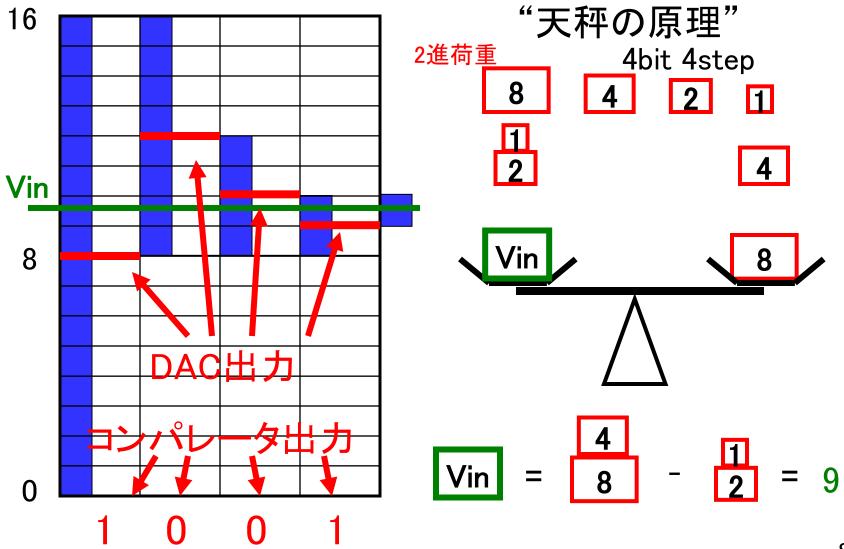

### SAR ADCの動作 2進探索アルゴリズム

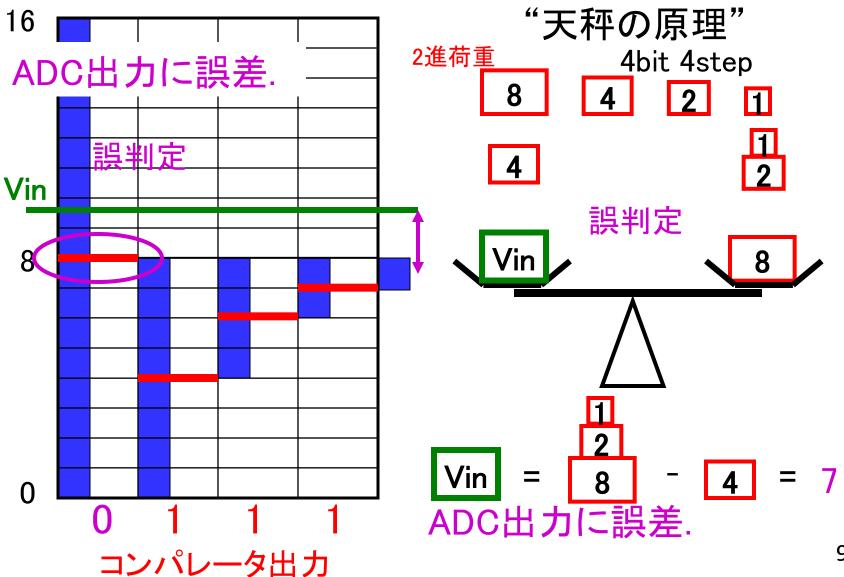

### 2進探索アルゴリズムの問題点

## 発表内容

- 研究背景

- SAR ADC

- ・ 非2進アルゴリズム

- ・提案テスト方法

- 再構成可能な非2進SAR ADC

- ・まとめ

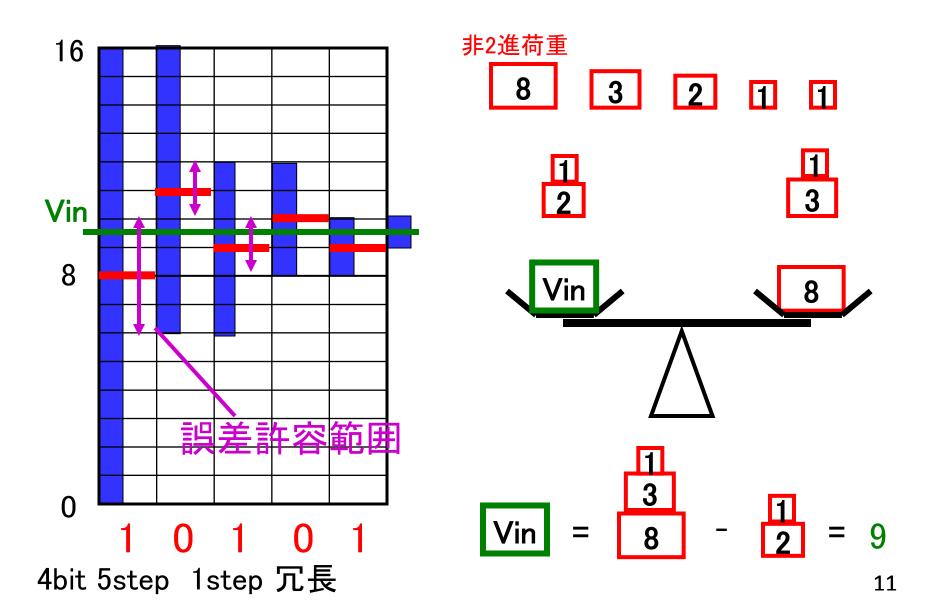

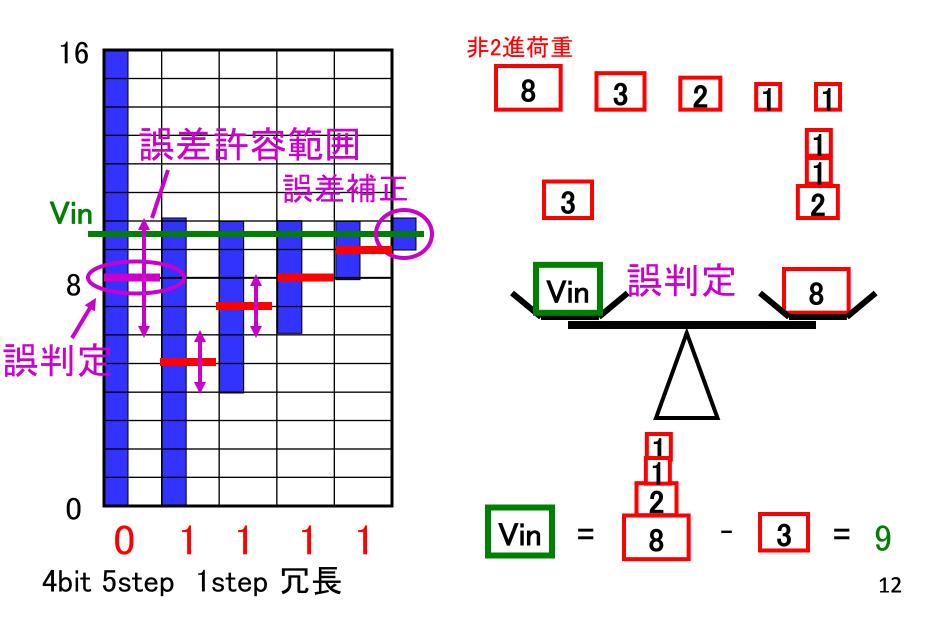

### 非2進探索アルゴリズム 判定が正しい場合

## 非2進探索アルゴリズム 1ステップ目で誤判定した場合

# 非2進アルゴリズムでのデジタル誤差補正原理

デジタル出力"9"の場合 2進探索アルゴリズム

誤差補正不可

コンパレータ出力: 1001

Dout =

$$8 + 4 - 2 - 1 + 0.5 - 0.5 = 9$$

#### 非2進探索アルゴリズム

誤差補正可能

<del>----</del> 複数パターン

Dout = 8 + 3 - 2 + 1 - 1 + 0.5 - 0.5 = 9

コンパレータ出力: 01111

Dout = 8 - 3 + 2 + 1 + 1 + 0.5 - 0.5 = 9

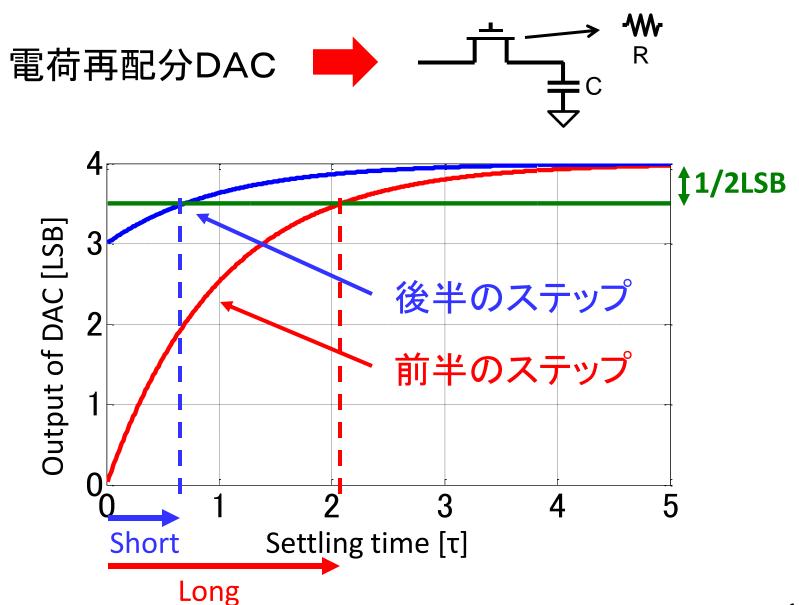

## DAC出力の整定

### 非2進アルゴリズムによる SAR ADC高速化の原理

4bit 2進アルゴリズム Step1 Step2 Step3 Step4 完全に整定 → 時間:長 AD変換時間 非2進アルゴリズム Step2 Step3 Step4 Step5 Step1

不完全整定誤差を補正

不完全整定→時間:短

## 発表内容

- 研究背景

- SAR ADC

- 非2進アルゴリズム

- 提案テスト方法

- 再構成可能な非2進SAR ADC

- ・まとめ

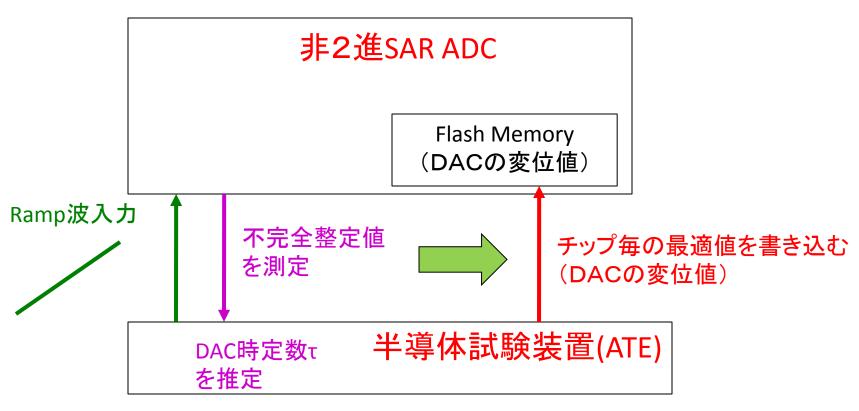

## 提案テスト方法

- ・ランプ波入力

- ・コンパレータ出力観測、ADC出力観測

• 非2進SAR ADCの各ステップでの DACの整定値を推定

・ADCチップのスピードの余裕を計算

- ・ADCスピードと電源電圧、温度変動に相関あり

- •十分余裕があれば変動による劣化を吸収可能

・低速ATEでSAR ADC が実クロック速度動作 可能かの推定可

### 非2進冗長SAR ADC テストの構成

- テスト用に、SAR ADCチップはコンパレータ出力ピンを設ける

- ATEはSAR ADCに対して

- ランプ波入力

- 各ステップ毎にコンパレータ出力を読む

- 最後に2進デジタル出力を読む

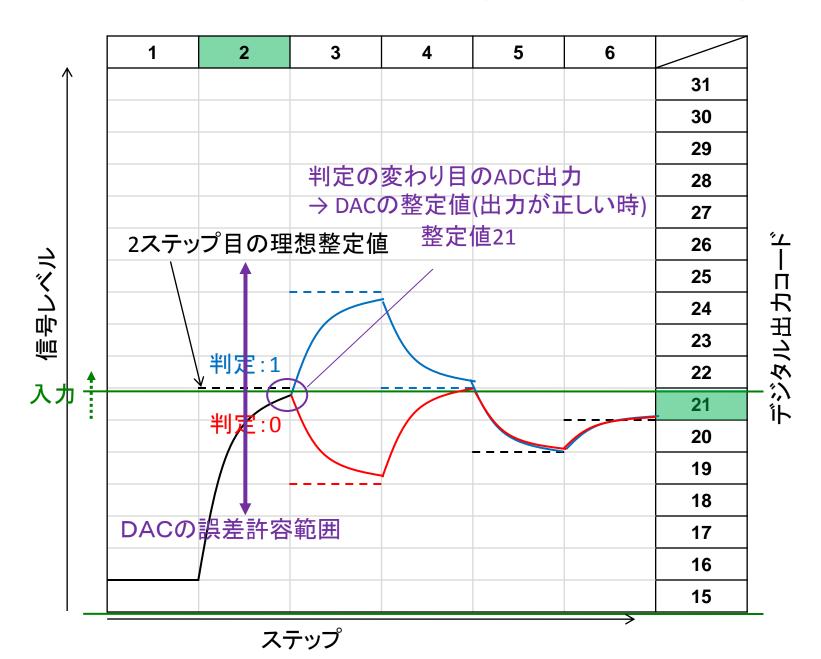

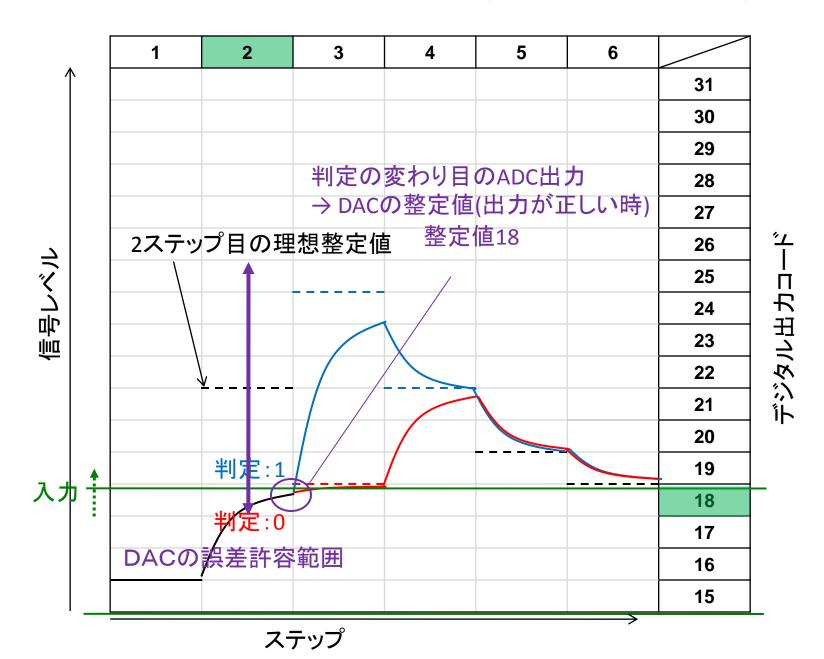

### DAC整定値の推定方法(5ビット6ステップ)

### DAC整定値の推定方法(5ビット6ステップ)

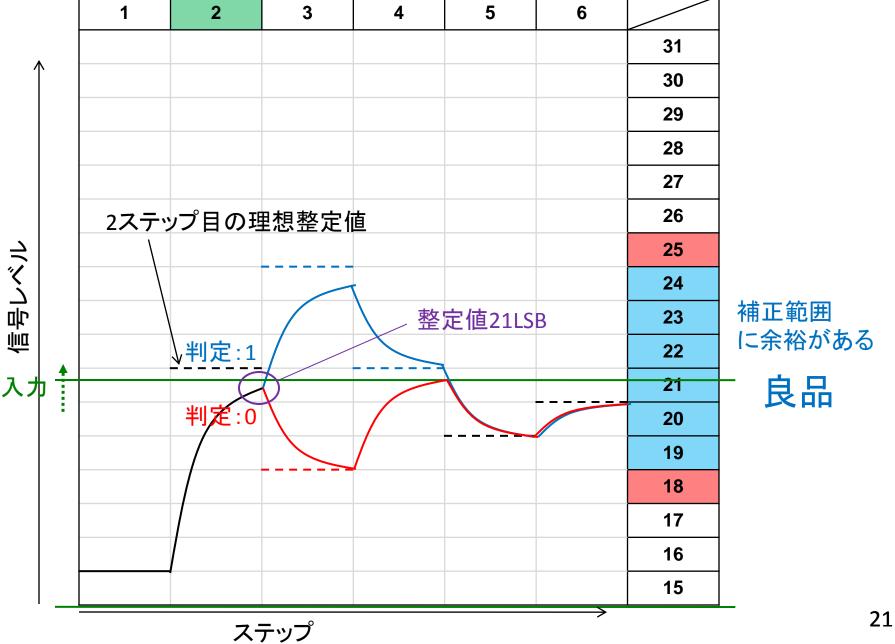

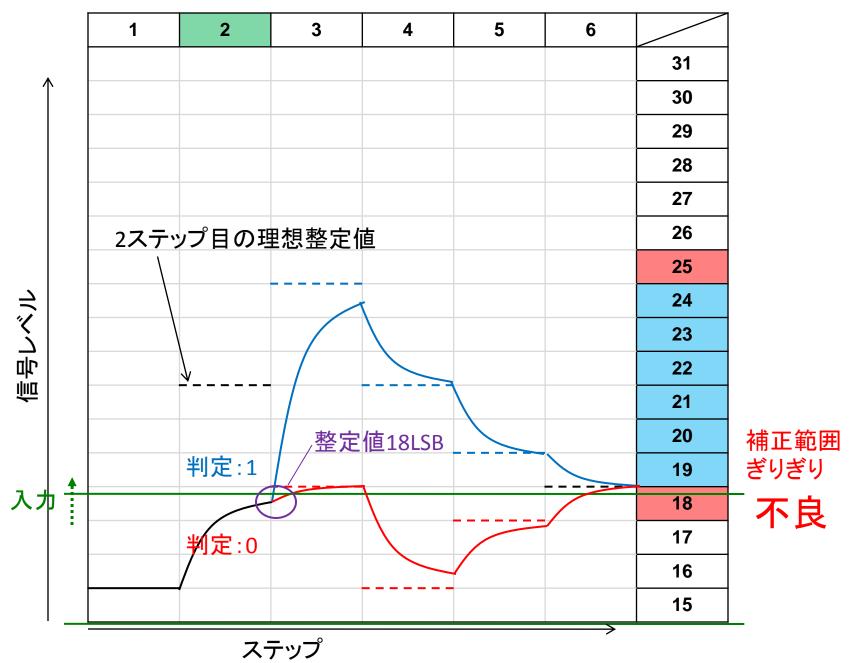

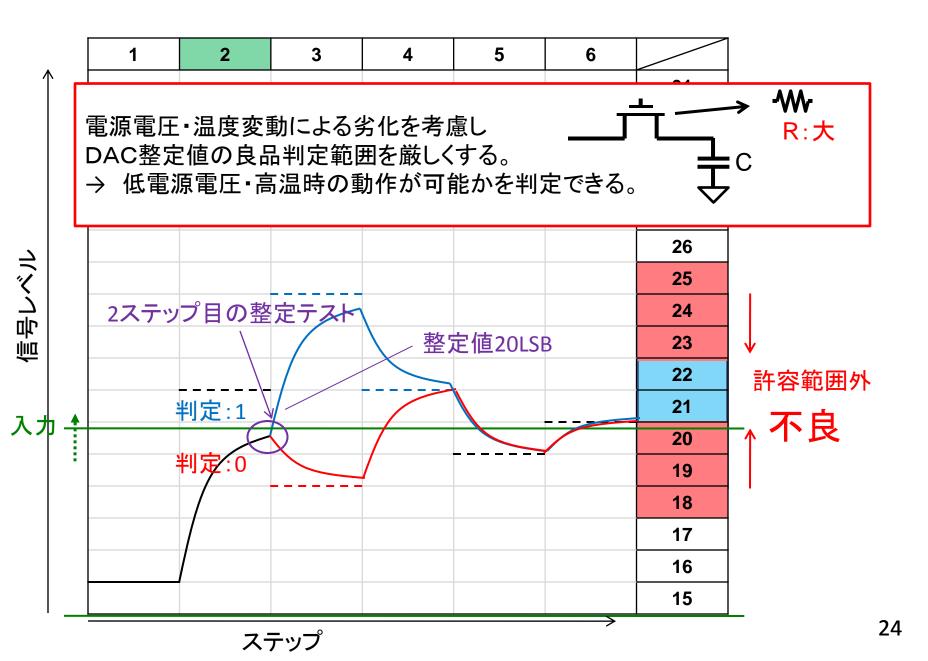

#### 2ステップ目の整定テスト(5ビット6ステップ)

### 2ステップ目の整定テスト(5ビット6ステップ)

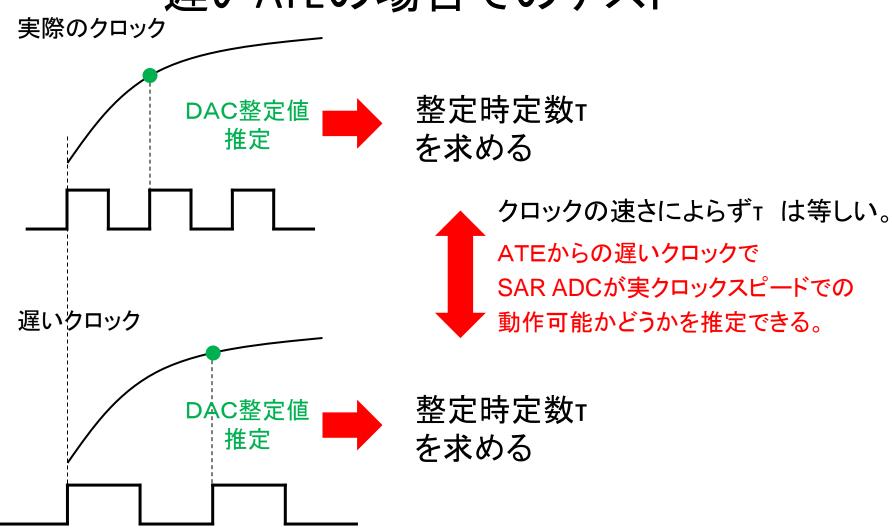

# 実際のクロック周波数よりも遅いATEの場合でのテスト

### 電源電圧・温度変動に対するテスト

# シミュレーションによる確認 非2進アルゴリズム 10ビット12ステップの例

| step | p(DACの重み) | q(誤差許容範囲) |

|------|-----------|-----------|

| 1    | 512       | 20        |

| 2    | 246       | 40        |

| 3    | 113       | 23        |

| 4    | 65        | 14        |

| 5    | 37        | 9         |

| 6    | 21        | 4         |

| 7    | 13        | 3         |

| 8    | 7         | 2         |

| 9    | 4         | 2         |

| 10   | 2         | 0         |

| 11   | 2         | 0         |

| 12   | 1         | 0         |

### 2ステップ目の整定値(1ステップ目の判定1)

### 時定数typicalの時

2ステップ目でDACは 充分時間あれば 512+246=758 に収束する

ステップ

$512 + 246(1 - e^{\tau_{TP}}) = 733.3 LSB$  **一** DAC整定値 コンパレータの判定(MATLABシミュレーション)

|   | $\longrightarrow$ |   |   |   |   | ,,,,,, |     |   |        | <b></b> / |    |     |

|---|-------------------|---|---|---|---|--------|-----|---|--------|-----------|----|-----|

| 1 | 2                 | 3 | 4 | 5 | 6 | 7      | 8   | 9 | 10     | 11        | 12 | 出力  |

| 1 | 1                 | 0 | 0 | 0 | 0 | 0      | 1   | 1 | 1      | 0         | 0  | 734 |

| 1 | 1                 | 0 | 0 | 0 | 0 | _      | コンバ |   | タ出ナ    | <u> </u>  | 0  | 734 |

| 1 | 1                 | 0 | 0 | 0 | 0 | Ļ_     |     |   | У ЦІ / |           | 0  | 734 |

| 1 | 1                 | 0 | 0 | 0 | 0 | 0      | 1   | 1 | 1      | 0         | 0  | 734 |

| 1 | 1                 | 0 | 0 | 0 | 0 | 0      | 1   | 1 | 1      | 0         | 0  | 734 |

| 1 | 1                 | 0 | 0 | 0 | 0 | 0      | 1   | 1 | 0      | 1         | 1  | 733 |

| 1 | 1                 | 0 | 0 | 0 | 0 | 0      | 1   | 1 | 0      | 1         | 1  | 733 |

| 1 | 0                 | 1 | 1 | 0 | 1 | 0      | 1   | 0 | 0      | 1         | 1  | 733 |

| 1 | 0                 | 1 | 1 | 0 | 1 | 0      | 1   | 0 | 0      | 1         | 1  | 733 |

| 1 | 0                 | 1 | 1 | 0 | 1 | 0      | 1   | 0 | 0      | 1         | 0  | 732 |

| 1 | 0                 | 1 | 1 | 0 | 1 | 0      | 0   | 1 | 1      | 1         | 0  | 732 |

| 1 | 0                 | 1 | 1 | 0 | 1 | 0      | 0   | 1 | 1      | 1         | 0  | 732 |

| 1 | 0                 | 1 | 1 | 0 | 1 | 0      | 0   | 1 | 1      | 1         | 0  | 732 |

| 1 | 0                 | 1 | 1 | 0 | 1 | 0      | 0   | 1 | 1      | 0         | 1  | 731 |

| 1 | 0                 | 1 | 1 | 0 | 1 | 0      | 0   | 1 | 1      | 0         | 1  | 731 |

### 2ステップ目の整定値(1ステップ目の判定1)

2ステップ目でDACは 512+246-40 =718 以上の値に 収束すれば 正解を得る

### 時定数typicalの80% (fast)の時

$$\begin{array}{ll} -\frac{t}{\tau} & t = 2.3\tau_{TP} \\ 512 + 246(1 - e^{-\tau}) & \tau_{TP} : typical \circ )$$

時定数

$512 + 246(1 - e^{-0.8*\tau_{TP}}) = 744.1 LSB$  DAC整定値 コンパレータの判定(MATLABシミュレーション)

|   | <del></del> |   |   |   |   |   |     |     |          |          |    |     |

|---|-------------|---|---|---|---|---|-----|-----|----------|----------|----|-----|

| 1 | 2           | 3 | 4 | 5 | 6 | 7 | 8   | 9   | 10       | 11       | 12 | 出力  |

| 1 | 1           | 0 | 0 | 0 | 0 | 1 | 1   | 0   | 1        | 0        | 1  | 745 |

| 1 | 1           | 0 | 0 | 0 | 0 | _ | コンバ | سرا | タ出ナ      | <b>1</b> | 1  | 745 |

| 1 | 1           | 0 | 0 | 0 | 0 | 4 |     | U   | <u> </u> |          | 1  | 745 |

| 1 | 1           | 0 | 0 | 0 | 0 | 1 | 1   | 0   | 1        | 0        | 0  | 744 |

| 1 | 1           | 0 | 0 | 0 | 0 | 1 | 1   | 0   | 1        | 0        | 0  | 744 |

| 1 | 1           | 0 | 0 | 0 | 0 | 1 | 1   | 0   | 1        | 0        | 0  | 744 |

| 1 | 1           | 0 | 0 | 0 | 0 | 1 | 1   | 0   | 1        | 0        | 0  | 744 |

| 1 | 0           | 1 | 1 | 0 | 1 | 1 | 0   | 1   | 1        | 0        | 0  | 744 |

| 1 | 0           | 1 | 1 | 0 | 1 | 1 | 0   | 1   | 0        | 1        | 1  | 743 |

| 1 | 0           | 1 | 1 | 0 | 1 | 1 | 0   | 1   | 0        | 1        | 1  | 743 |

| 1 | 0           | 1 | 1 | 0 | 1 | 1 | 0   | 1   | 0        | 1        | 1  | 743 |

| 1 | 0           | 1 | 1 | 0 | 1 | 1 | 0   | 1   | 0        | 1        | 1  | 743 |

| 1 | 0           | 1 | 1 | 0 | 1 | 1 | 0   | 1   | 0        | 1        | 0  | 742 |

| 1 | 0           | 1 | 1 | 0 | 1 | 1 | 0   | 1   | 0        | 1        | 0  | 742 |

| 1 | 0           | 1 | 1 | 0 | 1 | 1 | 0   | 1   | 0        | 1        | 0  | 742 |

### 2ステップ目の整定値(1ステップ目の判定1)

2ステップ目でDACは 512 + 246 - 40=718 以上の値に 収束すれば 正解を得る

### 時定数typicalの110%(slow)の時

$$512+246(1-e^{-\frac{t}{\tau}})$$

$t=2.3\tau_{TP}$   $\tau_{TP}:typical$  の時定数

|   | $\longrightarrow$ |   |   |   |   |          |     |     |          |                |    |     |

|---|-------------------|---|---|---|---|----------|-----|-----|----------|----------------|----|-----|

| 1 | 2                 | 3 | 4 | 5 | 6 | 7        | 8   | 9   | 10       | 11             | 12 | 出力  |

| 1 | 1                 | 0 | 0 | 0 | 0 | 0        | 1   | 0   | 0        | 1              | 1  | 729 |

| 1 | 1                 | 0 | 0 | 0 | 0 | _        | コンバ | سرا | タ出ナ      | <del>ا</del> ا | 1  | 729 |

| 1 | 1                 | 0 | 0 | 0 | 0 | <u> </u> |     |     | <u>'</u> |                | 0  | 728 |

| 1 | 1                 | 0 | 0 | 0 | 0 | 0        | 0   | 1   | 1        | 1              | 0  | 728 |

| 1 | 1                 | 0 | 0 | 0 | 0 | 0        | 0   | 1   | 1        | 1              | 0  | 728 |

| 1 | 1                 | 0 | 0 | 0 | 0 | 0        | 0   | 1   | 1        | 1              | 0  | 728 |

| 1 | 1                 | 0 | 0 | 0 | 0 | 0        | 0   | 1   | 1        | 1              | 0  | 728 |

| 1 | 0                 | 1 | 1 | 0 | 0 | 1        | 1   | 1   | 1        | 0              | 1  | 727 |

| 1 | 0                 | 1 | 1 | 0 | 0 | 1        | 1   | 1   | 1        | 0              | 1  | 727 |

| 1 | 0                 | 1 | 1 | 0 | 0 | 1        | 1   | 1   | 1        | 0              | 0  | 726 |

| 1 | 0                 | 1 | 1 | 0 | 0 | 1        | 1   | 1   | 1        | 0              | 0  | 726 |

| 1 | 0                 | 1 | 1 | 0 | 0 | 1        | 1   | 1   | 1        | 0              | 0  | 726 |

| 1 | 0                 | 1 | 1 | 0 | 0 | 1        | 1   | 1   | 1        | 0              | 0  | 726 |

| 1 | 0                 | 1 | 1 | 0 | 0 | 1        | 1   | 1   | 1        | 0              | 0  | 726 |

| 1 | 0                 | 1 | 1 | 0 | 0 | 1        | 1   | 1   | 1        | 0              | 0  | 726 |

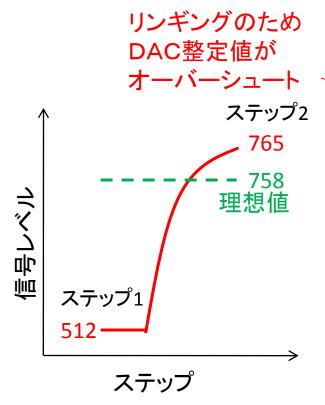

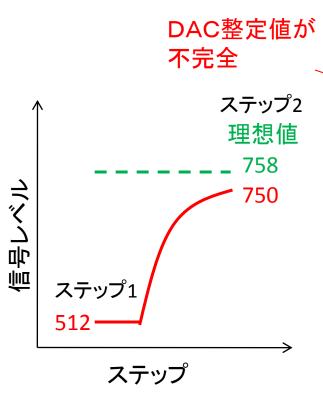

## 試作チップでの検証

- DAC整定値の推定を試作チップでの検証

- •DAC整定がリンギングしているもの(Chip A)

- •DAC整定がリンギングしていないもの(Chip B)

- → 整定値の違いを確認

- ※Chip A: バイパス容量なし

- % 外部から参照電圧を与えているので ボンデング・インダクタと寄生容量で 参照電圧がリンギングしていると推定した。

# リンギングしているもの(Chip A)

非2進10ビット12ステップ(1~4ステップ)

| step1  | step2  | step3  | step4  | 判定  |

|--------|--------|--------|--------|-----|

|        |        |        | 理想:936 | 111 |

|        |        | 理想:871 | 推定:939 |     |

|        |        | 推定:876 | 理想:806 | 110 |

|        | 理想:758 |        | 推定:809 |     |

|        | 推定:765 | /      | 理想:710 | 101 |

|        |        | 理想:645 | 推定:712 |     |

|        |        | 推定:647 | 理想:580 | 100 |

| 理想:512 |        |        | 推定:580 |     |

| 推定:512 |        |        | 理想:444 | 011 |

|        |        | 理想:379 | 推定:443 |     |

|        |        | 推定:377 | 理想:314 | 010 |

|        | 理想:266 |        | 推定:311 |     |

|        | 推定:258 |        | 理想:218 | 001 |

|        |        | 理想:153 | 推定:214 |     |

|        |        | 推定:146 | 理想: 88 | 000 |

|        |        |        | 推定: 84 |     |

# リンギングしていないもの(Chip B)

非2進10ビット12ステップ(1~4ステップ)

| step1  | step2  | step3  | step4  | 判定  |

|--------|--------|--------|--------|-----|

|        |        |        | 理想:936 | 111 |

|        |        | 理想:871 | 推定:931 |     |

|        |        | 推定:864 | 理想:806 | 110 |

|        | 理想:758 |        | 推定:802 |     |

|        | 推定:750 | )      | 理想:710 | 101 |

|        |        | 理想:645 | 推定:707 |     |

|        |        | 推定:642 | 理想:580 | 100 |

| 理想:512 |        |        | 推定:579 |     |

| 推定:511 |        |        | 理想:444 | 011 |

|        |        | 理想:379 | 推定:444 |     |

|        |        | 推定:381 | 理想:314 | 010 |

|        | 理想:266 |        | 推定:315 |     |

|        | 推定:273 |        | 理想:218 | 001 |

|        |        | 理想:153 | 推定:221 |     |

|        |        | 推定:160 | 理想: 88 | 000 |

|        |        |        | 推定: 92 | 3   |

## 発表内容

- 研究背景

- SAR ADC

- 非2進アルゴリズム

- ・提案テスト方法

- 再構成可能な非2進SAR ADC

- ・まとめ

### 再構成可能な非2進SAR ADCの目的

(Reconfigurable SAR ADC)

例: 10MS/s,10bit非2進SAR ADC

DAC時定数τ:小

DAC時定数τ:大

$\downarrow$

10MS/s動作可能な

ステップ数:少

(例:11ステップ)

$\downarrow$

消費電力:低

10MS/s動作可能な

ステップ数:多

(例:14ステップ)

$\downarrow$

消費電力:高

スピード性能救済

冗長アルゴリズムSAR ADC

ステップ数: 多 → 高速

→ 消費電力大

## 再構成可能な非2進SAR ADC

(Reconfigurable SAR ADC)

時定数τが大きいチップ →

スピード仕様を満たせる

時定数τが小さいチップ

ステップ数小さくして 低消費電力化

## 再構成可能な非2進SAR ADCの 実現構成例

# 10MS/s 10bit SAR ADC 実現のための

早いチップ

アルゴリズムの適用例

遅いチップ

推定DAC時定数 τ=3.5ns

10ビット11ステップ

必要な整定時間:2.3τ

許容時定数τ=3.95ns

$\tau = 4.0 \text{ns}$

10ビット12ステップ

必要な整定時間: 1.9τ

許容時定数τ=4.38ns

$\tau = 4.5 \text{ns}$

10ビット13ステップ

必要な整定時間: 1.6で

許容時定数τ=4.80ns

| ステップ | DACの重み:p | 誤差許容:q |  |  |  |  |

|------|----------|--------|--|--|--|--|

| 1    | 512      | 0      |  |  |  |  |

| 2    | 256      | 26     |  |  |  |  |

| 3    | 115      | 15     |  |  |  |  |

| 4    | 63       | 8      |  |  |  |  |

| 5    | 35       | 5      |  |  |  |  |

| 6    | 19       | 2      |  |  |  |  |

| 7    | 11       | 1      |  |  |  |  |

| 8    | 6        | 1      |  |  |  |  |

| 9    | 3        | 0      |  |  |  |  |

| 10   | 2        | 0      |  |  |  |  |

| 11   | 1        | 0      |  |  |  |  |

|      |          |        |  |  |  |  |

| ステップ | DACの重み:p | 誤差許容∶q |

|------|----------|--------|

| 1    | 512      | 0      |

| 2    | 256      | 38     |

| 3    | 109      | 23     |

| 4    | 62       | 13     |

| 5    | 36       | 7      |

| 6    | 21       | 4      |

| 7    | 12       | 2      |

| 8    | 7        | 1      |

| 9    | 4        | 1      |

| 10   | 2        | 1      |

| 11   | 1        | 0      |

| 12   | 1        | 0      |

| ステップ | DACの重み:p | 誤差許容:q |

|------|----------|--------|

| 1    | 512      | 0      |

| 2    | 256      | 52     |

| 3    | 102      | 32     |

| 4    | 61       | 19     |

| 5    | 37       | 12     |

| 6    | 22       | 8      |

| 7    | 13       | 5      |

| 8    | 8        | 3      |

| 9    | 5        | 2      |

| 10   | 3        | 1      |

| 11   | 2        | 1      |

| 12   | 1        | 0      |

| 13   | 1        | 0      |

## 発表内容

- 研究背景

- SAR ADC

- 非2進アルゴリズム

- ・提案テスト方法

- 再構成可能な非2進SAR ADC

- まとめ

## まとめ

- 非2進SAR ADCの各ステップでのDAC整定値を コンパレータの判定とADC出力から 推定する方法を提案した。

- ➡スピード余裕の推定可能

- シミュレーション、試作チップで推定方法の 実証を行った。

- 再構成可能な非2進SAR ADC の提案した。

- ➡ チップ毎に歩留まり向上、低消費電力化可能

## 謝辞

有意義なご討論をいただきました、森俊彦氏、 宮下博之氏、矢野雄二氏、力野邦人氏、 岸上真也氏、我毛辰弘氏、荒井智氏、 小林修氏、松浦達治氏、新津葵一氏 およびこの研究をご支援いただいています STARCに感謝の意を表します。