# ADC ディジタル誤差補正技術の統一理論の一考察

# 小林 春夫(群馬大学)

Some Thoughts on Unified Theory of ADC Digital Error Correction Technique Haruo Kobayashi (Gunma University)

#### Abstract

This paper discusses the unified theory of digital error correction techniques in several ADC architectures, and shows that the redundancy in ADC operation and circuit can improve its overall performance combined with the digital error correction technique.

キーワード:AD 変換器, ディジタル誤差補正, ディジタル自己校正, 冗長性, ディジタルアシスト・アナログ技術, 統一理論 (ADC, Digital Error Correction, Redundancy, Self-Calibration, Digitally-Assisted Analog Technology, Unified Theory )

#### 1. はじめに

微細 CMOS ADC の高性能化のためにディジタル誤差補正、ディジタル自己校正技術等のディジタルアシスト・アナログ技術の研究が活発に行われている<sup>(1)</sup>. しかしながらその多くは個別技術を論じており、統一的な理論体系は未構築の状態である. この論文ではいくつかの ADC アーキテクチャに使用されている「冗長性を用いたディジタル誤差補正技術」を統一的に説明できる理論の構築を目標に考察を行う.

- 2. ADC でのディジタルアシストアナログ技術の分類

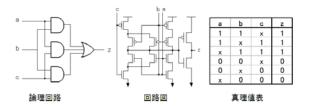

- **2・1** 冗長性を用いたディジタル誤差補正 図 1 の多数決回路を考える. 入力 (a,b,c) は a=b=c=1 または a=b=c=0 が正しい動作の場合とする. 多数決回路により入力 (a,b,c) のうち 2 つ以上が 1 であれば出力 z は 1 であり, 2 以上 0 であれば z は 0 である. すなわち, a,b,c でどれか一つが誤っていても正解の出力 z を得ることができる. これは冗長性を用いたディジタル誤差補正の典型例であり, a,b,c のでどれが誤っているかを知る必要がなく (計測せずに), 冗長性により正解の出力を得ることができる.

- 2・2 ディジタル自己校正 一方, 自己校正技術は回路の非理想特性を自分自身の回路で計測しそのデータをもとに測定データを補正する. 自己校正技術は電子計測器では古くから用いられているが, 近年その考え方が LSI 内の回路にも用いられるようになってきている.

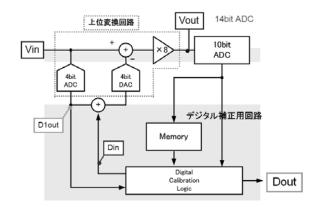

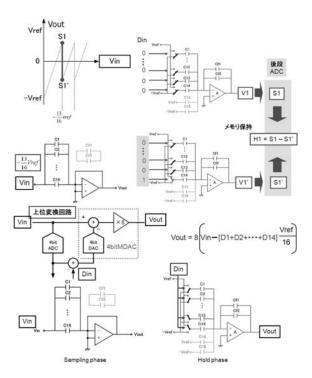

- A. フォアグランド自己校正: 自己校正のための時間を設け、この間は通常動作は停止している. パイプラインADC で後段の内部 sub-ADC で初段の DAC, 残差アンプの誤差を計測しメモリに記憶し、通常動作の際にそのデータで AD 変換データを補正する等が典型的な例である (図 2).

- B. バックグランド自己校正: 自己校正のための時間を設けず,通常動作時に自己校正も並行して行う. 統計的・論理的一貫性から特性誤差を推定する. 最初に一定の収束時間が必要である. その後は時間とともに温度、電源電圧変化にともなう回路の特性変動にも対応できる. 統計的な手法に加えて,異なる論理が一貫するように誤差推定を行う

3入力多数決回路

$z = a \cdot b + b \cdot c + c \cdot a$

図 1 多数決回路.

ことで収束時間を短くする技術 (Split ADC ) も提案されて いる  $^{(2)}$ .

フォアグランド自己校正, バックグランド自己校正のアルゴリズムは大きく異なる. バックグランド自己校正を用いる ADC の学会発表は多いが, 実際に商用化されている例はまだ少ない.

2・3 ダイナミックマッチング技術 回路・構成・動作の冗長性を利用し、素子・回路特性のばらつきを統計的に時間平均化する手法である (3)-(5). (ダイナミックマッチング技術とは異なるが、逆に素子ばらつきを積極的に回路特性向上に用いる手法も提案されている (6).)

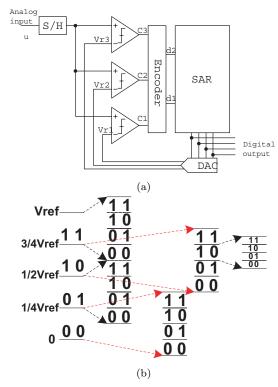

# 3. 逐次比較近似 ADC

この節では冗長性によるディジタル誤差補正技術を用いた 逐次比較近似 (Successive Approximation Register: SAR) ADC について考察する.

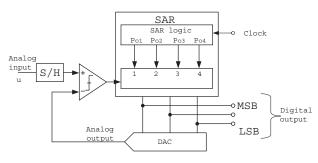

3・1 2 進アルゴリズム SAR ADC 逐次比較型 AD 変換器はトラック・ホールド回路,コンパレータ,DA 変換器,論理回路とタイミング発生回路から構成される(図3).内部回路がほとんどディジタル回路で実現できるので 微細 CMOS での ADC 実現に適した構成である.

通常の逐次比較型 ADC は "天秤の原理"で 2 進探索アルゴリズムに従って動作する . 2 進アルゴリズムは N ビット分解能を N 回の比較で実現する. すなわち k ステップ目で

図 2 フォアグランド自己校正 パイプライン ADC の構成.

図3 SAR ADC の構成.

比較したコンパレータ出力を  $b_k$  とすると  $(b_k=-1$  または  $1,\ k=1,2,...,N),\ {\rm ADC}$  ディジタル出力  $D_{out}$  は次のように表せる.

$$D_{out} = 2^{N-1} + \left(\sum_{k=1}^{N-1} b_k 2^{N-k-1}\right) + \frac{1}{2}(b_N - 1).$$

ここで  $0 \le D_{out} \le 2^N - 1$  である. ある  $D_{out}$  値に対して  $(b_1, b_2, ..., b_N)$  の組は一意にきまる.

2 進アルゴリズムは各ステップでの比較で誤判定が起きた場合に出力に誤差が生じてしまう. しかし 2 進アルゴリズム SAR ADC はむだ (冗長性) がなく非常に効率的な構成であるので, FOM (Figure of Merit) のよい ADC 構成として研究開発が行われている.

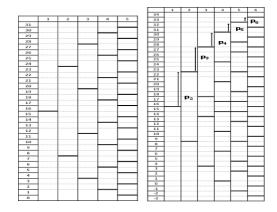

3・2 非 2 進アルゴリズム SAR ADC 冗長(非 2 進)アルゴリズムでは N ビット分解能を M 回 (N < M) の比較で実現する. 図 4 に N=5, M=6 の場合を示す. 分銅に対応する DAC 出力の重み付けは非 2 進荷重で初段は 16.0, 2 段目は初段のコンパレータ出力に応じて 23.0 (= $16.0+p_1$ ,  $p_1=7.0$ ) もしくは 9.0 (= $16.0-p_1$ ) とする. 比較回数を増やすことにより各出力コードに対応する比較パターンが複数となり,前半の判定で間違えた場合でも正解を出力できるようになる  $(7)^{-(9)}$  . 各ステップで許容できる誤差の範囲は比較ステップ数 M と分銅重み付けにより決まる.すなわち k ステップ目で比較したコンパレータ出力を  $s_k$  とすると  $(s_k=-1$  または 1, k=1, 2, ..., M) ADC ディジタル出力  $D_{out}$  は次のように表せる.

図 4 5 ビット 5 ステップ 2 進逐次比較近似アルゴリズム (左). 5 ビット 6 ステップ 冗長アルゴリズム (右).

$$D_{out} = 2^{N-1} + \sum_{k=1}^{M-1} s_k p_{k+1} + \frac{1}{2} (s_M - 1). \dots (1)$$

$p_{k+1} = \gamma^{M-k-1}$  の場合は基数  $\gamma$  進  $(\gamma = 2^{N/M}, 1 < \gamma < 2)$  である. これに制限されずにある程度の自由度をもって  $p_k$  を設計することも可能である.  $(s_1, s_2, ..., s_M)$  は  $2^M$  通りの組があり N < M なので  $2^N < 2^M$  である.  $0 \le D_{out} \le 2^N - 1$  の  $2^N$  通りの整数値のある一つの  $D_{out}$  値に対して  $(s_1, s_2, ..., s_M)$  の組  $(式\ (1)$  の解) は複数個あり得る. これは回路ではコンパレータ判定  $s_k$  が誤っても正解の  $D_{out}$  が得られる場合があることに対応しており、これが冗長アルゴリズム SAR ADC のディジタル誤差補正の原理である. またある  $D_{out}$  値に対して どの複数の  $(s_1, s_2, ..., s_M)$  の組を対応させるかが冗長アルゴリズムの設計である  $(7)^{-(9)}$ .

冗長性によりコンパレータ誤判定をディジタル補正できるということを利用して、SAR ADC の高速化・低消費電力化が実現できる. 非2進アルゴリズム SAR ADC は「動作に冗長性をもつ」(時間的冗長性)と言えよう.

3・3 3個コンパレータ使用 SAR ADC コンパレータ3個をもつ(冗長なコンパレータをもつ)2進アルゴリズム SAR ADC が提案されている(図5). コンパレータ判定誤りをディジタル補正することを用いて内部 DAC 不完全整定の影響を緩和して高速化を実現している(10)(11).

コンパレータ 3 個をもつ SAR ADC は「回路に冗長性を持つ」(空間的冗長性)と言えよう.

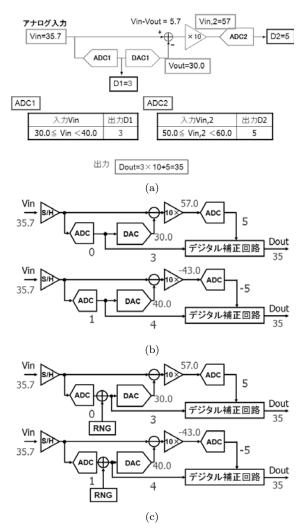

#### 4. パイプライン ADC

パイプライン ADC では一段あたり 2 個のコンパレータを用いる  $1.5 \mathrm{bit}$  /ステップ方式等の冗長によるディジタル 誤差補正技術が知られている. ここでは 2 段目の ADC の 冗長性により初段 ADC の判定誤りをディジタル誤差補正できる原理を示す (図 6(a), (b)). また (図 6(c)) はこの補正を利用したバックグランド自己校正方式である (a).

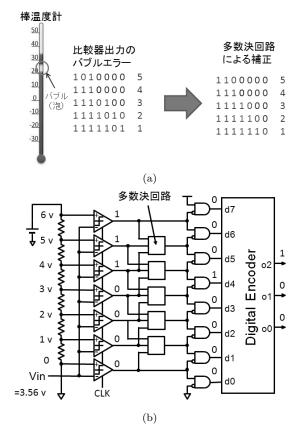

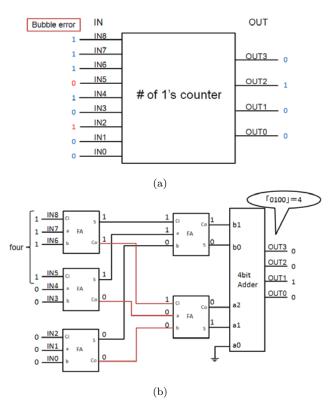

# 5. フラッシュADC

フラッシュ型では N ビット分解能実現のために  $2^N-1$  個のコンパレータを使用するので大きな冗長性を持ってい

図 5 3 個のコンパレータを用いた SAR ADC. (a) 構成. (b) 動作.

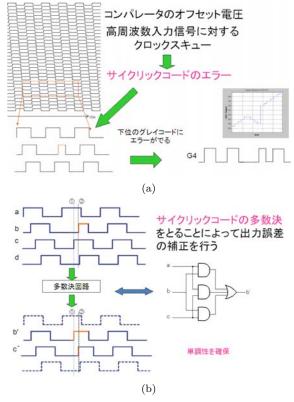

るといえよう. 理想的にはコンパレータ出力の配列は温度計コードとなりエンコーダ回路により 2 進コードに変換される (1対1対応である). しかし実際にはコンパレータオフセット等によりバブルエラーが生じ得て, 対処しないと大きな出力誤差となる (図 7 (a)). この影響を抑圧するため多数決回路 (図 7 (b)) や 1 の数を数えるエンコーダ回路 (図 8) を用いる.

フラッシュADC では冗長性によるディジタル誤差補正を性能向上のために積極的に使用するというより、冗長性により定義されていないコンパレータ出力パターンをできるだけ少なくする(それによる大きな出力誤差をなくす)という観点からディジタル誤差補正技術が用いられていると解釈できよう.

#### 6. 折り返し補間型 ADC

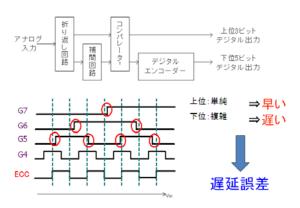

フラッシュ型 ADC アーキテクチャの改良版として折り返し補間型 (Folding/Interpolation)ADC が提案・実現されている (3)(4)(12)-(14). これは上位ビット生成は折り返し回路でアナログエンコードを行い、下位ビット生成は抵抗補間で回路量を減らし、フラッシュADC と同等のサンプリングスピードを達成しながら回路・消費電力・入力容量を大幅に削減する方式である.

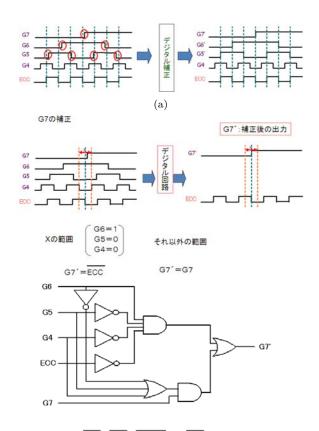

ここでは上位ビット生成回路と下位ビット生成回路間のタイミングスキューおよびアナログエンコーダ回路のオフセットが問題となり (図 9)、そのディジタル補正技術が開発されている (図 10)  $^{(3)}$   $^{(14)}$ . (すなわちディジタル誤差補正

図 6 (a) パイプライン ADC の構成と動作. (b) パイプライン ADC での 2 段目 ADC での冗長性によるディジタル 誤差補正の原理. (c) 冗長性を利用したバックグランド自己 校正パイプライン ADC の構成.

技術によりタイミングスキュー, アナログエンコーダ回路のオフセットの影響を軽減している.) これは下位ビット生成回路の冗長性を利用して上位ビットを補正するものである.

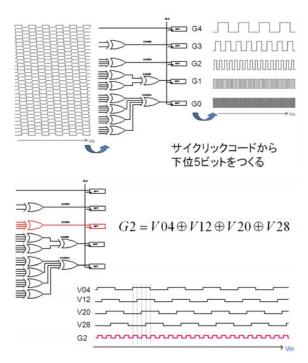

また、下位ビット生成においてもコンパレータオフセットの影響を低減するために(フラッシュADC と同様に下位ビット生成の冗長性を利用して)サイクリックコード間多数決コードを利用できる(図 11, 12).

#### 7. ADC でのディジタル誤差補正の共通の構造

以上のようにいくつかの ADC 構成でのディジタル誤差補 正技術を見てみると、そこに次のような共通なことがある。 命題 1 1つの 2 進ディジタルコード ADC 出力に対して、 複数の「コンパレータ出力の組」が対応するとき、冗長性 によるディジタル誤差補正が実現できる。

2 進逐次比較近似 ADC 以外の ADC ではほとんどの場合 が冗長性を持っていよう. また 筆者の経験から次のことが

図 7 (a) 温度計コードとバブルエラー. (b) 多数決回路を 用いたフラッシュADC 構成.

### 言えると考えている.

命題 2 ADC 内に (ある程度の) 冗長性を持たせると各回路構成要素への要求が緩和され, ADC 全体として性能向上を達成できる.

設計上注意すべき点として次のことがある。全てのコンパレータパターンが各々2進ディジタルコード ADC 出力に対応するように設計されているのが望ましい。(これを well-defined redundancy と呼ぶことにする。フラッシュADC で"コンパレータ出力で 1 の数を数えるエンコーダ回路を使用しているもの等がこれに対応する。) この設計がなされていないとき 予期せぬコンパレータ出力パターンのとき (バブルエラー対策がないフラッシュADC でバブルエラーが生じたとき等に対応する), 大きな ADC 出力誤差となりえる。

# 8. 冗長性をもつ回路の設計検証・テストの問題

アナログ部の非理想要因を回路,動作の冗長性によりディジタル誤差補正する技術は,量産時の歩留まりを考慮した際の設計検証およびテストは難しくなる(16)(17). 冗長性を全てテストする必要がある場合,ADCトータル性能の一部としてテストすればよい場合等の分類の考察も必要であろう.

9. ADC の可観測性向上によるテスト・診断容易化

多くの場合 ADC 出力は最終の2進コードのみであり内部のコンパレータの値は読めないことが多い. しかし,多く

図 8 フラッシュADC でバブルエラーの影響を抑圧するエンコーダ回路. (a) コンパレータ出力の1の数を数えるエンコーダ回路. (b) その全加算器による実現.

図 9 折り返し補間 ADC での上位・下位ビット間の誤差.

の ADC では冗長性をもち、一つの 2 進コード出力に対して 複数のコンパレータ出力の組をもつ。そこで SOC 内 ADC で、全てのコンパレータ出力を全てのタイミングで観測し SOC 内部のディジタル回路を利用して ADC の特性を推定 することがテストおよび診断容易化を実現する技術の候補 になり得よう。<sup>(15)</sup>.

#### 10. まとめ

いくつかの AD 変換器構成で用いられている, 回路や動作の冗長性によるディジタル誤差補正技術の共通構造を検討した. 冗長性により ADC 設計が容易になり, 結果として ADC が高速化・低消費電力化できる. これを一般化して考

$G7' = G6 \cdot \overline{G5} \cdot \overline{G4} \cdot \overline{ECC} + (\overline{G6} + G5 + G4) \cdot G7$ (b)

図 10 折り返し補 ADC での上位・下位ビット間の誤差補 正. (b) MSB ビット補正.

察すると、冗長性をもった回路システムでは冗長性によりある程度の誤動作・回路の非理想要因を許容するので、各構成要素・動作に対する要求が緩和され、結果的に全体としてより効率が良くなると言えよう。またこの技術を用いたADCの設計検証・テストの問題も重要である。今後もこの技術について体系的・俯瞰的な見方で検討していきたい。

謝 辞 有意義な御討論をいただきました Asad A. Abidi 先生, 松浦達治様, 小林修様, 宮下博之様, 力野邦人様, 関係 各位 およびこの研究をご支援いただいています半導体理工 学研究センター (STARC) に謝意を表します.

#### 参考文献

- (1) 小林春夫, "ナノ CMOS 時代のアナログ回路 ディジタルアシスト AD 変換技術を中心として -", 電子情報通信学会 第 22 回 回路とシステム(軽井沢) ワークショップ (2009 年 4 月).

- (2) T. Yagi, K. Usui, T. Matsuura, S. Uemori, Y. Tan, S. Ito, H. Kobayashi, "Background Calibration Algorithm for Pipelined ADC with Open-Loop Residue Amplifier using Split ADC Structure", IEEE Asia Pacific Conference on Circuits and Systems, Kuala Lumpur (Dec. 2010).

図 11 折り返し補間 ADC での下位ビット生成.

- (3) R. V. Plassche, "Integrated Analog-to-Digital and Digital-to-Analog Converters", Kluwer Academic Publishers (1994).

- (4) R. V. Plassche, "CMOS Integrated Analog-to-Digital and Digital-to-Analog Converters", Kluwer Academic Publishers (2003).

- (5) H. San, Y. Jingu, H. Wada, H. Hagiwara, A. Hayakawa, H. Kobayashi, T. Matsuura, K. Yahagi, J. Kudoh, H. Nakane, M. Hotta, T. Tsukada, K. Mashiko, A. Wada, "A Second-Order Multi-bit Complex Bandpass AD Modulator With I, Q Dynamic Matching and DWA Algorithm", IEICE Trans. Electronics, vol. E90-C, no.6, pp.1181-1188 (June 2007).

- ( 6 ) S. Ito, S. Nishimura, H. Kobayashi, S. Uemori, Y. Tan, N. Takai, T. J. Yamaguchi, K. Niitsu, "Stochastic TDC Architecture with Self-Calibration", IEEE Asia Pacific Conference on Circuits and Systems, (Dec. 2010).

- (7) T. Ogawa, H. Kobayashi, Y. Takahashi, N. Takai, M. Hotta, H. San, T. Matsuura, A. Abe, K. Yagi, T. Mori, "SAR ADC Algorithm with Redundancy and Digital Error Correction", IEICE Trans. Fundamentals, vol. E93-A, no.2 (Feb. 2010).

- (8) 小川 智彦, 松浦 達治, 小林 春夫, 高井 伸和, 堀田 正生, 傘 昊, 阿部 彰, 八木 勝義, 森 俊彦, "逐次比較近似 ADC コンパレータ・オフセット影響の冗長アルゴリズムによるディジタル補正技術", 電子情報通信学会誌 和文誌 C, vol. J94-C, no.3 (2011 年 3 月).

- ( 9 ) T. Ogawa, T. Matsuura, H. Kobayashi, N. Takai, M. Hotta, H. San, A. Abe, K. Yagi, T. Mori, "Non-binary SAR ADC with Digital Error Correction for Low Power Applications, "IEEE Asia Pacific Conference on Cir-

図 12 (a) サイクリックコードの誤差. (b) 多数決回路によるディジタル補正.

cuits and Systems, (Dec. 2010).

- (10) 早川晃, 趙楠, 堀田正生, 小林春夫、"高性能逐次比較 A D 変換器アーキテクチャ",電気学会電子回路研究会, 桐生 (2006 年 3 月).

- (11) M. Hotta, M. Kawakami, H. Kobayashi, H. San, N. Takai, T. Matsuura, A. Abe, K. Yagi, T. Mori, "SAR ADC Architecture with Digital Error Correction", IEEJ Transactions on Electrical and Electronic Engineering, vol.5, no.6, pp.651-659 (Nov. 2010).

- (12) 林海軍、山口 宣、真壁 和也、亀井 篤、小林春夫, "電荷 モード折り返し AD 変換回路", 電子情報通信学会誌 和 文誌 C, vol.J89-C, no.10 (Oct. 2006).

- (13) H. Kobayashi, T. Mizuta, K. Uchida, H. Matsuura, A. Miura, T. Yakihara, S. Oka and D. Murata, "A High-Speed 6-bit ADC Using SiGe HBT", IEICE Trans. on Fundamentals, vol.E81-A, no.3, pp.389-397 (March 1998).

- (14) H. Kobayashi, H. Sakayori, T. Tobari and H. Matsuura, "Error Correction Algorithm for Folding/Interpolation ADC", International Symposium on Circuits and Systems, vol.1, pp.700-703 (May 1995).

- (15) T. Ogawa, H. Kobayashi, Y. Tan, S. Ito, S. Uemori, N. Takai, K. Niitsu, T. J. Yamaguchi, T. Matsuura, N. Ishikawa, "SAR ADC That is Configurable to Optimize Yield", IEEE Asia Pacific Conference on Circuits and Systems, (Dec. 2010).

- (16) 小林春夫、山口隆弘、"ディジタルアシスト・アナログテ

図 13 フォアグランド自己校正パイプライン ADC での MDAC 単位容量の測定.

スト技術",電子情報通信学会 集積回路研究会 (2010 年7月).

(17) 小林春夫, 新津葵一, 高井伸和, 山口隆弘, "ディジタルア シスト・アナログ RF テスト技術 - サブ 100nm ミックス トシグナル SoC テストの考察 - ", 電子情報通信学会 総合大会 (2011 年 3 月).

# 付 録

パイプライン ADC のフォアグランド自己校正では、後段の sub-ADC で初段の内部 DAC の特性を測定し、その値をメモリに記憶して通常動作時に出力データを補正することが行われる(図 2). なぜ理想的でない(分解能・精度が限られた) sub-ADC で測定して全体として正しい値が得られるか(自己校正ができるか)を考察する.

内部 DAC をスイッチトキャパシタ回路で構成する場合を考える (図 13). 各容量値を後段の sub-ADC で測定する場合,容量が分割されているので各容量の許容誤差に対する測定のダイナミックレンジを小さくできる (Divide and conquer). これが分解能が低く精度の悪い sub-ADC で測定しても自己校正ができる定性的な理由であろう. 一方,これらの容量をオペアンプで結合して内部 DAC を構成する場合のオペアンプ有限ゲイン等による誤差 (superposition error) も必要に応じて測定・補正して自己校正を実現しなければならない.

逆にこれらの観点から、自己校正実現のための後段の sub ADC への要求性能を求めることができる.