ジッタ測定 BIST に向けたインターリービング PFD のプロセス依存性の解析

櫻井 正人 針谷 尚裕 新津 葵一\* 山口 隆弘 小林 春夫

Masato Sakurai Naohiro Harigai Kiichi Niitsu Takahiro Yamaguchi Haruo Kobayashi 群馬大学大学院 工学系研究科 電気電子工学専攻 〒376-8515 群馬県桐生市天神町 1-5-1

Electronic Engineering Dept. Gunma University, Kiryu 376-8515 \* E-mail: niitsu@el.gunma-u.ac.jp

## 1. 研究目的・背景

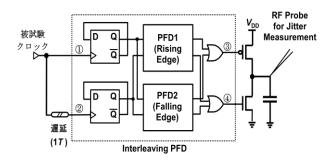

半導体製造プロセスの微細化に伴い、大規模集積回路における動作周波数は上昇の一途をたどっている。動作周波数が向上するにつれて顕在化しているのがジッタによる動作不良である。そこで、近年チップ上でジッタを測定する回路技術が多く発表されている[1](図1)。本研究においては、ジッタをオンチップで測定する際にキーコンポーネントとなるインターリービング位相比較器(Phase Frequency Detector: PFD)のスケーリング(製造プロセス依存性)に関する報告を行う。

## 2. インターリービング PFD 回路の設計

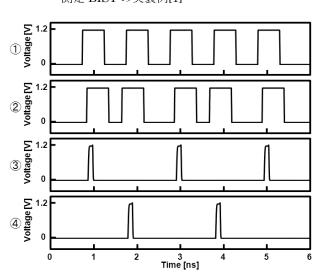

インターリービング PFD は 2 種類のクロックの位相を比較し、 クロックのタイミングに応じたパルスを出力する(図 2)。インター リービング PFD では通常の PFD の前段でクロックを分周して回 路の活性化率を低減させることで、ジッタの発生を抑えている。

180nm,65nm,40nm の各プロセス世代において SPICE シミュレーションを行ったところ、スケーリングにより消費電力・面積・動作周波数の向上が確認できた(表 1)。

消費電力・面積ではスケーリングの効果が大きく表れていることが分かった。特に面積において 40nm プロセスは 180nm プロセスに対して 25 倍もの縮小が可能であり、スケーリングが有効であることが確認できた。動作周波数についてもスケーリングは有効であるが、分周器の動作周波数によって律即されているためスケーリング則から期待される動作周波数の向上はみられなかった。

## 3. 結論

スケーリングにより消費電力・面積・動作周波数の向上が確認できた。40nm,65nm 世代において、インターリービング PFD 回路を用いた回路が高速シリアルインタフェースなどへの適用が可能であることを示した。

図 1.インターリービング PFD を用いたジッタ 測定 BIST の実装例[1]

図 2.インターリービング PFD の動作 (①~④は図 1 に対応)

| Technology      | 40nm | 65nm | 180nm |

|-----------------|------|------|-------|

| Power [mW]      | 1.45 | 3.29 | 36.2  |

| Area [um²]      | 41   | 125  | 1080  |

| Frequency [GHz] | 12.5 | 11.1 | 2.2   |

図3.電力・面積・動作周波数のプロセス依存性

謝辞:この研究をご支援いただいています半導体理工学研究センター(STARC)に謝意を表します。

参考文献: [1] M. Ishida, T. J. Yamaguchi, et al., "A Programmable On-Chip Picosecond Jitter-Measurement Circuit without a Reference-Clock Input," in *Proc. IEEE Int. Solid-State Circuits Conf.*, pp. 512-513, (Feb. 2005.)