# SoC 内 ADC テスト信号生成アルゴリズム

## ADC Test Signal Generation Algorithm for Mixed-Signal SoC

上森 聰史<sup>\*1</sup>

Satoshi Uemori

伊藤 聰志<sup>\*1</sup>

Satoshi Ito

古川 靖夫<sup>\*2</sup>

Yasuo Furukawa

山口 隆弘<sup>\*3</sup>

Takahiro J. Yamaguchi

浅見 幸司<sup>\*2</sup>

Koji Asami

小林 春夫<sup>\*1</sup>

Haruo Kobayashi

<sup>\*1</sup>群馬大学大学院 工学系研究科 電気電子工学専攻 〒376-8515 群馬県桐生市天神町 1-5-1

Electronic Engineering Dept. Gunma University, Kiryu 376-8515

<sup>\*2</sup>(株)アドバンテスト Advantest Corporation, <sup>\*3</sup>(株)アドバンテスト研究所 Advantest Laboratories LTD

### 1. SoC 内 ADC 線形性の短時間・高精度テスト

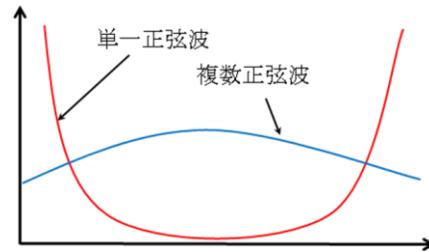

SoC 内 ADC ではその入力信号は ADC 入力フルレンジを均等に使うのではなく主に中心付近を使う場合が多い。SoC 出荷試験時でのその ADC の線形性テストの際には短時間テストで中心付近の線形性テストの精度を高めることが重要である。しかしランプ波入力、単一正弦波を用いるヒストグラム法による線形性テスト法では入力レンジで頻度は均一、もしくは中心付近での頻度は少なくなるてしまう[1] (図 1)。ここでは上記要求を満たすために、複数の正弦波を足し合わせた信号を線形性テスト入力とすることにより中心付近の頻度を増加させるアルゴリズムを提案する。

### 2. 提案するテスト信号生成アルゴリズム

三角波のフーリエ級数は以下となる。

$$V_{in} = \frac{4}{\pi} \sum_{n=1}^{\infty} \frac{\cos((2n-1)\omega t)}{(2n-1)^2} \quad (n=1,2,\dots)$$

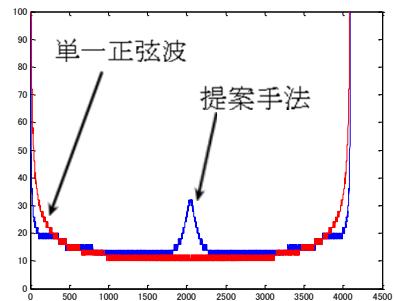

この三角波入力フーリエ級数展開で、第一項+(n が偶数項)を足し合わせた場合、入力波形の中心付近の傾きは緩やかになる。その結果、ヒストグラムの中心付近が持ち上がる。足し合わせる偶数項を増やすと持ち上がる範囲は狭くなってしまう(図 2)。

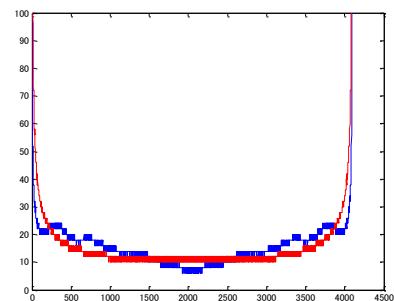

一方、第一項+(n が奇数項)を足し合わせた場合、入力波形の中心付近の傾きは急になり、両端付近は逆に緩やかになる。したがってヒストグラムの中心付近は下がり両端付近が持ち上がる。足し合わせる奇数項を増やした場合中心付近の下がりは大きくなるが、両端の持ち上がる範囲は広くなる(図 3)。

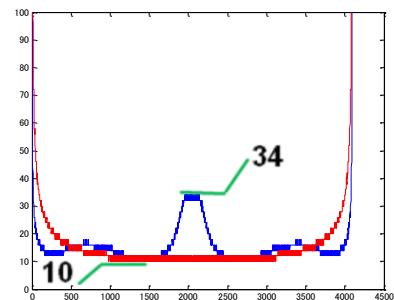

奇数項でのヒストグラムの中心付近の下がりに対し、偶数項での持ち上がる割合の方が大きいことが分かった。そこで、足し合わせる偶数項、奇数項、及びその振幅を調整した信号をテスト入力とすることにより、中心付近でヒストグラムの持ち上がる量を維持しつつ、その持ち上がる範囲を広げることができる(図 4)。

複数正弦波を合成するテスト入力を生成するには半導体試験装置内の任意波形発生器(Arbitrary Waveform Generator: AWG)を用いることで比較的容易に実現できる。すなわちデジタル的に複数正弦波の合成信号を発生させて DA 変換器に入力し、その出力を低域通過アノログフィルタを通して ADC にテスト信号として入力する。

今後は 入力波形合成アルゴリズムのシステムマッテックな設計法の確立と実験による有効性の確認をおこなう。

<参考文献> [1] B .Razavi , Data Conversion System Design, IEEE Press(1995)

図 1. 単一正弦波の場合と目標のヒストグラム

図 2. 第一項+(n が偶数項)の場合のヒストグラム

図 3. 第一項+(n が奇数項)の場合のヒストグラム

図 4. 調整後の合成入力波形でのヒストグラム