平成24年1月 FTC研究会

# デジタル信号時間差測定用回路の構成の検討(システムレベル検証)

上森聡史 石井正道 小林春夫 土井佑太(群馬大学) 小林修(STARC) 松浦達治 新津葵一(群馬大学)

- 研究背景と目的

- ΔΣ TDCの構成・動作

- マルチビットΔΣ TDCの構成・動作と

エレメントローテーション回路の適用

- エレメントローテーション回路の動作

- MATLABシミュレーションによる検証

- 結論

- 研究背景と目的

- ΔΣ TDCの構成・動作

- マルチビットΔΣ TDCの構成・動作と

エレメントローテーション回路の適用

- エレメントローテーション回路の動作

- MATLABシミュレーションによる検証

- 結論

# 研究背景

- 半導体製造コストの減少に対しテストコストは増加

- テストコストを下げる

- ・ デジタル信号間の時間差の測定

- 短時間で求める精度で測定する必要あり

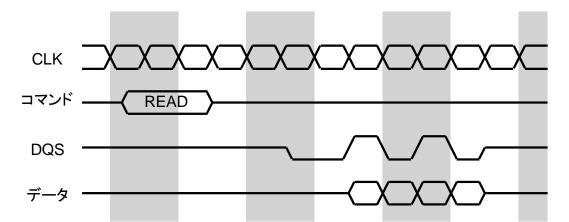

- 適用するアプリケーションの例

- DDR(Double Data Rate)メモリのデータ、クロック間の 時間差の計測等:

内部処理回路とメモリアクセスのタイミング、制御信号・ データ信号間のタイミング

# 研究目的

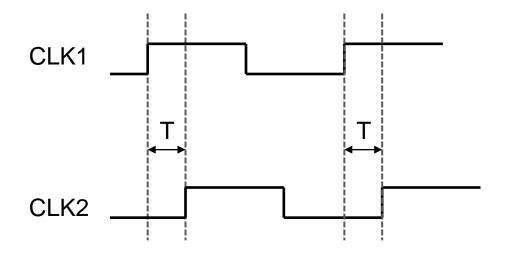

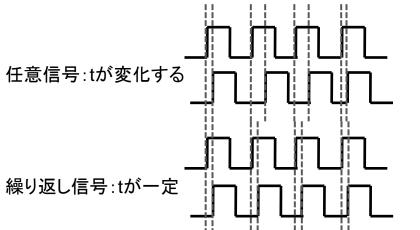

- 2つの繰り返しクロック間の時間差を 高時間分解能・簡単な回路で計測

- ΔΣ型タイムデジタイザを用いる

- マルチビットΔΣ型タイムデジタイザの提案

- 短時間で所定の精度・分解能で時間差をテスト

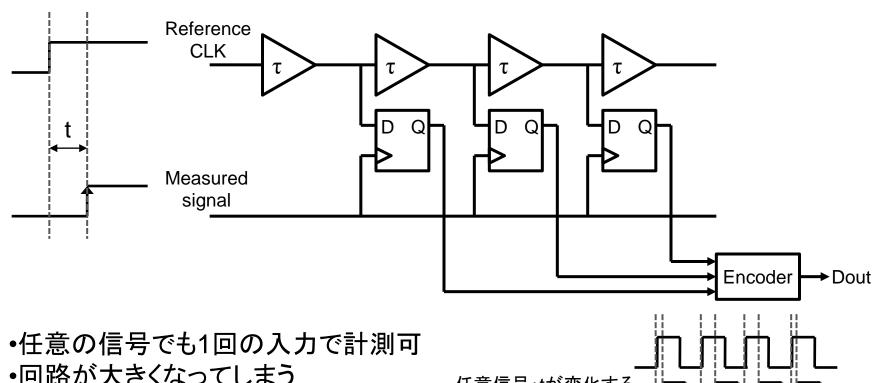

# 従来基本TDC構成

### •Flash型TDC

- ・回路が大きくなってしまう

- •時間分解能はτで決まってしまう

- •何回も入力 ⇒ 高精度で測定する ▶繰返し信号を計測

- 研究背景と目的

- ΔΣ TDCの構成・動作

- マルチビットΔΣ TDCの構成・動作と

エレメントローテーション回路の適用

- エレメントローテーション回路の動作

- MATLABシミュレーションによる検証

- 結論

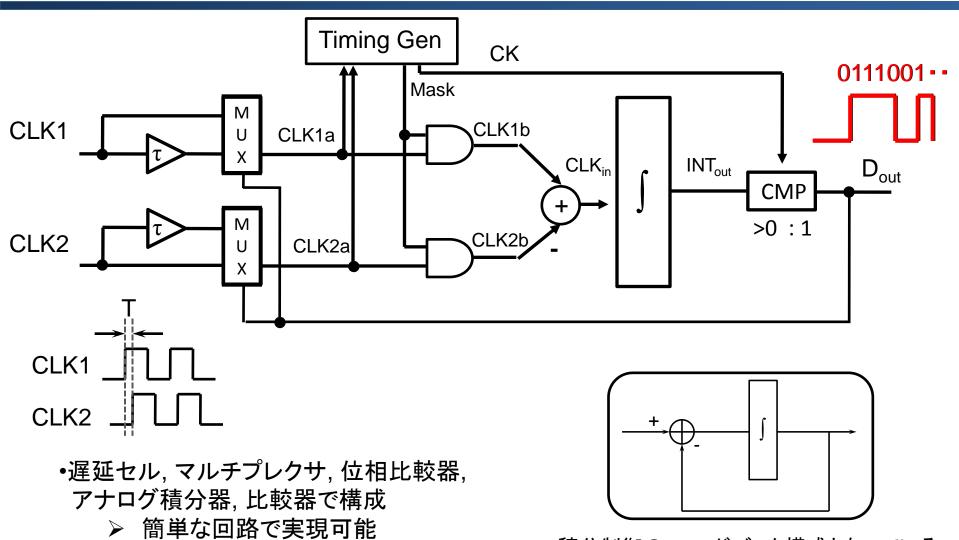

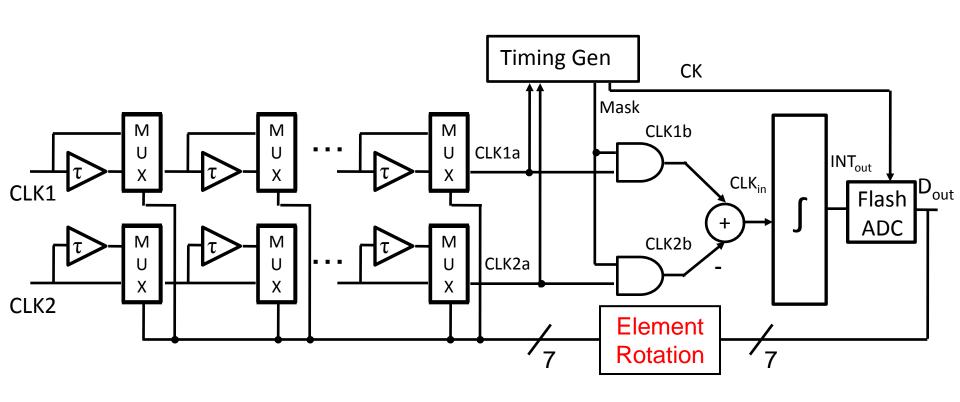

# ΔΣ TDC回路の構成

•積分制御のフィードバック構成となっている

- •CLK1とCLK2間の時間差を計測

- •出力は時間差Tに比例 ⇒ 1の個数でTを測定可能

- •測定可能範囲:-τ<T<τ

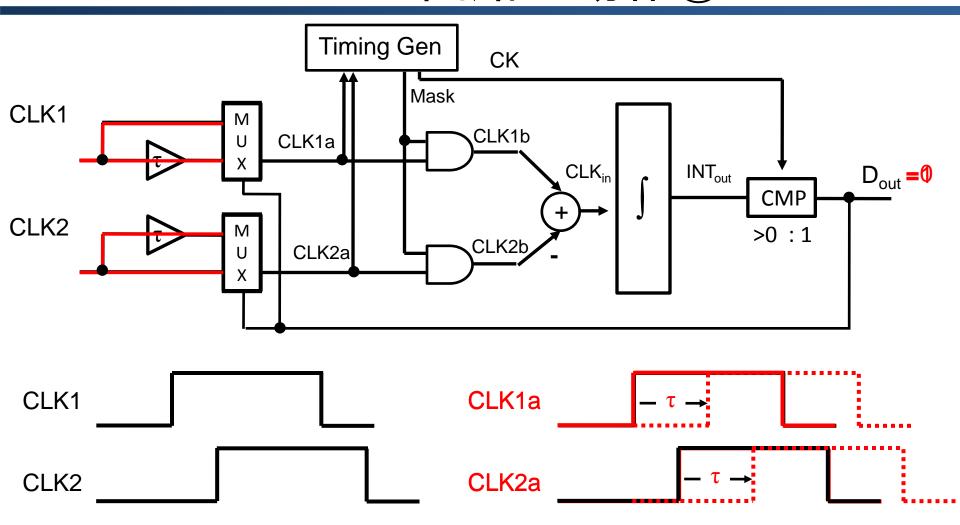

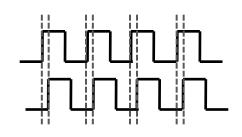

# ΔΣ TDC回路の動作①

- •CLK1とCLK2を入力

- ・比較器出力により経路選択

- ➤ CLK1a, CLK2aを得る

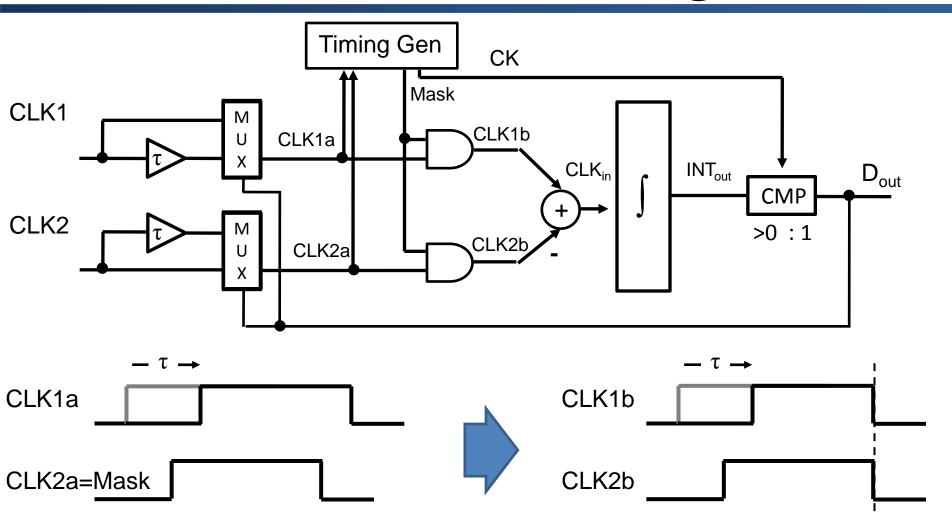

# ΔΣ TDC回路の動作②

- •タイミングジェネレータによりMask信号(=速い方の信号)を発生させる

- ➤ Mask信号とCLK1a, CLK2aとの論理積をとり、立下りを合わせる

- ➤ CLK1b, CLK2bを得る

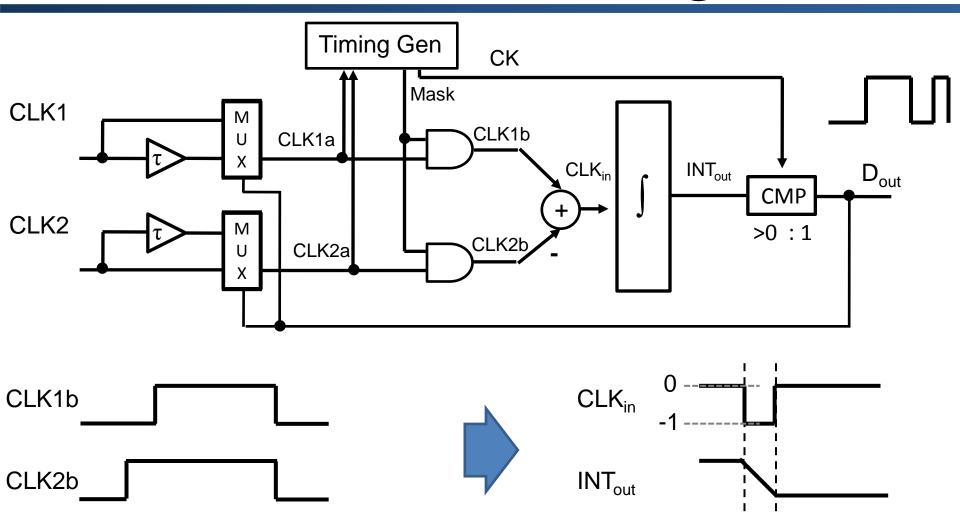

# ΔΣ TDC回路の動作③

- •CLK1bとCLK2bとの差をとり結果のCLKinを積分

- •比較器でINToutを0と比較し、出力Doutを得る

- ▶ 次のクロックでの経路を制御

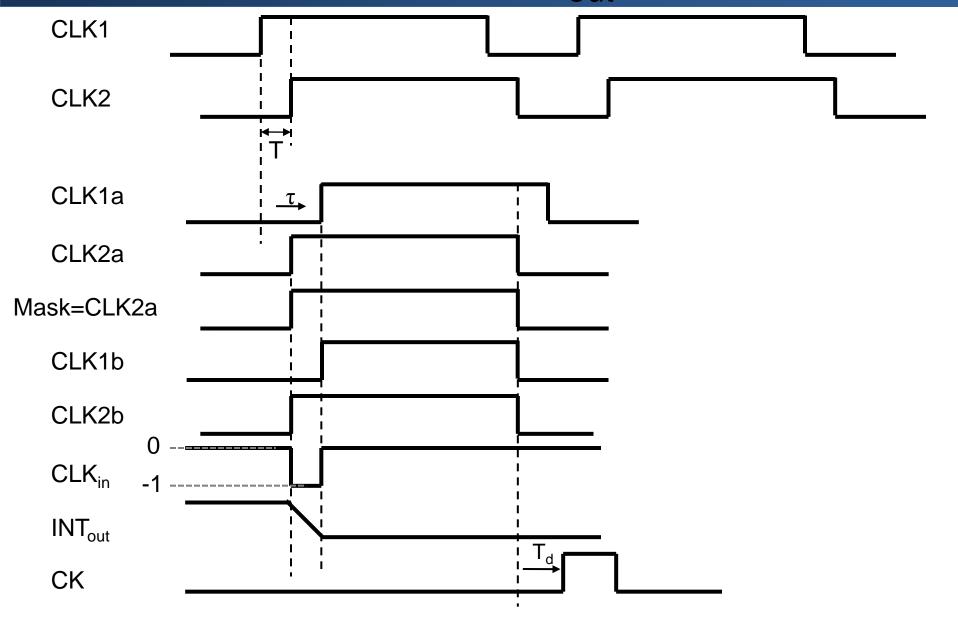

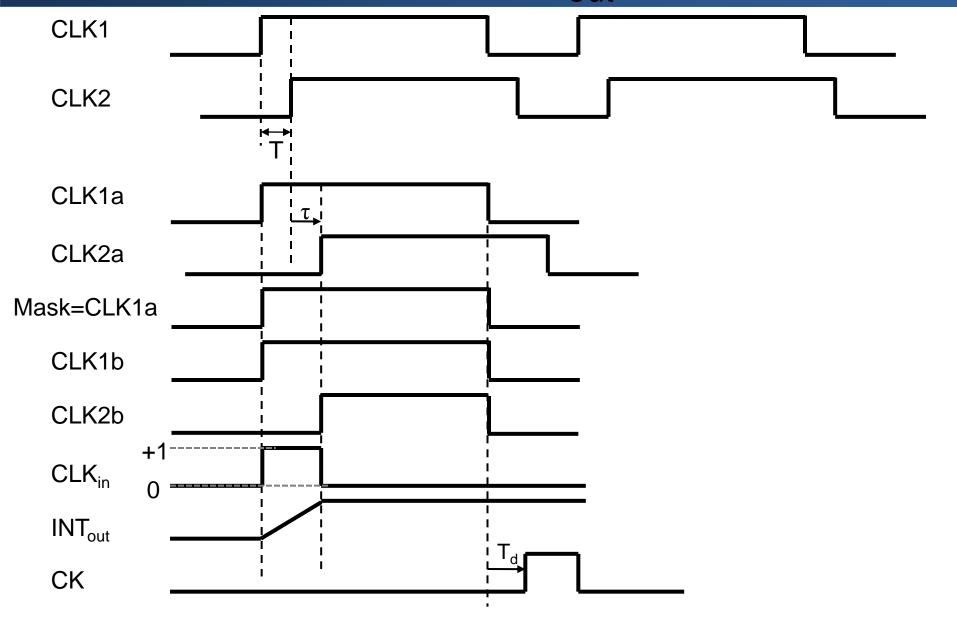

# タイミングチャート(Dout=1のとき)

# タイミングチャート(Dout=0のとき)

- 研究背景と目的

- ΔΣ TDCの構成・動作

- マルチビットΔΣ TDCの構成・動作と

エレメントローテーション回路の適用

- エレメントローテーション回路の動作

- MATLABシミュレーションによる検証

- 結論

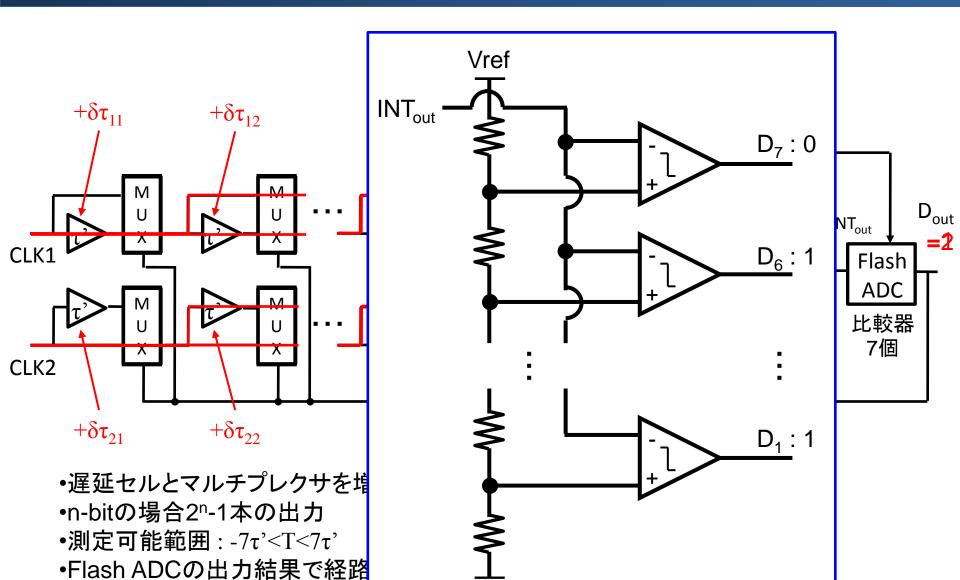

# マルチビットΔΣ TDC回路の構成

遅延セルのミスマッチによって

# エレメントローテーション回路の適用

- •エレメントローテーション回路(DWA)でFlash ADCの温度計コード出力を シャッフルしてから各MUXに入力する

- ・工夫してシャッフルすることでミスマッチを時間平均 ⇒ ノイズを高周波側へ移す

- •遅延ばらつきの影響を少なくする

# マルチビットにする利点

- •シングルビットΔΣ TDC

- •遅延ミスマッチが影響しない

- •精度は出せる

- •テストの際には短時間で所定の精度で評価

- •マルチビットにすることで速く計測できる

- •エレメントローテーション回路を用いることである程度精度 が出せる

- 研究背景と目的

- ΔΣ TDCの構成・動作

- マルチビットΔΣ TDCの構成・動作と

エレメントローテーション回路の適用

- エレメントローテーション回路の動作

- MATLABシミュレーションによる検証

- 結論

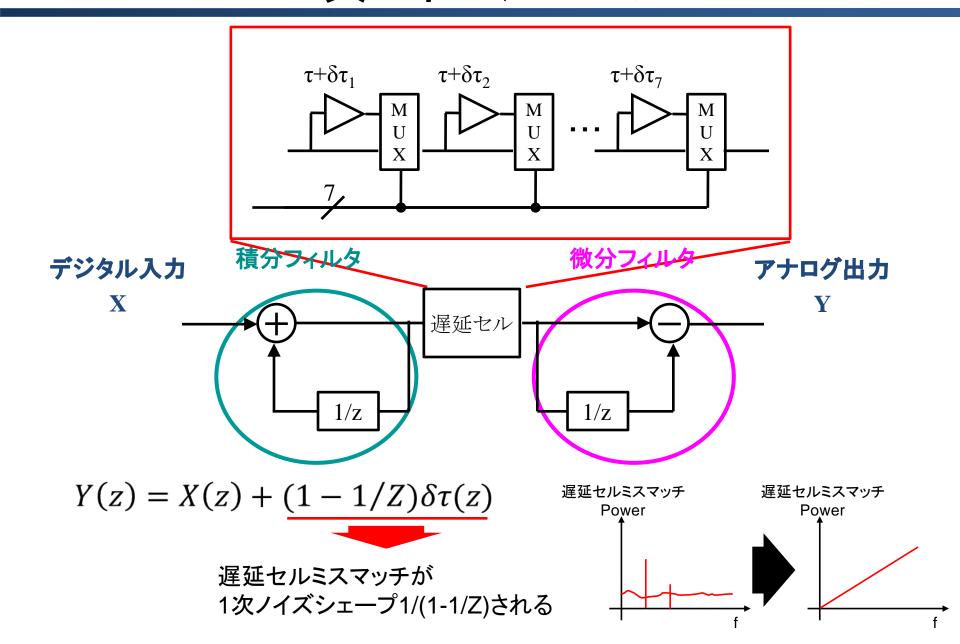

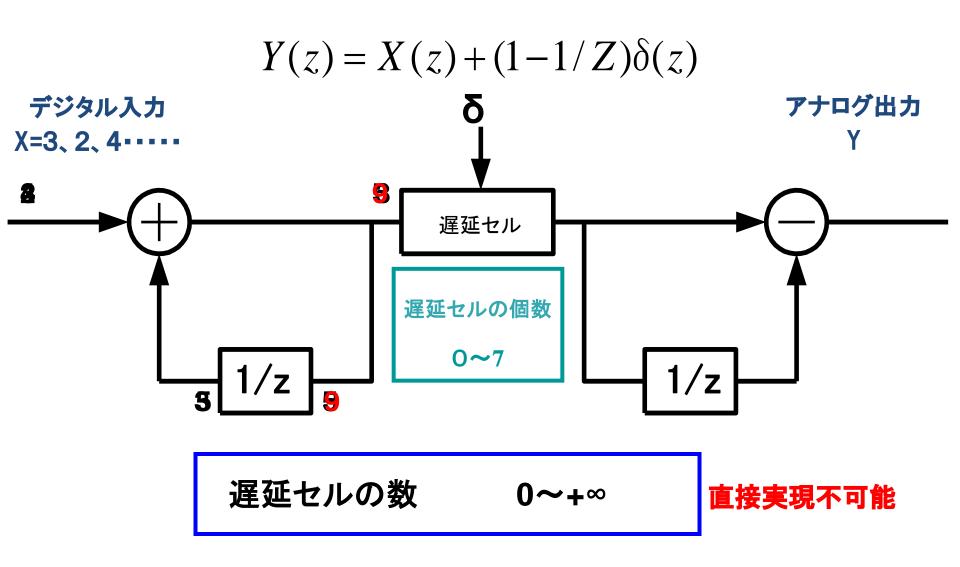

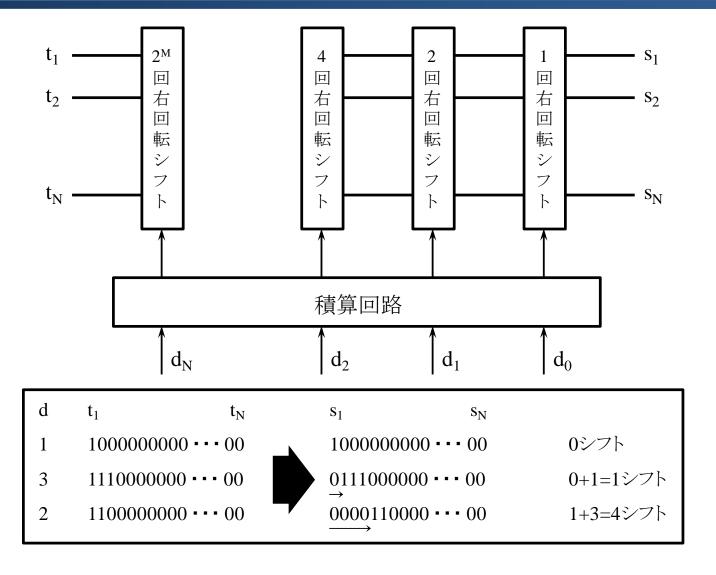

# 1次ノイズシェープ

# 1次ノイズシェープの動作

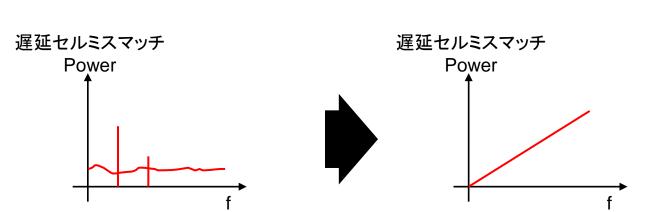

# エレメントローテーション回路の効果

•積分して微分を等価的に実現 ▶遅延セルミスマッチが1次ノイズシェープ

繰り返し信号を測定する

DC成分のノイズが減少すれば 理想に近づく

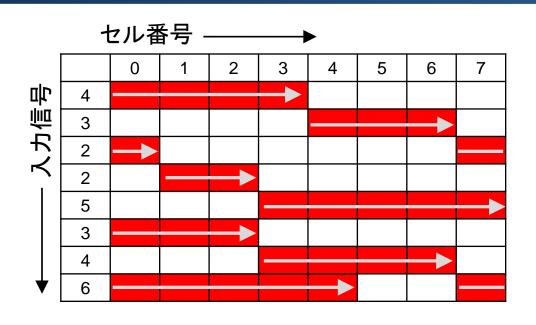

### エレメントローテーション回路の動作

•デジタル入力によりシフトする量を制御する

- 研究背景と目的

- ΔΣ TDCの構成・動作

- マルチビットΔΣ TDCの構成・動作と

エレメントローテーション回路の適用

- エレメントローテーション回路の動作

- MATLABシミュレーションによる検証

- 結論

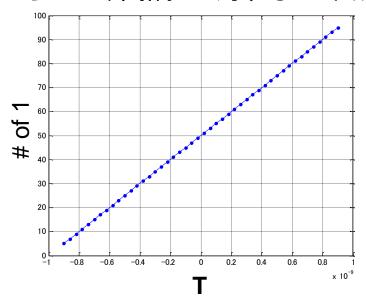

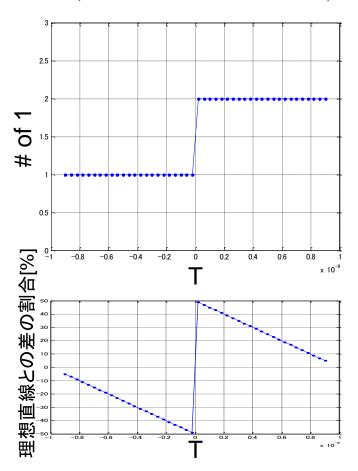

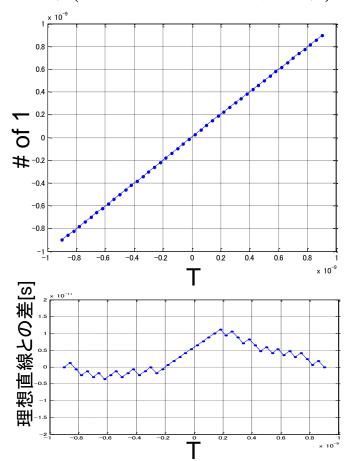

# ΔΣ TDCのシミュレーション結果

#### MATLABシミュレーション

#### 1bitの場合

・立ち上がり間隔 : T=0.04ns刻み

-0.9~0.9ns

•遅延時間: τ=1ns

•出力数(コンパレータで比較した回数): 99点

●立ち上がり間隔Tに対する1の出力数

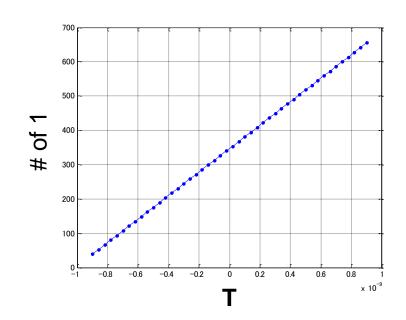

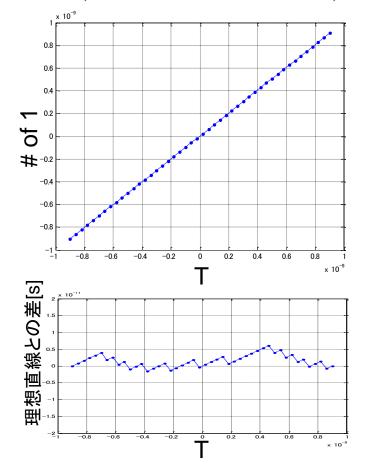

#### 3bitの場合

•立ち上がり間隔 : T=0.04ns刻み

-0.9~0.9ns

•遅延時間: τ=0.145ns

•出力数(コンパレータで比較した回数): 99点

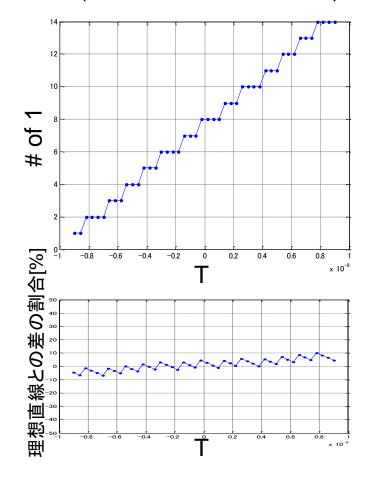

# 測定時間を短縮した場合の検討

1bit

•遅延時間: τ=1ns

・出力数(コンパレータの比較回数):2点

#### 3bit

•遅延時間:τ=0.145ns

・出力数(コンパレータの比較回数):2点

✓マルチビット化することで短時間で細かく測定可能

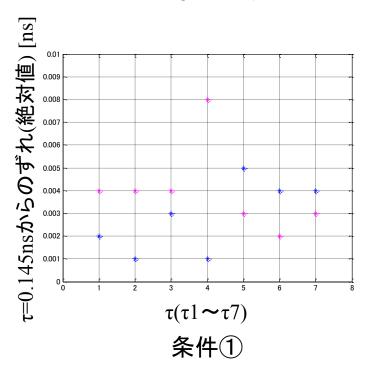

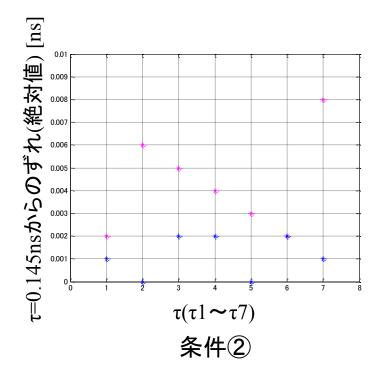

# 遅延ばらつきの影響の検証

•遅延ばらつき: ガウス分布でランダムに生成 最大でτ=0.145ns の±10%程度の誤差とした

•シミュレーション時に生成した遅延パラメータ

\*:CLK1経路の遅延値

\*:CLK2経路の遅延値

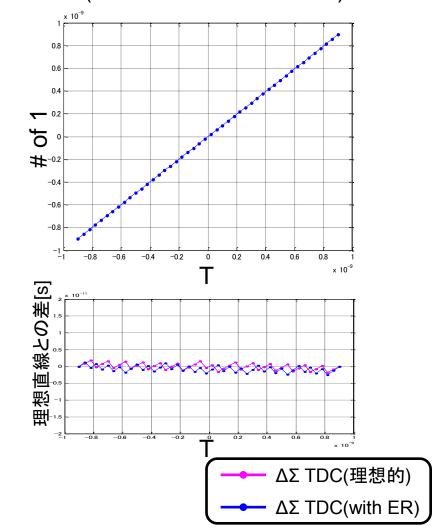

# エレメントローテーションの効果(条件①)

3bit, 遅延ばらつき有

•遅延時間: τ=0.145ns

出力数(コンパレータの比較回数):99点

✓遅延ばらつきの影響を軽減できる

3bit, エレメントローテーション回路適用

•遅延時間:τ=0.145ns

・出力数(コンパレータの比較回数):99点

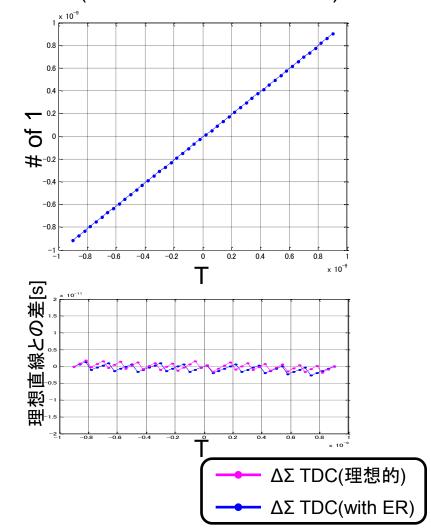

# エレメントローテーションの効果(条件②)

3bit, 遅延ばらつき有

•遅延時間: τ=0.145ns

出力数(コンパレータの比較回数):99点

✓遅延ばらつきの影響を軽減できる

3bit, エレメントローテーション回路適用

•遅延時間:τ=0.145ns

・出力数(コンパレータの比較回数):99点

# 回路性能のまとめ

|       | Flash TDC | 1-bit ΔΣ TDC | マルチビット<br>ΔΣ TDC<br>(without ER) | マルチビット<br>ΔΣ TDC<br>(with ER) |

|-------|-----------|--------------|----------------------------------|-------------------------------|

| 回路量   | 大 ×       | 小◎           | 中〇                               | 中〇                            |

| 時間分解能 | 粗×        | 細 ◎          | 細 ◎                              | 細◎                            |

| 精度    | Δ         | 0            | ×                                | 0                             |

| 測定時間  | 短◎        | 長 ×          | 中〇                               | 中〇                            |

# 2ステップ方式による測定範囲拡大

- 細かく測定するにはでは出来るだけ小さい方が良い

- > 測定可能範囲は狭くなる

- Coarse TDC:通常のTDC回路

- ➤ バッファ遅延線とFlip-Flopアレイを使用

- Fine TDC : ΔΣ TDC

- マルチビットの場合はエレメントローテーションを用いて補正

- 自己校正:

- ➤ 基準クロックを与えてCoarse TDC内バッファ遅延線の各 バッファ遅延値を測定 その値を元にデジタル補正

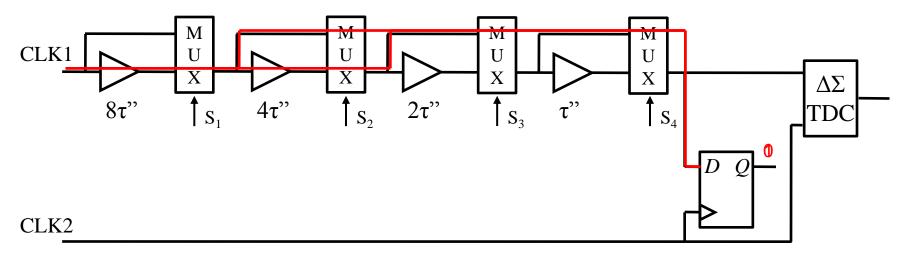

### 逐次比較TDCを用いた広入力範囲TDC

Step1:  $8\tau$ "を通して測定  $\Rightarrow$  Q=0なら $S_1$ =0, Q=1なら $S_1$ =1

Step2:  $4\tau$ "を通して測定  $\Rightarrow$  Q=0なら $S_2$ =0, Q=1なら $S_2$ =1

Step3:  $2\tau$ "を通して測定  $\Rightarrow$  Q=0なら $S_3$ =0, Q=1なら $S_3$ =1

Step4:  $\tau$ "を通して測定  $\Rightarrow$  Q=0なら $S_4$ =0, Q=1なら $S_4$ =1

- Δ∑ TDCで精度を出すには何クロックも入力する必要がある

- ▶ 数ステップ増えても大差ないことを利用

- 測定時:通常動作

- 遅延誤差補正:テスト動作

- 測定可能範囲:15τ"+τ

τ : ΔΣ TDC内の遅延値(τ≧τ")

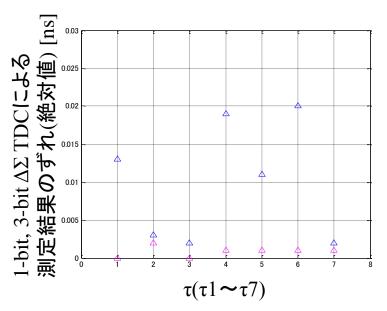

# 広入力範囲TDCの例

- Coarse TDCの遅延値に0.5n secの±10%の誤差

- 1-bitと3-bitのΔΣ TDC(遅延誤差なし)で測定 (シミュレーション: MATLAB)

- Tが8.5n secまで測定可(Coarse TDC 7.5n sec+ ΔΣ TDC 1n sec)

出力数(比較回数):99点

<u>Δ</u>: 1-bit ΔΣ TDCの結果

Δ:3-bit ΔΣ TDCの結果

✓同じ測定時間でも3-bitのΔΣ TDCの方が細かく測定できる

- 研究背景と目的

- ΔΣ TDCの構成・動作

- マルチビットΔΣ TDCの構成・動作と

エレメントローテーション回路の適用

- エレメントローテーション回路の動作

- MATLABシミュレーションによる検証

- 結論

# 結論

- 時間差測定回路としてΔΣ TDCを検証

- 短時間測定のためのマルチビット ΔΣ TDCを提案

- ➤ 3bit で動作確認

- ▶ 短時間で細かく測定できることを確認(テスト時間短縮可)

- 遅延誤差により測定誤差が生じる

- エレメントローテーション回路を適用した3bit ΔΣ TDCを提案・動作を確認

- > 線形性を改善可能

- ・ 2ステップ変換方式を検討