平成24年2月29日

ETG-11-25

# デルタシグマ型タイムデジタイザ・ アーキテクチャ

上森聡史 石井正道 土井佑太 小林春夫 松浦達治(群馬大学) 小林修(STARC) 新津葵一(群馬大学)

### アウトライン

- 研究背景と目的

- ΔΣ TDC及び提案マルチビットΔΣ TDCの構成・動作

- 出力補正手法

- エレメントローテーション回路による補正

- 自己測定遅延値を用いた自己校正

- MATLABシミュレーションによる検証

- まとめ

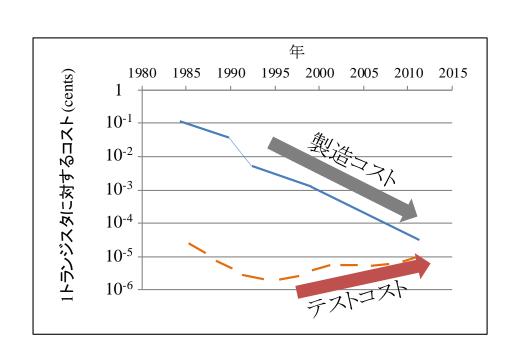

### 研究背景

- 半導体製造コスト: 減少

- テストコスト:増加

- テストコスト∞テスト時間

- 要求事項

- ・低コスト・テスト

- ・高い不良検出率 (テスト精度の向上)

低コスト・高品質テスト技術が重要

### 研究目的

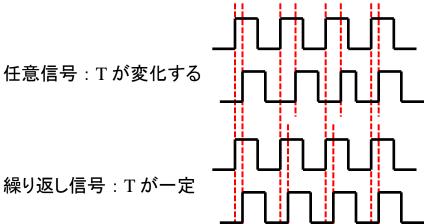

- 2つの繰返しクロック間の時間差テスト

- DDR(Double Data Rate)メモリのデータ クロック間の時間差テスト等

- 組込み可能な測定回路

### 研究目的

● 短時間、高精度でテストする回路の実現

### <u>ΔΣ TDC</u>

- 高時間分解能

- 回路量:小

- 測定時間:長(測定時間≪精度)

- マルチビットΔΣ TDCの提案

- マルチビット化に伴う非線形性 補正手法の提案

### マルチビットにする利点

- シングルビットΔΣ TDC

- 遅延ミスマッチが影響しない

- ・精度が出せる

- ・測定時間が長い

- マルチビットΔΣ TDC

- 測定時間を短縮可能

- 補正技術を適用することで精度が保てる

テスト: 短時間, テスト精度の向上が重要

マルチビット化によりテスト時間が短縮

テストコストを削減可能

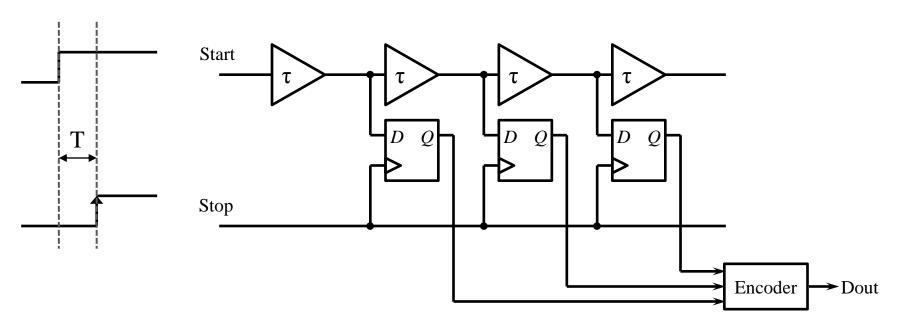

### 従来基本TDC構成

### •Flash型TDC

- ・任意の信号でも1回の入力で計測可

- 回路規模: 大

- ・時間分解能:τで決まる

- ・繰返し信号の計測

- ▶ 何回も入力 ⇒ 高精度で測定

## アウトライン

- 研究背景と目的

- ΔΣ TDC及び提案マルチビットΔΣ TDCの構成・動作

- 出力補正手法

- エレメントローテーション回路による補正

- 自己測定遅延値を用いた自己校正

- MATLABシミュレーションによる検証

- まとめ

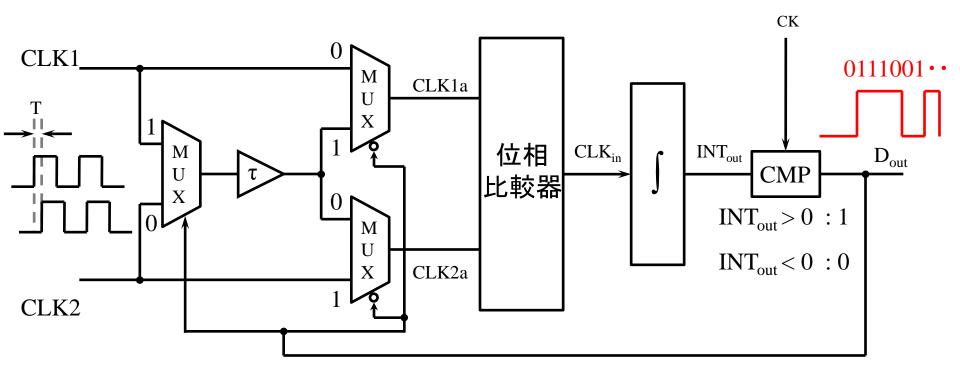

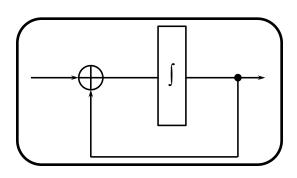

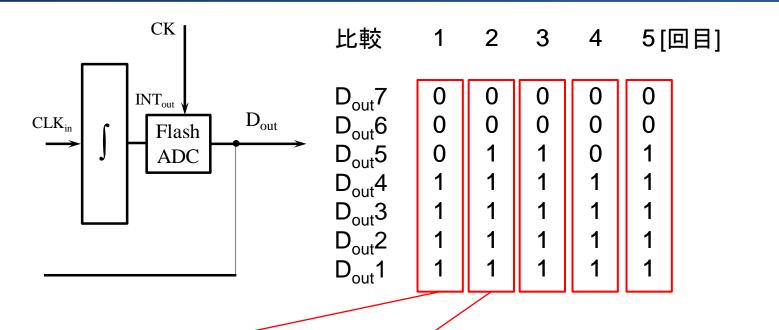

### ΔΣ TDC回路の構成

- CLK1とCLK2間の時間差を計測

- ・出力は時間差Tに比例 ⇒ 1の個数でTを測定可

- D<sub>out</sub>で経路制御

- 測定可能範囲: -τ < T < τ

•積分制御のフィードバック構成

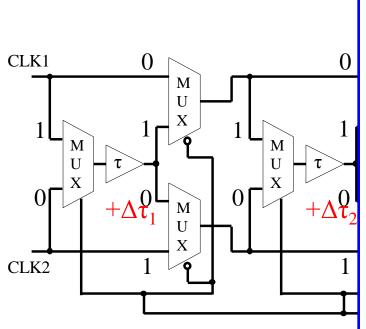

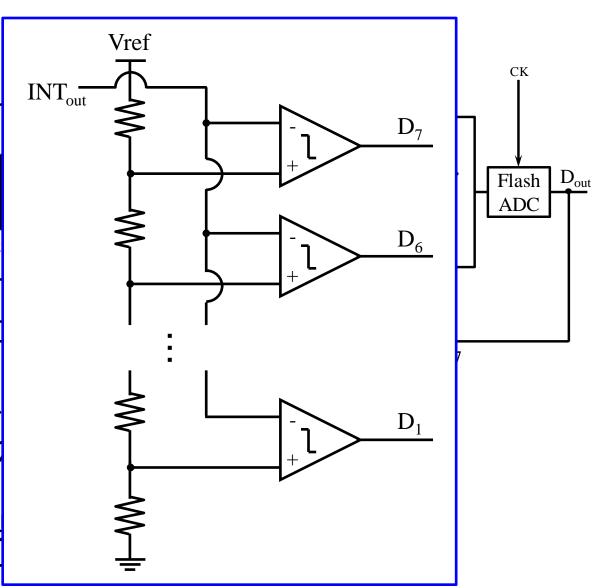

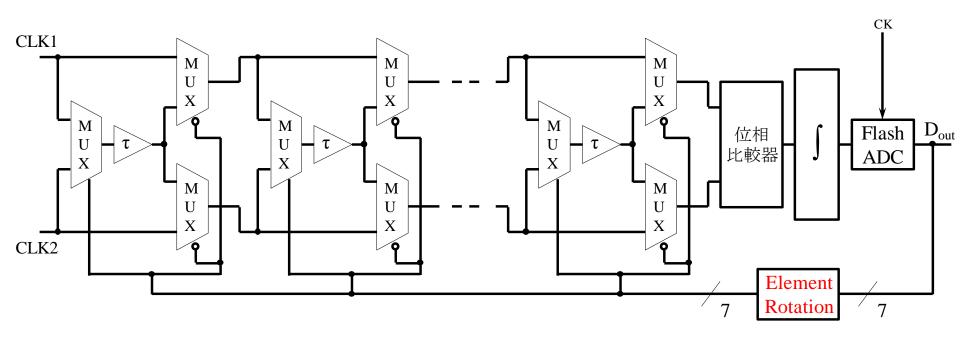

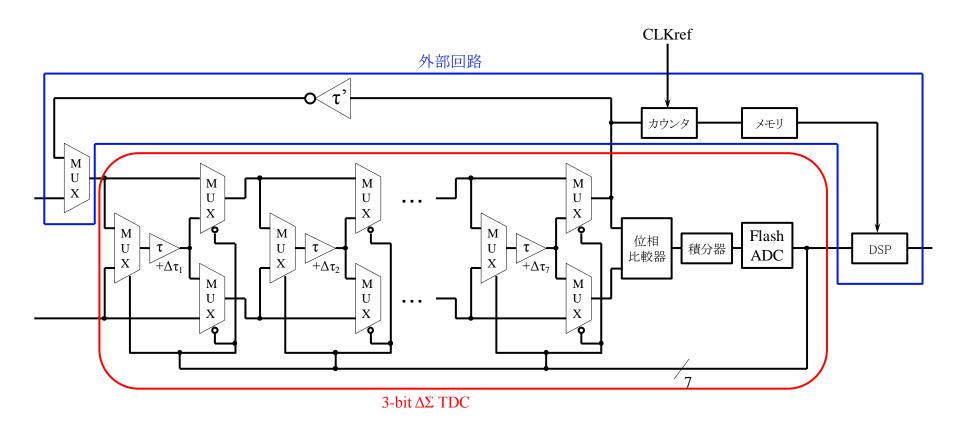

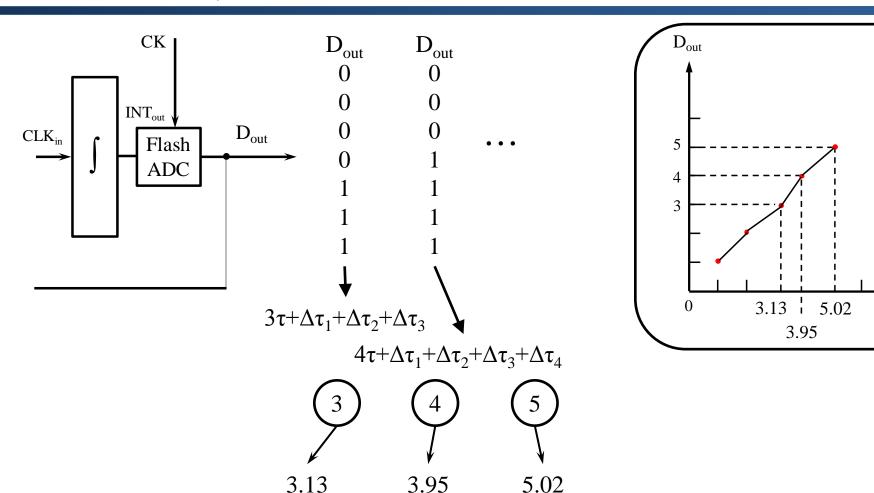

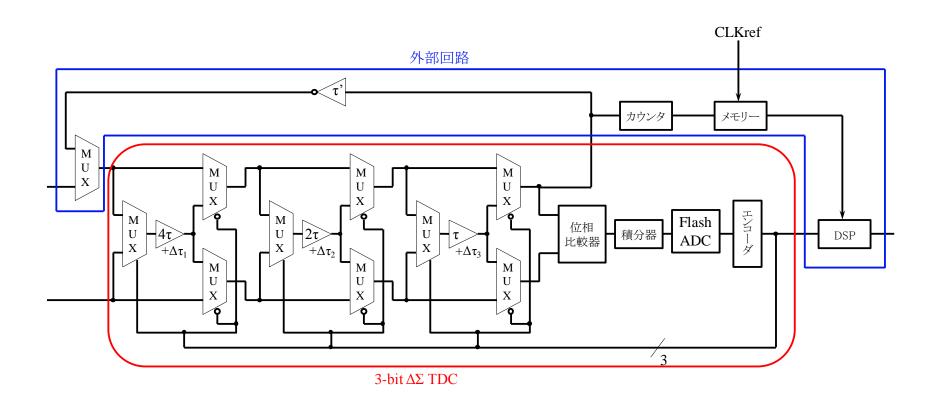

### マルチビットΔΣ TDCの構成

- 遅延セル, マルチプレ

- n-bitの場合: 2<sup>n</sup>-1本の

- 測定可能範囲: -7τ <

- Flash ADCの出力結:

- 遅延セルのミスマッチ

### アウトライン

- 研究背景と目的

- ΔΣ TDC及び提案マルチビットΔΣ TDCの構成・動作

- 出力補正手法

- エレメントローテーション回路による補正

- 自己測定遅延値を用いた自己校正

- MATLABシミュレーションによる検証

- まとめ

# エレメントローテーション回路の適用

- エレメントローテーション回路でFlash ADCの出力をシャッフル

- ・シャッフル後、各MUXへ入力

- ・シャッフルでミスマッチを時間平均 ⇒ ノイズを高周波側へ移す(ノイズシェープ)

- 遅延ばらつきの影響を少なくする

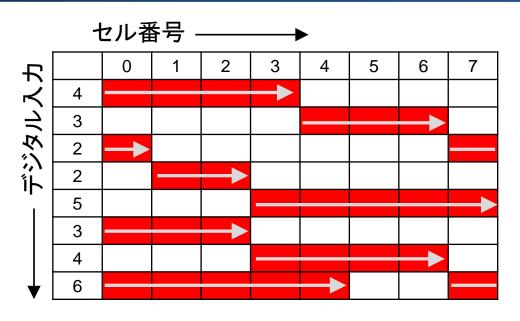

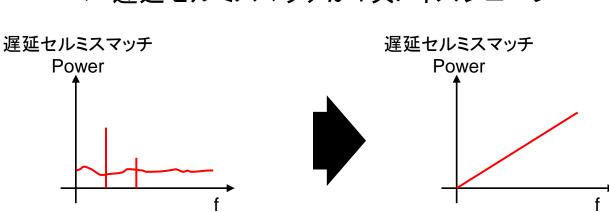

## エレメントローテーションの動作と効果

- •デジタル入力によりシフトする量を制御

- •積分して微分を等価的に実現

- ▶ 遅延セルミスマッチが1次ノイズシェープ

繰り返し信号を測定する

DC成分のノイズが減少 すれば理想に近づく

### アウトライン

- 研究背景と目的

- ΔΣ TDC及び提案マルチビットΔΣ TDCの構成・動作

- 出力補正手法

- エレメントローテーション回路による補正

- 自己測定遅延値を用いた自己校正

- MATLABシミュレーションによる検証

- まとめ

### 自己校正の全体構成

- インバータ、カウンタ、メモリ、マルチプレクサを追加

- 各遅延値を測定しメモリに格納

- クロック間立ち上がり時間差を測定

- ●メモリから遅延データを読み出し出力補正

### 自己測定遅延値を用いた出力補正方法

- 誤差を含む遅延値を考慮して出力することで線形化を目指す

- 細かい遅延値がわかれば精度の向上可能

- ➤ 遅延値の自己測定が必要

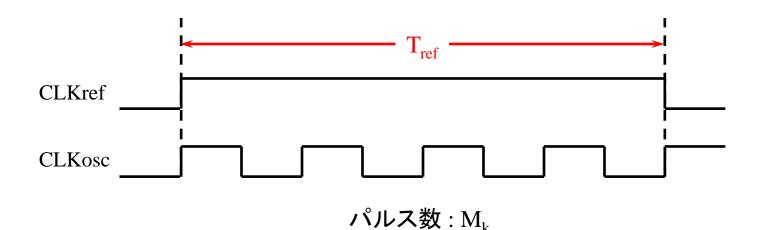

### 遅延時間の自己測定方法

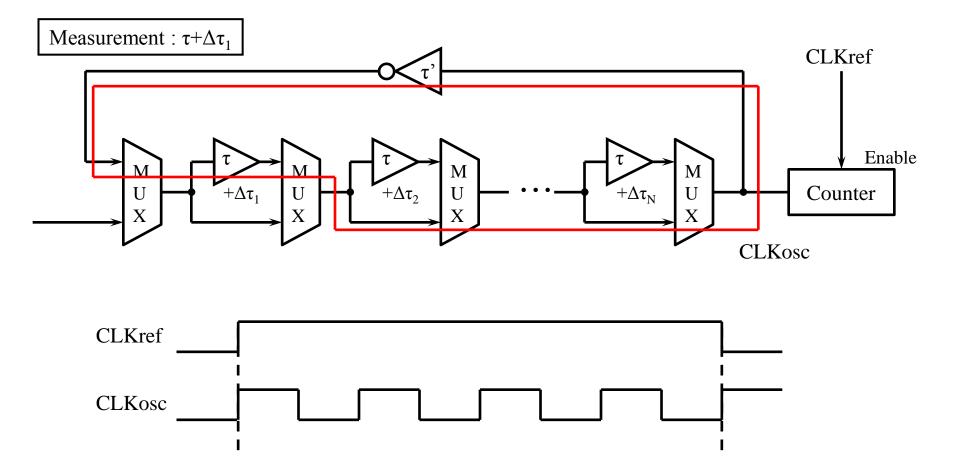

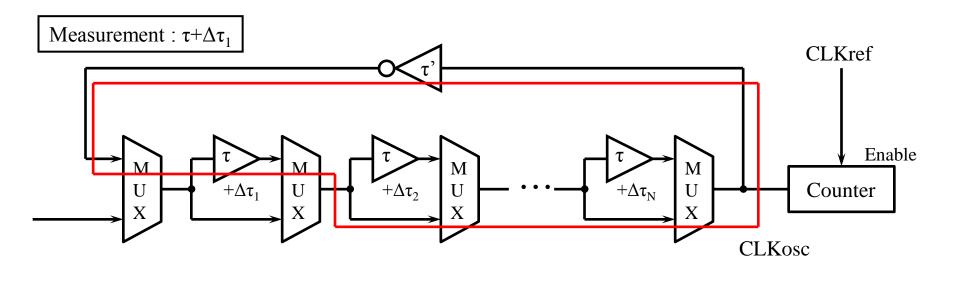

- リング発振回路構成として自己測定

- カウンタでパルス数を数え発振周波数を求める

- デジタル的に測定可能

### 遅延時間の自己測定方法

発振周波数からΔτ₁を計算可能

同様に $\Delta au_{2}$ 、 $\Delta au_{3}$ ,  $\Delta au_{4}$  、 . . . .  $\Delta au_{N}$  を測定可能

- 測定遅延値情報はメモリに格納

- > その情報を基に出力時に補正

### クロック間時間差の算出方法

$$T + \Delta \tau_{1} + \Delta \tau_{2} + \Delta \tau_{3} + \Delta \tau_{4} + \Delta \tau_{5} + \Delta \tau_{6} + \Delta \tau_{7} \\ T_{measure} \frac{1}{3\tau} + \Delta \tau_{1} + \Delta \tau_{2} + \Delta \tau_{3} + \Delta \tau_{4} + \Delta \tau_{5} - \Delta \tau_{6} - \Delta \tau_{7} \\ 3\tau + \Delta \tau_{1} + \Delta \tau_{2} + \Delta \tau_{3} + \Delta \tau_{4} + \Delta \tau_{5} - \Delta \tau_{6} - \Delta \tau_{7}$$

$\tau + \Delta \tau_1 + \Delta \tau_2 + \Delta \tau_3 + \Delta \tau_4 - \Delta \tau_5 - \Delta \tau_6 - \Delta \tau_7$  $3\tau + \Delta\tau_1 + \Delta\tau_2 + \Delta\tau_3 + \Delta\tau_4 + \Delta\tau_5 - \Delta\tau_6 - \Delta\tau_7$

- <del>平均を</del>とった値が最終的な測定値 出力が1ならばτ、0ならば -τ として加算

- 比較1回表別是種を含量ため測定精度が向上

### アウトライン

- 研究背景と目的

- ΔΣ TDC及び提案マルチビットΔΣ TDCの構成・動作

- 出力補正手法

- エレメントローテーション回路による補正

- 自己測定遅延値を用いた自己校正

- MATLABシミュレーションによる検証

- まとめ

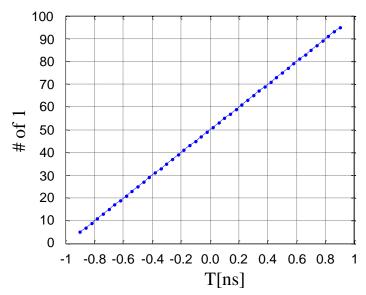

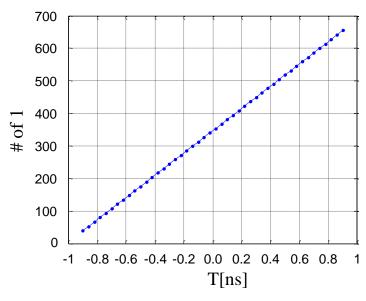

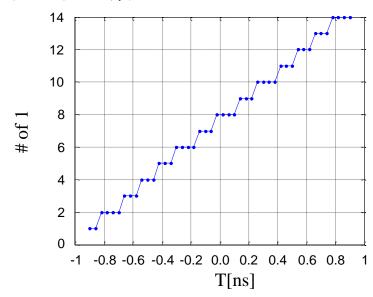

### ΔΣ TDCのシミュレーション結果

#### ● シミュレーション条件

|           | 1-bit ΔΣ TDC                   | 3-bit ΔΣ TDC                   |  |

|-----------|--------------------------------|--------------------------------|--|

| 立上がり時間差T  | -0.9 ~ 0.9[ns] (刻み : 0.04[ns]) | -0.9 ~ 0.9[ns] (刻み : 0.04[ns]) |  |

| 遅延時間 τ    | 1[ns]                          | 0.145[ns]                      |  |

| 出力数(比較回数) | 99点                            | 99点                            |  |

#### ■ 立ち上がり間隔Tに対する1の出力数

- 1の出力数は入力時間差に比例

- > 時間差測定が可能

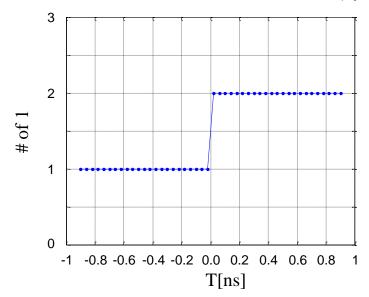

### 測定時間を短縮した場合の検討

#### ● シミュレーション条件

|           | 1-bit ΔΣ TDC                   | 3-bit ΔΣ TDC                   |  |

|-----------|--------------------------------|--------------------------------|--|

| 立上がり時間差T  | -0.9 ~ 0.9[ns] (刻み : 0.04[ns]) | -0.9 ~ 0.9[ns] (刻み : 0.04[ns]) |  |

| 遅延時間 τ    | 1[ns]                          | 0.145[ns]                      |  |

| 出力数(比較回数) | 2点                             | 2点                             |  |

#### ■ 立ち上がり間隔Tに対する1の出力数

✓マルチビット化することで短時間で細かく測定可能 ⇒ 低コスト・テストの実現

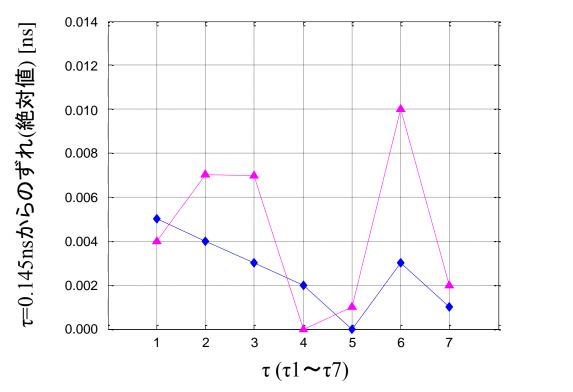

### 遅延ばらつきの影響の検証

•遅延ばらつき: ガウス分布でランダムに生成 最大でτ=0.145ns の±10%程度の誤差とした

● シミュレーション時に生成した遅延パラメータ

◆:条件①

▲:条件②

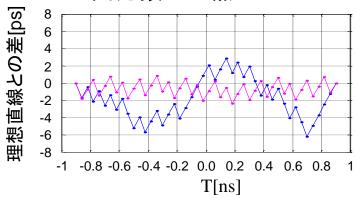

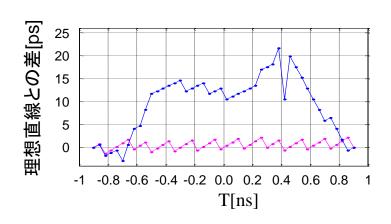

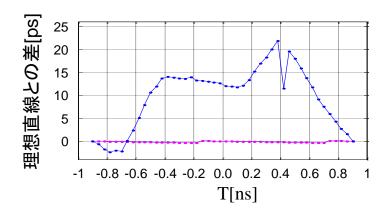

### エレメントローテーションの効果検証

•3-bit  $\Delta\Sigma$  TDC (遅延時間:  $\tau$ =0.145ns+ $\Delta\tau_N$ )

#### 条件①

● 出力数:99点

● 出力数:599点

✓遅延ミスマッチの影響が軽減 ➤ 出力の線形性を改善

#### 条件②

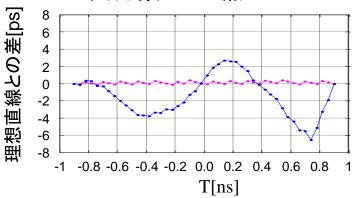

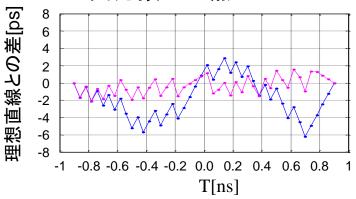

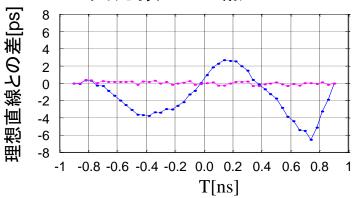

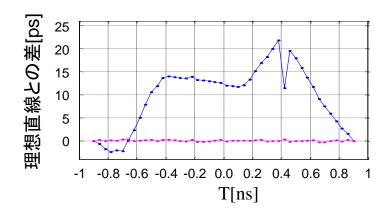

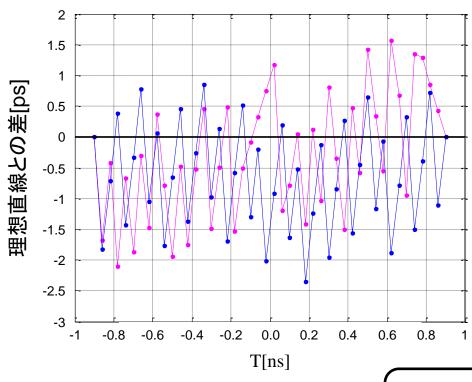

### 測定済遅延値による自己校正の検証

•3-bit  $\Delta\Sigma$  TDC (遅延時間:  $\tau$ =0.145ns+ $\Delta\tau_N$ )

#### 条件①

● 出力数:99点

● 出力数:599点

✓遅延ミスマッチの影響が軽減 ➤ 出力の線形性を改善

条件②

### アウトライン

- 研究背景と目的

- ΔΣ TDC及び提案マルチビットΔΣ TDCの構成・動作

- 出力補正手法

- エレメントローテーション回路による補正

- 自己測定遅延値を用いた自己校正

- MATLABシミュレーションによる検証

- まとめ

# 回路性能のまとめ

|       | Flash<br>TDC | 1-bit ΔΣ<br>TDC | マルチビット<br>ΔΣ TDC<br>(without<br>correction) | マルチビット<br>ΔΣ TDC<br>(with<br>correction) |

|-------|--------------|-----------------|---------------------------------------------|------------------------------------------|

| 回路量   | ×            | 0               | 0                                           | 0                                        |

| 時間分解能 | ×            | 0               | 0                                           | 0                                        |

| 精度    | Δ            | 0               | ×                                           | 0                                        |

| 測定時間  | 0            | ×               | 0                                           | 0                                        |

### まとめ

- 時間差測定回路としてΔΣ TDCを検証

- マルチビット ΔΣ TDCを提案

- ➤ 短時間で細かく測定可能 (テスト時間短縮可)

- > 遅延誤差により測定誤差が生じる

- 2つの補正手法を提案

- エレメントローテーション回路による補正

- 測定済み遅延値情報を用いた自己校正

- ▶線形性を改善可能

短時間・高精度測定可能な回路を実現

# 補足資料

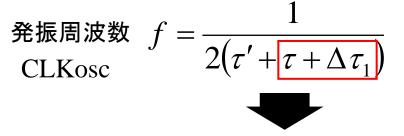

## パルス数からの遅延値計算方法

$$f_{OSC}^{k} \approx \frac{M_{k}}{T_{ref}} = \frac{1}{2(\tau' + \tau_{k})}$$

$$\tau_{k} = \tau + \Delta \tau_{k}$$

$$f_{OSC}^{0} \approx \frac{M_{0}}{T_{ref}} = \frac{1}{2\tau'}$$

$$\tau_k = \frac{1}{2} \left( \frac{1}{f_k} - \frac{1}{f_0} \right) \approx \frac{T_{ref}}{2} \left( \frac{1}{M_k} - \frac{1}{M_0} \right)$$

$$k=1, 2, ..., 2^{N}-1$$

## 各遅延値の測定時間を短縮する構成

- 各遅延値に重みをもたせる

- 測定にはN-bit で Nステップかかる

### 理想状態と補正後の線形性比較

•3-bit ΔΣ TDC (遅延時間(理想状態): τ=0.145ns)

### 出力数99点において

・ 理想状態 :±2 ps 以内の差

補正後 : ±2.5 ps 以内の差

> 線形性がほぼ理想状態まで改善

ΔΣ TDC (with Element Rotation)ΔΣ TDC (with Self-Calibration)