# TVチューナ用完全ディジタルPLL回路

<u>○湯本 哲也</u>, <u>村上 健</u>,

壇 徹。 高橋 伸夫。 内藤 智洋。 北村 真一。 坂田 浩司。

小林 春夫 高井 伸和 新津 葵一

<u>群馬大学大学院 工学研究科</u>1

三洋半導体 株式会社。

- 研究背景と目的

- 従来の完全ディジタルPLLの基本動作

- 提案するTVチューナ用ADPLL回路設計技術

- シミュレーションによる検証

- チップ測定結果

- まとめと今後の課題

- 研究背景と目的

- 従来の完全ディジタルPLLの基本動作

- 提案するTVチューナ用ADPLL回路設計技術

- シミュレーションによる検証

- チップ測定結果

- まとめと今後の課題

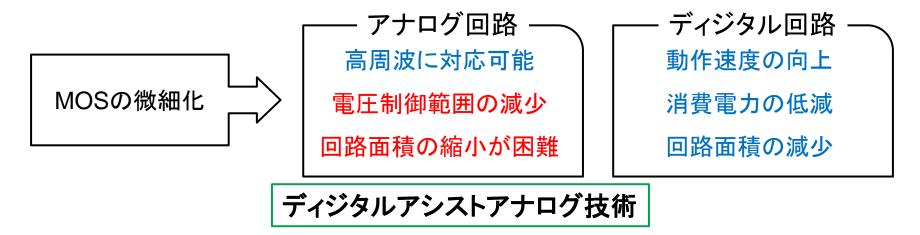

## 研究背景

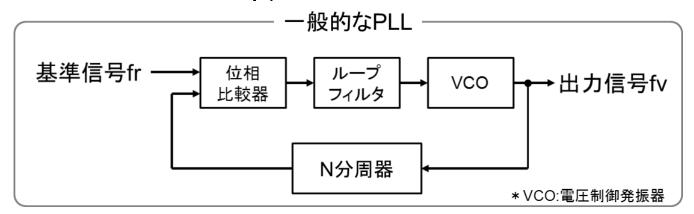

## ■PLL(Phase Locked Loop)

分周比Nを制御することで任意の出力が得られる fv = N×fr

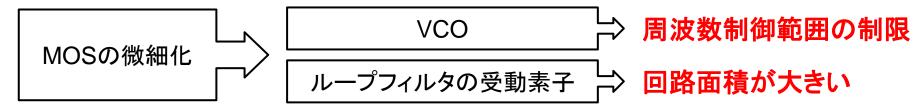

## 研究背景•目的

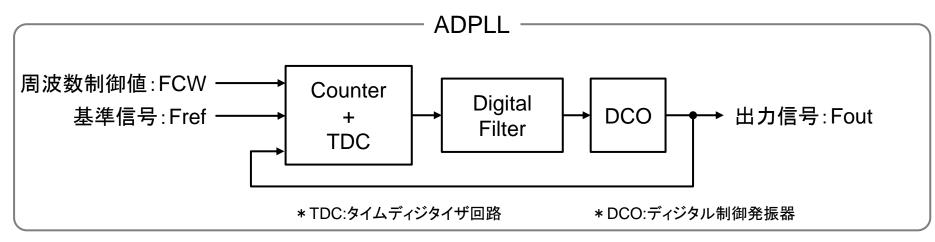

## ■ ADPLL (All Digital PLL)

### PLL回路をほぼ全てディジタル回路で構成

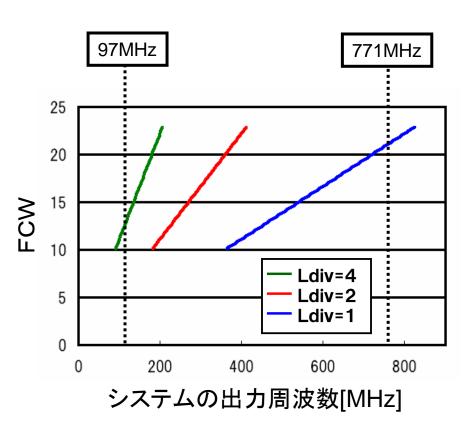

FCWを制御することで任意の出力が得られる Fout = FCW Fref

### 研究目的:TVチューナを目的とした広帯域なADPLLの開発

目標仕様

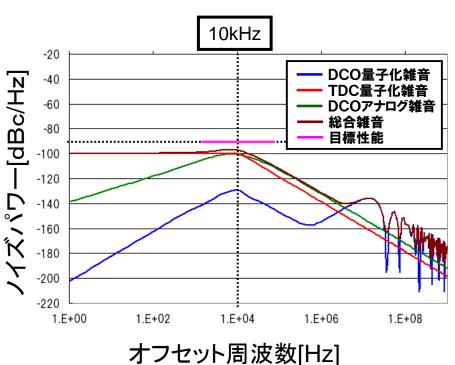

出力周波数範囲 97M~771MHz 位相雑音 -90dBc/Hz @10kHz 研究課題

- •低位相雑音化

- •広帯域動作化

- ・チューニング時間短縮化

- 研究背景と目的

- 従来の完全ディジタルPLLの基本動作

- 提案するTVチューナ用ADPLL回路設計技術

- シミュレーションによる検証

- チップ測定結果

- まとめと今後の課題

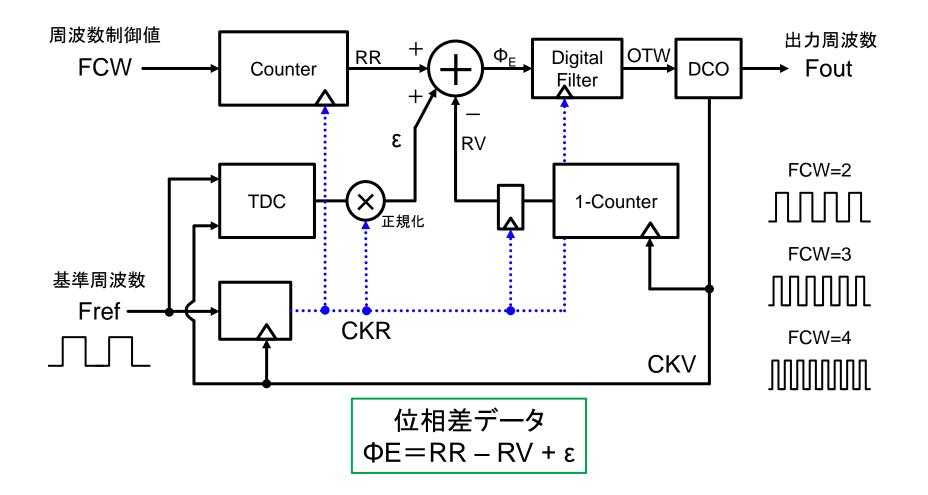

## ADPLLの主要なパラメータ

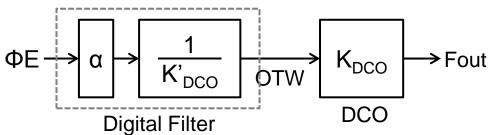

ディジタルフィルタ+DCOの伝達関数モデル

ループゲイン:α システムの応答を決定 収束精度 収束時間 トレードオフ DCOゲイン: K<sub>DCO</sub>

発振周波数に依存した非線形なパラメータ システムの伝達関数に影響

ADPLLのディジタル的な性質 αを切り替えることが可能

システム内でK<sub>DCO</sub>を推定 K'DCO=K<sub>DCO</sub>であればキャンセル可能

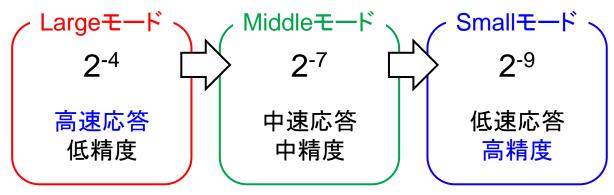

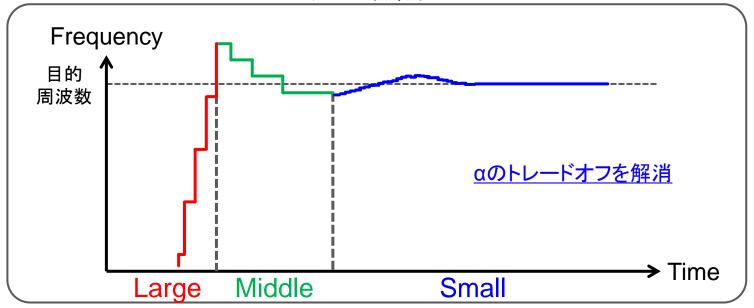

### ループゲインαの段階的シフト構成

\*Smallモードのみ2次フィルタ+ΔΣ使用

#### システムの収束イメージ

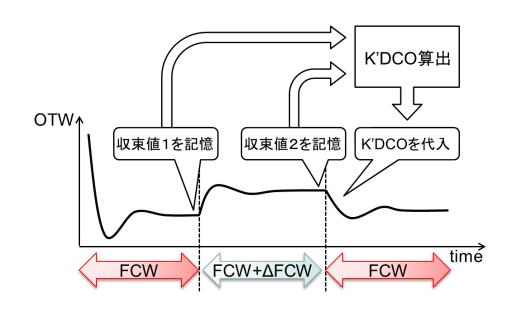

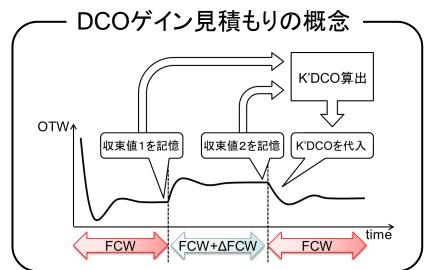

### DCOゲインの定義式

$$K_{DCO} = \frac{\Delta f v}{\Delta OTW} = \frac{\Delta FCW * Fref}{OTW2 - OTW1}$$

ADPLLの制御式  $\Delta f v = \Delta FCW * Fref$

### 見積もりフロー

FCWで収束値1を記憶

FCW+△FCWで収束値2を記憶

K'DCOを演算で算出

$$K'_{DCO} = \frac{\Delta FCW * Fref}{OTW2 - OTW1}$$

K'DCOをシステムに代入

システム内のパラメータを用いて自己校正を実現

- 研究背景と目的

- 従来の完全ディジタルPLLの基本動作

- 提案するTVチューナ用ADPLL回路設計技術

- シミュレーションによる検証

- チップ測定結果

- まとめと今後の課題

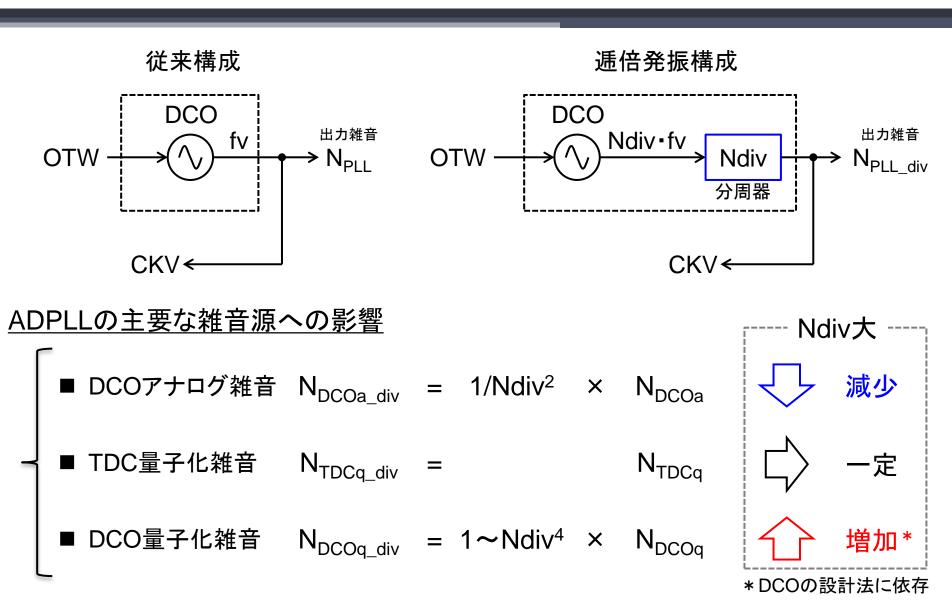

### 課題と提案手法

1. 位相雑音特性

DCOアナログ雑音の影響

位相雑音特性の劣化

逓倍発振・分周構成による雑音低減化

2. 周波数特性

DCOの発振周波数の可変限界

ADPLLの発振周波数の制限

可変分周回路・複数のDCO切り替えによる広帯域化

3. チューニング時間

DCOゲインの見積もり

長いチューニング時間

Middleモードで見積もりチューニング時間を短縮する

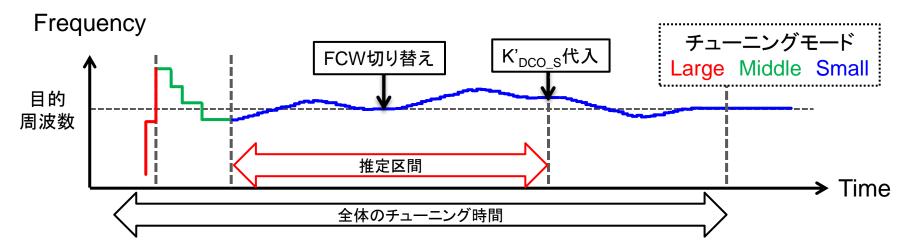

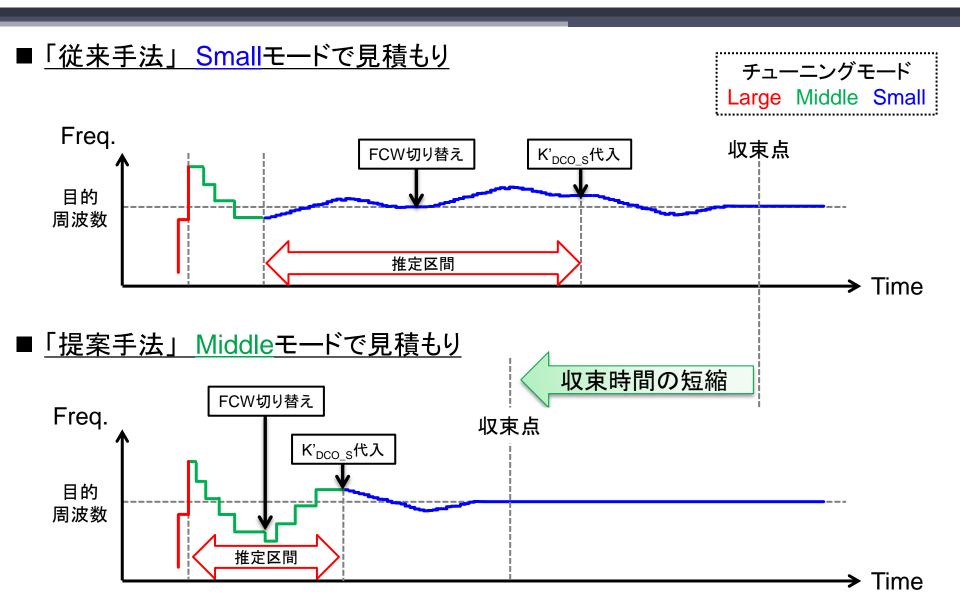

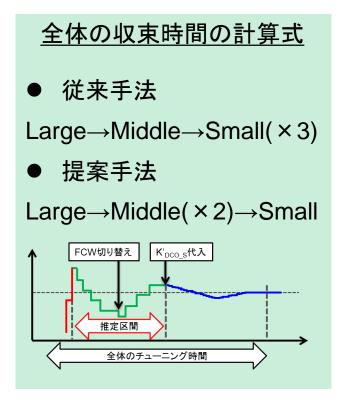

## チューニング時間短縮化 一従来手法一

最も精度を要求されるSmallモードのDCOゲインK'<sub>DCO\_S</sub>が重要 K'<sub>DCO\_S</sub>はSmallモードで見積もる必要がある

Smallモードを3回行う必要がある (推定に2回、K'DCO代入後に1回)

高精度 長い収束時間

収束時間の短い Middleモードに着目

# チューニング時間短縮化 ー提案手法ー

MiddleモードでSmallモードのK'DCOを求められればチューニング時間の大幅な短縮が可能

提案方法の課題

Middleモード K'<sub>DCO M</sub>

求められる値

Smallモード  $K'_{DCO\_S}$

求めたい値

DCOゲインの計算式

$$K_{DCO} = -2\pi^2 * \Delta C_{1LSB} * L * fv^3$$

Middle  $\pm - + \Delta C_{11SB} = 6.25 fF$

Small<sup>±</sup>−F∆C<sub>1LSB</sub>=250aF

K'<sub>DCO\_M</sub>からK'<sub>DCO S</sub>への変換方法

DCOゲインの比 バラクタ分解能の比

$\mathsf{K}_{\mathsf{DCO\_S}} : \mathsf{K}_{\mathsf{DCO\_M}} = \Delta \mathsf{C}_{\mathsf{1LSB\_S}} : \Delta \mathsf{C}_{\mathsf{1LSB\_M}} \qquad \square \searrow \mathsf{K'}_{\mathsf{DCO\_S}} = \frac{\Delta \mathcal{C}_{\mathsf{1LSB\_S}}}{\Delta \mathcal{C}_{\mathsf{1LSB\_M}}} * \mathsf{K}_{\mathsf{DCO\_M}}$

提案したMiddleモードによるK'DCO\_Sの推定を実現

- 研究背景と目的

- 従来の完全ディジタルPLLの基本動作

- 提案するTVチューナ用ADPLL回路設計技術

- シミュレーションによる検証

- チップ測定結果

- まとめと今後の課題

# シミュレーション条件

### MATLAB Simulinkを使用してシステムを解析

| 主なパラメータ           | 設定値                                                                                                         |  |

|-------------------|-------------------------------------------------------------------------------------------------------------|--|

| Fref              | 36.57142857MHz(1/7 × 2^8MHz)                                                                                |  |

| TDC時間分解能          | 68psec                                                                                                      |  |

| ビット幅              | Wi=8bit, Wf=7bit                                                                                            |  |

| ループゲイン            | Large $\alpha_L$ = $2^{-4}$ Middle $\alpha_M$ = $2^{-7}$ Small $\alpha_S$ = $2^{-9}$ , $\rho_S$ = $2^{-19}$ |  |

| K' <sub>DCO</sub> | K' <sub>DCO_L</sub> =20MHz<br>K' <sub>DCO_M</sub> =1.5MHz                                                   |  |

| DCOバラクタ分解能        | $\Delta C_{1LSB\_L}$ =105fF<br>$\Delta C_{1LSB\_M}$ =6.25fF<br>$\Delta C_{1LSB\_S}$ =250aF                  |  |

| ΔFCW              | 0.05                                                                                                        |  |

| MASH ΔΣ構成         | 3次                                                                                                          |  |

| FCW               | 13.625                                                                                                      |  |

| シミュレーション時間        | 350µsec                                                                                                     |  |

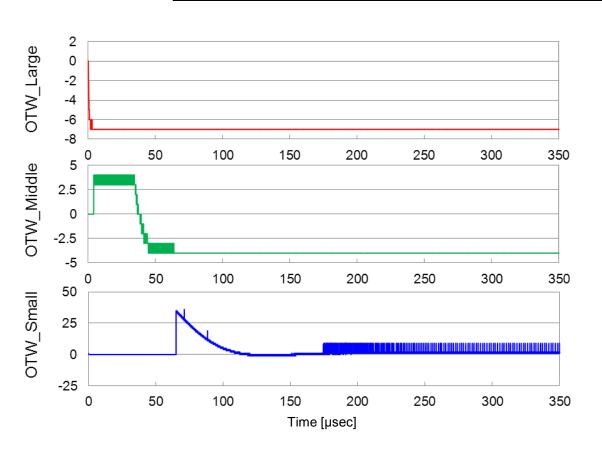

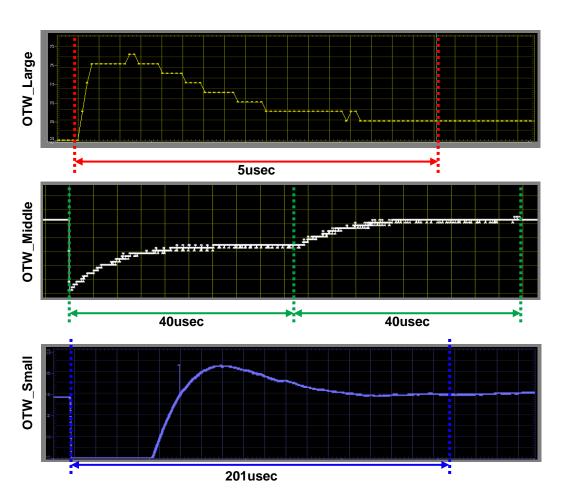

## チューニング時間の検証

### 各モードのOTWの収束時間から全体の収束時間を比較する

チューニング時間の比較

従来手法: 3u + 30u + 205u×3 ≧ 600usec

提案手法: 3u + 30u×2 + 205u ≒ 268usec

Middleモード見積もりによる チューニング時間の短縮を確認

- 研究背景と目的

- 従来の完全ディジタルPLLの基本動作

- 提案するTVチューナ用ADPLL回路設計技術

- シミュレーションによる検証

- チップ測定結果

- まとめと今後の課題

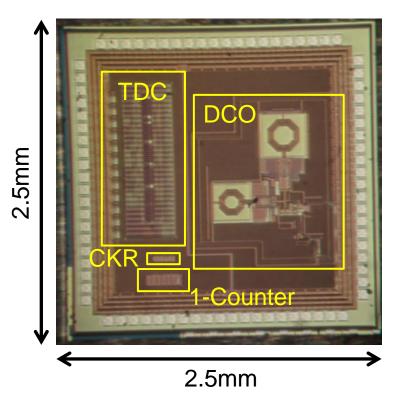

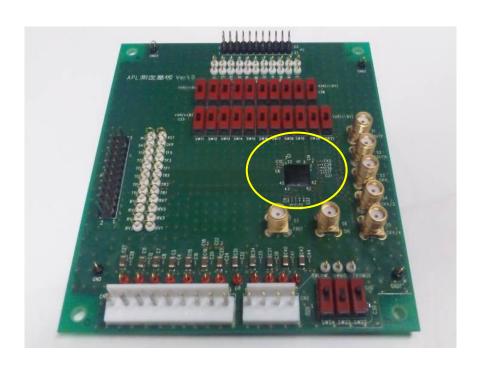

# 試作したチップと測定基板

複雑なディジタル部を1チップに実装することは困難

FPGA(Field-Programmable Gate Array)とチップを併用

試作チップ TSMC 180nm CMOSプロセス

### 測定用基板

# チューニング動作 測定結果

### 各モードのOTWの収束時間から全体の収束時間を比較する

全体の収束時間の計算式 ● 提案手法

Large→Middle(×2)→Small

FCW切り替え K'DCO\_S代入 推定区間 全体のチューニング時間

シミュレーション: 3u + 30u×2 + 205u ≒ 268usec

測定結果: 5u + 40u×2 + 201u ≒ 286usec

同様の収束時間 実装で効果を確認

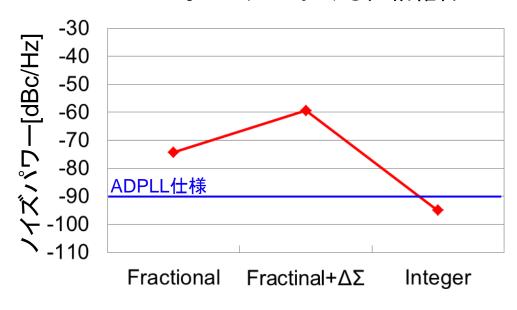

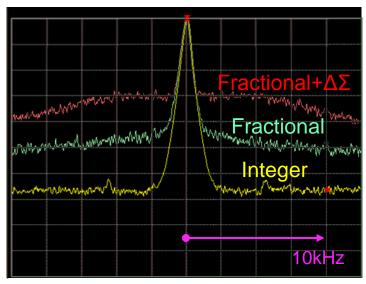

## 位相雜音 測定結果

| 測定項目          | 詳細                           |  |

|---------------|------------------------------|--|

| Fractional    | FCW=13.685~17.375(8個の平均)     |  |

| Fractional+ΔΣ | 上記と同様のFCW+ΔΣ制御               |  |

| Integer       | FCW=14, 15, 16, 17(整数値4個の平均) |  |

#### 10kHzオフセットにおける位相雑音

### スペクトルアナライザによる測定波形

\* Span=25kHz, RBW=300Hz

Integer: 目標仕様を達成

Fractional: 量子化雑音が支配的 Fractional+ $\Delta\Sigma$ :  $\Delta\Sigma$ による雑音が支配的

- 研究背景と目的

- 設計した完全ディジタルPLLの基本動作

- 提案するTVチューナ用ADPLL回路設計技術

- シミュレーションによる検証

- チップ測定結果

- まとめと今後の課題

- 新しいDCOゲイン見積もり技術を提案

- シミュレーションよる検証を行い、仕様を満たすことを確認

- チップへの実装を行い動作を確認、雑音も一部仕様を達成

|                    | シミュレーション結果 | 測定結果               |

|--------------------|------------|--------------------|

| 周波数範囲 [MHz]        | 97~771     | 88~599             |

| 収束時間 [usec]        | 268        | 285                |

| 位相雑音[dBc/Hz]@10kHz | -90        | -74.3 (fractional) |

### 今後の課題

- 3個のDCOを用いた周波数範囲の確保

- ADPLLの1チップ化を行い、さらに性能の向上を目指す

- さらに微細なプロセスへの移行の検討

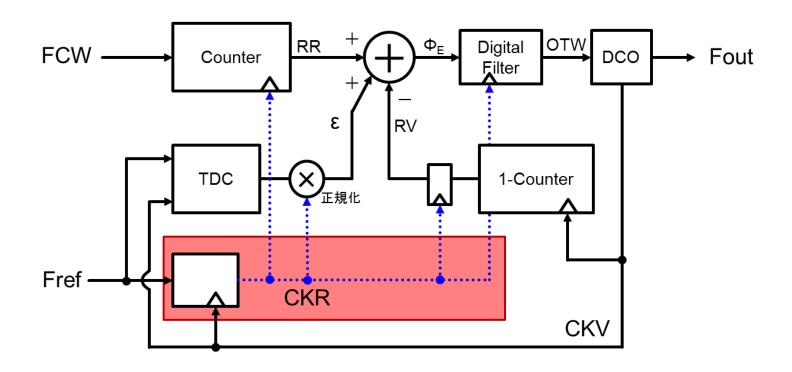

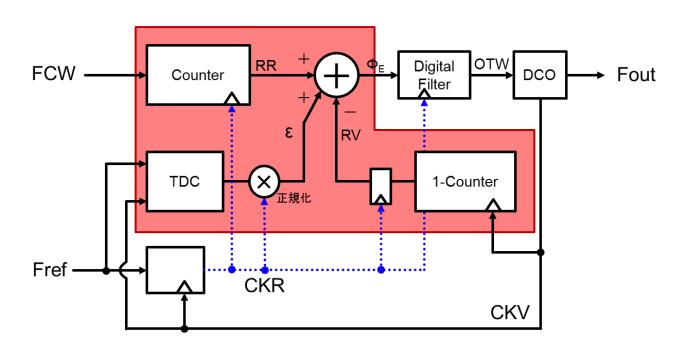

### CKR:システム同期クロック

- 全ての演算及び制御はCKRのタイミングで行われる

- FrefとCKVの位相を関連付ける

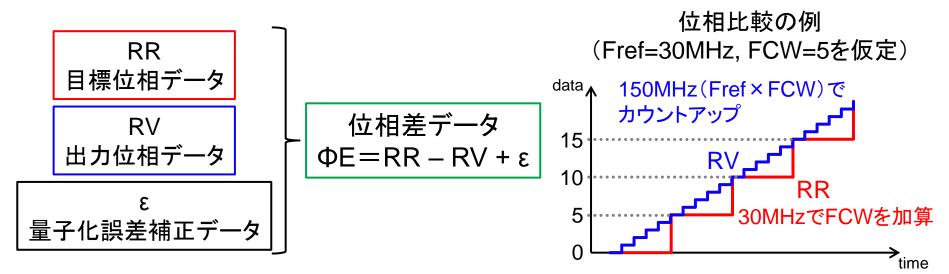

## ADPLLの基本動作 一位相差検出ー

## 1. 低位相雑音化技術

Ndivの設定、DCOの設計を適切に行うことで雑音を小さくすることができる

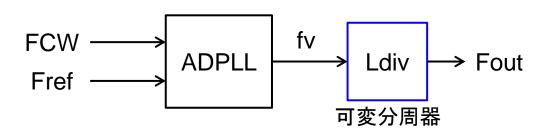

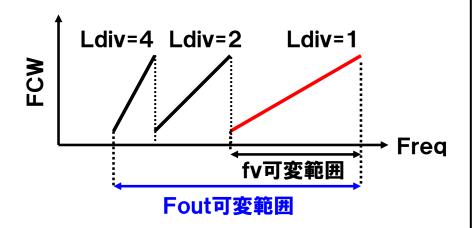

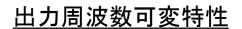

## 2. 広帯域化技術 一可変分周回路一

### 可変分周回路の付加

出力の特性式 Fout = fv / Ldiv

周波数の可変域を拡張

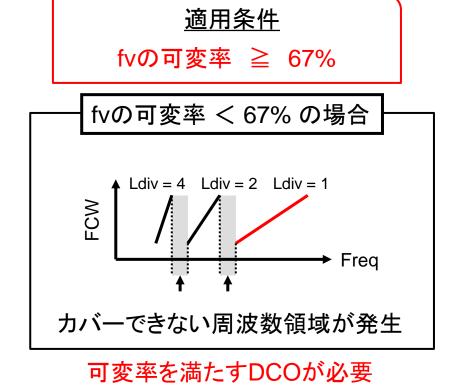

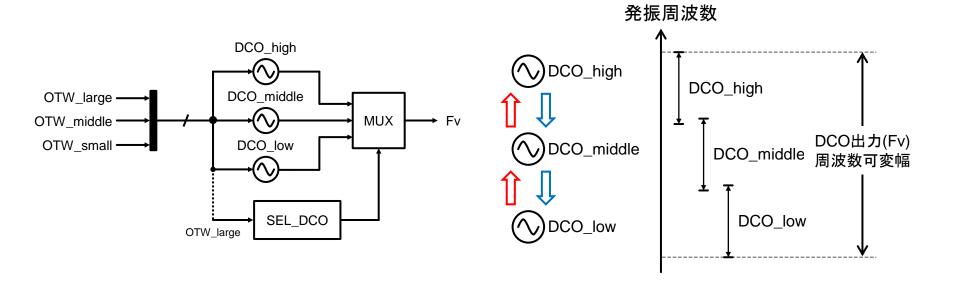

## 2. 広帯域化技術 - 複数のDCO-

fvの可変率 ≧ 67% を満たすDCOが必要

単体の可変帯域は限られる

DCO回路を複数用いて可変率を達成

### 切り替え構成ブロック図

### 切り替え動作とカバ一範囲

3個のDCO+可変分周回路を用いて目標仕様の帯域を確保

出力位相雑音特性

共に目標性能を満たすことを確認