ETT-11-7 遅延デジタルフィルタの分散型積和 演算回路を用いたFPGA実装の検討

> 易 茹\* 立岩武徳(群馬大学) 浅見幸司(株式会社アドバンテスト) 小林春夫(群馬大学)

## 発表内容

- ・ 研究の背景・目的

- 分散型積和演算回路

- ・実装の検討

- まとめ・今後の課題

## 発表内容

- ・研究の背景・目的

- 分散型積和演算回路

- ・ 実装の検討

- まとめ・今後の課題

# 研究の背景・目的

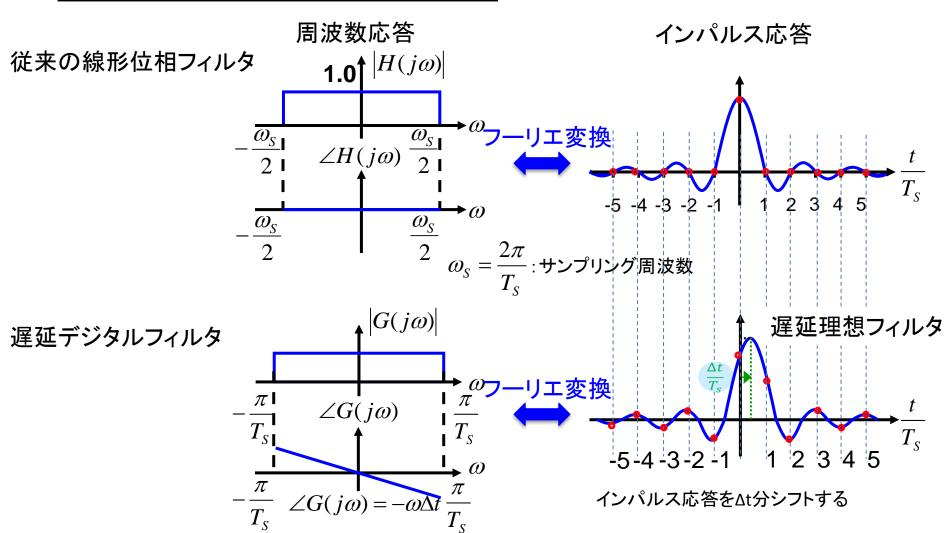

LSIテスタ・電子計測器では <u>タイミングスキューの影響</u>が問題

線形位相を保つ

従来の線形位相フィルタ

群遅延:一定(T<sub>s</sub>/2)

遅延デジタルフィルタ

群遅延:任意(Δt)

# 研究の背景・目的

振幅特性は変化しない、位相特性はAt分傾く

# 研究の背景・目的

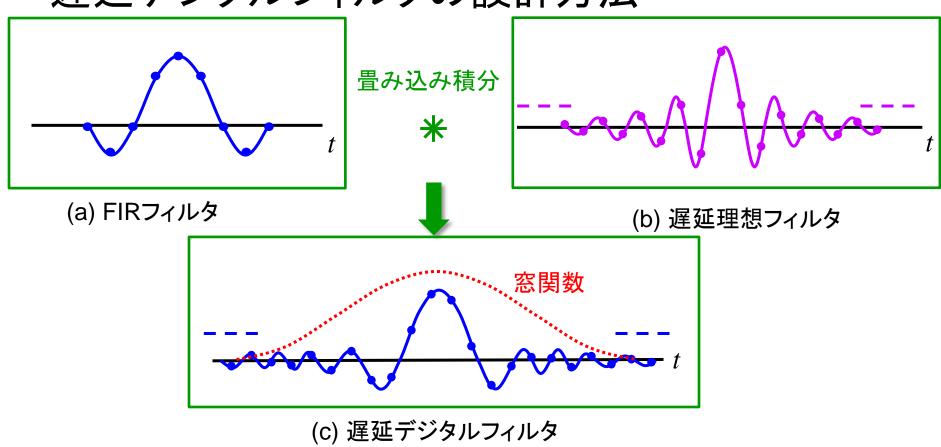

### 遅延デジタルフィルタの設計方法

Koji Asami, Hiroyuki Miyajima, Tsuyoshi Kurosawa, Takenori Tateiwa, Haruo Kobayashi, "Timing Skew Compensation Technique using Digital Filter with Novel Linear Phase Condition," IEEE International Test Conference, Austin, TX (Nov.2010)

## 発表内容

- 研究の背景・目的

- 分散型積和演算回路

- 実装の検討

- まとめ・今後の課題

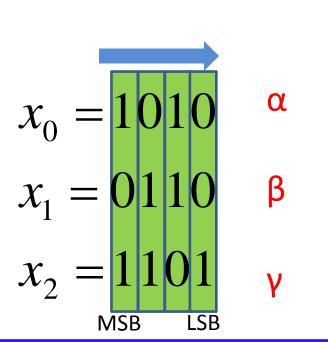

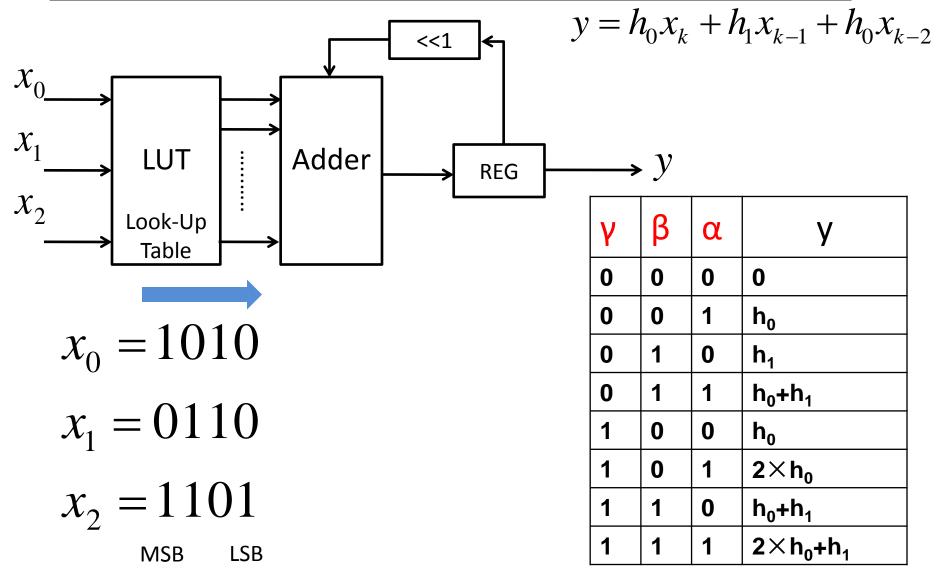

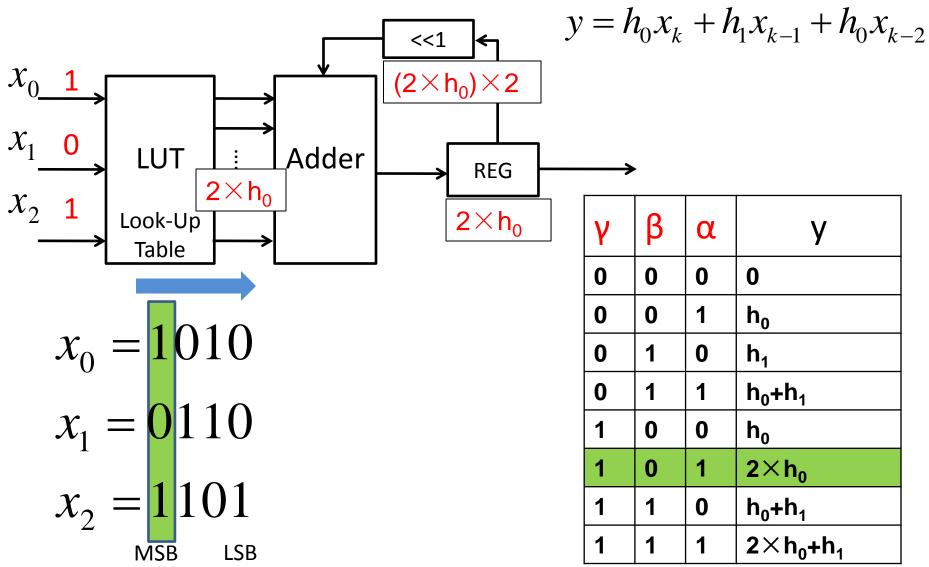

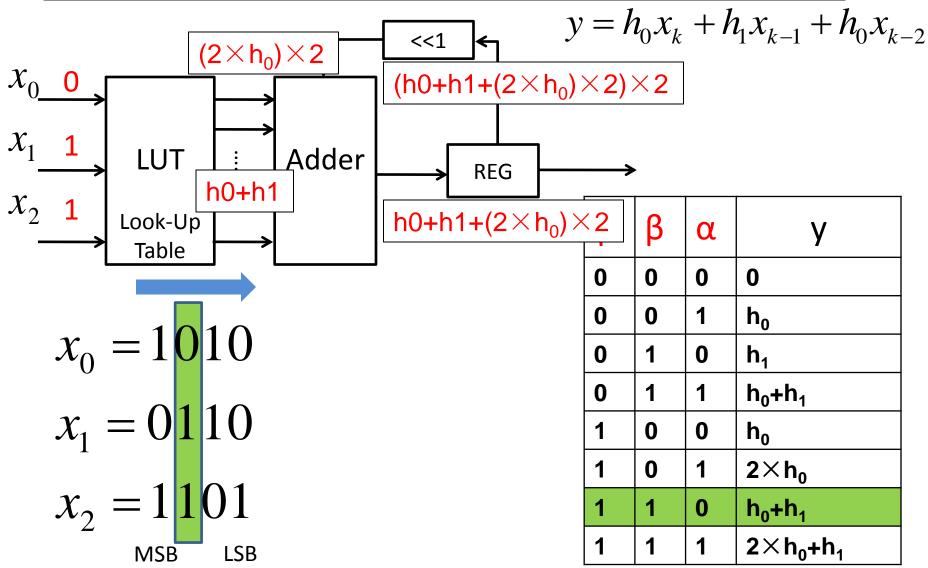

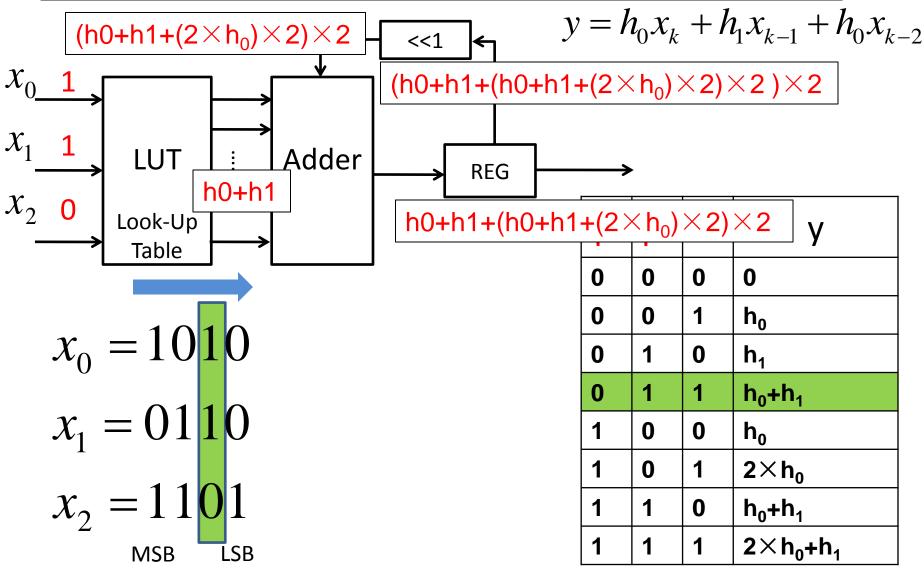

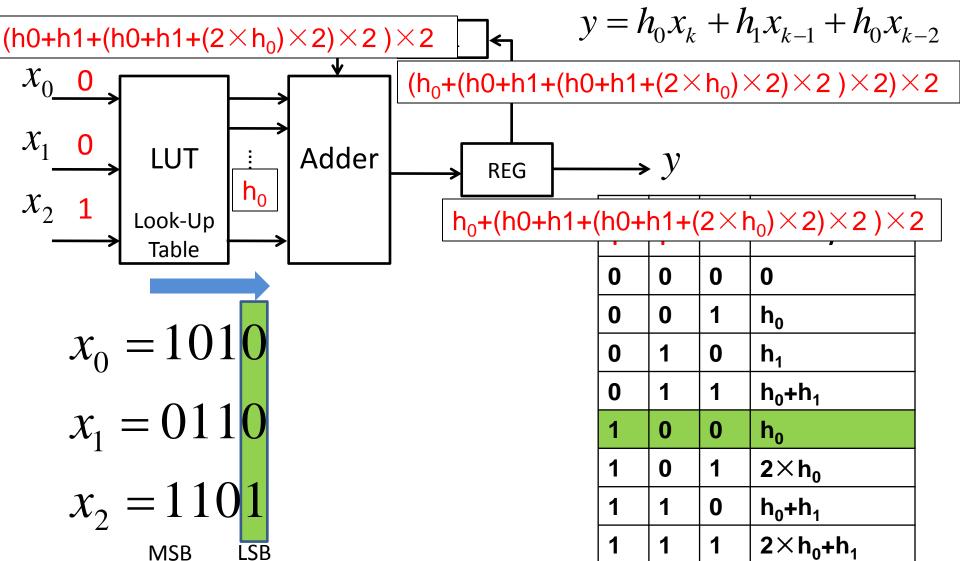

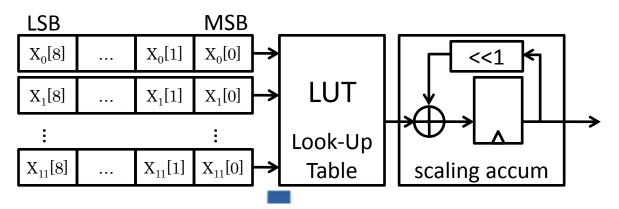

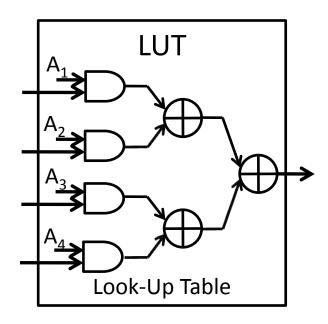

# 分散型積和演算回路

• 分散型積和演算回路(Distributed Arithmetic) 定係数の積和演算をLUT(Look-Up Table)とビットシフト と加算器で効率的に実現する

乗算器を使用しない

小規模回路•低消費電力

# 分散型積和演算回路の式

$$y = -\sum_{k=1}^{K} A_k \cdot (b_{k0}) + \sum_{n=1}^{N-1} \left[ \sum_{k=1}^{K} A_k \cdot b_{kn} \right] 2^{-n}$$

項目Kの係数ベクトルA=[A<sub>1</sub>, A<sub>2</sub>,..., A<sub>K</sub>]

項目KのNビット変数ベクトルx=[x<sub>1</sub>, x<sub>2</sub>,..., x<sub>K</sub>]

xを固定小数点形の2の補数表示で  $x_k = -b_{k0} + \sum_{n=1}^{N-1} b_{kn} 2^{-n}$  と表される。ただし $b_{k0}$ は符号ビットである。 例:

$$0.375_{(10)} \longleftrightarrow 0.0011_{(2)}$$

$$x_k = -0 + 0 \times 2^{-1} + 1 \times 2^{-2} + 1 \times 2^{-3} = 0.25 + 0.125 = 0.375$$

$$y = h_0 x_k + h_1 x_{k-1} + h_0 x_{k-2}$$

#### Look-Up Table

| γ | β | α | У                                |

|---|---|---|----------------------------------|

| 0 | 0 | 0 | 0                                |

| 0 | 0 | 1 | h <sub>o</sub>                   |

| 0 | 1 | 0 | h <sub>1</sub>                   |

| 0 | 1 | 1 | h <sub>0</sub> +h <sub>1</sub>   |

| 1 | 0 | 0 | h <sub>0</sub>                   |

| 1 | 0 | 1 | $2 \times h_0$                   |

| 1 | 1 | 0 | h <sub>0</sub> +h <sub>1</sub>   |

| 1 | 1 | 1 | 2×h <sub>0</sub> +h <sub>1</sub> |

# 発表内容

- 研究の背景・目的

- 分散型積和演算回路

- ・実装の検討

- まとめ・今後の課題

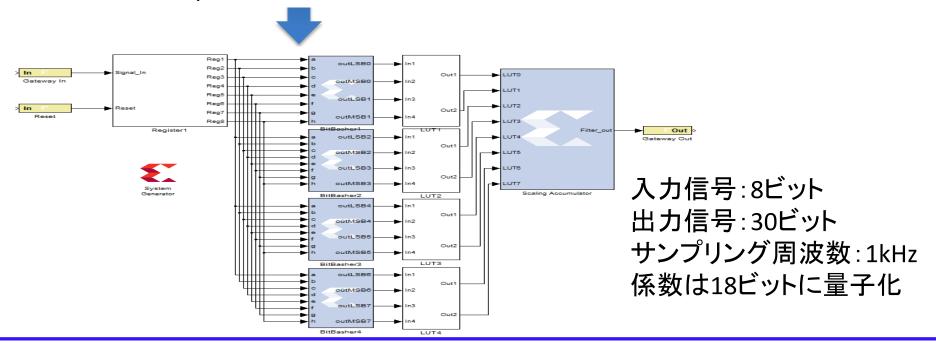

## 実装のためのSimlinkモデルの検討

MATLABおよびSystem GeneratorでSimlinkモデルを作成

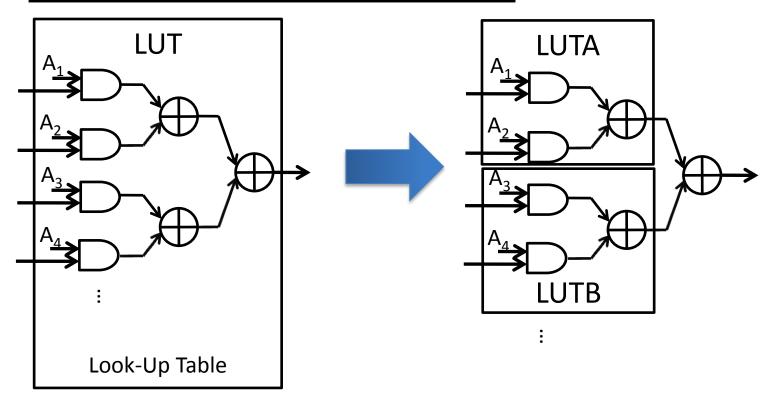

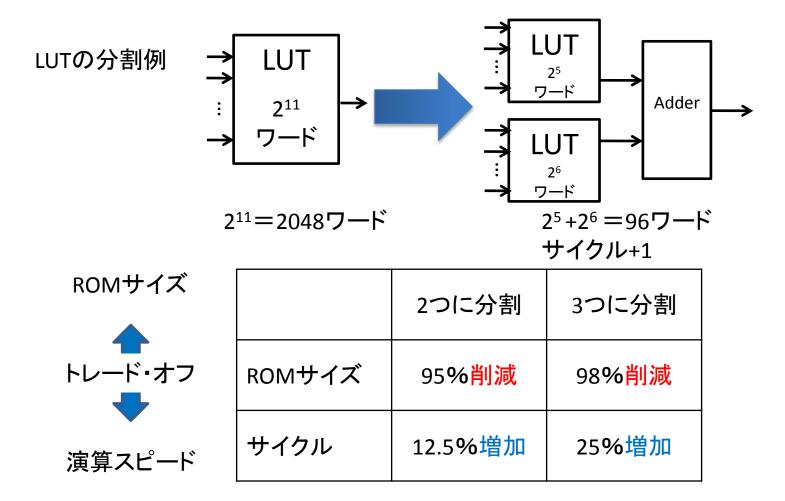

# <u>LUTの検討</u>

LUTの内容:  $\sum_{k=1}^K A_k \cdot b_{kn}$  の全ての結果

LUTのサイズ: 2kワード

指数関数的に増大

LUTのサイズを縮小する必要がある

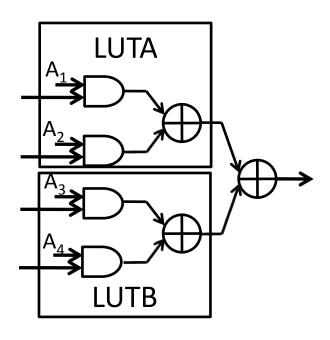

# LUTの本質と分割法

LUTのサイズ $S(k) = 2^k$

#### 2分割の場合

$$S(k) = \begin{cases} 2^{\frac{k}{2}} + 2^{\frac{k}{2}} = 2^{\frac{k}{2}+1} & (k \text{は偶数の場合}) \\ 2^{\frac{k-1}{2}} + 2^{\frac{k+1}{2}} = 3 \times 2^{\frac{k-1}{2}} & (k \text{は奇数の場合}) \end{cases}$$

※LUT内容は付録を参照

# LUTを最適な分割

11タップの場合ではトレード・オフを考慮して2分割が最適

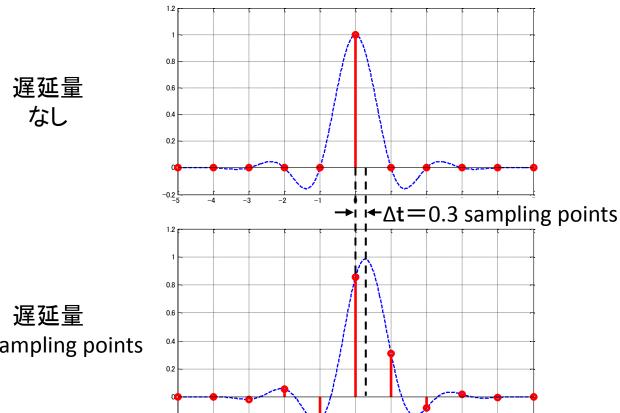

### Simlinkモデルに使用したフィルタ係数

11タップでブラックマン窓を 掛けた場合のインパルス応答

0.3 sampling points

(3)浅見幸司,立岩武徳,黒沢烈士,易茹,荒川雄太,小林春夫:「線形位相遅延ディジタルフィルタの実装の 参考文献 検討」, 第13回DSPS教育者会議 ポスターセッション 東京都市大学,(2011).

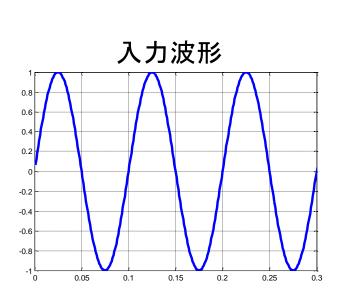

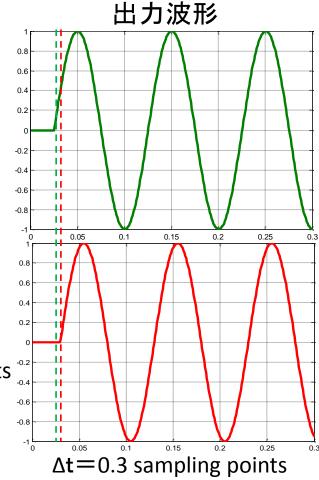

### 正弦波を入力した場合のSimlinkモデルの有効性確認

遅延量なし

Simlinkモデルの有効性を確認

# 発表内容

- 研究の背景・目的

- 分散型積和演算回路

- 実装の検討

- まとめ・今後の課題

# まとめ・今後の課題

### まとめ

- 分散型積和演算回路を用いた遅延デジタルフィルタのMATLABモデルを作成した

- ・係数を入れてモデルの有効性を確認した 今後の課題

- 作成したプログラムをFPGAに実装する

- 評価を行う

## 付録

#### k=4のときのLUTの内容

#### LUT

| b <sub>1n</sub> | b <sub>2n</sub> | b <sub>3n</sub> | b <sub>4n</sub> | $\sum_{k=1}^{4} A_k \bullet b_{kn}$              |

|-----------------|-----------------|-----------------|-----------------|--------------------------------------------------|

| 0               | 0               | 0               | 0               | 0                                                |

| 0               | 0               | 0               | 1               | <b>A</b> <sub>4</sub>                            |

| 0               | 0               | 1               | 0               | $A_3$                                            |

| 0               | 0               | 1               | 1               | A <sub>3</sub> + A <sub>4</sub>                  |

| 0               | 1               | 0               | 0               | A <sub>2</sub>                                   |

| 0               | 1               | 0               | 1               | A <sub>2</sub> + A <sub>4</sub>                  |

| 0               | 1               | 1               | 0               | A <sub>2</sub> + A <sub>3</sub>                  |

| 0               | 1               | 1               | 1               | A <sub>2</sub> + A <sub>3</sub> + A <sub>4</sub> |

| 1               | 0               | 0               | 0               | <b>A</b> <sub>1</sub>                            |

| 1               | 0               | 0               | 1               | A <sub>1</sub> + A <sub>4</sub>                  |

| 1               | 0               | 1               | 0               | A <sub>1</sub> + A <sub>3</sub>                  |

| 1               | 0               | 1               | 1               | $A_1 + A_3 + A_4$                                |

| 1               | 1               | 0               | 0               | A <sub>1</sub> + A <sub>2</sub>                  |

| 1               | 1               | 0               | 1               | A <sub>1</sub> + A <sub>2</sub> + A <sub>4</sub> |

| 1               | 1               | 1               | 0               | $A_1 + A_2 + A_3$                                |

| 1               | 1               | 1               | 1               | $A_1 + A_2 + A_3 + A_4$                          |

# 付録

#### 2分割したLUTの内容

#### **LUTA**

| b <sub>1n</sub> | b <sub>2n</sub> | $\sum_{k=1}^4 A_k \bullet b_{kn}$ |

|-----------------|-----------------|-----------------------------------|

| 0               | 0               | 0                                 |

| 0               | 1               | <b>A</b> <sub>1</sub>             |

| 1               | 0               | A <sub>2</sub>                    |

| 1               | 1               | A <sub>1</sub> + A <sub>2</sub>   |

#### **LUTB**

| b <sub>3n</sub> | b <sub>4n</sub> | $\sum_{k=1}^4 A_k \bullet b_{kn}$ |

|-----------------|-----------------|-----------------------------------|

| 0               | 0               | 0                                 |

| 0               | 1               | $A_3$                             |

| 1               | 0               | <b>A</b> <sub>4</sub>             |

| 1               | 1               | A <sub>3</sub> + A <sub>4</sub>   |