# TV チューナ用完全ディジタル PLL 回路 - 広帯域化の検討

村上 健\* 長谷川 賀則 大介(群馬大学) 湯本 哲批 三田 北村 真一((株)三洋半導体) 壇 徹 内藤 智洋 高橋 伸夫 坂田 浩司 小林 新津 葵一(群馬大学) 春夫 高井 伸和

Wideband Techniques of ADPLL for TV Tuner Application

Ken Murakami\*, Tetsuya Yumoto, Yoshinori Hasegawa, Daisuke Mita (Gunma University)

Toru Dan, Tomohiro Naito, Nobuo Takahashi, Koji Sakata, Shinichi Kitamura

(SANYO Semiconductor Co., Ltd)

Haruo Kobayashi, Nobukazu Takai, Kiichi Niitsu (Gunma University)

This paper present design and performance of wideband ADPLL chip sets for TV tuner applications. We propose here to employ architecture of multiple DCOs and their selection as well as a programmable divider to wideband variable output frequency. Their SPICE simulation and chip measurement results are described. +-7-ド: 完全ディジタル PLL 回路,広帯域,ディジタル制御発振回路,TV チューナ (ADPLL, Wideband, DCO, TV Tuner,)

#### 1. はじめに

近年の目覚ましい集積回路技術の発達により、無線通信で行われるサービスが増加し、複数のアプリケーションを1つの端末で使用できるマルチバンド技術、より正確な情報を沿う受信可能とする低雑音技術など、様々な高度化技術の実現・更なる発展が期待されている。CMOSプロセスの微細化加工技術の進歩により高周波動作帯域を可能にしたが、アナログ回路の低電源電圧動作、低雑音動作の要求を満たすのが困難な状況になりつつある。それに対してディジタル回路はプロセス微細化に伴い、高速動作化、低スイッチング雑音化、低電源電圧動作化など、微細化に伴うアナログ回路のデメリットを補う利点が多くあるため、ディジタルリッチなアナログ回路技術が次世代無線通信技術として注目されている。

本研究では PLL(Phase Locked Loop)を完全ディジタル化した、完全ディジタル PLL 回路(All Digital Phase Locked Loop: ADPLL)に着目した。ADPLL の構成については明確化されつつあるが、GSM や Bluetooth などの今日帯域無線への適用を想定した例が多く、広帯域無線への適用例はあまり見られない。そこで、本研究においては次世代無線技術のキーコンポーネントの一つとして期待されるADPLL に用いているディジタル発振器部分において、TVチューナ用の広帯域動作化技術についての検討を行い、その一部についてのチップ試作と測定を行ったので報告する。

#### 2. ADPLL

#### 〈2·1〉 PLL 回路

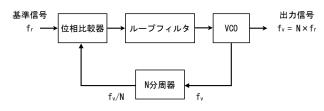

図1 一般的な PLL のブロック図

Fig.1. Block diagram of general PLL.

図1に一般的な(アナログまたはアナログ・デジタル混載)PLLのブロック図を示す。位相比較器、チャージポンプ、ループフィルタ、電圧制御発振回路(Voltage Controlled Oscillator: VCO)、分周器から構成される。位相比較器は基準信号と分周された出力信号の位相比較を行い、二つの信号の位相差を検出する。検出された位相差信号をループフィルタに通す事で信号が積分され、DC レベルの電圧信号へ変換される。ループ回路には雑音成分の除去や、PLL 回路全体の応答特性の決定などの重要な役割を持っている。ループフィルタによって得られる電圧信号により VCO の発振周波数が制御される。この際に基準信号と分周された出力信号の位相差をゼロにすることでシステムが収束し、基準信号の逓倍(分周比倍)の出力信号を得る事ができる。

PLL 回路の中で位相比較器、ループフィルタ、VCO はアナログ回路構成となる為、CMOS 微細化による低電源電圧化の影響による電圧制御範囲の制限、ノイズや特性ばらつ

きの影響の増大、受動素子(R, C)で構成されるループフィルタの広いチップ面積による微細化への弊害など、微細化プロセスの進展だけでは解決できない様々な問題が生じる。

#### 〈2·2〉 ADPLL の基本構成と動作原理

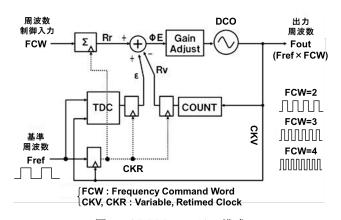

図 2 に ADPLL のシステム回路ブロック図を示す。図 1 で示した一般的な PLL に用いられていた位相比較器はカウンタ(COUNTER)と TDC(Time to Digital Converter)に、ループフィルタはディジタル演算回路を用いたディジタルフィルタに、VCO は DCO(Digitally Controlled Oscillator)にそれぞれ置き換わっている。ADPLL の制御の基本式は(1)式で表す事ができる。

図 2 ADPLL システム構成. Fig. 2. ADPLL system block diagram.

$$F_{out} = FCW * F_{ref}$$

.....(1)

この式は周波数制御信号 FCW (Frequency Command Word)により出力周波数  $F_{out}$  を制御することを表している。システムのクロックは基準信号  $F_{ref}$  とフィードバック信号 CKV によって生成された CKR を用いる。システム内の演算は全て CKR によって駆動される。FCW を CKR のタイミングで加算して得られたデータ  $R_r$  と、CKV をカウントして CKR でサンプリングしたデータ  $R_v$  を演算する事で大まかな位相差を検出する。より細かな位相差をは TDC で検出する。TDC は 2 信号間の遅延差をディジタル的に検出することが可能な回路である。180nm の CMOS を用いた場合の TDC においては、80psec 程度の時間分解能を得る事ができる。

以上より位相差 $\phi$ Eは(2)式のように表す事ができる。

$$\phi_E = R_r - R_v + \varepsilon_{\dots(2)}$$

演算により求めた  $\phi$  E はディジタルフィルタで処理され、 DCO の制御信号である OTW(Oscillator Tuning Word)に 変換され DCO の周波数を設定周波数に制御する。図 3 に FCW が 4.25 の場合の  $\phi$  E の計算イメージについて示す。

# 〈2·3〉 ADPLL による収束精度と収束時間の改善

PLL のループゲイン $\alpha$ は、システム全体の動作特性を決定する重要な要素である。このループゲインを小さく設定する事で高い収束精度を得る事が可能になるが、収束時間が長くなるというトレードオフが発生してしまう。アナログ PLL においては、ループフィルタの回路素子によってループゲインが決定し、収束時間の高速化と高精度化の両立は困難であった。しかし、ADPLLではディジタルフィルタを用いており、ループゲインをプログラマブルに設定可能なため、段階的にループゲインを切り替える事で、精度と収束時間のトレードオフを改善することが可能である。最初はループゲインを大きく取り低精度かつ高速で目標値付近まで収束させ、次にループゲインを小さくさせていき、徐々に精度を高めていく。このような動作を行う事で速い収束時間と高精度を実現している。

Fig. 3. The concept calculating  $\phi$  E.

# 3. DCO について

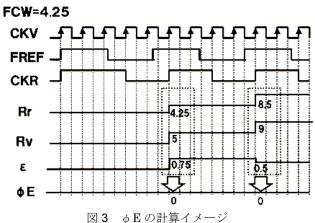

#### ⟨3·1⟩ VCO

発振回路は、インバータ等の反転論理回路を奇数個用いて遅延により発振動作させるリング発振回路、LCの共振により単一周波数発振条件を満たして発振動作させるLC共振回路などが主に用いられている。リング発振回路に比べてLC発振回路の方が位相雑音特性に優れているため、無線通信回路ではLC発振回路が多く用いられている。基本的なLC共振型のVCOの構成を図4に示す。

図 4 LC-VCO 回路の構成 Fig.4. LC-VCO circuit.

この VCO の発振周波数  $f_o$  は負荷のインダクタンス L と キャパシタンス C、バラクタと呼ばれる可変容量のキャパシタンス  $C_v$  により

$$f_0 = \frac{1}{2\pi\sqrt{L(C+C_V)}}....(3)$$

と与えられる。VCO のバラクタは入力の電圧レベルに応じて連続的な容量可変動作を行うため、微細化によるモデルのばらつきやノイズに弱いという欠点がある。

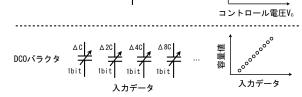

# (3·2) DCOVCOバラクタUCOバラクタ

図 5 VCO と DCO のバラクタ制御方法

Fig.5. Control methods of VCO and DCO.

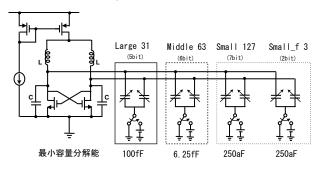

DCO はディジタル入力により発振周波数の制御を行う。 基本的には VCO とほぼ同様の構成であるが、バラクタの制御方法が異なる。図 5 に LC-VCO と LC-DCO の各バラクタの制御方法を示す。入力の電圧レベルに応じて連続的な容量可変動作を行う VCO のバラクタと異なり、DCO は容量値の小さなバラクタのアレイ構成を用いて各バラクタをON/OFF の 2 値で変化させることでディジタル的な制御を可能にする。DCO のバラクタの容量分解能は ADPLL 出力の位相雑音特性に大きく影響する為、微小な容量変化が要求されるが、分解能を細かくすると周波数可変範囲が狭くなるというトレードオフが発生する。そのトレードオフを解消するために、ここでは容量分解能の異なる三種類のバラクタを用いている。

図 6 DCO に用いているバラクタの種類 Fig.6. Classification of DCO varactors.

図 6 に、DCO に用いているバラクタの種類について示す。 粗い精度で大きく周波数可変を行う Large バラクタを 5bit、 中程度の精度と周波数可変を行う middle バラクタを 6bit, 高精度の周波数可変を行う small バラクタを 7bit、更にフ ラクショナル制御用のバラクタを 2bit 用いている。

サブミクロン MOS バラクタを適用し、最小で数百 aF オーダーでの容量分解能を得る事が可能になる。small バラクタの最小容量分解能からさらに細かい精度を得る為に、バラクタの ON/OFF のタイミングを切り替える事により時間平均での実効的な容量値の制御(フラクショナル制御)を行う方法をとっているが、更にここではバラクタ容量の切り替え時に発生するスプリアス成分を軽減する方法として、 $\Delta \Sigma$ 変調を用いた制御方法を使用している。

## 4. TV チューナ用に向けた広帯域化技術

#### 〈4·1〉 分周器を用いた広帯域化

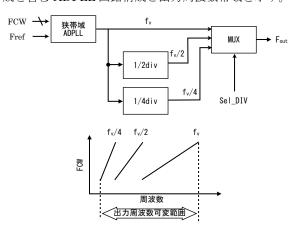

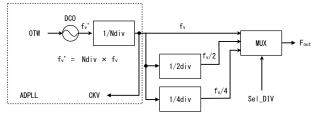

TV チューナ用 ADPLL の広帯域化技術の一つとして分周 回路構成の適用について検討を行った。図 6 に分周回路構成を含む ADPLL 回路構成と出力周波数帯域を示す。

図7 可変分周回路を用いた広帯域化構成

Fig.7. Wideband architecture with programmable divider

図 7 に示すように ADPLL の出力信号 fv を、複数の異なる 分周比を持つ分周回路を通す事でそれぞれ分周し、外部から Sel\_DIV 信号を与える事でマルチプレクサを操作し、目的の周波数を選択できる構成を取る事で、より広帯域な ADPLL の出力周波数を取る事ができる。ただし、分周回路 構成を用いて連続した周波数可変帯域幅を得るには、70% ( $f_{vmax} \ge 2f_{vmin}$ )以上の周波数可変率を持った DCO が必要と なる。

#### 〈4·2〉 DCO 回路の広帯域化

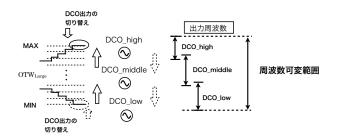

可変分周回路構成による ADPLL の広帯域化手法を用いるには広帯域動作可能な DCO が必要となる。しかし、DCO はバラクタのアレイ構成をのぞくとほぼアナログ PLL 回路で使用される VCO と同様の構成になっている。その為、VCO と同様に DCO の発振周波数可変帯域はバラクタの可変容量範囲や回路内部の寄生容量により制限されてしまう。単体の DCO では目標とする発振周波数帯域の実現が困難であることから、図 8 に示すように異なる周波数可変範囲を持つ複数の DCO 回路を用いて、使用する周波数帯域に

応じて切り替える構成を取る事で、目標とする可変帯域の 実現を検討した。

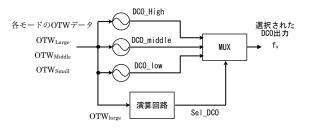

図8 複数 DCO 切り替え構成.

Fig .8. Multiple-DCO switching architecture.

図8は今回実際に用いた、3つのDCOの切り替え構成を示している。所望周波数帯域のうち、低い周波数帯をDCO\_low、中間の周波数帯をDCO\_midddle、高い周波数帯をDCO\_highがそれぞれ担当している。Sel\_DCO信号は各DCO出力の中から一つを選択する為の制御信号であり、OTW信号の演算から得られる。演算回路の原理を図9に示す。

図 9 制御信号と DCO 回路の切り替え動作原理 Fig.9. Control signal and principle of DCO switching.

演算回路の入力には、制御信号のうち最も広域で周波数制御を行うモード(ここではLarge バラクタを制御するモード)のデータが用いられる。制御信号に使用されるビット幅の最大値および最小値を検出してDCOの切り替えを行う。ADPLLシステムに要求される周波数に応じて使用するDCOを切り替える事で、広帯域動作を行うDCOブロックの実現が可能になる。

# 〈4・3〉位相雑音の低減化技術

DCO から発生する DCO アナログ雑音は、ADPLL 内で発生するいくつかの雑音の中で主要な雑音源となっている。 PLL などの位相雑音特性が重要な性能指標となる回路では、要求される周波数の逓倍信号をつくり、後に分周させる事で低位相雑音化を行う技術が用いられる。そこでADPLL においても逓倍発振による位相雑音の改善について検討を行った。図 10 に逓倍発振構成の ADPLL の部分ブロックを示す。

図 10 逓倍発振構成 ADPLL

Fig .10. Architecture of frequency multiplying oscillation ADPLL.

N<sub>div</sub> 倍発振させた DCO の出力を f<sub>v</sub>とし、N<sub>div</sub> 分周させて ADPLL の出力周波数 f<sub>v</sub> を生成する構成である。

DCO のアナログ雑音により生じる位相雑音  $N_{DCOa}$  は  $N_{div}$  分周を行う事で $(1/div)^2$  倍に低減する事が可能になり、 $N_{div}$  分周後のアナログ雑音により生じる雑音を  $N_{DCOadiv}$  とすると次式で表せる。

$$N_{DCOadiv} = \left(\frac{1}{N_{div}}\right)^2 N_{DCOa} \tag{4}$$

DCO の量子化雑音について、バラクタ制御ビット 1LSB の変化に対する DCO の出力周波数の変化  $fv_{res,DCO}$ 、フラクショナル構成を用いたときの周波数分解能  $fv_{res,dith,DCO}$  は  $N_{div}$  分周により  $1/N_{div}$  倍され、DCO 回路の出力周波数は  $N_{div}$  倍で出力されている事を考慮する必要がある。 DCO の発振周波数は前述の式と同様、DCO に使用するインダクタンス L と総合的なキャパシタンス  $C_{tot}$  を用いて次式のように表せる。

$$f_v = \frac{1}{2\pi\sqrt{L \times C_{tot}}} \tag{5}$$

発振周波数を  $N_{\rm div}$  倍に設定するには  $L \times C_{\rm tot}$  の項を $(1/N_{\rm div})^2$  に設定する必要がある。この時、量子化分解能  $fv_{\rm res,DCO}$  は L の値に依存性を持つ事から  $N_{\rm div}$  倍の DCO 出力周波数の設定について、 $C_{\rm tot}$  を買えずに L を $(1/N_{\rm div})^2$  倍、L を変えずに  $C_{\rm tot}$  を $(1/N_{\rm div})^2$ 、L と  $C_{\rm tot}$  共に  $1/N_{\rm div}$  倍した時の各周波数分解能を考えるとそれぞれ次式のように表せる。

#### L を(1/N<sub>div</sub>)<sup>2</sup>倍

$$fv_{res,DCO,DIV,L} = -\frac{1}{N_{div}} \times 2\pi \times \Delta C \times \frac{L}{N_{div}^2} \times (N_{div} \times f_v)^3$$

$$= -2\pi \times \Delta C \times L \times f_v^3 = f_{vres,DCO}$$

C を(1/N<sub>div</sub>)<sup>2</sup>倍

$$f_{vres,DCO,DIV,C} = -\frac{1}{N_{div}} \times 2\pi \times \Delta C \times L \times (N_{div} \times f_v)^3$$

$$= -2\pi \times N_{div}^2 \times \Delta C \times L \times f_v^3 = N_{div}^2 \times f_{vres,DCO}$$

....(7)

LとCを共に1/Ndiv倍

$$f_{vres,DCO,DIV,LC} = -\frac{1}{N_{div}} \times 2\pi \times \Delta C \times \frac{L}{N_{div}} \times (N_{div} \times f_v)^3$$

$$= -2\pi \times N_{div} \times \Delta C \times L \times f_v^3 = N_{div} \times f_{vres,DCO}$$

.....(8)

DCO を逓倍発振に設定する時の回路パラメータの変化によって、周波数分解能 fvres,DCO が Ndiv に依存した違いを生じさせていることが分かる。また、フラクショナル構成を用いたときの周波数分解能 fvres,dith,DCO においても同様の効果が現れる。Ndiv 倍発振、Ndiv 分周構成を有するシステムで発生する DCO 量子化雑音は分周構成を持たないシステムの雑音 NDCOg, と比較すると次式で表せる。

$$N_{DCO_q,DIV} = \lambda \times N_{DCO_q}$$

.....(9)

ここで  $\lambda$  は  $N_{div}$ 倍発振設定時の DCO パラメータの変化により  $1\sim N_{div}^4$ までの値を取りうる。 DCO 量子化雑音の増加を回避する為にはインダクタンス L の値を小さくすることで DCO の発振周波数の高周波化を行う必要がある。

次に DCO の位相雑音の式を(10)式に示す。[5]

$$L(\Delta f) = \frac{kT \cdot F}{P_{osc}} [1 + (\frac{1}{2Q} \cdot \frac{f_{osc}}{\Delta f})^2] (1 + \frac{f_c}{\Delta f}).....(1 \ 0)$$

ここで k はボルツマン定数、T は絶対温度、F は発振器を構成するゲインセルの雑音指数、 $P_{osc}$  は発振電力、Q は共振器の Q 値(一般的にインダクタの Q が低く、支配的となる)、 $f_{osc}$  は発振周波数、 $\Delta f$  はキャリアからの離調周波数、 $f_c$  はフリッカ雑音起因の位相雑音と熱雑音起因の位相雑音のコーナー周波数である。この式から分かるように、位相雑音は発振周波数の二乗に比例する。そのため、実際には N 分周による雑音低減は相殺されてアナログノイズは一定となる。しかし、発振周波数を高周波化してインダクタンスが小さい集積インダクタを用いる事で、線路長が短くなり直列の寄生抵抗が下がり、インダクタの Q 値が上昇するため (10)式より位相雑音を低減することができる。従って、発振周波数を高くする事で位相雑音特性を改善する事が可能 上なる.

TDC で生じる量子化雑音も ADPLL で発生する主な雑音 のひとつであり、遅延分解能  $\Delta \tau$ 、CKV の周期  $T_{CKV}$ 、基準 周波数  $F_{ref}$  を用いて(11)式で表される。

$$N_{TDCq} = \frac{(2\pi)^2}{12} \left(\frac{\Delta \tau}{T_{CKV}}\right)^2 \frac{1}{F_{ref}....(1.1)}$$

(11)式から、TDCの量子化雑音は遅延分解能と周期  $T_{CKV}$ に大きな依存性を持つ事が分かる。 逓倍発振時における CKV 周期は従来構成と等しい為、逓倍発振時に発生する量子化雑音  $N_{TDCq,DIV}$  は(12)式のように表される。

$$N_{TDCq,DIV} = N_{TDCq\dots(1\ 2)}$$

以上の結果から ADPLL の逓倍発振構成を用いる事により DCO で発生するアナログ雑音の軽減が可能になる。また、LC-DCO の発振周波数の式より、発振周波数を逓倍設定することでインダクタンス L およびキャパシタンス C を小さな値に設定できる事から、微細化という面でも利点が大きい。しかし、DCO パラメータの設定によっては DCO量子化雑音と呼ばれる雑音の増加を招く恐れがあり、それらのトレードオフを考慮した設計が必要になる。

RF 回路において、信号の周波数変換を行う際には正確な 90°位相差の IQ 信号が必要であり、それを得るためには 4 倍分周が必要なため、今回は  $N_{\rm div}=4$  として設計を行った。

### 5. シミュレーションと実測結果

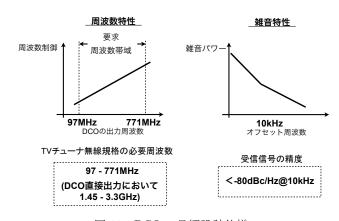

図 11 DCO の目標設計仕様 Fig .11. DCO design specification.

図 11 に設計する DCO の目標仕様を示す。実際の TV チューナ用の規格である地上デジタルテレビジョン放送 D(アナログ放送停波前)の ISDB-T(Integrated Services Digital Broadcasting Terrestrial) 方式の規格を満たすように仕様決めを行った。 $0.18 \mu$  mCMOS プロセスを想定し、SPICE を用いてシミュレーションを行った。

#### 〈5·1〉シミュレーション結果

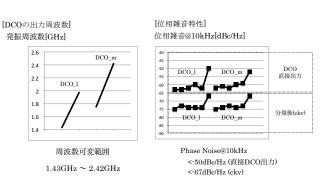

検討 DCO のシミュレーション結果を図 12 に示す。

図 12 検討 DCO のシミュレーション結果 Fig.12. DCO simulation result.

周波数特性においては仕様を満たしており、位相雑音特性においても(一部では仕様を満たしていないが)概ね仕様に近い結果を得る事ができた。

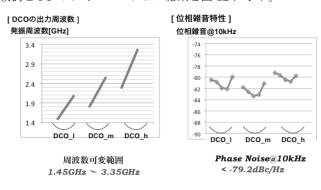

#### 〈5·2〉実測結果

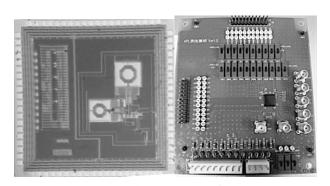

図 13 にチップ写真と測定基板を示す。今回の実測は 0.18um CMOS フルカスタム試作チップと FPGA を接続して行った。試作チップには DCO、カウンタ、TDC が入って

おり、ADPLL のその他のブロックは FPGA によって実装されている。試作チップのサイズは  $2.5 \,\mathrm{mm} \times 2.5 \,\mathrm{mm}$  であり、今回の試作チップには三つの DCO のうち DCO\_low と DCO\_middle が入っている。

図 13 試作チップと測定基板 Fig .13. ADPLL chip and evaluation board.

図 14 に試作チップにおける周波数と位相雑音の測定結果を示す。

図 14 実測結果 Fig .14.Measurement result.

実測結果の位相雑音特性がシミュレーション結果に比べてかなり劣化しているが、今回の試作では DCO を正常動作させ、チップと FPGA と接続し、ADPLL 回路としての動作を確認することを優先した。そのため、レイアウトを行う段階で、ばらつきによる動作不良を避けるために位相雑音特性を犠牲にし、DCO の発振動作を優先するように各種パラメータを調整している。

#### 6. まとめ

本研究ではTV チューナ用 ADPLL に向けた DCO の広帯域化時技術についての検討を行った。ADPLL システムに可変分周回路を用いることで広帯域動作化が可能となることを示した。また、複数の異なる周波数帯域を持つ DCO を、システムの内部データ OTW により制御して切り替えて用いる事で、広帯域動作可能な DCO ブロックとして構成する事ができることを示した。また、検討回路の一部について180nm の CMOS プロセスにおいてチップ試作を行い、測

定評価する事で、実際に広帯域化技術が有効である事を確認した。

今後の課題として、DCO の位相雑音特性の改善、全ての 帯域をカバーするチップの作製、ADPLL 回路のワンチップ 化などが挙げられる。

#### 文 献

- R. B. Staszewski and P. T. Balsara: "All-Digital Frequency Synthesizer a Deep-Submicron CMOS", Wiley-Interscience(2006)

- (2) R. B. Staszewski: "Frequency Synthesizers in Nanometer CMOS", DCAS SEMINAR, 21 Feb 2007

- (3) Bogdan Staszewski: "All-Digital TX Frequency Synthesizer and Discrete-Time Receiver for Bluetooth Radio in 130-nm CMOS", IEEE Journal of Solid-State Circuits, Vol.39, No.12, Dec 2004

- (4) 田辺朋之・壇徹・小林春夫 他:「TV チューナ用 ADPLL の検討」、電子情報通信学会大会講演論文集,エレクトロニクス 2, pp.132, 2009

- (5) T. H. Lee, "The Design of CMOS Radio-Frequency Integrated Circuits," Cambridge University Press, p535, 1998, ISBN 0-521-63061-4