平成23年10月 電子回路研究会

ECT-11-077

# シグマデルタ型タイムデジタイザ 回路の検討

上森聡史 土井佑太 小林春夫(群馬大学) 小林修(STARC) 松浦達治 新津葵一(群馬大学)

- 研究背景と目的

- ・ シグマデルタ型TDCの構成・動作

- マルチビットシグマデルタ型TDCの構成・動作と Element Rotation回路の適用

- Element Rotation回路の動作

- MATLABシミュレーションによる検証

- 結論

- 研究背景と目的

- ・ シグマデルタ型TDCの構成・動作

- マルチビットシグマデルタ型TDCの構成・動作と Element Rotation回路の適用

- Element Rotation回路の動作

- MATLABシミュレーションによる検証

- 結論

#### 研究背景

- 半導体製造コストの減少に対しテストコストは増加

- テストコストを下げる

- ・ デジタル信号間の時間差の測定

- 短時間で求める精度で測定する必要あり

- 適用するアプリケーションの例

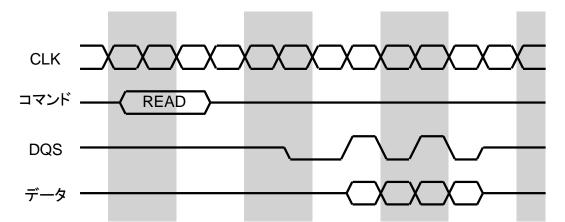

- DDR(Double Data Rate)メモリのデータ、クロック間の 時間差の計測等:

内部処理回路とメモリアクセスのタイミング、制御信号・ データ信号間のタイミング

#### 研究目的

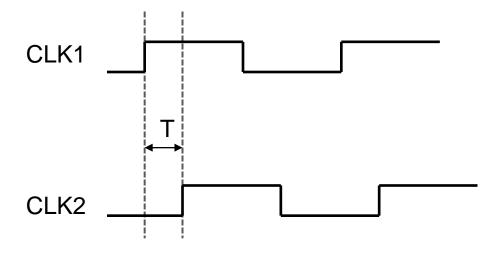

- 2つの繰り返しクロック間の時間差を 高時間分解能・簡単な回路で計測

- シグマデルタ型タイムデジタイザを用いる

- マルチビットシグマデルタ型タイムデジタイザの提案

- 短時間で所定の精度・分解能で時間差をテスト

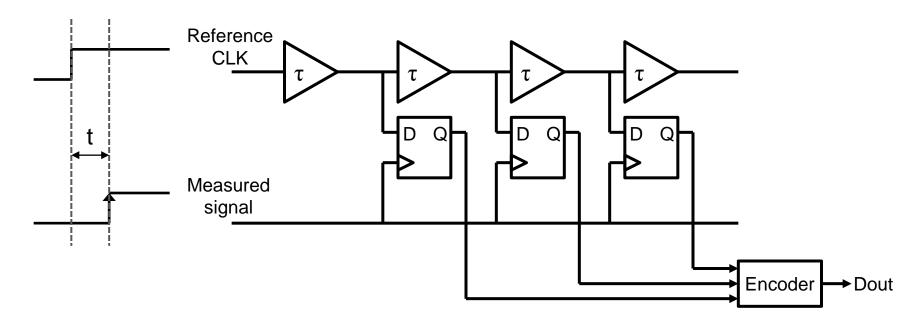

#### 従来基本TDC構成

#### •Flash型TDC

- •任意の信号でも計測可

- ・回路が大きくなってしまう

- •時間分解能はτで決まってしまう

- ・高精度で測定できるようにする→繰返し信号を計測

- 研究背景と目的

- シグマデルタ型TDCの構成・動作

- マルチビットシグマデルタ型TDCの構成・動作と Element Rotation回路の適用

- Element Rotation回路の動作

- MATLABシミュレーションによる検証

- 結論

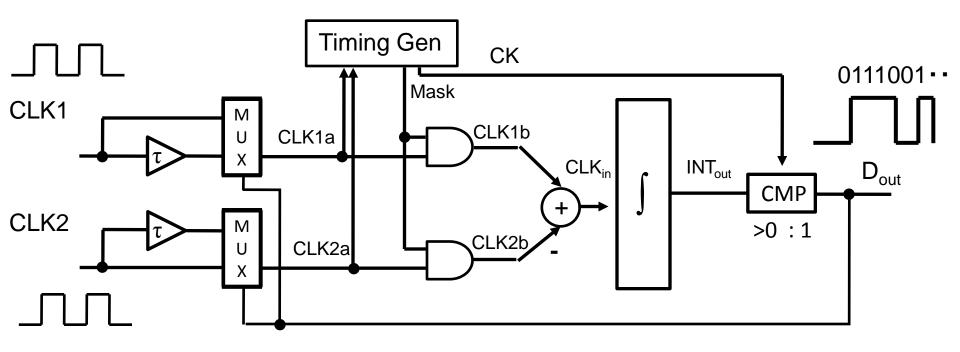

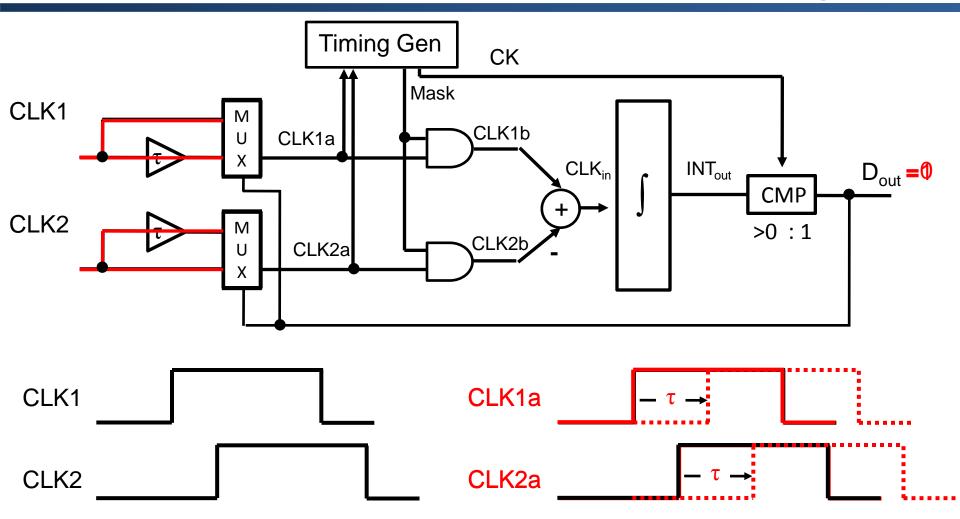

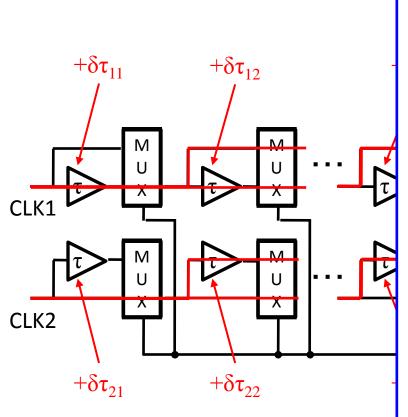

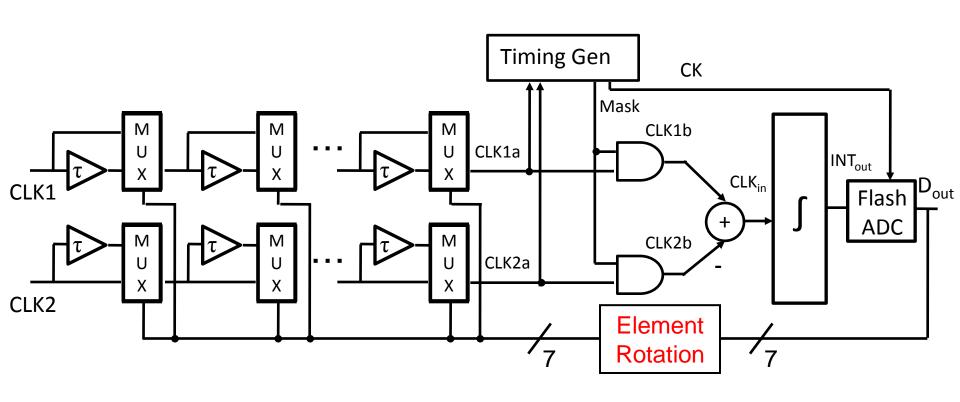

### シグマデルタ型TDC回路の構成

- •遅延セル, マルチプレクサ, AND回路, アナログ積分器, 比較器で構成

- ▶ 簡単な回路で実現可能

- •CLK1とCLK2間の時間差を計測

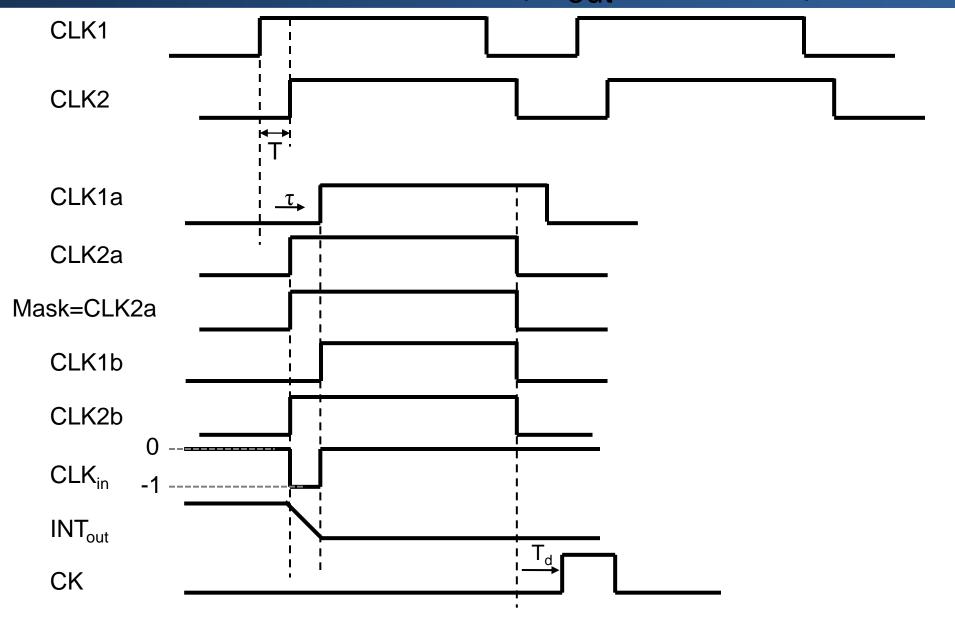

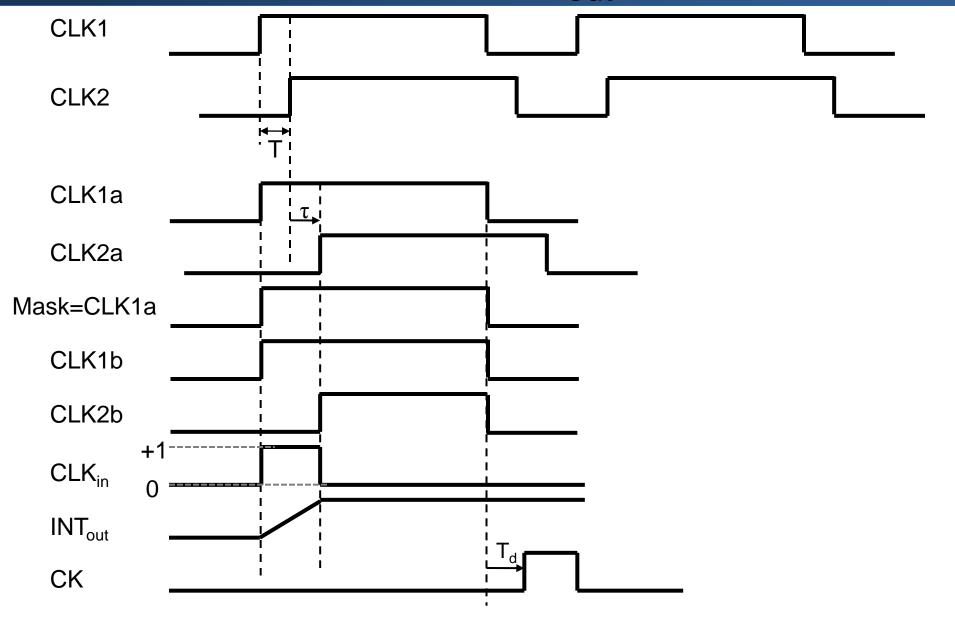

### シグマデルタ型TDC回路の動作①

- •CLK1とCLK2を入力

- ・比較器出力により経路選択

- ➤ CLK1a, CLK2aを得る

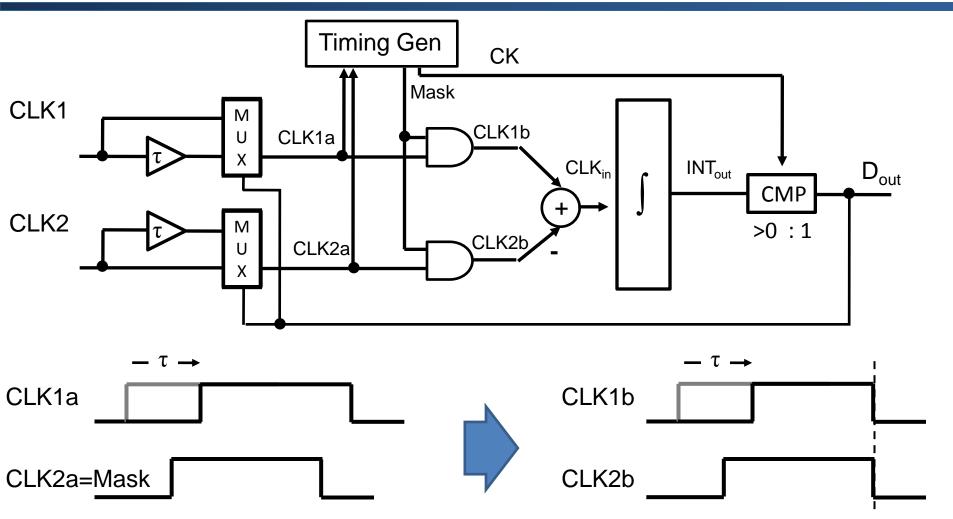

## シグマデルタ型TDC回路の動作②

- •タイミングジェネレータによりMask信号(=速い方の信号)を発生させる

- ➤ Mask信号とCLK1a, CLK2aとの論理積をとり、立下りを合わせる

- ➤ CLK1b, CLK2bを得る

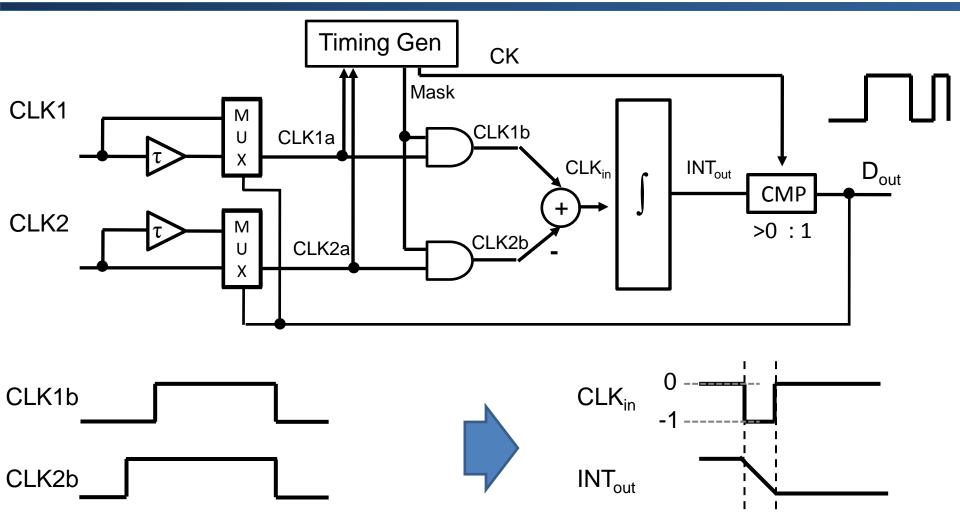

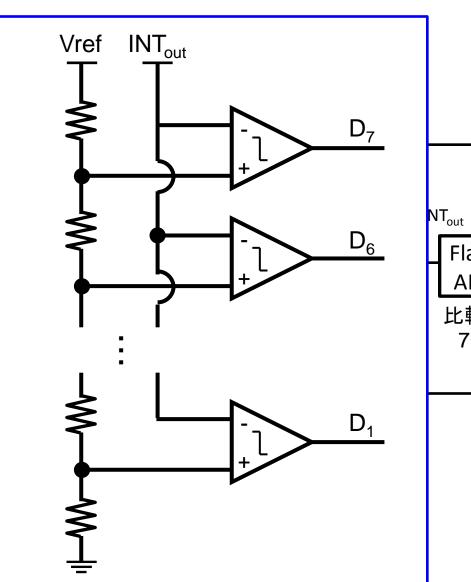

### シグマデルタ型TDC回路の動作③

- •CLK1bとCLK2bとの差をとり結果のCLKinを積分

- ・比較器でINT。utを0と比較し、出力D。utを得る

- 次のクロックでの経路を制御

# タイミングチャート(Dout=1のとき)

# タイミングチャート(Dout=0のとき)

- 研究背景と目的

- ・ シグマデルタ型TDCの構成・動作

- マルチビットシグマデルタ型TDCの構成・動作と Element Rotation回路の適用

- Element Rotation回路の動作

- MATLABシミュレーションによる検証

- 結論

$\mathsf{D}_{\mathsf{out}}$

Flash

**ADC**

比較器 7個 =2

# マルチビット∑∆TDC回路の構成

- •遅延セルとマルチプレクサを増や

- •Flash ADCの出力結果で経路選

- •遅延セルのミスマッチによって非

#### Element Rotation回路の適用

- •Element Rotation回路でFlash ADCの温度計コード出力を シャッフルしてから各MUXに入力する

- •遅延ばらつきの影響を少なくする

### マルチビットにする利点

- •シングルビットシグマデルタ型TDC

- •遅延ミスマッチが影響しない

- •精度は出せる

- •テストの際には短時間で所定の精度で評価

- •マルチビットにすることで速く計測できる

- •Element Rotation回路を用いることである程度精度が出せる

- 研究背景と目的

- ・ シグマデルタ型TDCの構成・動作

- マルチビットシグマデルタ型TDCの構成・動作と Element Rotation回路の適用

- Element Rotation回路の動作

- MATLABシミュレーションによる検証

- 結論

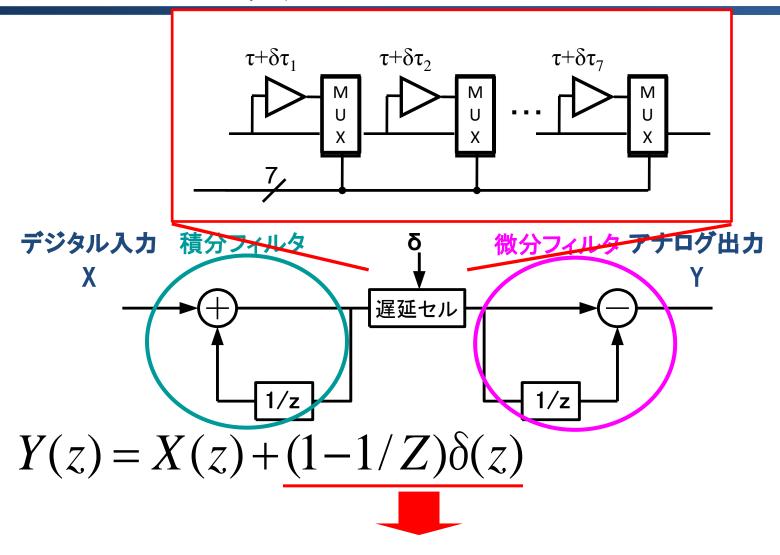

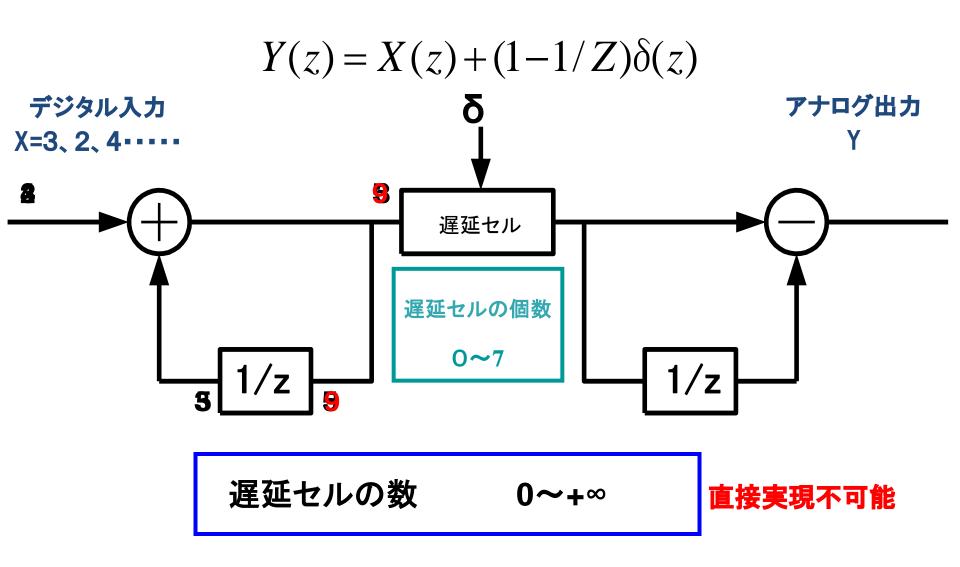

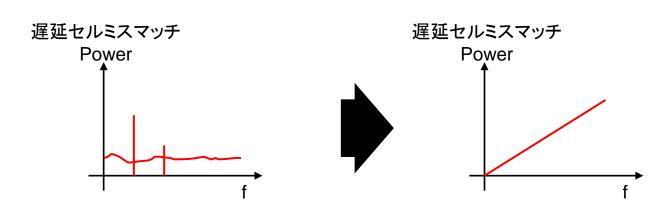

### 1次ノイズシェープ

遅延セルミスマッチが1次ノイズシェープ 1/(1-1/Z)されている

#### 1次ノイズシェープの動作

#### Element Rotation回路の効果

•積分して微分を等価的に実現 ▶遅延セルミスマッチが1次ノイズシェープ

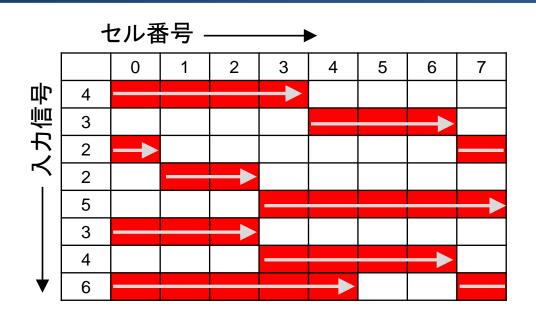

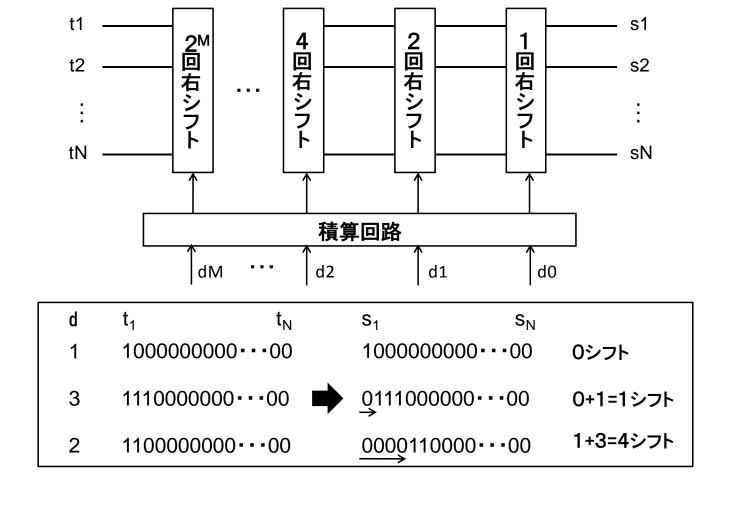

#### Element Rotation回路の動作

•デジタル入力によりシフトする量を制御する

- 研究背景と目的

- ・ シグマデルタ型TDCの構成・動作

- マルチビットシグマデルタ型TDCの構成・動作と Element Rotation回路の適用

- Element Rotation回路の動作

- MATLABシミュレーションによる検証

- 結論

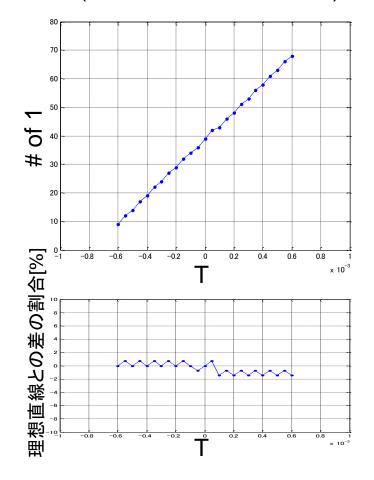

### ΣΔTDCのシミュレーション結果

#### MATLABシミュレーション

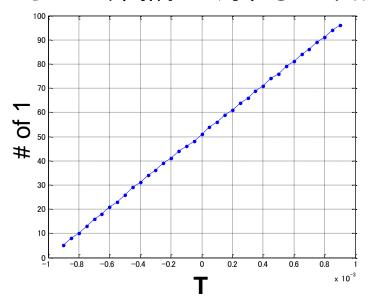

#### 1bitの場合

・立ち上がり間隔 : T=0.05ns刻み

-0.9~0.9ns

•遅延時間: τ=1ns

•出力数(コンパレータで比較した回数): 100点

●立ち上がり間隔Tに対する1の出力数

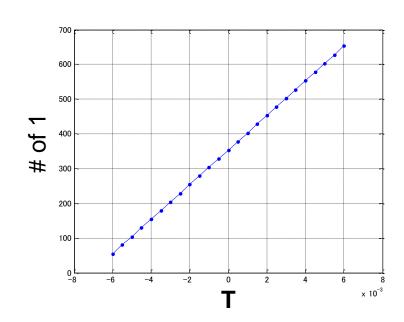

#### 3bitの場合

・立ち上がり間隔:T=0.5ns刻み

-6~6ns

•遅延時間: τ=1ns

•出力数(コンパレータで比較した回数): 100点

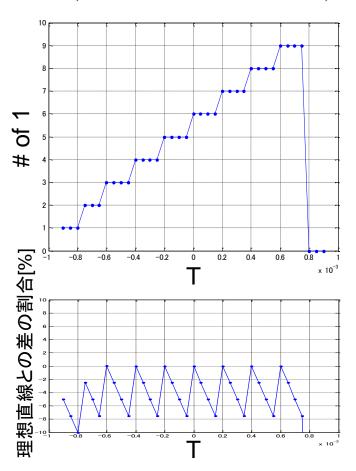

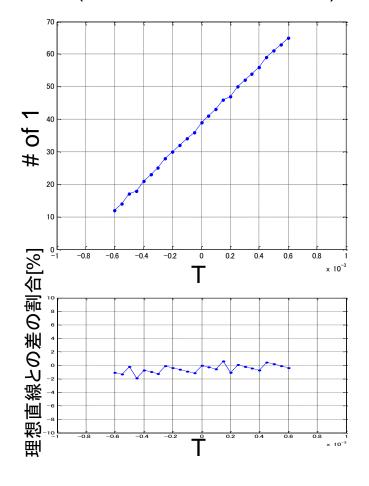

#### 測定時間を短縮した場合の結果

1bit

•遅延時間: τ=1ns

・出力数(コンパレータの比較回数):10点

3bit

•遅延時間: τ=0.1ns

・出力数(コンパレータの比較回数):10点

✓マルチビット化することで短時間で細かく測定可能

#### 遅延ばらつきの影響の検証

•遅延ばらつき: ガウス分布でランダムに生成 最大で $\tau=1$ ns の $\pm 10$ %程度の誤差とした

#### •シミュレーション時に生成した遅延パラメータ

| 1      | τ1   | τ2   | τ3   | τ4   | τ5   | τ6   | τ7[ns] | τ合計  |

|--------|------|------|------|------|------|------|--------|------|

| CLK1経路 | 1.02 | 1.01 | 1.03 | 0.99 | 0.95 | 1.04 | 1.04   | 7.08 |

| CLK2経路 | 1.04 | 1.04 | 1.04 | 0.92 | 1.03 | 0.98 | 1.03   | 7.08 |

| 2      | T1   | τ2   | τ3   | τ4   | τ5   | τ6   | τ7[ns] | τ合計  |

|--------|------|------|------|------|------|------|--------|------|

| CLK1経路 | 0.96 | 0.97 | 1.01 | 0.91 | 0.96 | 1.02 | 1.02   | 6.85 |

| CLK2経路 | 1.06 | 1.02 | 0.96 | 1.00 | 1.02 | 1.07 | 0.97   | 7.10 |

#### 遅延ばらつきがある場合の結果

•遅延ばらつきがある場合と無い場合との差

- •クロック間立ち上がりタイミングTに対する出力に差が生じる

- •遅延ばらつきにより出力に非線形性を生じる

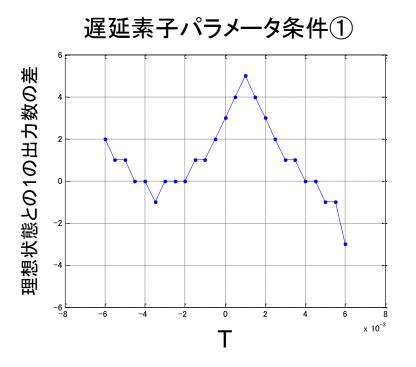

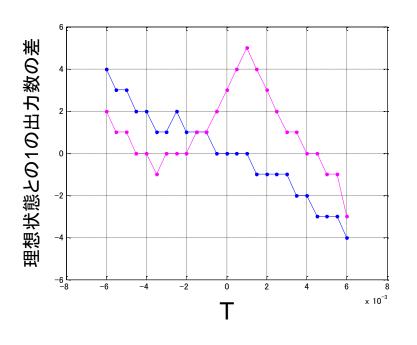

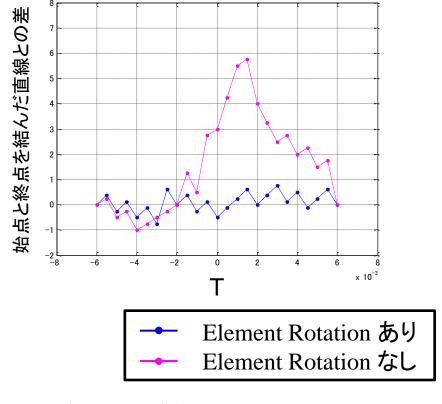

### Element Rotationの効果検証(条件①)

•理想状態との差

•Element Rotationを適用しない場合と 適用した場合のINL

・条件①の場合は遅延ばらつきのないときと比べ傾きが変わるが線形化される ▶遅延ばらつきの影響を軽減できる

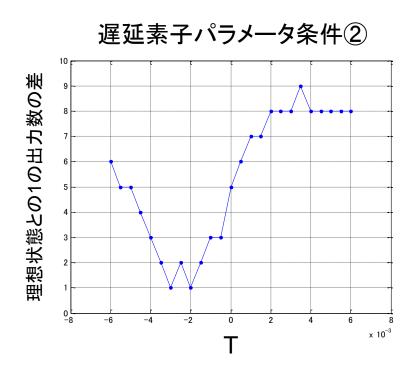

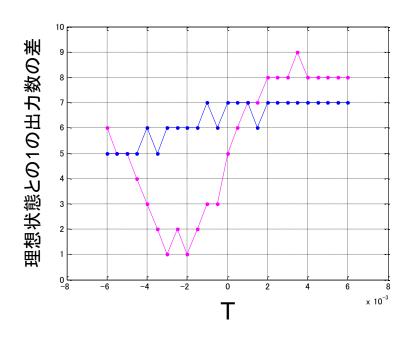

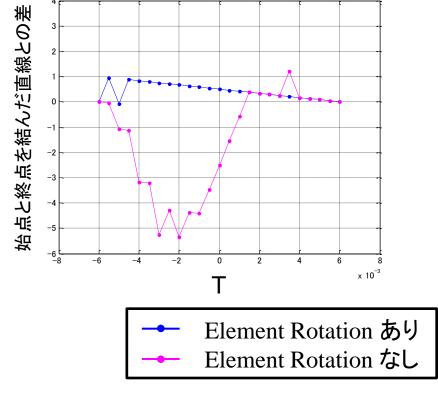

### Element Rotationの効果検証(条件②)

・理想状態との差

•Element Rotationを適用しない場合と 適用した場合のINL

・条件②の場合は全体的に1の出る数が増えるが線形化される ▶遅延ばらつきの影響を軽減できる

#### 測定時間を短縮した場合の結果

3bit, 遅延ばらつき有

•遅延時間: τ=0.1ns

・出力数(コンパレータの比較回数):10点

3bit, Element Rotation回路適用

•遅延時間:τ=0.1ns

・出力数(コンパレータの比較回数):10点

✓遅延ばらつきの影響を軽減できる

- 研究背景と目的

- ・ シグマデルタ型TDCの構成・動作

- マルチビットシグマデルタ型TDCの構成・動作と Element Rotation回路の適用

- Element Rotation回路の動作

- MATLABシミュレーションによる検証

- 結論

#### 結論

- 1bit シグマデルタTDCの動作を確認

- マルチビットのシグマデルタTDCを提案

- ➤ 3bit シグマデルタ TDCの動作を確認

- ▶ 短時間で細かく測定できることを確認(テスト時間短縮可)

- 遅延線に遅延ばらつきがある場合、非線形性を生じることを 確認

- Element Rotation回路を適用した3bitシグマデルタTDCを提案・動作を確認

- ➤ MATLABシミュレーションで非線形性の問題を軽減できる ことを確認

ご清聴ありがとうございました

# 質疑応答

#### 質疑

#### ●Q1

- ・Mask信号を用いてクロックの立下りを合わせる意味は?

- ⇒立下りを合わせずに信号の差をとると、結果には+1と-1が同じ量だけ 現れるため積分結果は0となってしまう。結果としてCLK間の差が見 れないため。

#### ●Q2

- ・測定する信号のジッタの扱いは? ⇒今回は考えていない。

- ・ジッタのスペックが載ってる資料があるから検討してみて

#### ●Q3(アドバイス)

・デルタシグマの出力は最後が1なのか0なのかはわからないため2%の誤差が出る。もっと多く点数をとった方が良い。