# TV チューナ用完全ディジタル PLL 回路 - システムの観点から

湯本 哲也\* 村上 健 西村 繁幸 田邊 朋之(群馬大学) 伸夫 内藤 智洋 坂田 浩二 ((株) 三洋半導体) 壇 徹 高橋 北村 真一 小林 春夫 葵一 (群馬大学) 高井 伸和 新津

### ADPLL System Design for TV Tuner Applications

Tetsuya Yumoto\*, Ken Murakami, Shigeyuki Nishimura, Tomoyuki Tanabe (Gunma University)

Toru Dan, Nobuo Takahashi, Tomohiro Naito, Shinichi Kitamura, Koji Sakata

(SANYO Semiconductor Co., Ltd)

Haruo Kobayashi, Nobukazu Takai, Kiichi Niitsu (Gunma University)

This paper presents design and measurement of ADPLL chip sets for TV tuner applications. We describe the ADPLL architecture, Especially we propose a fast convergence algorithm for frequency setting and confirmed its effectiveness with chip measurements.

**キーワード**: 完全ディジタル PLL 回路, TV チューナ, タイムディジタイザ, 高速整定 (ADPLL, TV Tuner, Time-to-Digital Converter, Fast Settling)

# 1. 研究背景と概要

より快適な通信環境の実現を目的として、無線通信システムでは複数のサービスを 1 つの端末で利用できるマルチバンド化技術、無線システムのワンチップ構成を可能とするモノリシック化技術など様々な高度化技術の実現が期待されている。近年の CMOS 微細化とアナログ回路の CMOS 化が進むことで実現可能となってきている。CMOS 微細化は遮断周波数の向上と低電源電圧化をもたらした。これによりディジタル回路は高速動作、低消費電力化、チップ面積縮小といった恩恵を受け、微細化によるメリットが多い。一方、アナログ回路は MOS トランジスタの耐圧低下に伴う低電源電圧化や、素子ばらつきの増大により設計が一層困難になってきているため、必ずしも微細化によるメリットは多くはない。そこでアナログ回路をディジタル回路で高性能化するディジタルリッチなアナログ回路技術が次世代無線回路技術として注目されている。

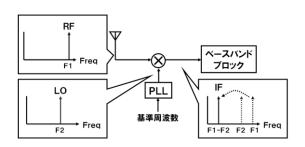

本研究では無線システムのキーコンポーネントである PLL に着目した。PLL は周波数変換を行うミキサーに必要 な LO 信号を生成するために用いられる(図 1)。PLL は通常アナログ回路もしくは一部ディジタル回路で構成されるが、CMOS の微細化による電圧制御範囲の制限や、アナログフィルタの回路面積が大きいといった問題が顕在化している。そこでPLLのディジタルリッチな構成としてADPLL (All Digital Phase Locked Loop) 回路に着目した。ADPLLは 2000 年代中頃に提案され、設計方法は確立されつつある

が、ほとんどが Bluetooth 等の狭帯域無線向けであった。 そこで我々はTVチューナを標的とした広帯域なADPLLを 開発したので報告する。

図1 一般的な受信アーキテクチャ

Fig. 1. General receiver architecture.

# 2. ADPLL システム

# 〈2·1〉概要

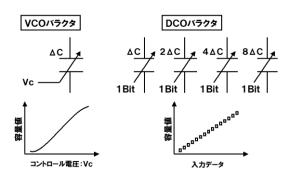

システムに用いる発振器には LC 発振器を採用した。これは位相雑音と動作周波数に優れており、無線通信のアーキテクチャによく採用されている。アナログ PLL の発振器は図2のようにキャパシタの容量値をコントロール電圧 Vc により可変することのできるバラクタを使用する VCO (Voltage Controlled Oscillator)が用いられていたが、全てディジタル領域で制御する ADPLL には適さない。そこで容量の小さいバラクタをアレイ状に並べ、スイッチのオンオフにより容量を制御する DCO (Digitally Controlled Oscillator)を

採用した。周波数分解能が MOS バラクタの最小変化容量に依存するが、近年の微細プロセスを用いることで数十 aF程度の分解能を得ることが可能である。また、単独の DCO では目標の周波数をカバーすることができないため、周波数帯の違う複数の DCO を用いることにより広帯域化を達成した。

図2 VCOとDCOのバラクタ比較

Fig. 2. VCO and DCO varactors.

DCO ゲイン(Kpco)は周波数によって大きく変化し、これらはシステムの伝達関数に影響を及ぼしてしまう。そこで Kpco をシステム内のパラメータから見積もり、正規化することによりその影響をキャンセルする自己校正技術を使用する。今回我々は自己校正をより高速で行うことで全体の整定時間を短縮できる手法を提案し、実機にて効果を確認した。

ADPLL システムの帯域は 93MHz~788MHz。目標とする位相雑音は 90dBc/Hz @10kHz offset。チップには 180-nm CMOS プロセスを使用し、低速動作するディジタル回路部には Xilinx 社製の FPGA を用いた。

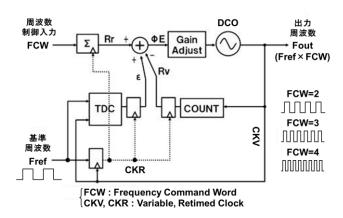

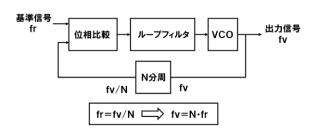

# 〈2·2〉 ADPLL の構成と基本的な動作原理

ADPLLのシステム回路ブロックを図3に示す。従来のアナログPLL(図4)の位相比較器(PD)、ループフィルタ、VCO (Voltage Controlled Oscillator)といった要素回路がそれぞれTDC、ディジタルフィルタ、DCOに置き換わっている。ADPLLの制御の基本は式(1)である。周波数制御信号FCW (Frequency Command Word)により出力周波数Foutを制御することができる。

$$Fout = FCW * Fref$$

(1)

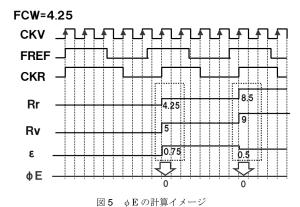

システムのクロックは基準信号 Fref とフィードバック信号 CKV によって生成された CKR を用いる。システム内の演算は全て CKR によって駆動される。FCW を CKR のタイミングで加算して得られたデータ Rr と、CKV をカウントして CKR でサンプリングしたデータ Rv を演算することで位相差を荒く検出する。より細かな位相差  $\epsilon$  は TDC (Time-to-Digital Converter)で検出する。TDC は 2 信号間の遅延差をディジタル的に検出することが可能な回路である。180-nm のプロセスルールでは 80psec 程度の時間分解能を得ることが可能である。これより位相差  $\epsilon$  に式(2)の

ように求められる。 $\phi$  E の計算イメージを図 5 に示す。周波数がロックしている状態では、このように $\phi$  E は O (一定値)になる。

$$\phi_{\scriptscriptstyle E} = RR - RV + \varepsilon \tag{2}$$

図3 ADPLLシステムブロック図

Fig. 3. ADPLL system block diagram.

図4 一般的なアナログ PLL

Fig. 4. General analog PLL architecture.

Fig. 5. Concept of calculating  $\phi$  E.

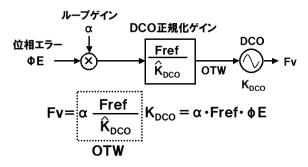

得られた  $\phi$  E は Gain Adjust ブロックにおいてディジタルフィルタを通り、 $K_{DCO}$  の正規化を行った後、DCO の制御信号である OTW (Oscillator Tuning Word) に変換され DCO を変調する。図 6 に Gain Adjust ブロックの内部構成を示す。位相誤差検出の演算によって得られた位相エラー  $\phi$  E は、各モードに対応したループゲイン  $\alpha$  及び  $K_{DCO}$  の正規化の演算が行われ、DCO 制御信号 OTW として各モードに対応したバラクタを制御する。

図6 KDCO調整の構成

Fig. 6. DCO gain adjustment architecture.

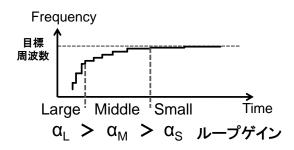

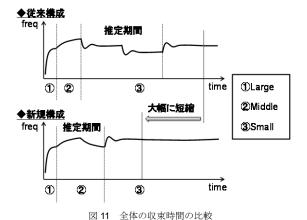

#### 〈2·3〉 チューニングモードの切り替え

ADPLL システムのチューニングはループゲインαを段階的に切り替えることで、収束時間の改善を可能にしている。ループゲインαはシステム全体の動作特性を決定する重要な要素である。ループゲインを小さく設定することで高い収束精度を得ることが可能であるが、収束時間が多くなってしまうというトレードオフが発生する。アナログPLLではループフィルタの定数が回路素子で決定してしまうため、両立させることが困難であった。一方、ADPLLはディジタルフィルタを用いているため、ループゲインをプログラマブルに設定することが可能となった。

位相誤差検出の演算によって得られた位相エラー  $\phi$  E は、各モードに対応したループゲイン  $\alpha$  及び  $K_{DCO}$  の正規化値の乗算が行われ、DCO 制御信号 OTW として各モードに対応したバラクタを制御する。初めループゲインを大きく取り、荒くではあるが高速で目標値付近まで収束させる。次にループゲインを小さくさせていき、徐々に精度を高める。今回は 3 つのモードをとり、それぞれ Large モード、Middle モード、Small モードと呼ぶことにする。(図 7)また、同時に DCO のバラクタにも同様の重み付けを行う。Large モードでは周波数可変範囲を全てまかなえるようにバラクタ容量を大きく取り、Middle と Small モードではその容量を小さくしていき可変範囲を狭めていく。

図7 チューニングモード

Fig. 7. Tuning mode.

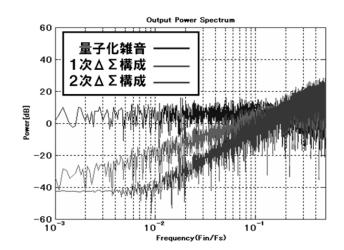

Small モードはチューニングの最終段であり、システムの精度に大きく影響する。より高い精度を実現するため、フラクショナル N 構成を用いる。しかし、フラクショナル

N 構成はシステムの雑音特性にスプリアスをもたらしてしまうが、 $\Delta \Sigma$ 変調を応用したバラクタ制御により図 8 のようにノイズを高周波へとシェイピングする。

図8  $\Delta$   $\Sigma$ 変調の次数による雑音スペクトルの変化 Fig. 8. DSM order effects to noise power spectrum.

#### (2·4) K<sub>DCO</sub>

システム内で値がわからない幾つかの定数に  $K_{DCO}$  がある。 $K_{DCO}$  は DCO 制御信号 OTW の 1LSB 変化に対する発振周波数変化であり、OTW の 1LSB 変化に対する容量分解能  $\Delta C_{1LSB}$  と置くと式(3)で与えられる。発振周波数に依存するため、システムの伝達関数に影響を与えるパラメータとなることがわかる。 $K_{DCO}$  はシステム内のパラメータから推定することが可能であり、逆数としてループゲインと共に乗算することでこの影響をキャンセルすることができる。

$$K_{DCO} = -2\pi \times \Delta C_{1LSB} \times L \times fv^3 \dots (3)$$

#### 〈2·5〉 広帯域化技術

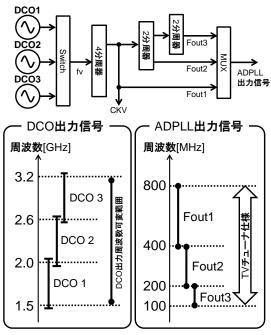

TV チューナの仕様は約 90MHz~800MHz と帯域が広いため、1 つの DCO で周波数範囲をカバーすることが困難である。それは、DCO 回路はバラクタのアレイ構造を除くとほぼアナログ VCO と同様に構成されるため、アナログ VCO と同様に可変容量範囲や回路内部の寄生容量により制限されてしまうためである。そこで複数個の DCO と分周器を組み合わせることでこの仕様を達成する。図 9 に 3 つの DCO 回路及び分周器を用いた場合の構成を示す。各 DCO は Large モードの OTW データを用いて選択され、分周器は外部から制御信号を入力することで切り替えを行い、所望の周波数を得る。

# 〈2·6〉 位相雑音の低減化技術

ADPLL内で発生する雑音成分はTDC量子化雑音、DCO量子化雑音、DCOアナログ雑音の3つに分けられる。アナログPLL回路では要求される周波数の逓倍信号を作り、後に分周させることで低位相雑音化を行う技術が用いられ

る。そこで ADPLL に対して逓倍発振構成が有効であるか検証した。ADPLLの出力周波数の Ndiv 倍である fv'で DCO を発振させ、分周器で Ndiv 分周し ADPLL 出力 fv を得る。一般に DCO 回路のアナログ雑音 NDCO\_a は、Ndiv 分周することで 1/Ndiv<sup>2</sup>倍に低減することが可能である。

図9 広帯域化技術の構成と周波数カバー範囲

Fig. 9. Wideband technique and frequency range.

# 3. K<sub>DCO</sub>推定手法

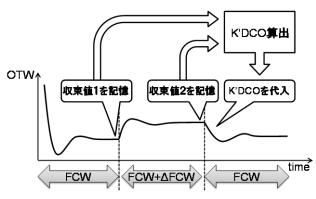

#### 〈3·1〉 従来の KDCO 推定手法

システムの伝達関数への影響から、 $K_{DCO}$ を予め見積もる必要がある。これは、DCO 回路はアナログ回路であるため、発振周波数の変化に加えて PVT ばらつきの影響を受けやすいためである。DCO 制御信号に対する出力周波数 fv の変化を観測することで推定を行うが、周波数を計測することは困難である。そこで周波数の変位に対しての OTW の変化量を計測することでこれを推定する。FCW を微小に変化させた時の出力周波数の変位  $\Delta fv$  は式(4)のようになる。式(3)に代入することで式(5)を得る。これから  $K_{DCO}$ を推定できることがわかる。

$$\Delta fv = \Delta FCW * Fref ..... (4)$$

$$K'_{DCO} = \frac{\Delta FCW * Fref}{OTW2 - OTW1} ..... (5)$$

$K_{DCO}$  の推定を行う際は最後の Small モードで行う。まず  $K_{DCO}$  に初期値を与え、Small モードで収束を確認した後、 FCW を  $\Delta$  FCW だけ変化させた値を入力する。収束を確認後、式(5)より  $K_{DCO}$  を算出し、再び元の FCW で収束させる。 しかし、Small モードはループゲインを小さく設定している ため、収束までに時間がかかってしまい、結果として全体の整定時間が大幅に増加するという問題がある。

図 10 K'DCO 算出手順 (small モード) Fig. 10. Calibration K'DCO.

## 〈3·2〉 提案手法

今回提案する手法は、従来は Small モードで行っていた Kpco の推定を Middle モードで行うものである。Middle モードは Small モードに比べてループゲインが大きいため、収束時間が短いため全体の収束時間を短縮することができると考えられる。しかし Middle モードで推定した DCO ゲイン K'pco\_m は式(6)から分かるように、最小 DCO バラクタ 容量の違いによって値が異なってしまう。そこで Middle モードと Small モードの最小バラクタ容量の比を使って Small モードの DCO ゲイン K'pco\_s に変換する。(式 6)

$$K'_{DCO,s} = \frac{\Delta Cs}{\Delta Cm} K'_{DCO,m}$$

(6)

Fig. 11. Comparison of the whole settling time.

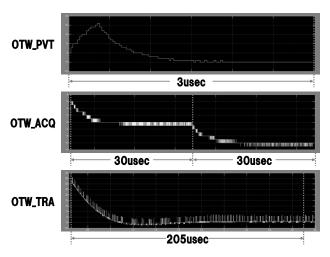

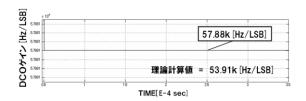

### 〈3·3〉 シミュレーションによる検証

シミュレーションにより提案手法の有効性を検討する。 シミュレーションは MATLAB Simulink で行った。それぞれ Large モード、Middle モード、Small モードにおける OTW を出力したものを図 12 に示す。それぞれ Large = 3 usec、Middle = 30 usec、Small = 205 usec で収束していることがわかる。よって、従来の手法における全体の収束時間は約 630 usec であるが、提案手法では約 260 usec であり、従来構成の半分以下の時間でシステムをチューニングする ことが可能である。また、Kpco の見積もり結果を図 13 に示した。Kpco の理論値とシミュレーションによって求めた値を比較すると一致している。以上の結果から、提案手法の有効性をシミュレーションにより確認することができた。

図 12 各モードの収束時間

Fig. 12. Settling time for each mode.

図 13 K'DCOのシミュレーション結果と理論値の比較

Fig. 13. K'DCO comparison of simulation and theoretical calculation.

### 4. 実装と測定結果

# 〈4·1〉 実装手法

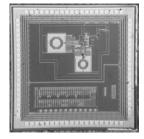

今回の実装方法としてはカスタムチップと FPGA を組み合わせた方法を取る。1 チップに収めたほうが雑音特性などで有利であるが、FPGA を用いることでシステムに変更を施すことが可能となり、実験の幅が広がると考えたためこの構成を取った。DCO は LC-VCO を基本としたアナログ回路であるためチップに搭載する。また FPGA の最大動作周波数は  $100 \mathrm{MHz}$  程度であるため高速動作する回路は組み込めない。そこでチップには高速動作するカウンタ (RV)及び TDC を搭載した。その他の回路ブロックは全て FPGAで作成し、システムの制御を行う。図 14 に試作したチップとその測定基板を示す。チップは  $0.18 \mu$  m CMOS プロセスで試作し、チップサイズは  $2.5 \mathrm{mm} \times 2.5 \mathrm{mm}$  である。

図 14 試作したチップと測定基板

Fig. 14. ADPLL chip and evaluation board.

### 〈4·2〉 測定結果

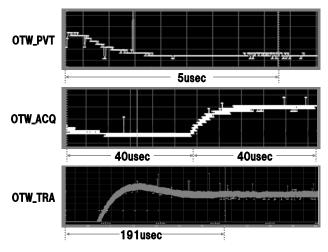

今回の実験では主に  $K_{DCO}$  の推定による高速収束アルゴリズムの検討に着目して行った。それぞれ Large モード、 Middle モード、Small モードにおける OTW を測定した波形が図 15 である。それぞれ 5 usec、40 usec、191 usec で収束していることがわかる。よって、Middle モードでゲイン推定を行った場合は 276 usec であることから、シミュレーションと同等の収束時間となり、提案手法の有効性を測定で確認することができた。

図 12 各モードの収束時間

Fig. 12. Settling time for each mode.

### 5. まとめ

TV チューナ応用のための ADPLL を  $0.18 \mu$  m CMOS プロセスのチップおよび FPGA を用いて設計・実装を行った。このシステムを実測で提案アルゴリズムの有効性を示した。

- (1) ループゲイン切り替えによる高速収束が可能であることを確認した。

- (2) 提案した Kpco 推定手法を MATLAB シミュレーションで確認、実測においても確認した。同様の有効性を確認することができた。

上記の結果から今後は 1 チップ化を目指し、位相雑音特性の向上を行っていく必要があると考えている。また、プ

ロセスの微細化が進むことにより、性能を向上させることができる可能性を確認でき、更に研究を進めていきたいと考えている。

# 文 献

- (1) R. B. Staszewski and P. T. Balsara: "All-Digital Frequency Synthesizer a Deep-Submicron CMOS", Wiley-Interscience(2006)

- (2) R. B. Staszewski: "Frequency Synthesizers in Nanometer CMOS", DCAS SEMINAR, 21 Feb 2007

- (3) B. Staszewski: "All-Digital TX Frequency Synthesizer and Discrete-Time Receiver for Bluetooth Radio in 130-nm CMOS", IEEE Journal of Solid-State Circuits, Vol.39, No.12, Dec 2004

- (4) 田辺朋之・壇徹・小林春夫 他:「TV チューナ用 ADPLL の検討」、 電子情報通信学会大会講演論文集,エレクトロニクス 2, pp.132, 2009