# Vernier Stochastic TDC Architecture with Self-Calibration

Yuta Doi, Satoshi Ito, Shigeyuki Nishimura, Haruo Kobayashi, Nobukazu Takai Department of Electronic, Graduate School of Engineering Gunma University, 1-5-1 Tenjin-cho, Kiryu 365-8515, Japan K\_haruo@el.gunma-u.ac.jp

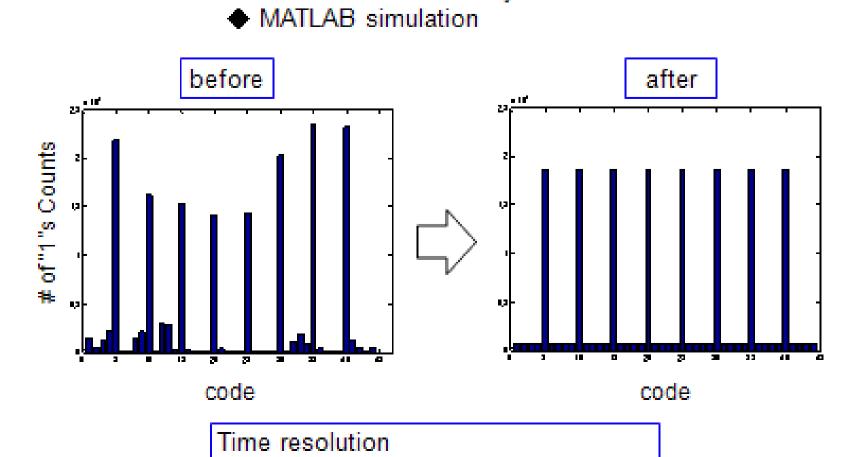

## Simulation Results Self-calibration Results

#### ◆ Stochastic TDC 8 delay buffers

5 DFFs from one delay buffer

Delay buffer >> DFF offset variations

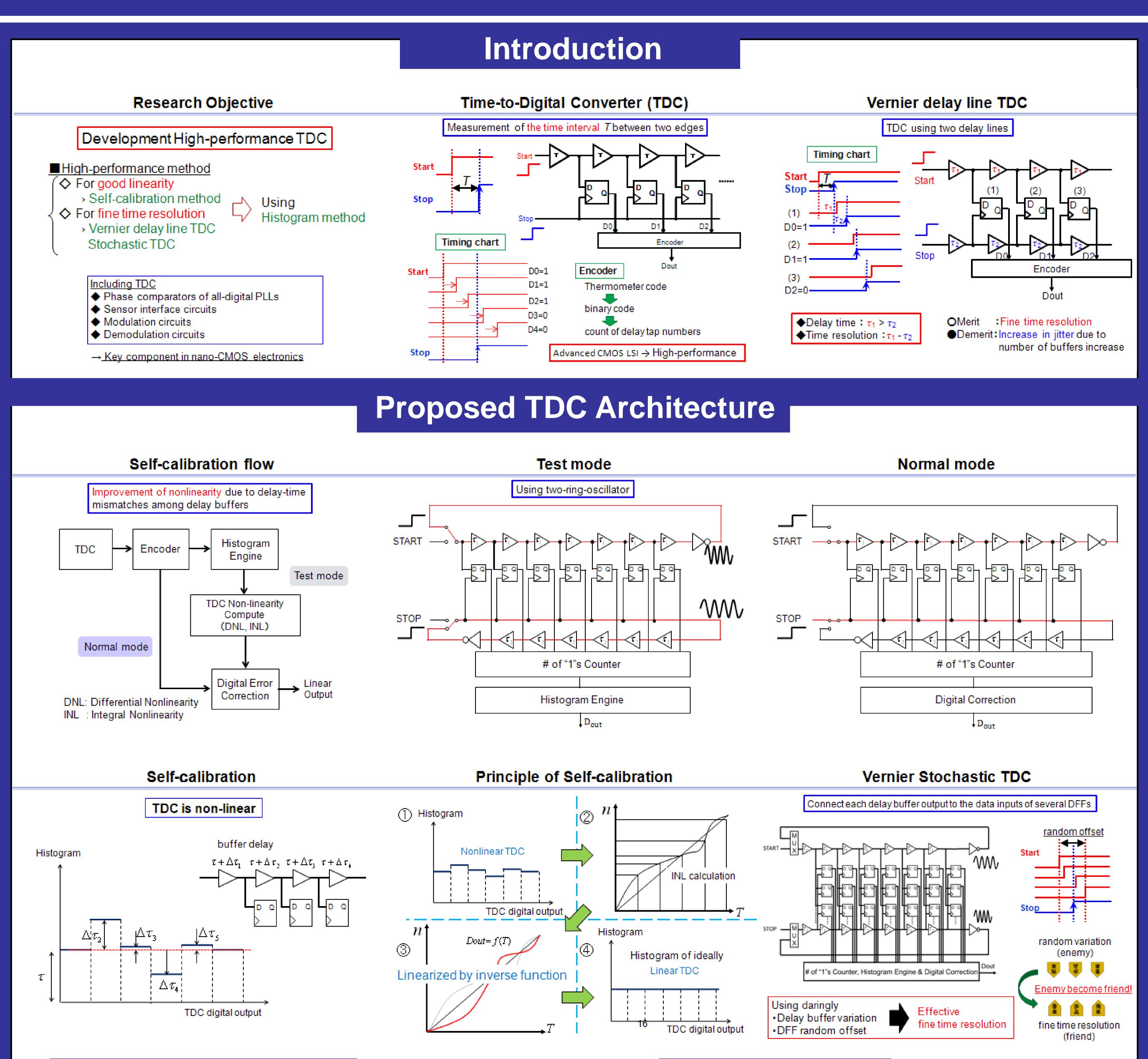

### For good linearity - Self-calibration

♦ For fine time resolution

(using a two-ring-oscillator, signal is "time")

Stochastic topology (using process variations)

Vernier technique (using two delay lines)

Conclusion

as TDC for fine time resolution and good linearity.

■ We propose Vernier Stochastic TDC

All digital circuit

Suitable for advanced fine CMOS implementation

### Summary

- Our Publication

- [1] S. Ito, S. Nishimura, H. Kobayashi, et. al., "Stochastic TDC Architecture with Self-Calibration," IEEE Asia Pacific Conference on Circuits and Systems (Dec. 2010).

- [2] S. Uemori, M. Ishii, H. Kobayashi, Y. Doi, O. Kobayashi, T. Matsuura, K. Niitsu, F. Abe, D. Hirabayashi, "Multi-bit Sigma-Delta TDC Architecture for Digital Signal Timing Measurement", IEEE International Mixed-Signals, Sensors, and Systems Test Workshop (May 2012).