# 高精度・低消費電力サイクリックADCの自己校正法の検討

群馬大学大学院 工学研究科 電気電子工学専攻 情報通信システム第2研究室 劉 羽

# アウトライン

- 研究背景•目的

- Cyclic ADCの基本構造・動作

- 有限ゲイン誤差、容量ミスマッチの影響

- 自己校正アルゴリズム

- シミュレーション結果

- まとめと今後の予定

# アウトライン

- 研究背景•目的

- Cyclic ADCの基本構造・動作

- 有限ゲイン誤差、容量ミスマッチの影響

- 自己校正アルゴリズム

- シミュレーション結果

- まとめと今後の予定

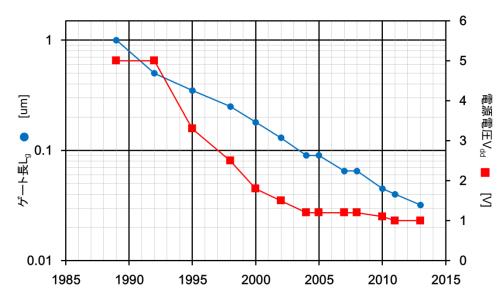

# 研究背景

#### CMOSプロセスの微細化

年代 [year]

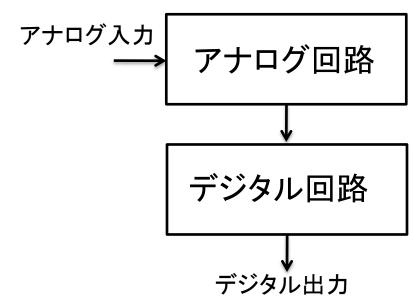

#### デジタルアシスト技術

・デジタル

→ 大きな恩恵(高精度、低消費電力)

-アナログ

- → 必ずしも恩恵を受けない(電源電圧低下)

- ・デジタルアシスト技術 → アナログ回路の性能を向上

#### 研究目的

- ·研究目的

- → 高精度・低消費電力Cyclic AD変換器のデジタル自己校正法

- •Cyclic AD変換器

- → 高精度・回路面積小(メリット)

- ・アンプ低消費電力化、容量を小さくする

- → 回路誤差(有限ゲイン、容量ミスマッチ)

- ・デジタルアシスト技術の応用

- → デジタル自己校正法

# アウトライン

- 研究背景•目的

- Cyclic ADCの基本構造・動作

- 有限ゲイン誤差、容量ミスマッチの影響

- 自己校正アルゴリズム

- シミュレーション結果

- まとめと今後の予定

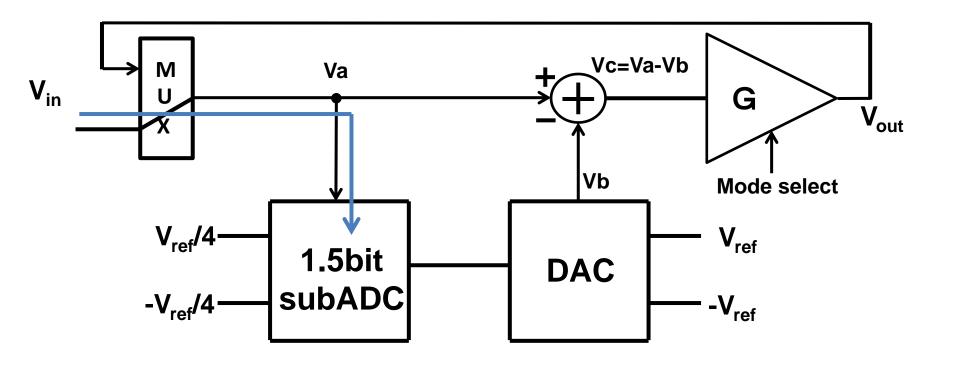

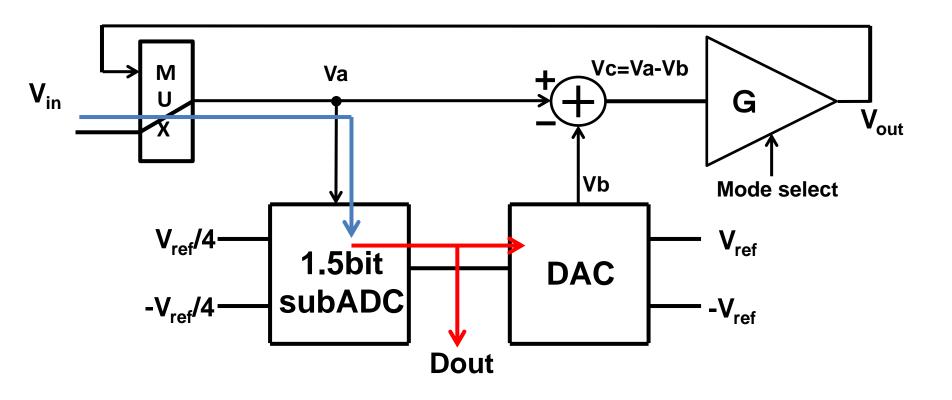

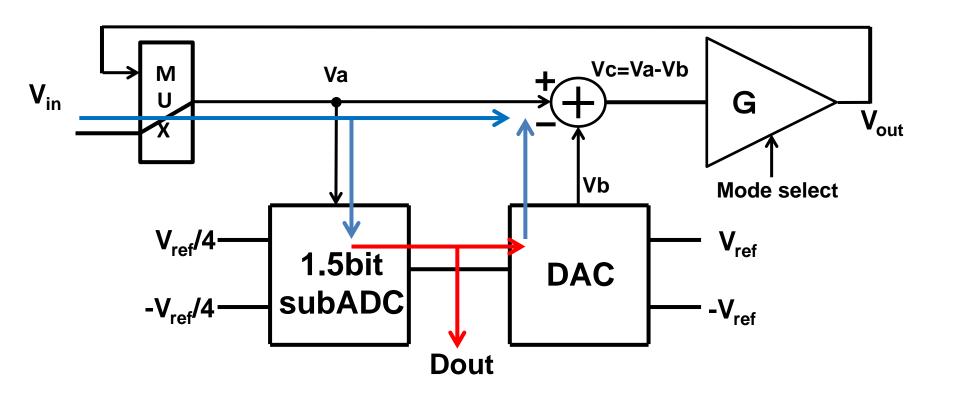

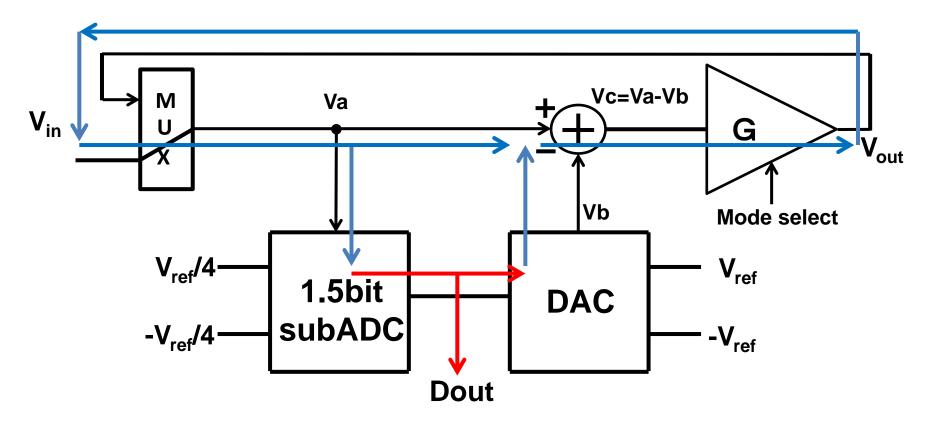

伝達関数(理想)

$$Vout = 2Vin - D * Vref$$

$$D = \begin{cases} 1 & (Vin \ge Vref/4 & Vb = Vref) \\ 0 & (-Vref/4 \le Vin \le Vref/4 & Vb = 0) \\ -1 & (Vin \le -Vref/4 & Vb = -Vref) \end{cases}$$

# Cyclic ADC基本回路

冗長性を考慮し、二つのコンパレータの構造を使用

# アウトライン

- 研究背景•目的

- Cyclic ADCの基本構造・動作

- 有限ゲイン誤差、容量ミスマッチの影響

- 自己校正アルゴリズム

- シミュレーション結果

- まとめと今後の予定

# ADCへの誤差影響

|    | 有限ゲイン誤差 | 容量ミス<br>マッチ |

|----|---------|-------------|

| 理想 | A=無限大   | Cf=Cs       |

| 実際 | A=有限    | Cf≠Cs       |

主な電力が消費される

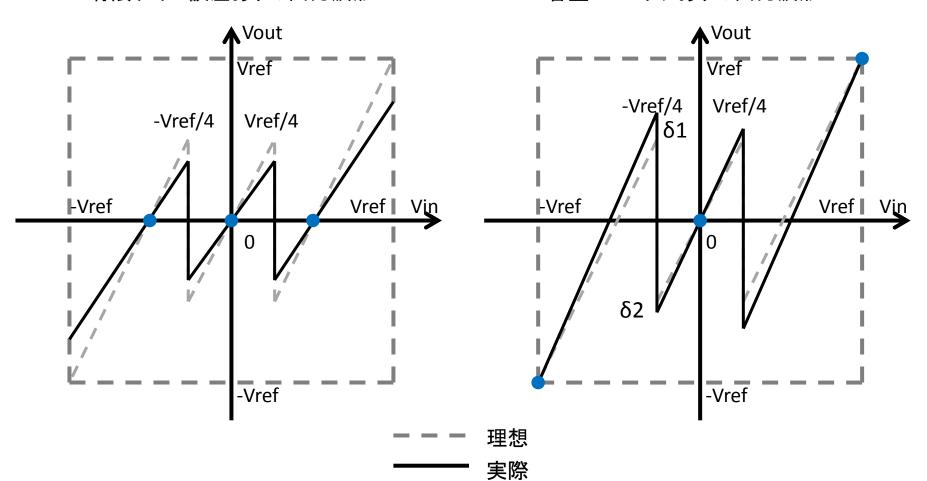

# ADCへの誤差影響

有限ゲイン誤差ありの出力波形

容量ミスマッチありの出力波形

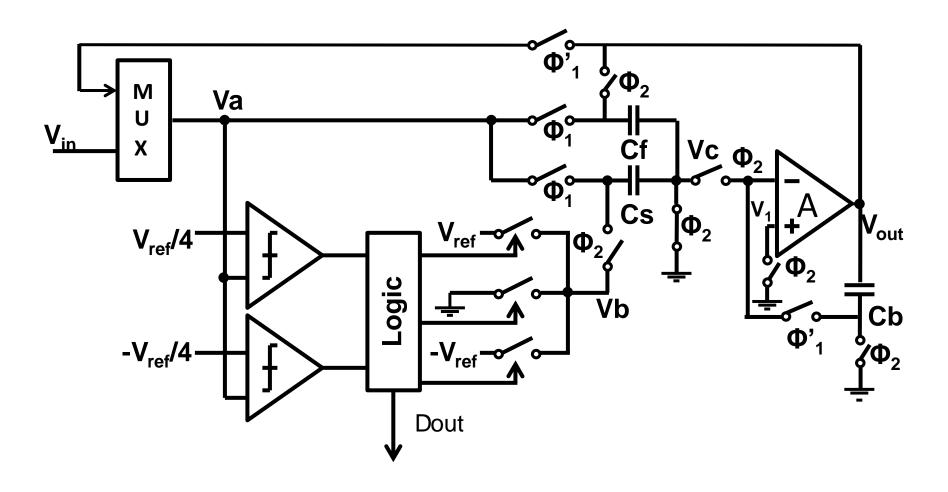

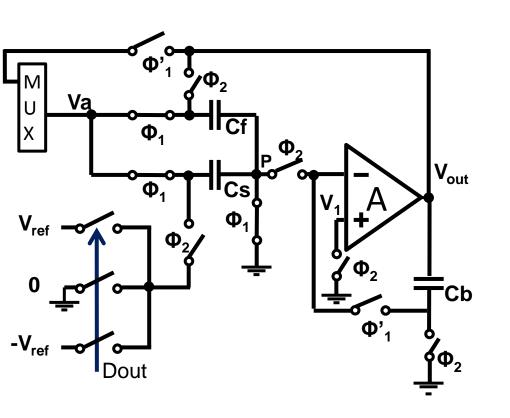

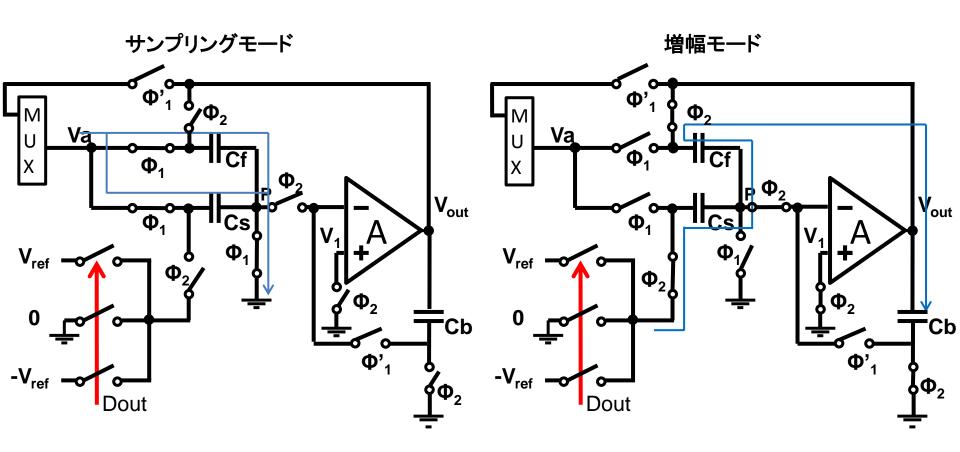

# 乗算型DAC動作

Qf=Vin\*Cf

Qs=Vin\*Cs

2. Q'f=(Vout-V1)\*Cf

Q's=(VDAC-V1)\*Cs

# 乗算型DAC動作

3. 次サイクル Qf=Vin\*Cf Qs=Vin\*Cs 4. 次サイクル Q'f=(Vout-V1)\*Cf Q's=(VDAC-V1)\*Cs

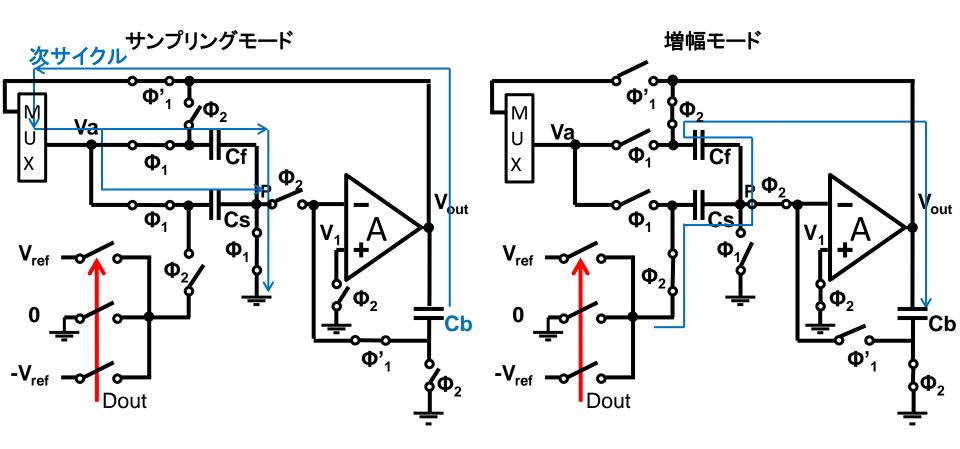

# 伝達関数の導出

#### 点P: 電荷保存則を用い、伝達関数を導出

$$-Qf - Qs = -Qf' - Qs'$$

,  $V1 = Vout/A$

$$-Vin * Cf - Vin * Cs = -(Vout - V1) * Cf - (VDAC - V1) * Cs$$

$$Vout = \frac{Vin - D * VDAC * \frac{Cs}{Cs + Cf}}{\frac{Cf}{Cf + Cs} - \frac{1}{A}} = \frac{\left(1 + \frac{Cs}{Cf}\right)Vin - \frac{Cs}{Cf} * D * VDAC}{1 + \frac{1}{A\beta}}$$

容量ばらつき: em=(Cs-Cf)/Cf 有限ゲイン: efg=1/Aβ A:アンプ利得

β:帰還係数=Cs/(Cs+Cf)

$$Vout = (1 - efg)\{(1 + \frac{em}{2}) * 2Vin - (1 + em)D * Vref\}$$

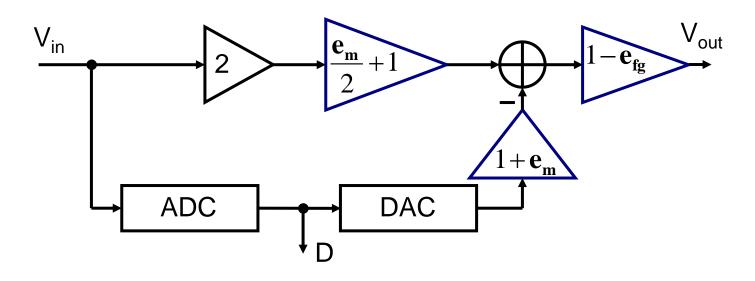

# 伝達関数モデル

(実際)

$$Vout = (1 - efg) \{ (1 + \frac{em}{2}) * 2Vin - (1 + em)D * Vref \}$$

#### アウトライン

- 研究背景•目的

- Cyclic ADCの基本構造・動作

- 有限ゲイン誤差、容量ミスマッチの影響

- 自己校正アルゴリズム

- シミュレーション結果

- まとめと今後の予定

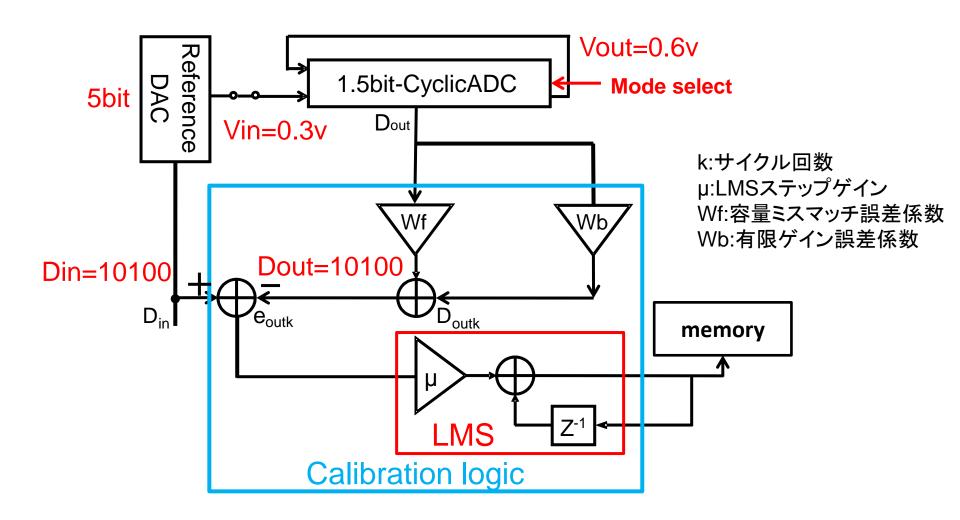

# 提案自己校正のアプローチ

自己校正モード

・高電力モード ──> 容量ミスマッチを測定

・通常モード ──→ 有限ゲイン誤差を測定

通常動作モード

・システム通常動作 ―― 自己校正を行う

# 提案自己校正のアプローチ

システムの分解能と合わせるリファレンスDACを使用

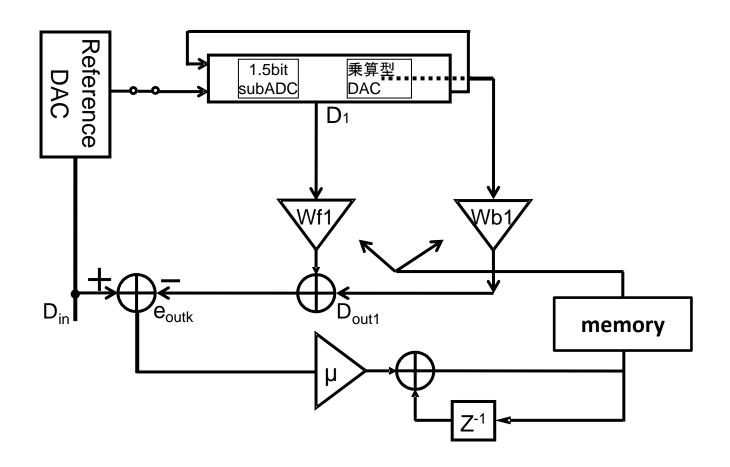

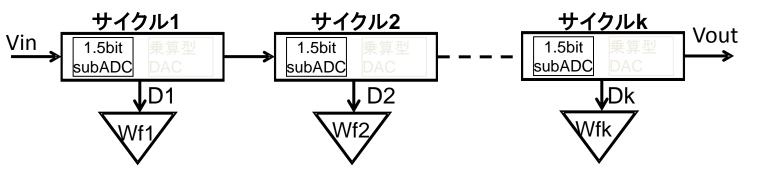

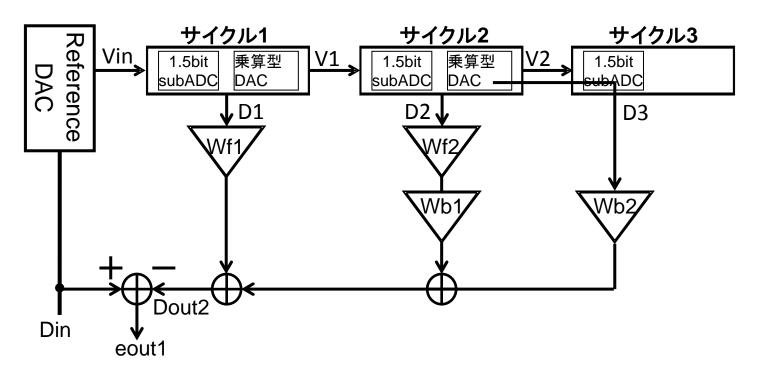

# 自己校正システムの1サイクル動作

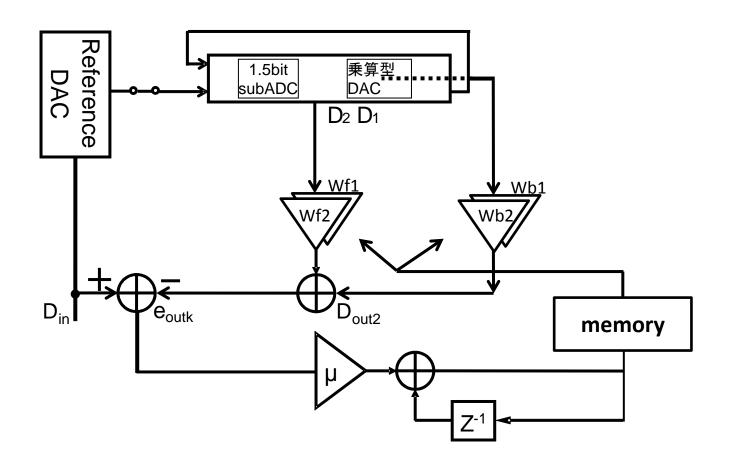

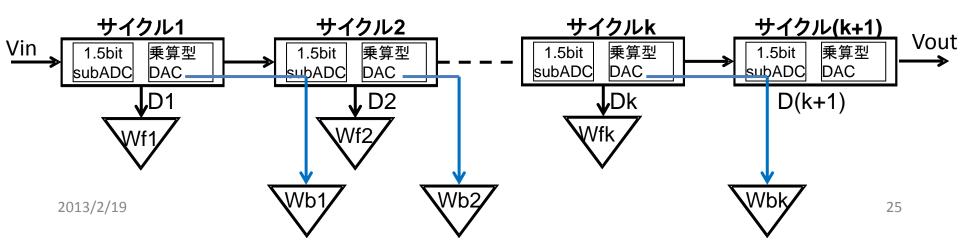

# 自己校正システムの2サイクル動作

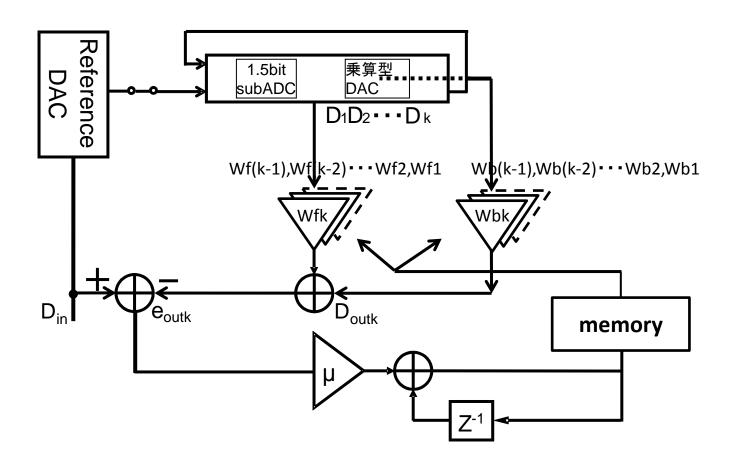

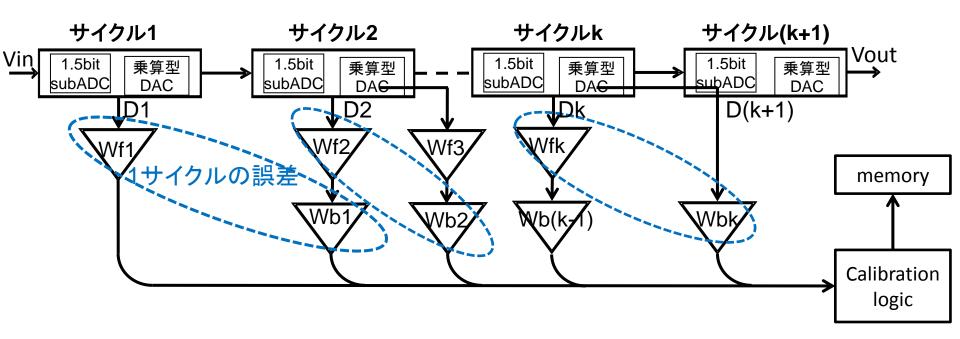

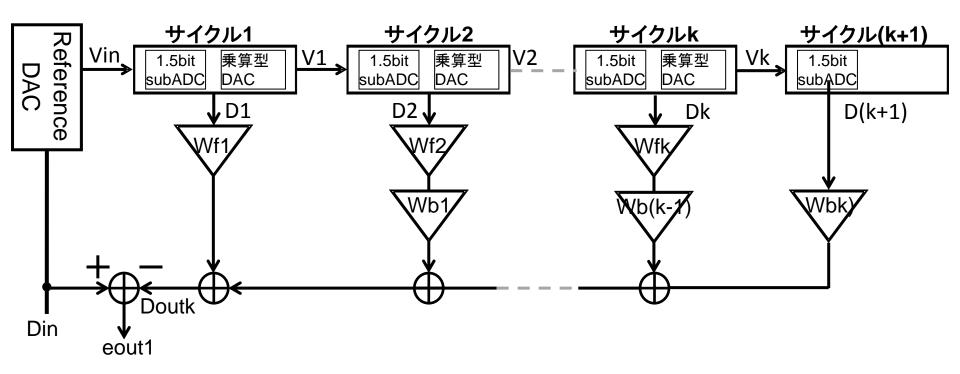

# 自己校正システムのkサイクル動作

# 回路誤差の測定

・システムが高電カモードとなり、オペアンプの利得が無限大一→ 回路誤差は容量ミスマッチのみ

・システムが通常モードに戻り、容量ミスマッチ誤差を除き→ 有限ゲイン誤差Wb

# 回路誤差の分析

- ・高電カモード → 容量ミスマッチ補正係数Wf(k)

- •通常モード → 有限ゲイン補正係数Wb(k)

2013/2/19 26

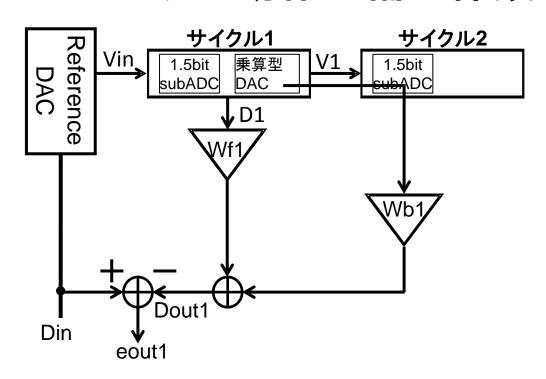

```

Dout1=Wf1*D1+Wb1*V1

V1=(1-efg)[(1+em/2)*2*Vin-(1+em)*D1*Vref]

Vref=1

```

```

eout1 = Din-Dout1 \\ = Vin-Wf1*D1-Wb1*(1-efg)\{(1+em/2)*2*Vin-(1+em)*D1*Vref\} \\ = Vin[1-Wb1(1-efg)(1+em/2)*2] + D1[Wb1(1-efg)(1+em)-Wf1]

```

・eout1=0 → Wf1とWb1が最適に収束 | Wb1=1/2(1-efg)(1+em/2) | Wf1=(1+em)/2(1+em/2)

#### 最急降下法(LMS)

$Wb(k+1) = Wb(k) + \mu(eoutb1) = Wb(k) + \mu\{Vin-Wb(k)2(1-efg)(1+em/2)Vin\}$   $Wf(k+1) = Wf(k) + \mu(eoutf1) = Wf(k) + \mu\{D1(1+em)/2(1+em/2) - Wf(k)\}$

29

```

eout2=Din-Dout2

=Vin-Wf1*D1-Wf2*Wh1*D2-Wh2*V2

=Vin-Wf1*D1-Wb1*Wf2*D2-Wb2(1-efg)\{[(2(1-efg)(1+em/2))^2]*Vin-efg)\}

(1+em/2)2(1-efg)(1+em)D1-(1+em)D2

=Vin\{1-Wb2[2(1-efg)(1+em/2)]^2\}

+D1\{Wb2*[(1-efg)^2]2(1+em/2)(1+em)-[(1+em)/(1+em/2)*2]\}

+D2\{Wb2(1-efg)(1+em)-Wf2/[(1-efg)(1+em/2)2]\}

・eout2=0 → Wf2とWb2が最適に収束

Wb2=1/[2(1-efg)(1+em/2)]^2

Wf2=(1+em)/2(1+em/2)

Wb(k+1)=Wb(k)+\mu(eoutb2)=Wb(k)+\mu(eoutb2)

Wf(k+1)=Wf(k)+\mu(eoutf2)=Wf(k)+\mu(eoutf2)

```

```

Doutk=Wf1*D1+Wf2*Wb1*D2+Wf3*Wb2*D3+ · · · Wfk*Wb(k-1)*Dk+Wbk*D(k+1)

Vk=(1-efg)[(1+em/2)*2*V(k-1)-(1+em)*Dk*Vref]

Vref=1

```

```

eoutk=Din-Doutk

=Vin-Wf1*D1-Wf2*Wb1*D2-Wf3*Wb2*D3 · · · -Wfk*Wb(k-1)*Dk-Wbk*D(k+1)

・eoutk=0 → WfkとWbkが最適に収束

Wbk=1/[2(1-efg)(1+em/2)]^k

Wfk=(1+em)/2(1+em/2)

Wb(k+1)=Wb(k)+\mu(eoutbk)=Wb(k)+\mu(eoutbk)

Wf(k+1)=Wf(k)+\mu(eoutfk)=Wf(k)+\mu(eoutfk)

```

# アウトライン

- 研究背景•目的

- Cyclic ADCの基本構造・動作

- 有限ゲイン誤差、容量ミスマッチの影響

- 自己校正アルゴリズム

- シミュレーション結果

- まとめと今後の予定

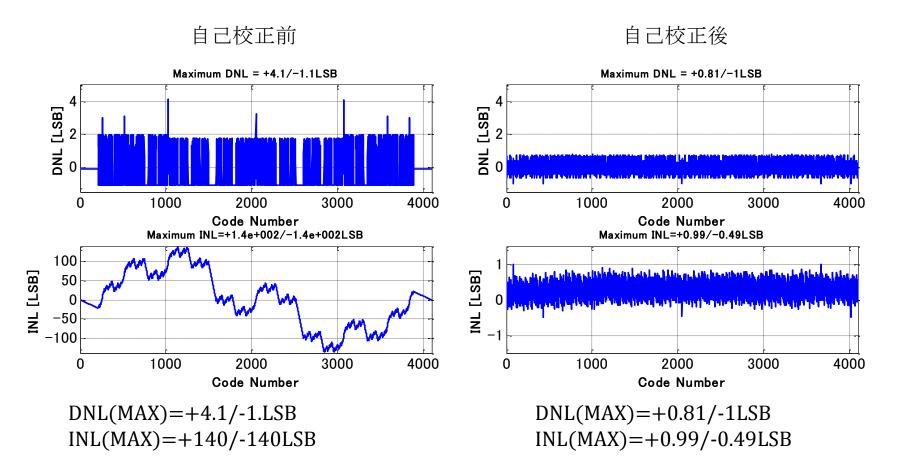

# シミュレーション結果

分解能:12bit

サンプリング周波数=2^16

Vref=1

ステップゲイン: μ=1/128

有限ゲイン誤差: efg=0.14

容量ミスマッチ誤差: em=0.02

ADCの線形性が良くなったことが分かった

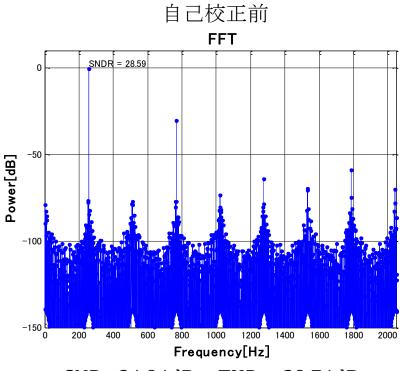

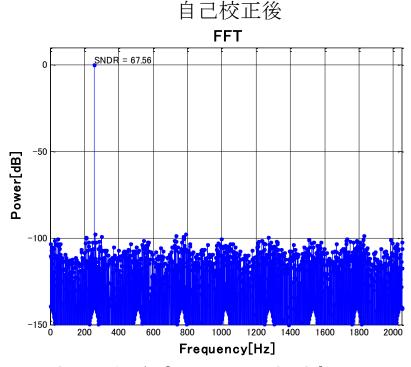

# シミュレーション結果

分解能:12bit 入力周波数=255 Vref=1  $\lambda = 1/128$

有限ゲイン誤差: efg=0.14 容量ミスマッチ誤差: em=0.02

SNR=34.94dB THD=-29.74dB SNDR=28.59dB ENOB=4.46Bit

SNR=67.57dB THD=-97.8dB SNDR=67.56dB ENOB=10.93Bit

有効bit数は4.46bitから10.93bitに大きく改善した

# アウトライン

- 研究背景•目的

- Cyclic ADCの基本構造・動作

- 有限ゲイン誤差、容量ミスマッチの影響

- 自己校正アルゴリズム

- シミュレーション結果

- まとめと今後の予定

# まとめ

- Cyclic ADCの誤差係数が規則的だと数学モデルで確認した。

- サイクル数が増えるにつれて、後段サイクルの有限ゲイン誤差が0に近づく。

- 有限ゲイン誤差、容量ミスマッチがある時、自己校正ができた。

# 今後の予定

■ オペアンプの非線形性まで考慮し、ADCのデジタル自己校正の効果を確認。