## シグマデルタTDCを用いた位相ノイズ測定手法(1) - システムレベル検討 -

◎大澤優介 針谷尚裕 平林大樹新津葵一 小林修 山口隆弘 小林春夫

群馬大学 名古屋大学 半導体理工学センター(STARC)

### **Outline**

- 研究背景、目的

- ΣΔTDCを用いた位相ノイズ測定原理

- Matlabを用いたシミュレーション

- まとめと今後の課題

### **Outline**

- 研究背景、目的

- ΣΔTDCを用いた位相ノイズ測定原理

- Matlabを用いたシミュレーション

- まとめと今後の課題

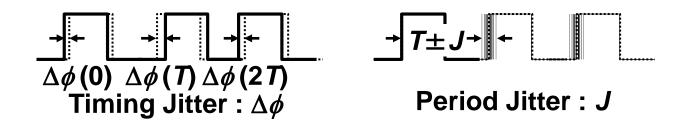

## 研究背景

位相ノイズを持つクロックはシステムの誤動作の原因となる

クロックの位相ノイズ、ジッタの測定・テスト

通信システム、ADCの高性能化において重要

## 研究背景

### クロックの位相ノイズ、ジッタの測定・テストの問題点

- ・ 測定に長時間かかる

- スペクトルアナライザが必要

非常に高価!!

LSIの量産時のテストのためには...

たくさんのスペクトル アナライザが必要

大幅にコスト増加!!

## 研究目的

スペクトルアナライザを用いず位相ノイズ、ジッタを測定・テストする

低コストの位相ノイズ、ジッタ測定を可能にする!

### **Outline**

- 研究背景、目的

- ΣΔTDCを用いた位相ノイズ測定原理

- Matlabを用いたシミュレーション

- まとめと今後の課題

# ΣΔTDCを用いた位相ノイズ測定の提案

#### **ΣΔΤDC**

線形性:良

回路規模:小

時間分解能:高

ディジタル演算で周波数特性が得られる

チップ内テスト容易化回路による低コスト・高品質テストの実現が可(BIST: Built-In Self Test)

外部に端子を接続する必要がない

Ш

さらなる位相ノイズがのる心配がない

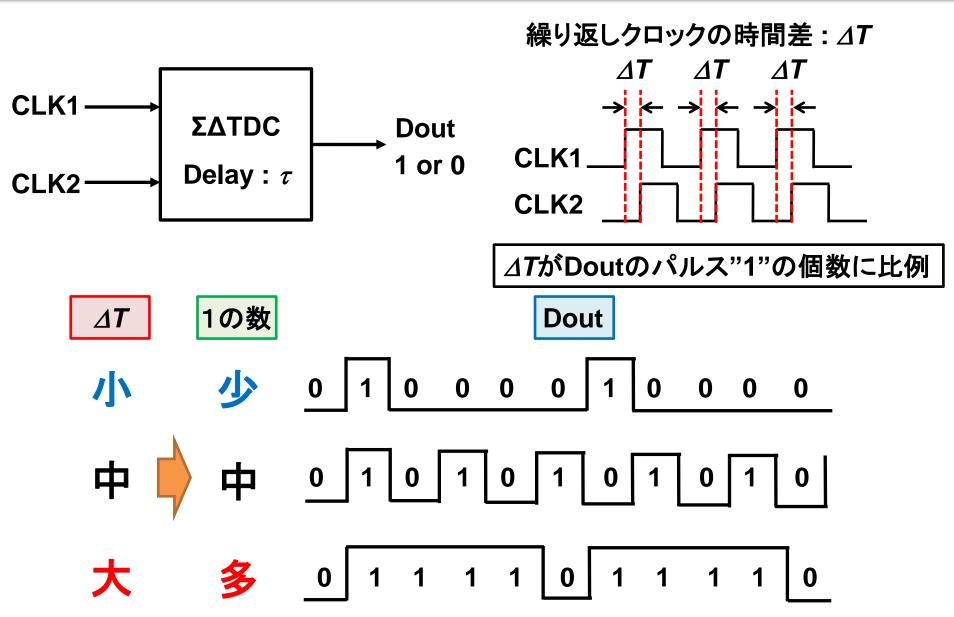

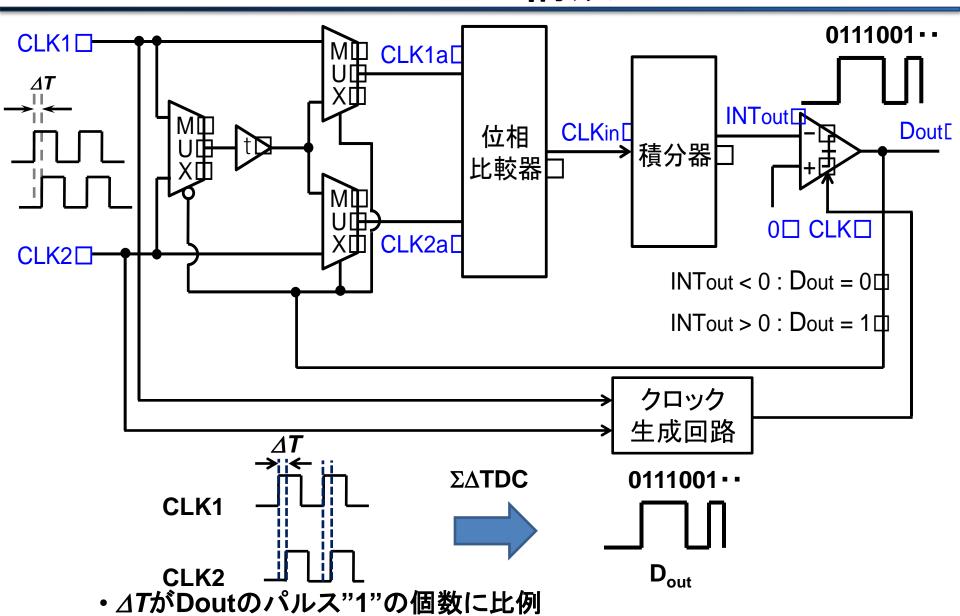

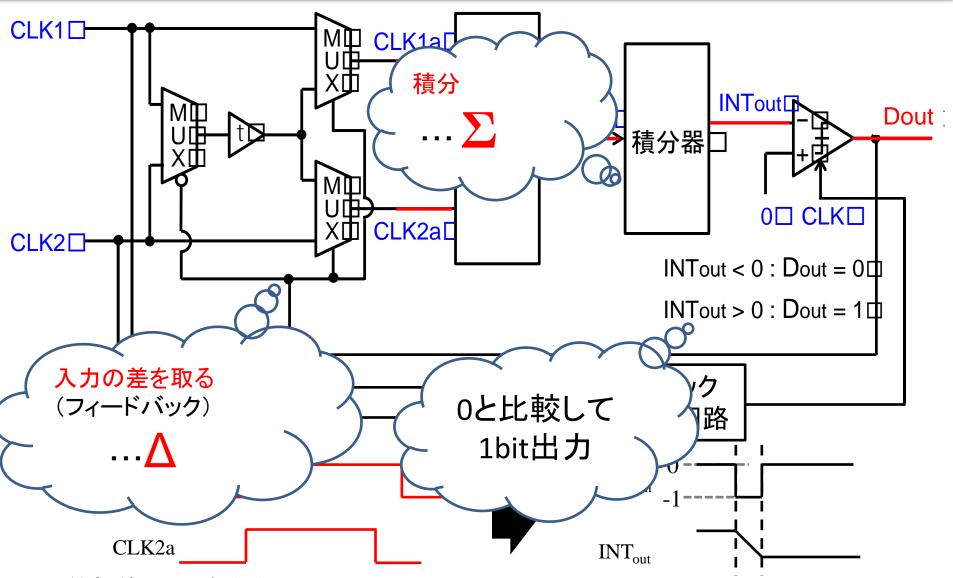

### ΣΔTDCの原理

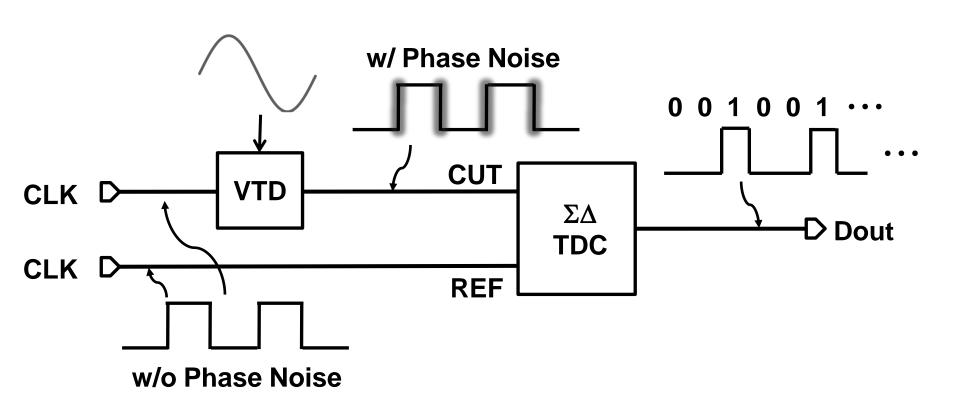

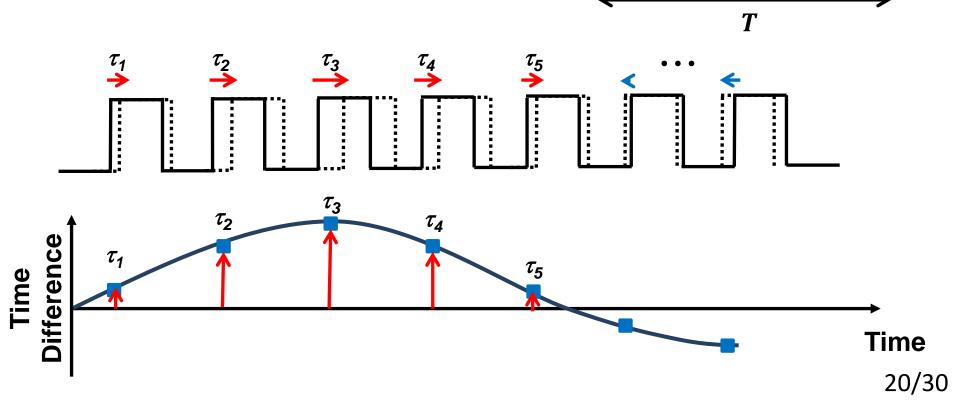

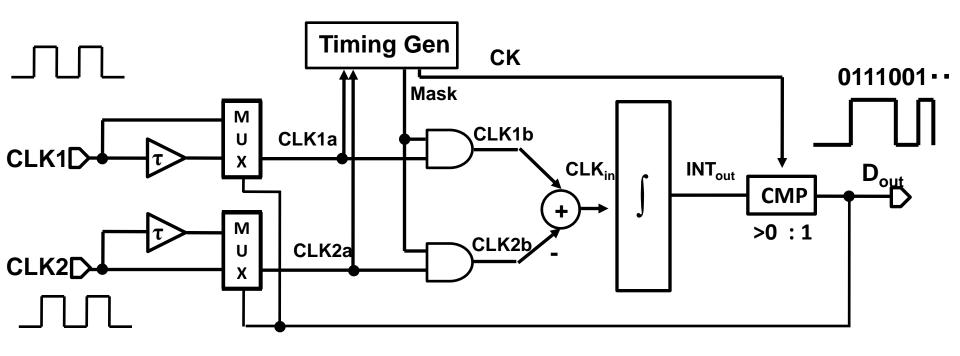

# ΣΔTDCを用いた位相ノイズ測定原理

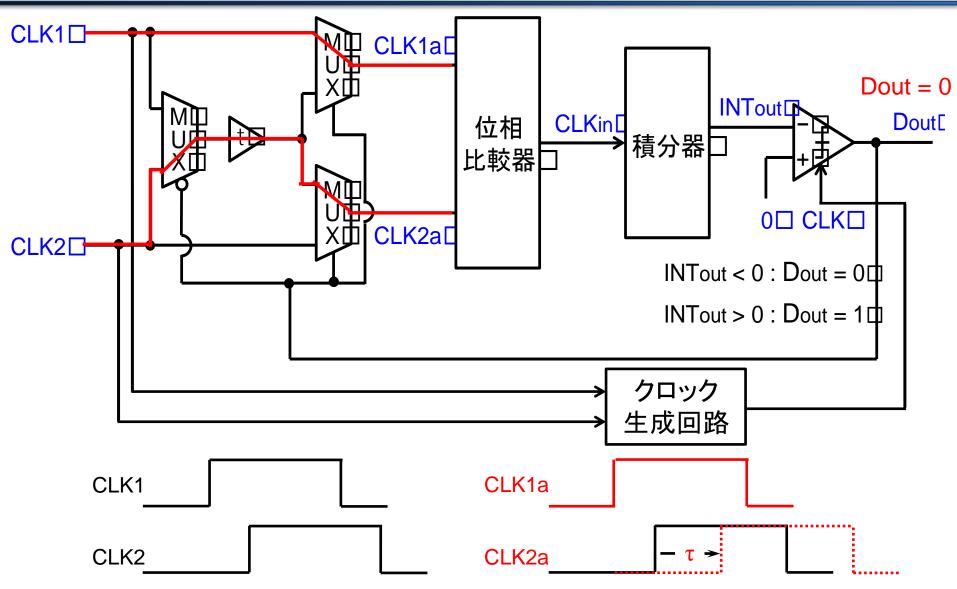

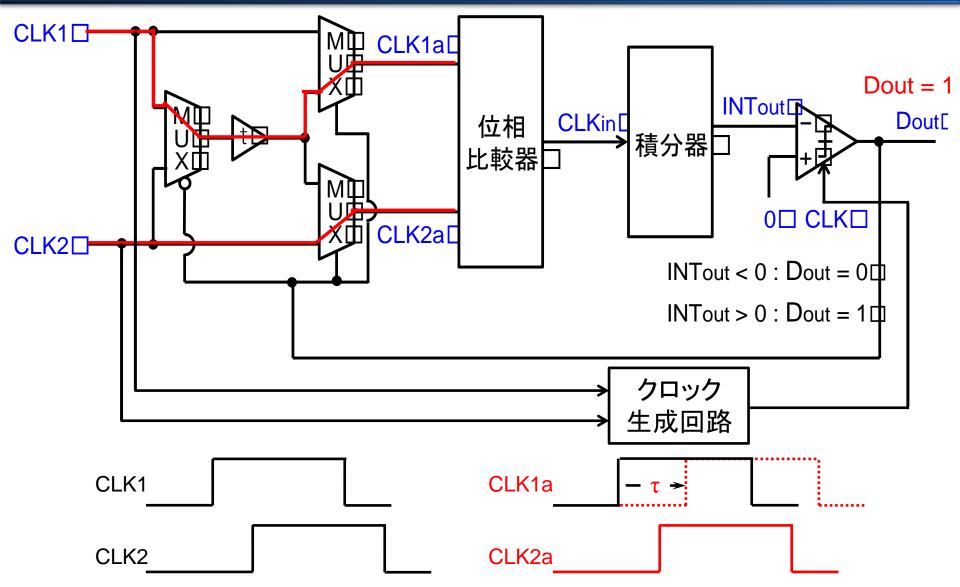

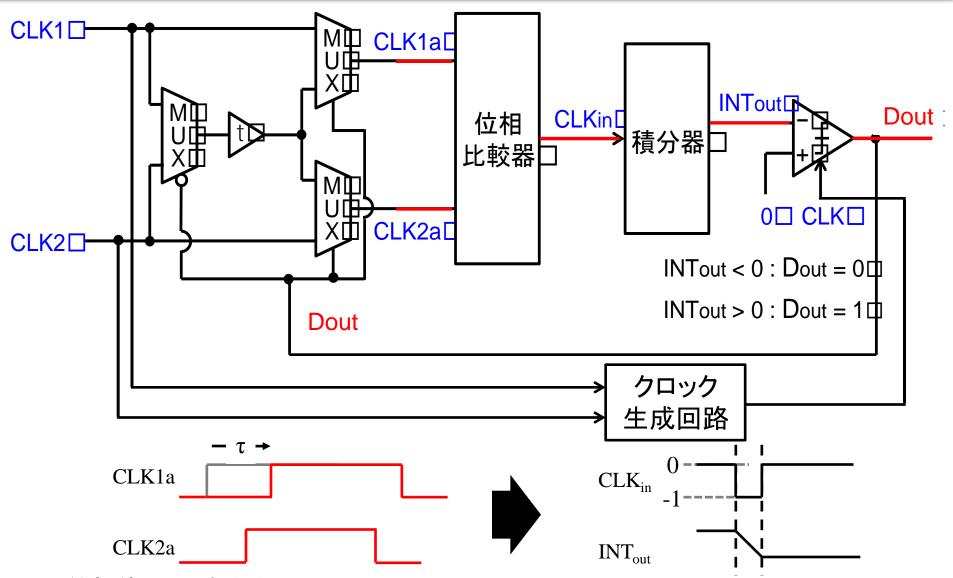

# ΣΔTDCの構成

・測定可能範囲:-τ < ΔT < τ</li>

- ・CLK1とCLK2を入力

- ・比較器出力により経路選択 → CLK1a, CLK2aを得る

- ・CLK1とCLK2を入力

- ・比較器出力により経路選択 → CLK1a, CLK2aを得る

- ・位相差CLK<sub>in</sub>を出力

- ・比較器でINT $_{out}$ を0と比較し、出力 $D_{out}$ を得る  $\rightarrow$  次のクロックでの経路を制御

- ・位相差CLK<sub>in</sub>を出力

- ・比較器でINToutを0と比較し、出力Doutを得る → 次のクロックでの経路を制御

# 位相ノイズ測定の数式議論

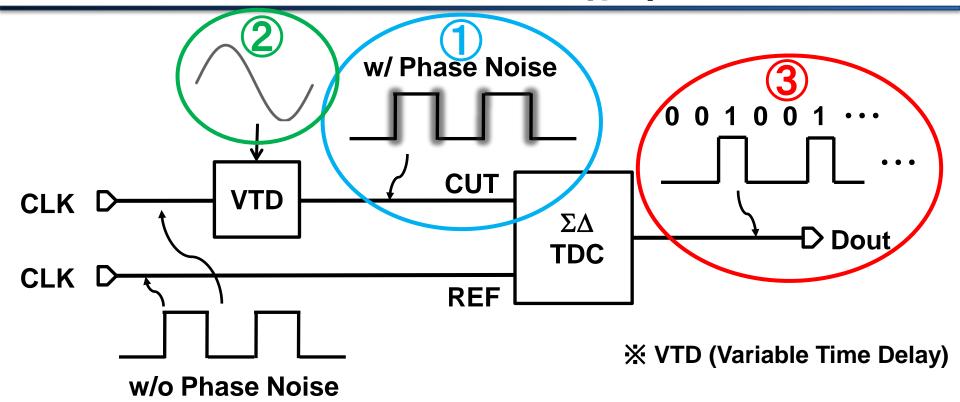

**VTD**: Variable Time Delay

# 位相ノイズ測定の数式議論

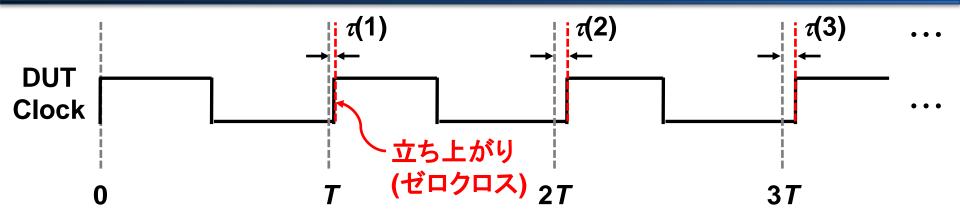

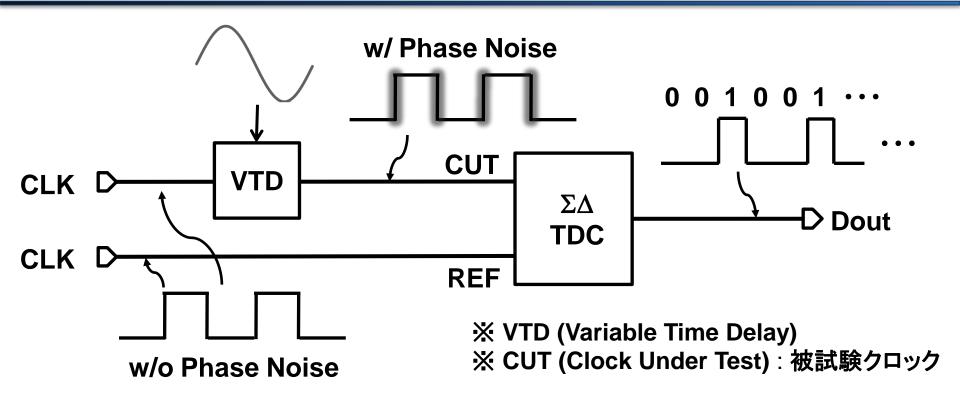

クロックの正弦波近似

$$clock(t) \approx \sin(2\pi f_{in}t + \phi(t))$$

$f_{in} = \frac{1}{T}$

立ち上が $\eta$ エッジのゼロクロス点変動関数:  $\tau(m)$

m: number of edges

立ち上がりエッジのm番目のゼロクロス

$$2\pi f_{in}(mT + \tau(m)) + \phi(mT) = 2\pi m$$

$$\therefore \phi(mT) = -2\pi f_{in}\tau(m)$$

: 位相ノイズ(時間領域)

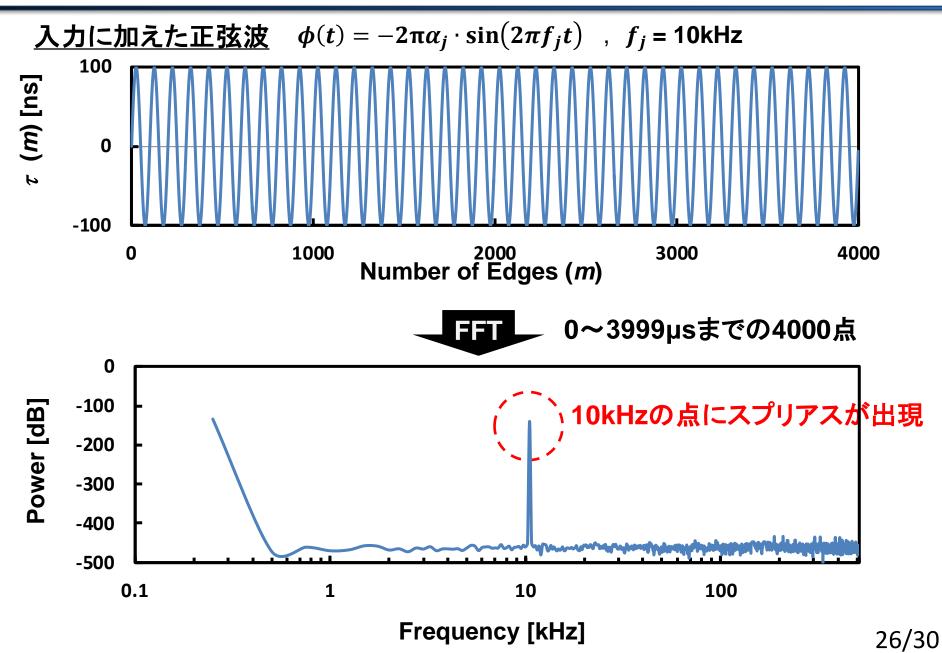

①  $\tau(m) = T \cdot \alpha_j \cdot \sin(\omega_j mT)$  の場合(単一正弦波の位相変動)  $0 \le \alpha_j \le 1$   $\phi(mT) = -2\pi f_{in}\tau(m) = -2\pi\alpha_j \cdot \sin(\omega_j mT)$ :位相ノイズ(時間領域)  $\Phi(\omega_j) = \frac{1}{2}(2\pi\alpha_j)^2$ :位相ノイズ(周波数領域)

### **Outline**

- 研究背景、目的

- ΣΔTDCを用いた位相ノイズ測定原理

- Matlabを用いたシミュレーション

- まとめと今後の課題

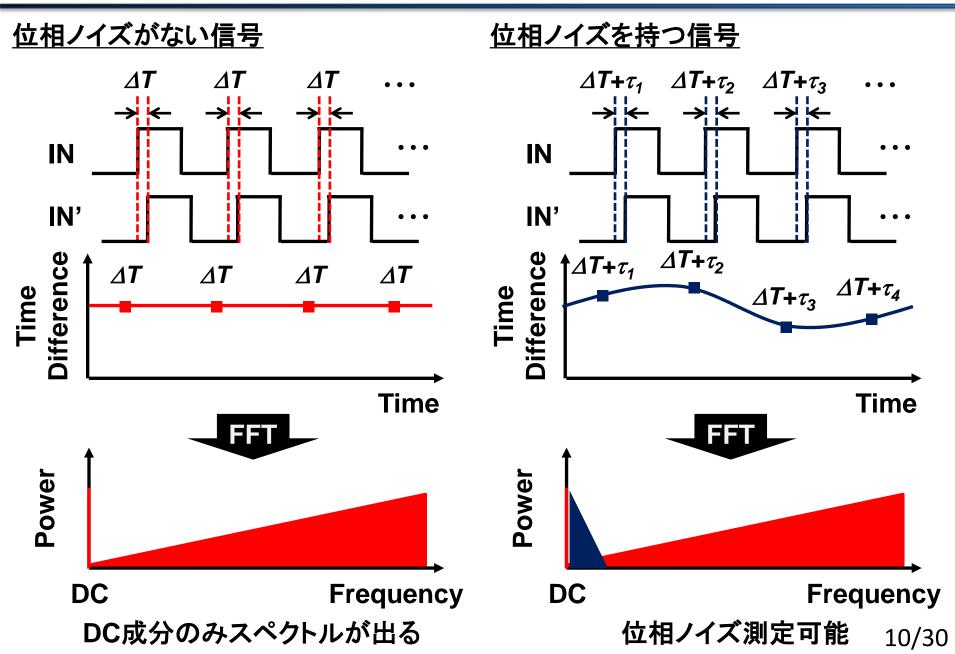

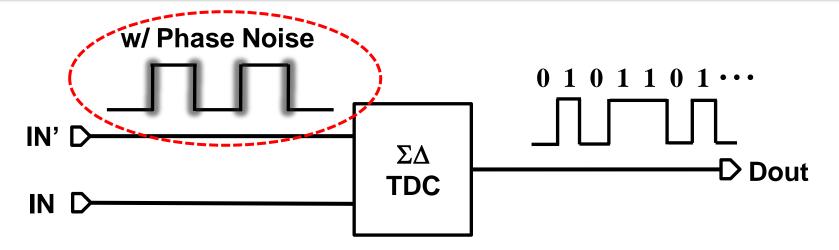

## シミュレーションによる位相ノイズ測定

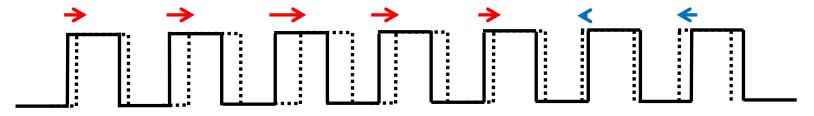

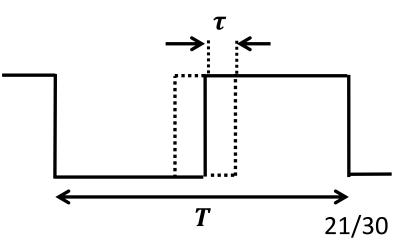

IN'に位相変動を与えることで疑似的な位相ノイズを実現する

正弦波の位相変動をあたえる

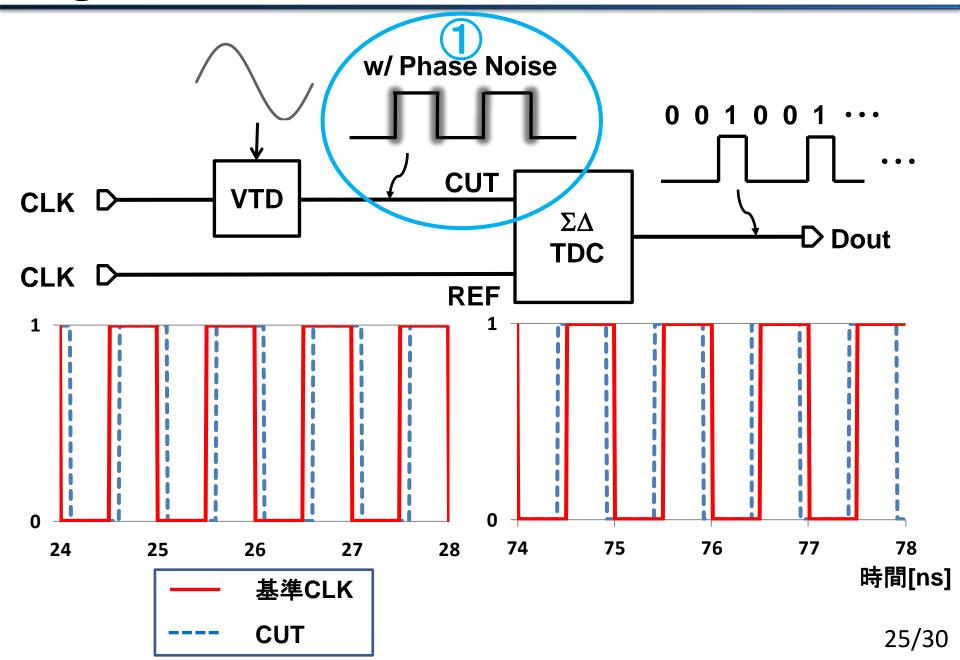

実線:基準CLK 点線:位相変動後CLK

# シミュレーション条件

#### Matlab (Simulink) によるシミュレーション

● CLKの周波数: f<sub>in</sub> = 1 MHz (T = 1 µs)

#### 正弦波の位相変動

- 周波数: f<sub>i</sub> = 10kHz

- 位相変動:  $-0.1 \mu s \le \tau \le 0.1 \mu s$

### 位相変動の加え方

#### Matlab ( Simulink ) によるシミュレーション

● CLKの周波数: f<sub>in</sub> = 1 MHz (T = 1 µs)

正弦波の位相変動

- 周波数: *f<sub>i</sub>* = 10kHz

- 位相変動: $-0.1 \mu s \le \tau \le 0.1 \mu s$

# ΣΔTDCのシミュレーション時の構成

# シミュレーション条件

| 入力周波数 |       | 1 MHz  |

|-------|-------|--------|

| 位相ノイズ | 単一正弦波 | 10 kHz |

| データ点数 |       | 4096   |

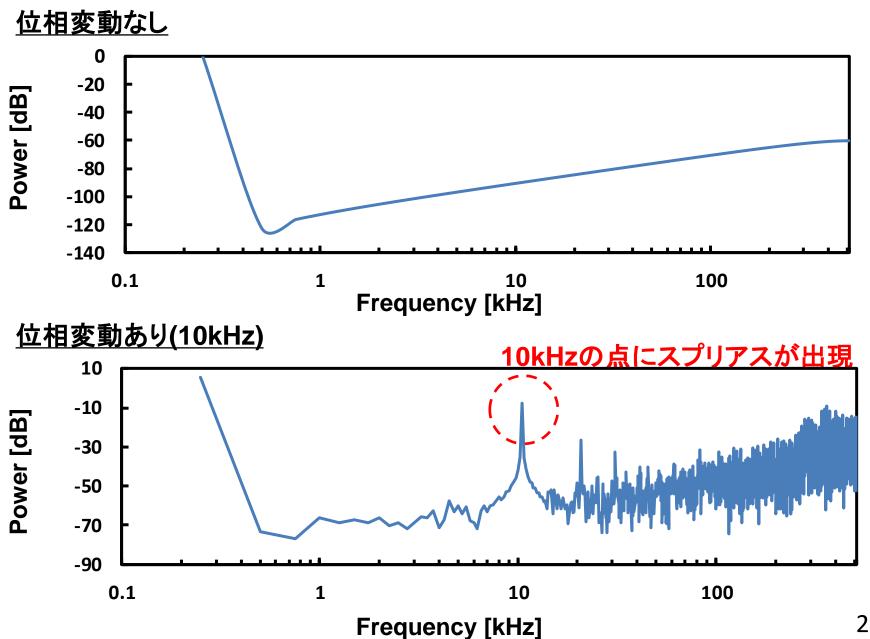

## シミュレーション結果

- ① 位相変動後のCUT(被試験クロック)を測定

- ② ③のFFT結果と比較するために測定

- ③ 出力Doutを測定

# ① 位相変動後の被試験クロックの波形

# ② 入力CLKに与えた位相変動正弦波のFFT

# ③ ΣΔTDC出力信号

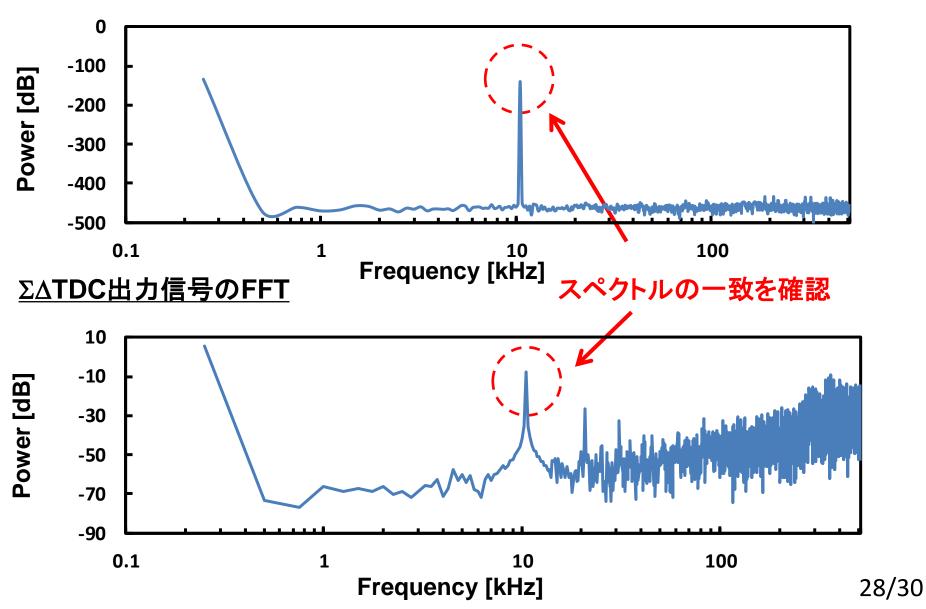

## 入力CLK信号とΣΔTDC出力信号の比較

#### 入力CLK信号のFFT

### **Outline**

- 研究背景、目的

- ΣΔTDCを用いた位相ノイズ測定原理

- Matlabを用いたシミュレーション

- まとめと今後の課題

## まとめと今後の課題

### まとめ

- ∑∆TDCを用いた位相ノイズ測定の原理を提案した

- ・ この手法よりスペクトルアナライザを用いない安価な測定が可能

- ・ オンチップで測定できるので高性能な測定が可能

- 提案手法の正当性をMatlabを用いたシミュレーションで確認した

- 単一正弦波の位相変動で、その周波数成分にスプリアスがでていることを確認

- 入力信号の位相ノイズと出力信号の位相ノイズのスペクトルとの一致を確認

### 今後の課題

- 出現したスプリアスのパワー(大きさ)についての数式的議論

- 外部からの参照クロックが必要ない手法の検討

### **Outline**

- 研究背景、目的

- ΣΔTDCを用いた位相ノイズ測定原理

- Matlabを用いたシミュレーション

- まとめと今後の課題

- Q&A

## 卒業論文発表 - 2013年2月27日-

- 位相ノイズのモデルとして正弦波を用いたのはなぜ?

- ・ 位相ノイズを測定する場合、周波数特性が重要であるため

- ホワイトノイズのようなものを測定する場合、様々な周波数のノイズが検出される。 単一周波数のものが検出できれば複数の周波数のものも検出できると考え、その 代表として正弦波を用いた。

- 出力のFFT結果の高周波のノイズは何か?

- コンパレータで発生する量子化ノイズ

## 電気学会発表 - 2013年3月1日-

- 従来のFlash型TDCよりもどの程度分解能は良いのか?

- ・ 下の式のように時間をかければかけるほど分解能が高くなる

$$R = \frac{2\tau}{N_{DATA}}$$

- 実装に関しては今後どうするのか?

- ・ 他の回路も検討し、さらにシミュレーションを行なってから実装もしていきたい