# フィボナッチ数列を用いた DA 変換回路

楊 志翔\* 小林 佑太朗 シャイフル ニザム ビン モーヤ 小林 春夫 (群馬大学)

Digital-to-Analog Converter with Fibonacci Sequence Weighted Current Sources

Zhixiang Yang\*, Yutaro Kobayashi,

Shaiful Nizam Bin Mohyar, Haruo Kobayashi, (Gunma University)

**キーワード**: フィボナッチ数列, 電流源 DAC, ミスマッチ, 冗長性, スプリアス化, グリッチ, 線形性 (Keywords, Fibonacci Sequence, Current Steering DAC, Mismatch, Redundancy, Spurious, Glitch, Linearity)

#### 1. 研究背景

エレクトロニクス分野でデジタル信号処理技術が著しく 進歩しつつある。通信システムで基本的な構成回路として Digital-Analog-Converter (DAC)がますます重要になって おり、更なる高性能化が望まれている。現在、DA変換器分 野においてバイナリ(Binary)ならびにユナリ(Unary)に基 づく回路の改善を通して線形性及び低スプリアス化の報告 例が多い。電流源 DA 変換器は回路構造が簡単、高速、チップ面積が小さいという特徴がある。本論文ではフィボナッチ数列を用いた電流源 DA 変換回路を提案し、伝統的なバイナリ型との比較検討を行った。

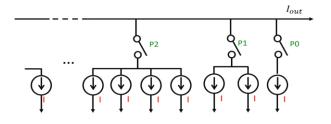

### 2. バイナリ型電流源 DAC

電流源を用いる DAC は電流源と直列の素子が、電流の流れを妨げないために高速性を実現できる。 100MS/s 以上の DAC は、ほとんどこの構成である。バイナリ型電流源 DAC は、 $2^{N-1}$ 個単項電流源を N 部分に分け、バイナリの形になるように合わせ、N 個スイッチを用いて制御する(図 1)。この DAC におけるデコーダ回路が不要であるのでチップ面積が小さい。

図1 バイナリ型電流源 DAC

図1において出力電流は、

$I_{\text{out}} = \sum_{i=0}^{N-1} D_i 2^i I$  (2.1)

となる、 $D_i$ が1のとき i番目のスイッチをオンする。2進重み付電流源 DAC において、各電流源には微小な電流のミスマッチが存在し、それらが出力電流の誤差となり、DAC の

線形性を劣化させてしまう。線形性に影響を与える要因はもう一つがある、これはグリッチ(glitch)であり動的な線形性を劣化させる。グリッチ(glitch)は入力デジタル信号の変化に対応したアナログ出力の変化に追随して発生する。重み付電流源 DAC において、スイッチの変化とデジタル入力の変化は比率ではないので、ハーフスケールのところに、僅か1LSB を変化して、全てのスイッチの ON/OFFが変化する。グリッチインパルスはフル・スケール電圧になり、入出力特性が一時的に非単調性を持つように見える。

グリッチの影響を軽減するために、DAC の後ろで T&H (track-and-hold) 回路を加える方法がある。この方法では DAC の分解能が高くなると、T&H 回路が要求する性能に足りない。この方法は分解能が低い場合にのみ有効である。 グリッチ対策として最も効果的な構成は、グリッチ振幅が小さい並列加算電流源 DAC ならびに抵抗ストリング型である、しかしながら、チップ面積が大きくなるという新たな問題が起こり得る。

通信デバイスの送信回路部では発生される信号周波数帯域以外の妨害波が一定値以下であるように規格を満たすことが要求される。また計測器の信号発生器では低スプリアスで純度の高い信号を発生することが求められている。スプリアス(spurious)は、入力信号には存在しないにも関わらず、出力信号には現れるノイズ・レベルを超える周波数成分である。バイナリ型DACにおいて、電流源の間のミスマッチによって、出力では信号成分だけでなくイメージ信号も生じさせる。これは送信器の場合はほかのチャンネルへの妨害波となり、信号発生器の場合はスプリアス成分となる。この問題を軽減するためには可変アナログ・バンドパス・フィルタなどが必要であるが、そのためにコスト、消費電力が大きくなってしまう。

本研究は、線形性を向上ならびに低スプリアス化のために、フィボナッチ数列を基づいて、電流源 DAC を設計する。

# 3. フィボナッチ数列

フィボナッチ数列とは以下の漸化式で定義される数列である、(1202年にフィボナッチが発行した「算盤の書」(Liber Abaci)に記載された数列である)。

$$F_{0} = 0;$$

$$F_{1} = 1;$$

$$F_{n+2} = F_{n} + F_{n+1}$$

(1)

初めの項を計算すると、

0,1,1,2,3,5,8,13,21,34,55,89,144,233,377,610,987,1586,2583,4180 ... となる。すなわち隣り合う二項の和になる数列である。この数列が一般的にも注目され一つの理由として、n番目が無限に近づけば、n+1番目の数がn番目の数で割ったものが、「黄金比」(golden ratio)の大きい方の数に収束する。

$$\lim_{n \to \infty} \frac{F_{n+1}}{F_n} = 1.618033 \dots \tag{2}$$

この黄金比は、古代ギリシア以来「神の比」としてもてはやされる。人間にとって最も安定し、美しい比率とされ、建築や美術的要素の一つとされる。

フィボナッチ数列は隣り合う数が約1.6倍で変わらないために1.6進とみなすことができる。フィボナッチ数列は適度な冗長性をもっていることに加えて、それを整数で実現できるという特性を保っている。DACの重み付は整数である必要があるが、一般的に整数の小数倍は小数となってしまうので、四捨五入を行うと一定比率(一定の進数)を維持することができない、だから、整数項と一定の項比率を維持することができるフィボナッチ数列は、DACの重み付け方法として非常に有効と考えた。

# 4. フィボナッチ数列の電流 DAC への応用

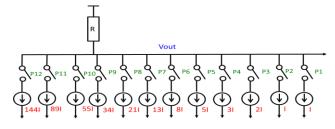

フィボナッチ数列を用いたアルゴリズムの応用として、電流源 DAC を考える。図 2 に示しているように、フィボナッチ数列を基づく、8 ビットの電流源 DAC を設計する。伝統的な8 ビットのバイナリ型電流源 DAC と比べると、提案した8 ビット重み付電流源 DAC はフィボナッチ数列の性質にしたがって、4 ステップを増やす、冗長性を得ることができ、フィボナッチ数列の特性ならびに冗長性を利用して、バイナリ型がもってない優位性がある。

図 2 提案するフィボナッチ数列を基づいて電流源 DAC 〈4·1〉 電流源の校正

各電流源には微小な電流のミスマッチを改善するため、 フィボナッチ数列の特性、隣り合う二項の和が次の項になる、

## $I_{k+2} = I_{k+1} + I_k (3)$

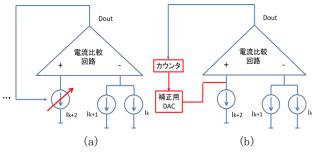

となるこの特性を用いて、電流源の重みを順番に校正することができる、アナログ校正は図 4(a)に示している。式(3)が成立するように $I_{k+2}$ のバイアス電圧を自動調整する

図4(a)アナログ校正;(b)デジタル校正 式(3)が成立するように、補正用DACのデジタル入力を自

式(3) か成立するように、補止用 DAL のテンタル人力を自動調整する。基準は $I_1 = I + \Delta I_1$ の場合、校正すると次のようになる。

- $I_2 = I + \Delta I_1$

- $\bullet I_3 = 2I + 2\Delta I_1$

- $I_4 = 3I + 3\Delta I_1$

- .

#### • $I_{12} = 144I + 144\Delta I_1$

各アナログ出力値は $I_N=NI+N\Delta I_1$ となり、N は出力したい値である。 $\Delta I_1$ を選択にしたがって、線形性の改善、単調性を確保することができる。

# 〈4・2〉 電流源の選択を用いて、線形性を改善

提案したアーキテクチャでは、適度な冗長性を持つように電流源の大きさを定めているので、各望むアナログ出力に対して入力のデジタル信号の表現方法が複数個存在することになる。例えばデジタル入力9のとき ON にするスイッチの組み合わせは次のようになる。

- ① (P5, P4, P1) 5I+3I+I=9I

- ② (P5, P4, P2) 5I+3I+I=9I

- ③ (P5, P3, P2, P1) 5I+2I+I+I=9I

- ④ (P6, P1) 8I+I=9I

- (5) (P6, P2) 8I+I=9I

要するに、組み合わせは5つあり、表現されたアナログ出力はすべて9Iである。すなわち、5つの組み合わせの中で一つを選び場合、9Iを得ることができる。しかしながら、電流源のミスマッチによる、実際値は9Iからずれる。一般に各電流源の間のミスマッチが異なるため、ずれも違う。

5つの組み合わせの中で、ずれが少ない組み合わせを選択すると、理想値 9I に近づく、このように、各理想的なデジタル出力のコースの中で、ずれが少ない組み合わせを選択すれば線形性を向上できる。ずれが少ない組み合わせを選択するため、

- ① はじめに、各組み合わせの大小関係を測定

- ② 次に真ん中のものを選択する

要するに、各組み合わせの大小関係を測定する方法が必要である。

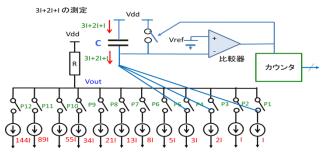

各組み合わせの大小関係を計測する回路は図5のように 構成する。

図5 3I+2I+Iを測定する回路の動作

ステップ①、時間 t=0 でスイッチを 0N する、C を初期化 する。比較器のマイナス端は Vdd になる、カウンタは動作しない。

ステップ②、時間 t>0 でスイッチ 0FF する、C に充電する、比較器のマイナス端は Vdd - Q/C になる。カウンタは動作をはじめ、0 を出力する。

ステップ③、時間 T に経って、Q=(3I+2I+1)T から、Vdd-Q/C=Vref、カウンタの出力は0から1になり。それあと、カウンタが止まり、リセットする。

ステップ④、測定する電流源は P5+P1 に変わる、C を初期 化する、比較器のマイナス端は Vdd になる、カウンタが動 作しない。

ステップ(S)、スイッチ OFF する、(C) に充電する、比較器のマイナス端は Vdd - Q/(C) になる。カウンタは動作をはじめ、(C) を出力する。以下繰り返す。

$$V_{dd} - \frac{Q}{C} = V_{ref}$$

$$Q = I_{in}T \tag{4}$$

にしたがって、

$$T = \frac{(V_{dd} - V_{ref})C}{I_{in}}$$

(5)

となり、Iinは測定される総電流値である。

式(5)による、 $V_{\rm dd}$ 、 $V_{\rm ref}$ 及び Cは定数のため、 $I_{\rm in}$ が大きければ、比較器プラス端とマイナス端の電圧値が等しくなる時間 T は短い、逆に、 $I_{\rm in}$ が小さければ、T が長い、カウンタの出力値の中で0 が多い。すなわち、カウンタの出力値の中で0 が少ないほど、電流値が大きくなる。このように、一つのデジタル入力に対して各組み合わせの大小関係を知ることができる。

各組み合わせを大きい順に並べ、真ん中のものを選択すると、INLが小さくなり、線形性を向上できる。

## 〈4・3〉 電流源の選択を用いて、グリッチを抑える

4ビットの2進重み付け DAC を例にとると、デジタル入力が0010から0011に遷移するときに内部で切り替わるスイッチの数は少ない。そのため、グリッチは感知できないほど微小なレベルとなる。一方、0111から1000(デジタル入力に対する出力アナログ値はフル・スケール出力の1/2になる)に変化するときには全てのスイッチが切り替わるため、最大のグリッチインパルスが生じる。

グリッチを抑えるため、クロック周期ごとに切り替わるスイッチの数は少なくなると、グリッチが小さくなる。しかしながら、バイナリ型は一つの望むアナログ出力に対して唯一のデジタル入力を持っているため、この方法を利用することができないである。提案するアーキテクチャにおいて、適度な冗長性を持っているために、一つの望むアナログ出力に対して入力デジタルコードの表現方法が複数個存在する。スイッチのオンになっているものが多いものを選択すると、別のデジタル信号を入力する場合、そのまま保持するスイッチが存在する可能性が大きい、切り替わるスイッチの数が少なくなって、グリッチを小さくできる。

# (4・4) 電流源の選択でミスマッチを周波数拡散 低スプリアス化のために、デジタル的手法の一つである イナミック・マッチング法を用いる。提案するアーキテ

ダイナミック・マッチング法を用いる。提案するアーキテクチャでは、一つのアナログ出力に対応するデジタル入力が複数個存在することになるので、電流源のスイッチをカウンタにしたがって切り替えるダイナミック・マッチング法を用いて、各電流源の間のミスマッチによって生じるスプリアス成分が周波数拡散されスプリアスのピークが減少し、低スプリアス化を実現する。

## 5. 提案方式の効果のシミュレーション検証

提案手法の有効性を確認するため Matlab を用いて、10 ビット15ステップの提案する DAC のいくつかの場合でシ ミュレーションを行った。

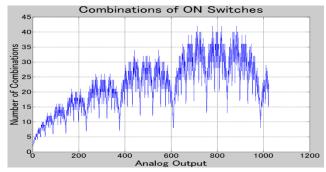

〈5・1〉 冗長性の確認

図 6 一つのアナログ出力に対応するデジタル入力の数  $0\sim1$  0 2 3 において、各アナログ出力に対応するデジタル入力の種類は等しくないことは図 5.1 に通じて知られる。 0 を除く、最小は 2 種類、最大は 4 2 種類がある。提案する DAC は冗長性を持っていることが証明できる。

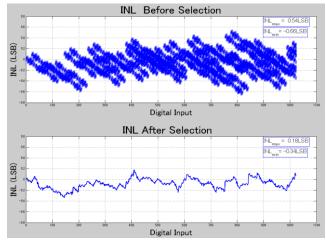

〈5・2〉 電流源の選択を用いて、線形性改善の確認 図7に示すようには選択する前に INL の最悪値は 0.66LSB である、選択すると、最悪値は 0.34LSB に変えることに示している。示している例で、約48%改善しまいました。表1に示しているように、五つケースの平均改善値は32%に達成してしまう。したがって選択に通じて、線形性を改善す

〈5・3〉 電流源の選択を用いたグリッチ抑制の確認表2から、入力波の周波数を増加する場合は切り替わるスイッチの数も増加する、しかしながら、スイッチのオン

ることができることが確認できる。

表1 選択前後で INL の変化

|         | Case1before | Case1after | Case2before | Case2after | Case3before | Case3after | Case4before | Case4after | Case5before | Case5after |

|---------|-------------|------------|-------------|------------|-------------|------------|-------------|------------|-------------|------------|

| INL_max | 0.29        | 0.07       | 0.10        | 0.05       | 0.29        | 0.13       | 0.54        | 0.18       | 0.52        | 0.31       |

| INL_min | -0.96       | -0.80      | -1.08       | -0.81      | -0.94       | -0.66      | -0.66       | -0.34      | -0.34       | -0.19      |

| 絶対値     | 0.29        | 0.07       | 0.10        | 0.05       | 0.29        | 0.13       | 0.54        | 0.18       | 0.52        | 0.31       |

|         | 0.96        | 0.80       | 1.08        | 0.81       | 0.94        | 0.66       | 0.66        | 0.34       | 0.34        | 0.19       |

| 最大値     | 0.96        | 0.80       | 1.08        | 0.81       | 0.94        | 0.66       | 0.66        | 0.34       | 0.52        | 0.31       |

| 改善      | 17%         |            | 25%         |            | 30%         |            | 48%         |            | 40%         |            |

| 平均改善    | 32%         |            |             |            |             |            |             |            |             |            |

になっているものが多いものを選択する場合、入力波の周波数の変化にかかわらず選択したコードの切り替わるスイッチの数は最小である。したがってスイッチのオンになっているものが多いものを選択と、切り替わるスイッチの数は一番少ないことがわかる、そのため、グリッチも一番ちいさくなる。

図7 選択前後の INL

表 2 入力波の周波数と切り替わるスイッチ数

| frequency(GHz) | average | selected | max    | min    | improve to min | improve to average |

|----------------|---------|----------|--------|--------|----------------|--------------------|

| 0.1011         | 104851  | 86707    | 107827 | 93919  | 8%             | 17%                |

| 0.2011         | 108467  | 92109    | 112308 | 99526  | 7%             | 15%                |

| 0.3011         | 114676  | 103607   | 121333 | 110731 | 6%             | 10%                |

| 0.4011         | 116716  | 105633   | 122572 | 110551 | 4%             | 9%                 |

| 0.5011         | 119275  | 107701   | 122630 | 114781 | 6%             | 10%                |

| 0.6011         | 120343  | 108529   | 123843 | 116513 | 7%             | 10%                |

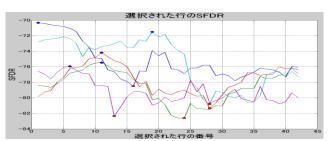

〈5·4〉 電流源のダイナミック・マッチング法の有効性 D確認

同じ区間で5つの乱数を生じる、5つのケースとみなす、ケースが行を基準として区分けして、各行のSFDRを求める。SFDR の値を図8に示す。

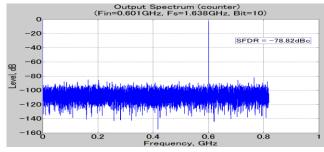

図8の中で、青い点は各ケースの最悪のSFDRの値である、赤の正方形は最良値である。図8より各ケースで、電流源のミスマッチが違うために、最悪また最良値を表す横軸の値もばらついている。量産プロセスにおいて、最良値を求めれば、各DACの電流源のミスマッチの値を測定することが必要、しかも選択するコードが個別に設置しねばならない、実用的ではない。ここで、カウンタを用いて、低スプリアス化を実現する。図9はカウンタを用いて、求められるSFDRを表す。

図 8 5 つの場合の SFDR

図9 DAC の出力スペクトル

このケースの曲線はブルーの線である、この曲線に表される最大値ならびに最小値は-80.79dBc と-71.51dBc である。カウンタを用いて、SFDR は-78.82dBc である。仮に電流源のミスマッチがなければ、SFDR の値は-82.63dBc である。各ケースのシミュレーションを行った結果を表3に示す。

表3 各ケースでのシミュレーション結果

| L 73 | ス番号 | SFDR   |        |        |          |  |  |  |

|------|-----|--------|--------|--------|----------|--|--|--|

| 7-1  |     | 最大値    | 最小值    | 平均值    | カウンタを用いる |  |  |  |

| ケース  | 1   | -78.49 | -70.33 | -75.30 | -76.25   |  |  |  |

| ケース  | 2   | -82.61 | -75.46 | -78.51 | -79.10   |  |  |  |

| ケース  | 3   | -81.33 | -74.17 | -77.67 | -77.85   |  |  |  |

| ケース  | 4   | -80.79 | -71.51 | -75.45 | -78.82   |  |  |  |

| ケース  | 5   | -82.36 | -75.94 | -79.15 | -80.72   |  |  |  |

|      |     |        |        |        |          |  |  |  |

表3より、カウンタを用いて求められる SFDR は平均値より良いものである。したがってカウンタを用いると、電流源のミスマッチの値を計測することならびに選択する項が個別に設置することがなくても、わりに高い SFDR を得ることができ、信号の純度も高いレベルに保持できる。

### 文 献

- (1)アルフレッド・S・ポザマンティエ、イングマル・レーマン、 (訳) 松浦俊輔、不思議な数列フィボナッチの秘密日経B P社 (2010年).

- (2) 小林佑太朗、香積正基、楊志翔、小林春夫、 "ADC/DAC の ヒボナッチ数列を用いた冗長性設計の検討", 電気学会 電子回路研究会、奈良 (2013年10月3-4日).