# A Multibit Complex Bandpass ΔΣΑD Modulator with I,Q Dynamic Matching and DWA Algorithm

<u>H. San</u>, Y. Jingu, H. Wada, H. Hagiwara,

A. Hayakawa, J. Kudoh<sup>2</sup>, K. Yahagi<sup>2</sup>,

T. Matsuura<sup>2</sup>, H. Nakane<sup>2</sup>, H. Kobayashi,

M. Hotta<sup>3</sup>, T. Tsukada<sup>2</sup>, K.Mashiko<sup>4</sup>, A.Wada<sup>5</sup>

1) Gunma University

2) Renesas Technology Corp.

3) Musashi Institute of Technology

4) STARC

5) Sanyo Electric Co., Ltd.

#### Motivation

- Complex Bandpass Delta-Sigma AD Modulator

- Proposed Architecture

- I, Q Dynamic Matching

- Complex DWA Algorithm

- Measured Results

- Conclusion

#### Motivation

- Complex Bandpass Delta-Sigma AD Modulator

- Proposed Architecture

- I, Q Dynamic Matching

- Complex DWA Algorithm

- Measured Results

- Conclusion

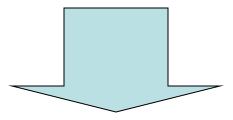

# Motivation

# Low power ADC in low-IF receiver targeted for bluetooth, wireless LAN.

# Complex bandpass delta-sigma AD modulator

# **Receiver Architecture Comparison**

#### Motivation

- Complex Bandpass Delta-Sigma AD Modulator

- Proposed Architecture

- I,Q Dynamic Matching

- Complex DWA Algorithm

- Measured Results

- Conclusion

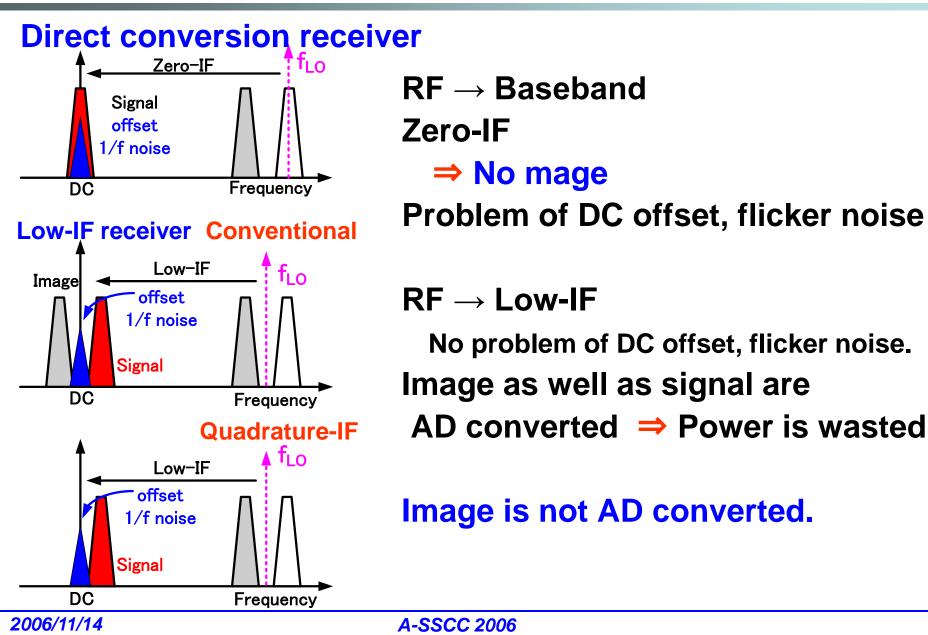

#### **Complex Bandpass Delta-Sigma Modulator**

#### Motivation

- Complex Bandpass Delta-Sigma AD Modulator

- Proposed Architecture

- I,Q Dynamic Matching

- Complex DWA Algorithm

- Measured Results

- Conclusion

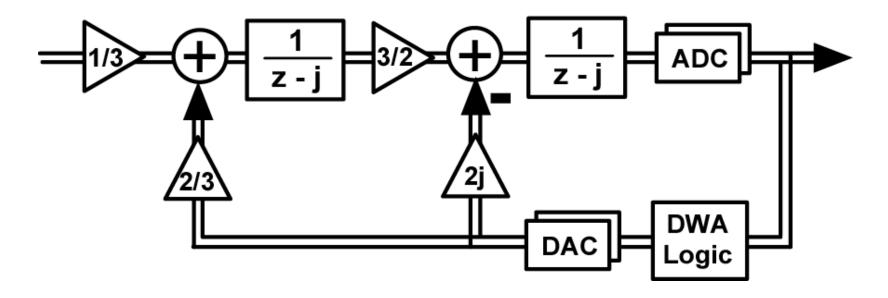

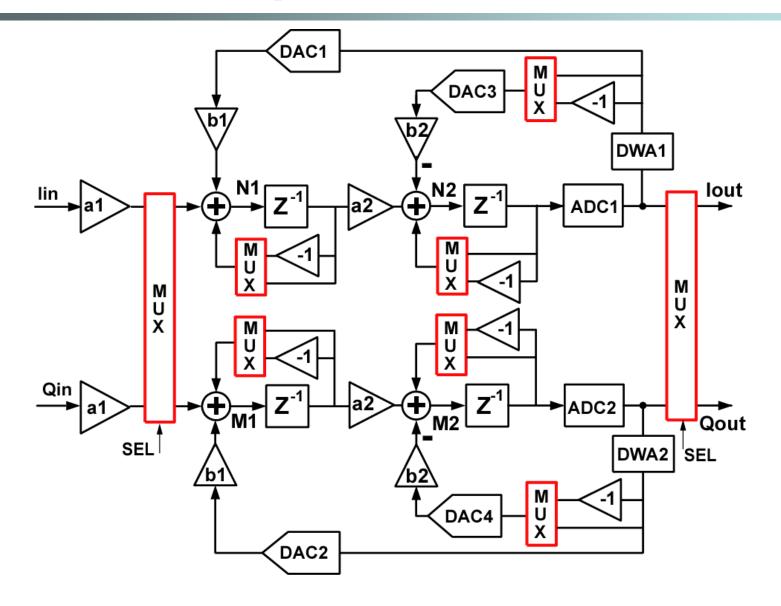

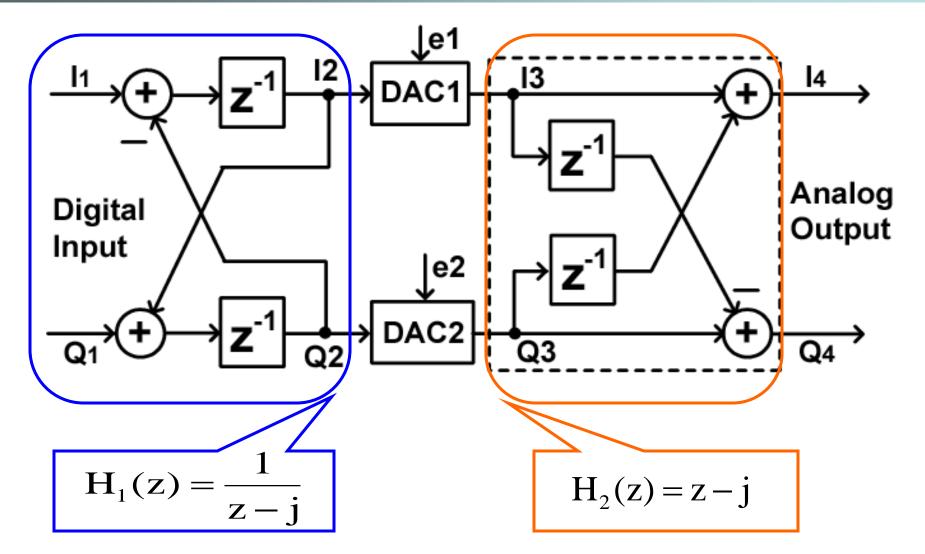

# **Proposed Architecture**

- New complex bandpass filter

- Multi-bit ADCs/DACs

- Complex DWA algorithm

### **Proposed Structure**

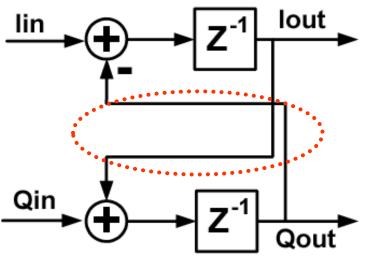

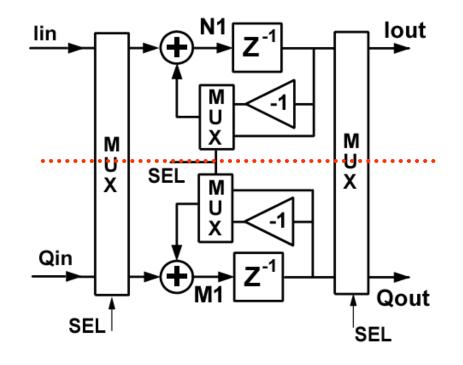

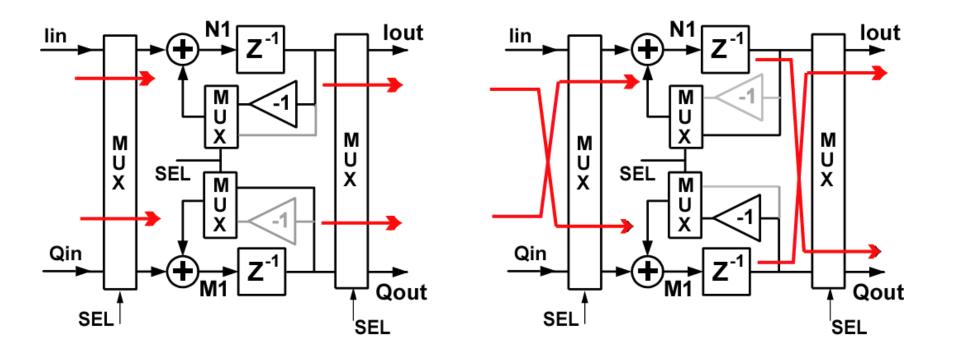

# I,Q Dynamic Matching of Complex Filter

Complex Filter

#### Conventional complex filter I &Q crossing paths

Proposed complex filter Upper, lower separated paths

- I,Q mismatch reduction.

- Layout simplification.

**A-SSCC 2006**

#### **Operation of Proposed Complex Filter**

# lout(n) = lin(n-1) - Qout(n-1)Qout(n) = Qin(n-1) + lout(n-1)

# **Complex BPDSM with Low-power**

- 2<sup>nd</sup> order ---- low power

- 9-level ADCs/DACs

- Stability improvement

- Low quantization error

- Power reduction of amplifiers

- I,Q mismatch

Solved by dynamic matching

Nonlinearities of multibit DAC

Solved by complex DWA

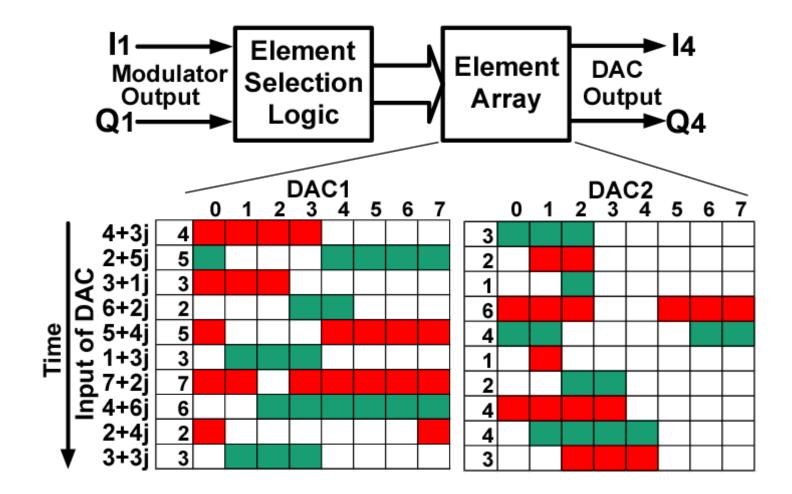

# **Complex DWA (1)**

**Digital bandpass filter**

#### **Analog band elimination filter**

# **Complex DWA (2)**

- Motivation

- Complex Bandpass Delta-Sigma AD Modulator

- Proposed Architecture

- I,Q Dynamic Matching

- Complex DWA Algorithm

- Measured Results

- Conclusion

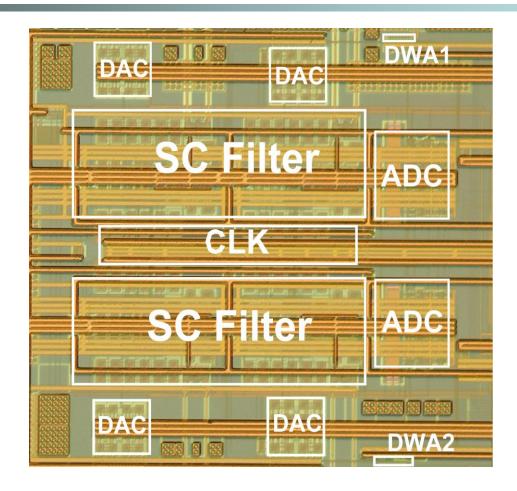

# **Chip Implementation**

- 1P6M 0.18µm CMOS Process

- Core size 1.4 \*1.3mm<sup>2</sup>.

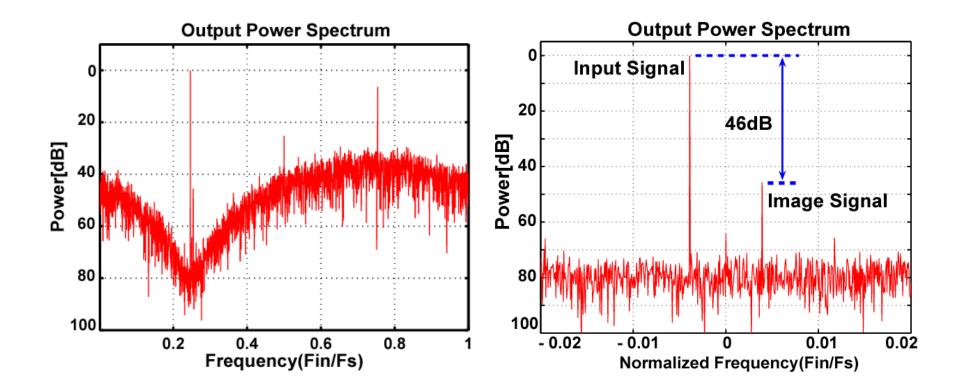

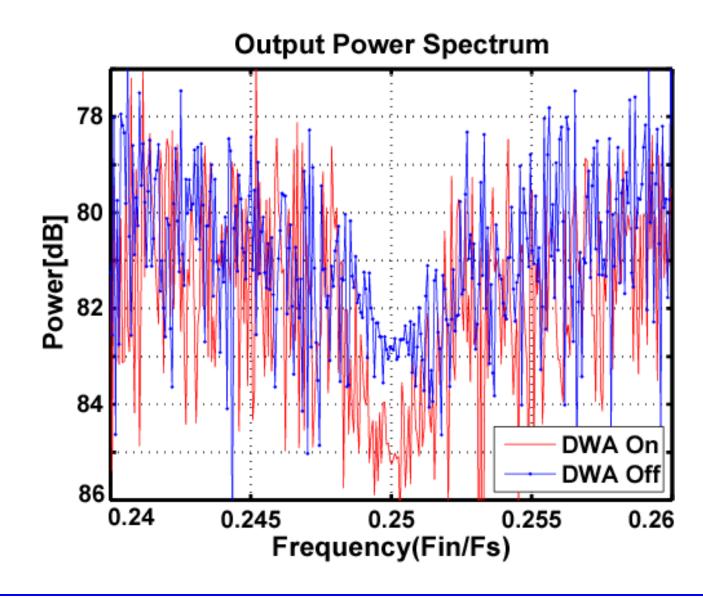

### **Measured Output Power Spectrum**

# **Effect of Complex DWA**

A-SSCC 2006

#### **Summary of Modulator Performance**

| Technology         | 0.18-µm CMOS 1P6M |

|--------------------|-------------------|

| Supply voltage     | 2.8V              |

| Sampling Frequency | 20MHz             |

| SNDR               | 64.5dB @ BW=78kHz |

| Power consumption  | 28.4mw            |

| Active area        | 1.4mm*1.3mm       |

#### Motivation

- Complex Bandpass Delta-Sigma AD Modulator

- Proposed Architecture

- I,Q Dynamic Matching

- Complex DWA Algorithm

- Measured Results

# Conclusion

# Conclusion

A 2<sup>nd</sup>-order multi-bit complex bandpass delta-sigma modulator

- Complex filter with dynamic matching

- I,Q mismatch reduction

- Layout simplification

- Complex DWA

- Suppression of multibit DACs nonlinearities

- Chip measurements demonstrated these