# フラッシュ型タイムデジタイザ回路の ヒストグラム法による自己校正の実験検証

中條剛志<sup>1</sup> 平林大樹<sup>1</sup> 加藤健太郎<sup>2</sup> 李 从兵<sup>1</sup> 李恩思<sup>1</sup>

小林佑太朗<sup>1</sup> 王俊善<sup>1</sup> 佐藤幸志<sup>3</sup> 小林春夫<sup>1</sup>

1:群馬大学 2:鶴岡工業高等専門学校 3:光サイエンス

*Supported by STARC*

# アウトライン

---

- 研究背景

- TDCの回路構成と線形性の自己校正原理

- アナログFPGAによる試作

- 測定結果・評価

- まとめ

# アウトライン

---

- **研究背景**

- TDCの回路構成と線形性の自己校正原理

- アナログFPGAによる試作

- 測定結果・評価

- まとめ

# 研究背景

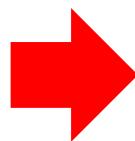

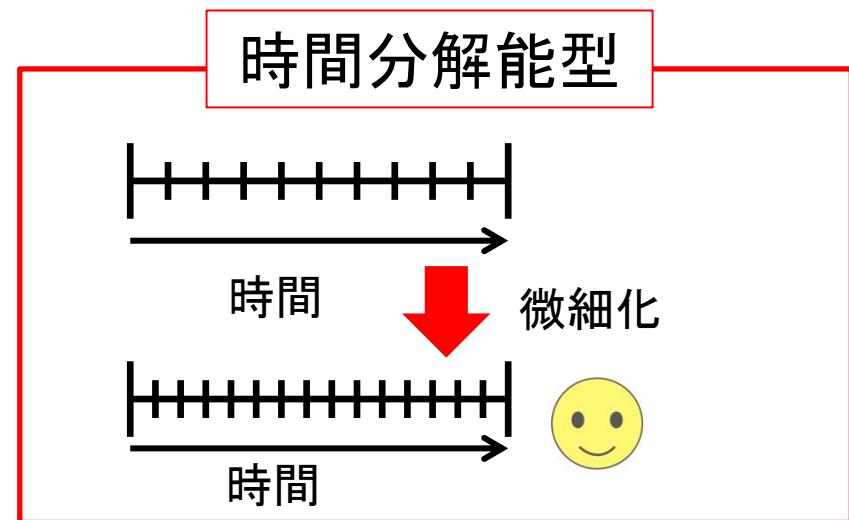

微細化CMOS LSI

電源電圧の低下

動作スイッチングスピードの向上

TDC(Time-to-Digital Converter)は2つのデジタル信号の時間差をデジタル値に変換

微細化CMOS LSIにおいて、TDCは時間領域アナログ回路のカギとなる

(センサ回路, All-Digital PLL, ADC, 変調回路等)

# アウトライン

---

- 研究背景

- TDCの回路構成と線形性の自己校正原理

- アナログFPGAによる試作

- 測定結果・評価

- まとめ

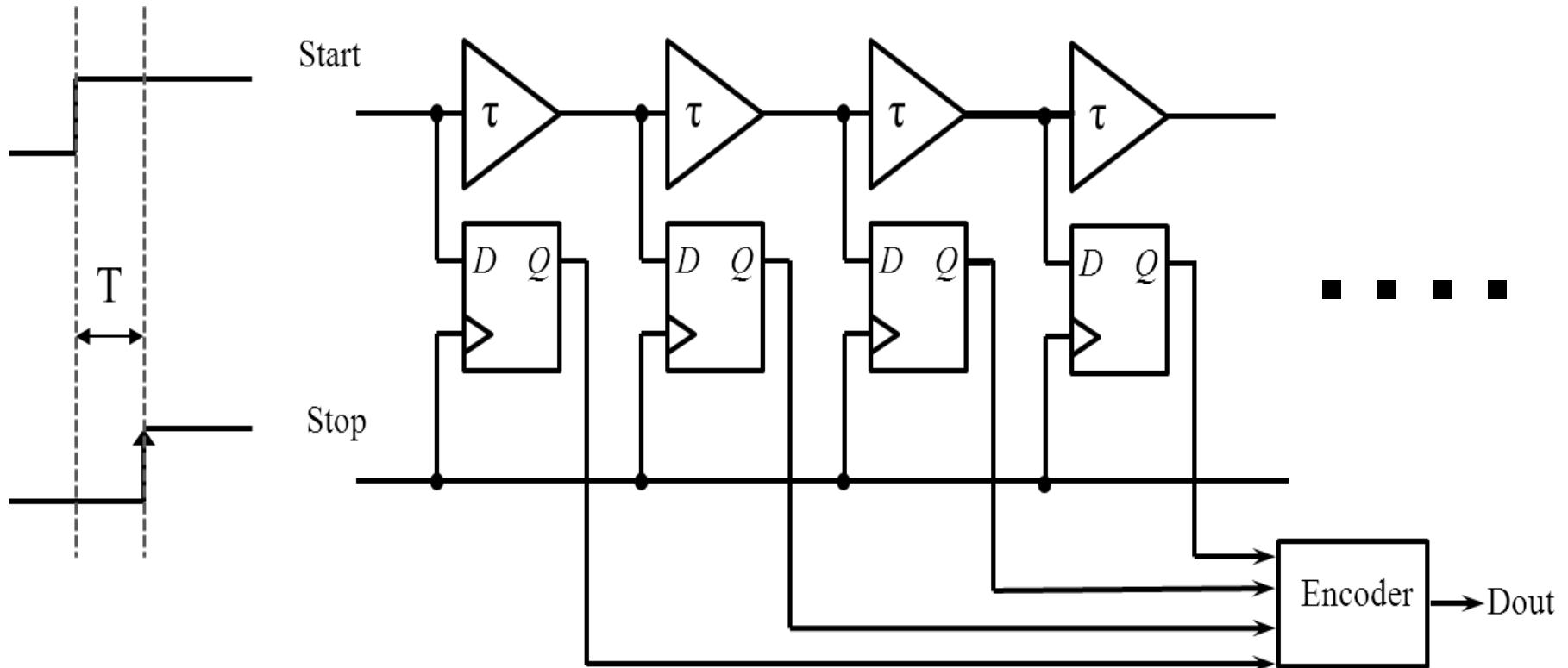

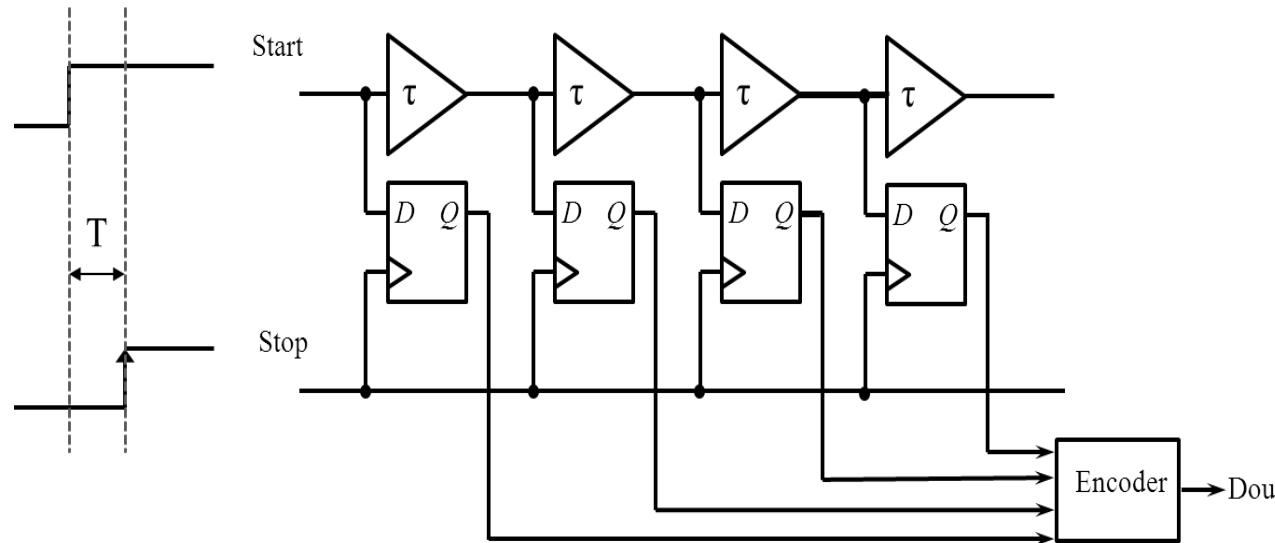

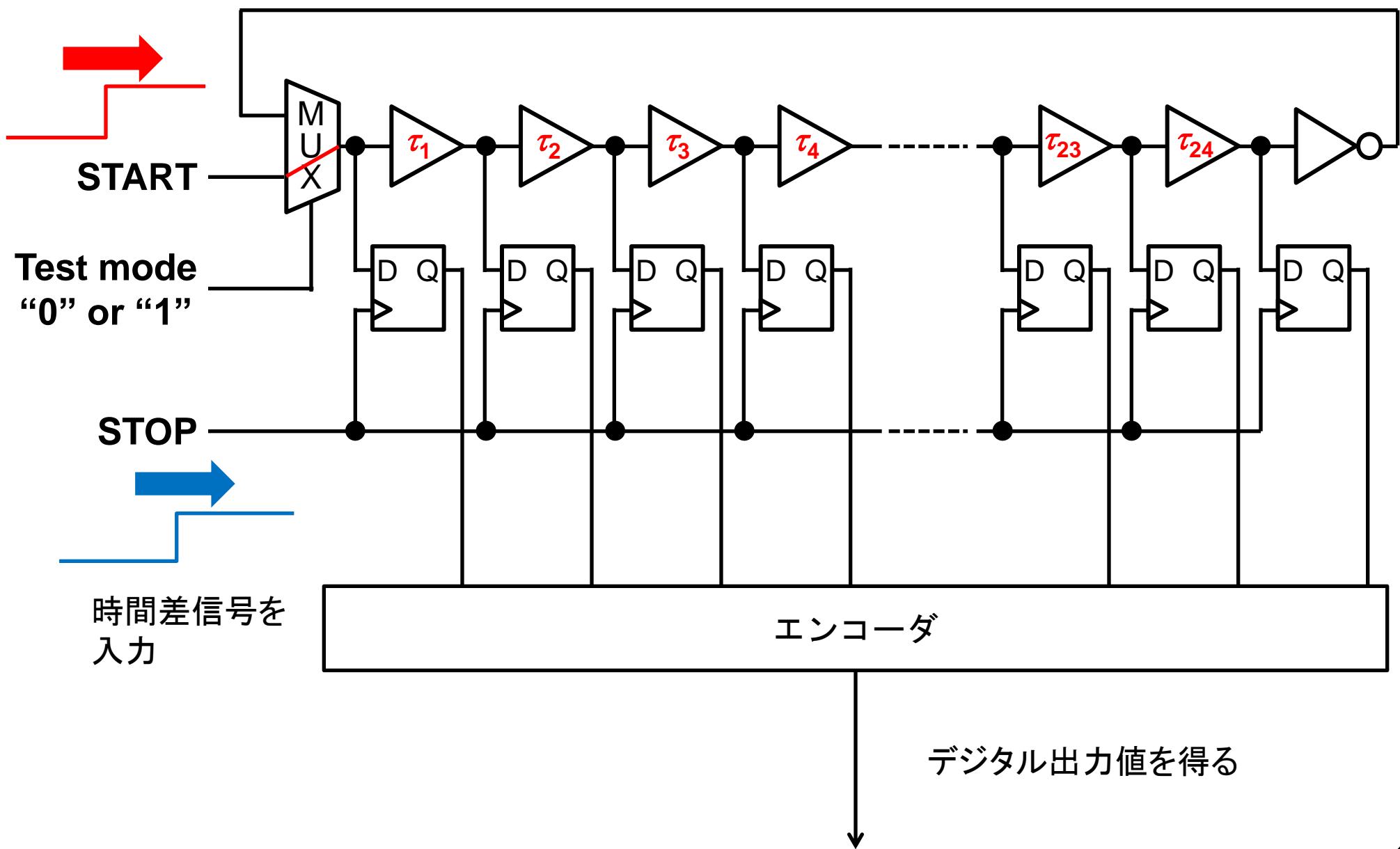

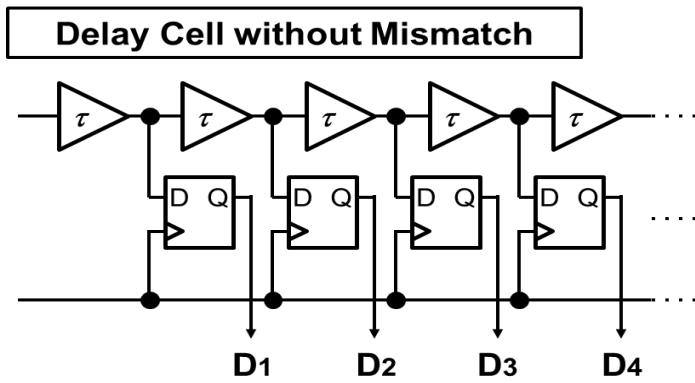

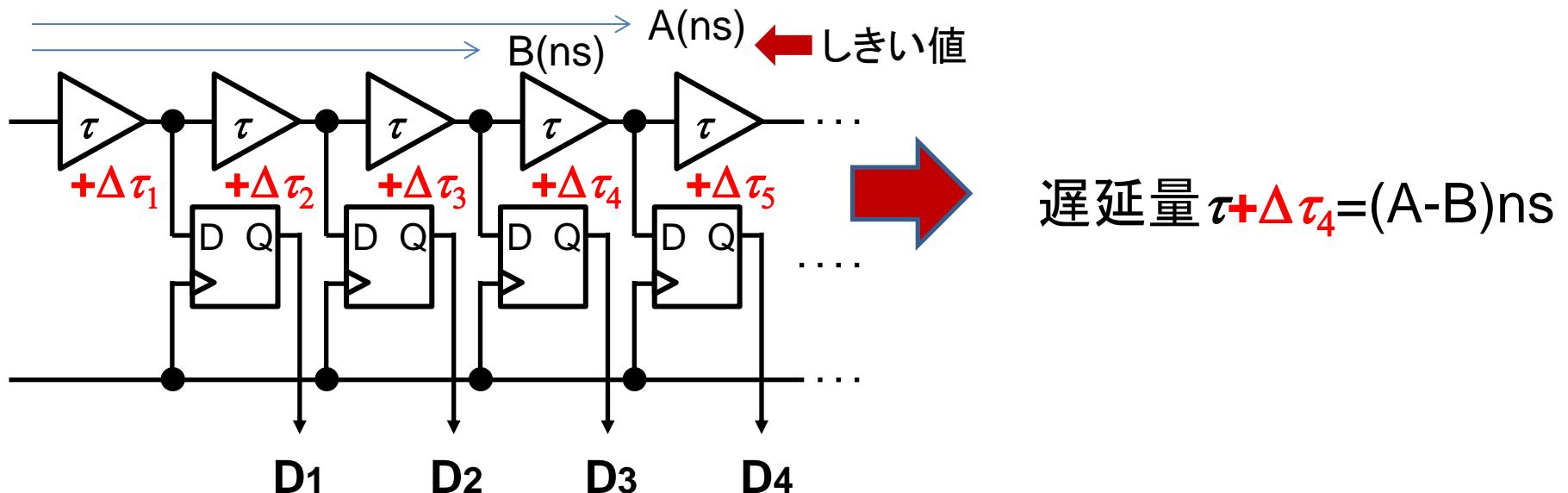

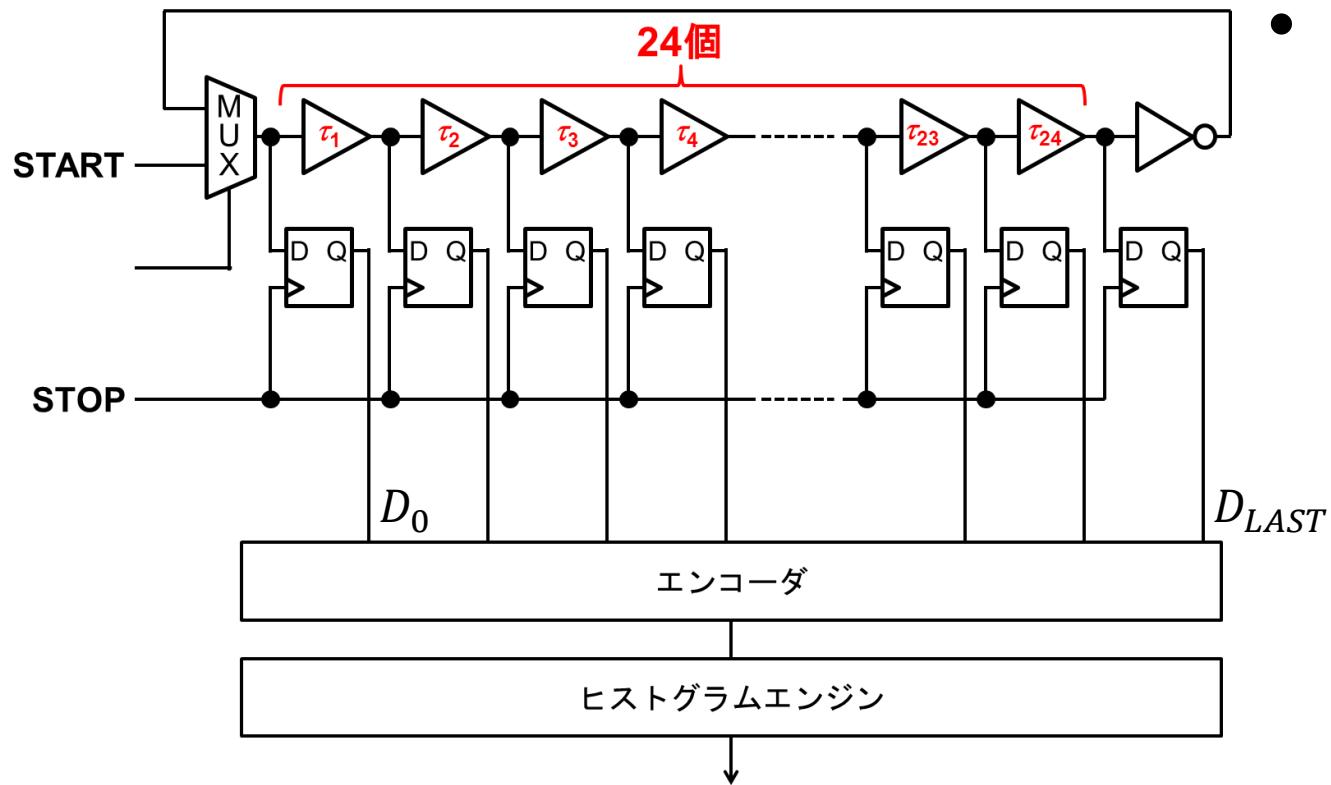

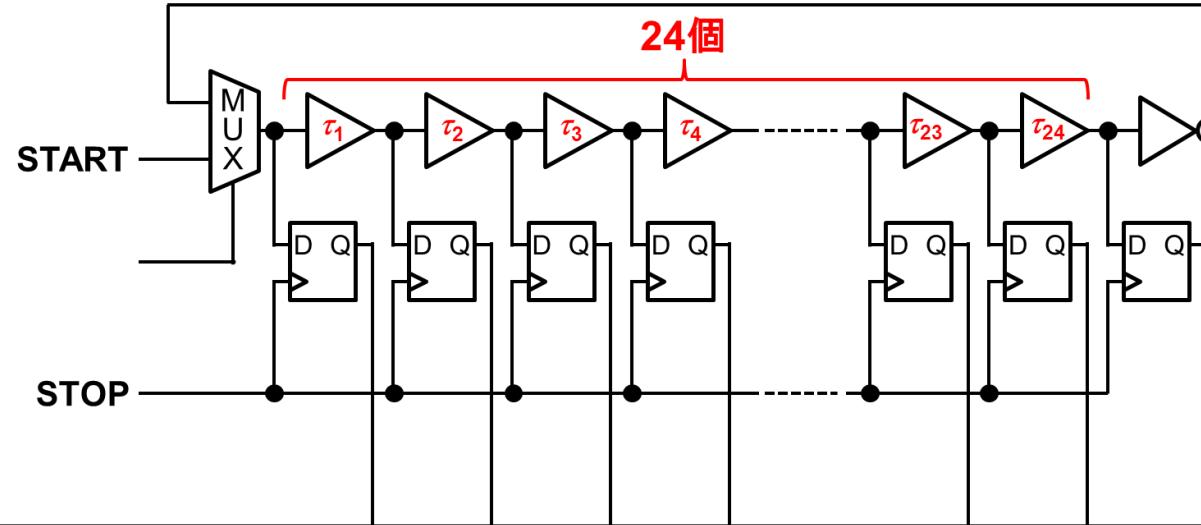

# フラッシュ型TDC

Start立ち上がり信号が入力され、遅延素子( $\tau$ )を伝搬している間に

stop立ち上がり信号が入力

入力信号時間差( $T$ )に比例してデジタル値( $D_{out}$ )を出力

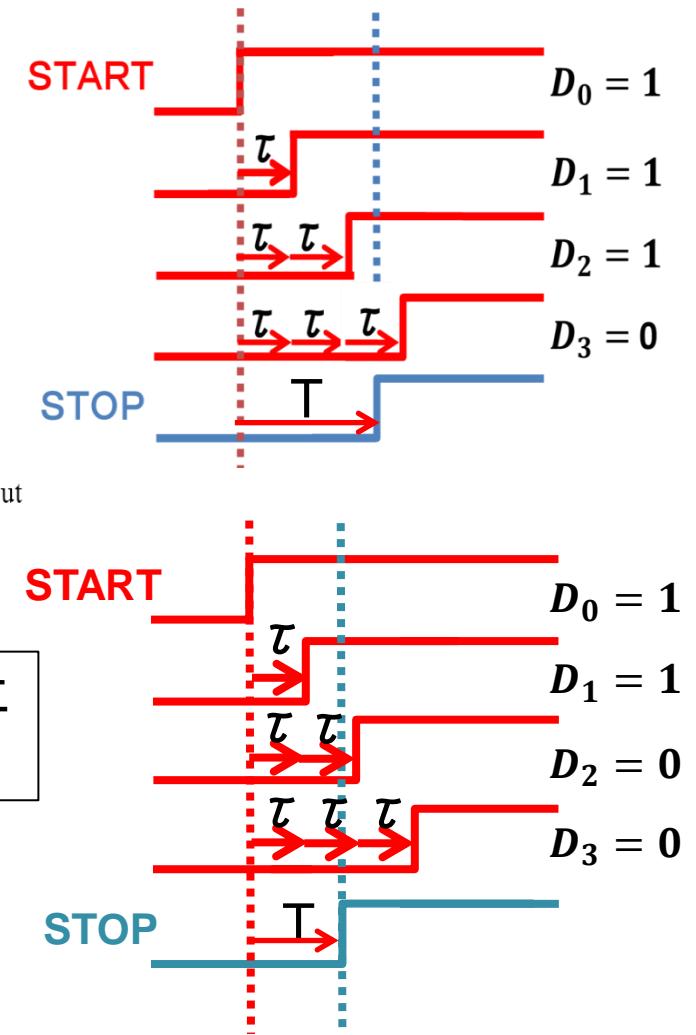

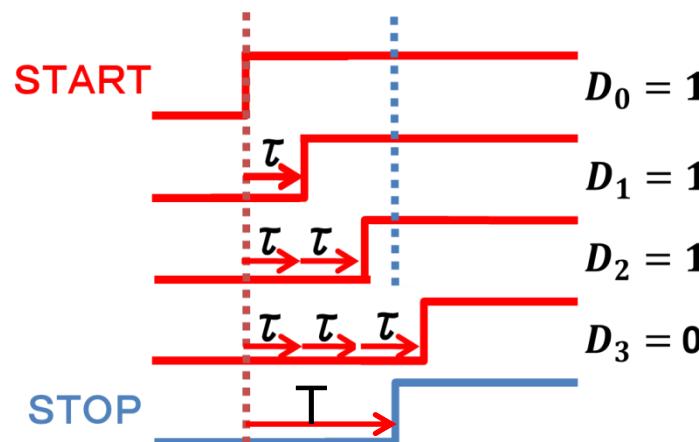

# フラッシュ型TDCの動作

start信号が入力され、遅延素子( $\tau$ )を伝搬している間に

stop信号を入力

入力信号時間差( $T$ )に比例して

デジタル値( $D_{out}$ )を出力

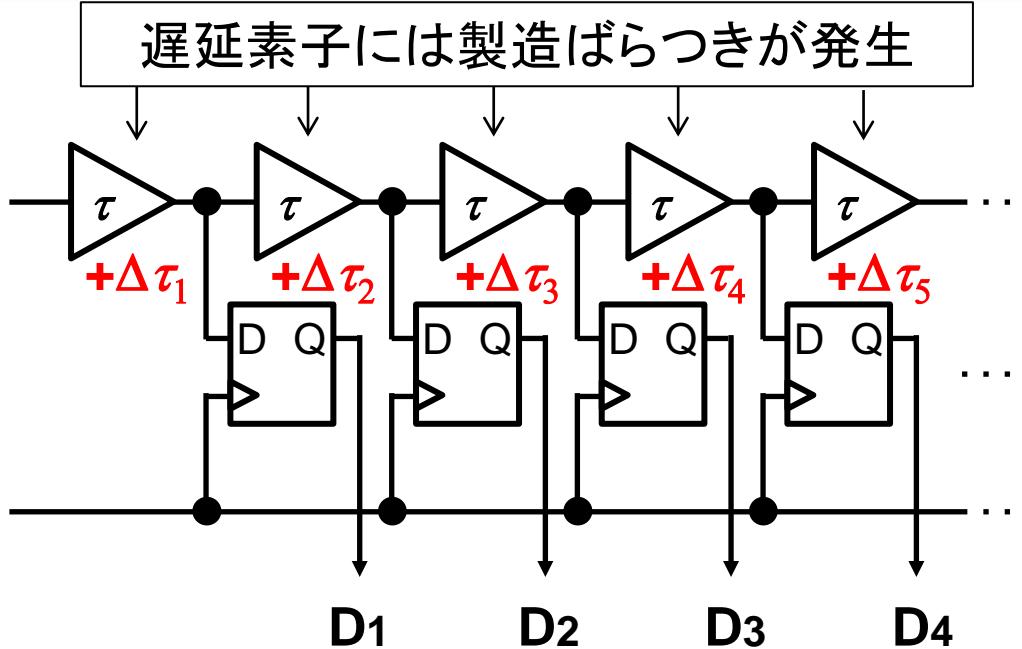

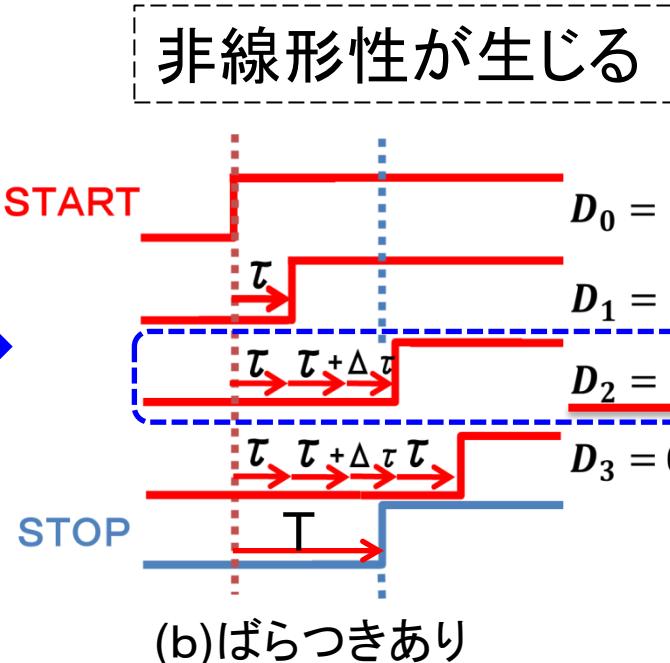

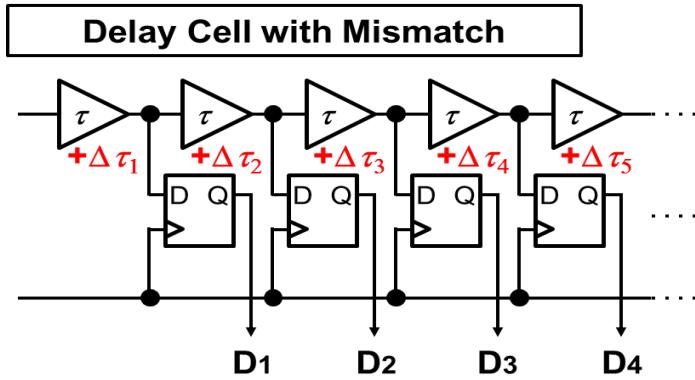

# TDC回路内の遅延素子バラつき

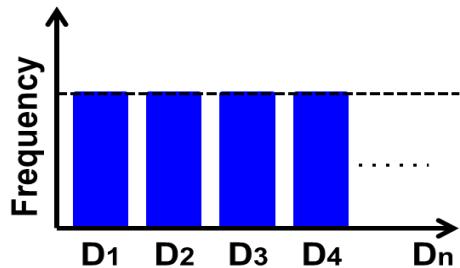

(a)ばらつきなし

(b)ばらつきあり

# 遅延素子の製造ばらつき

- 遅延  $\tau$  の製造ばらつき

「相対ばらつき」

→ 非線形性

「絶対(平均値)ばらつき」

→ 入力レンジに影響

- 今回は「相対ばらつき」に着目

# 研究目的

- TDCの線形性のヒストグラム法による自己校正

$$Dout(0)=1$$

$$Dout(1)=3$$

$$Dout(2)=5$$

$$Dout(3)=8$$

校正

$$Dout(0)=0.3$$

$$Dout(1)=2.8$$

$$Dout(2)=4.5$$

$$Dout(3)=7.3$$

遅延量に

適した出力値

▪

▪

▪

▪

- アナログFPGA(PSoC)で試作、評価

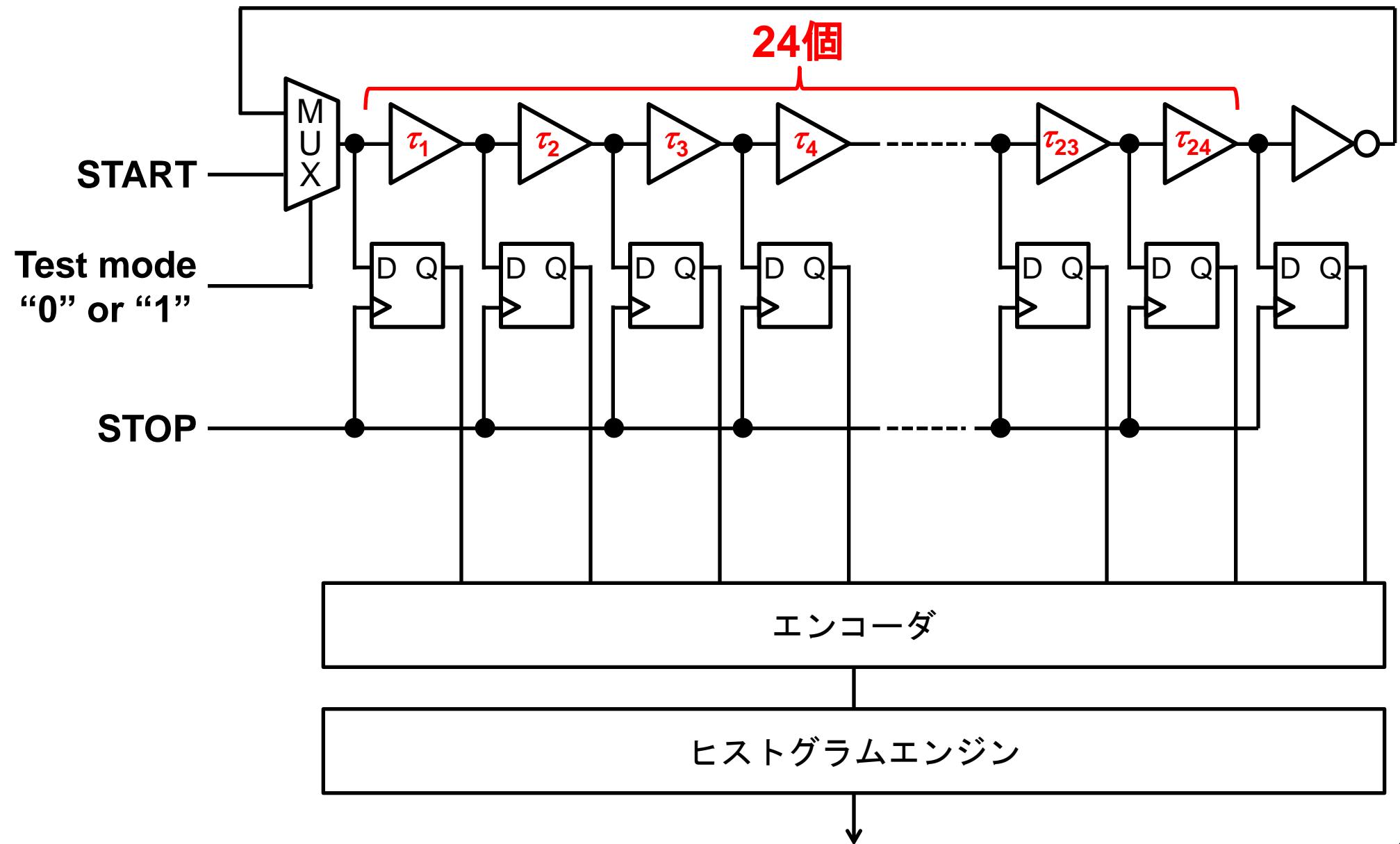

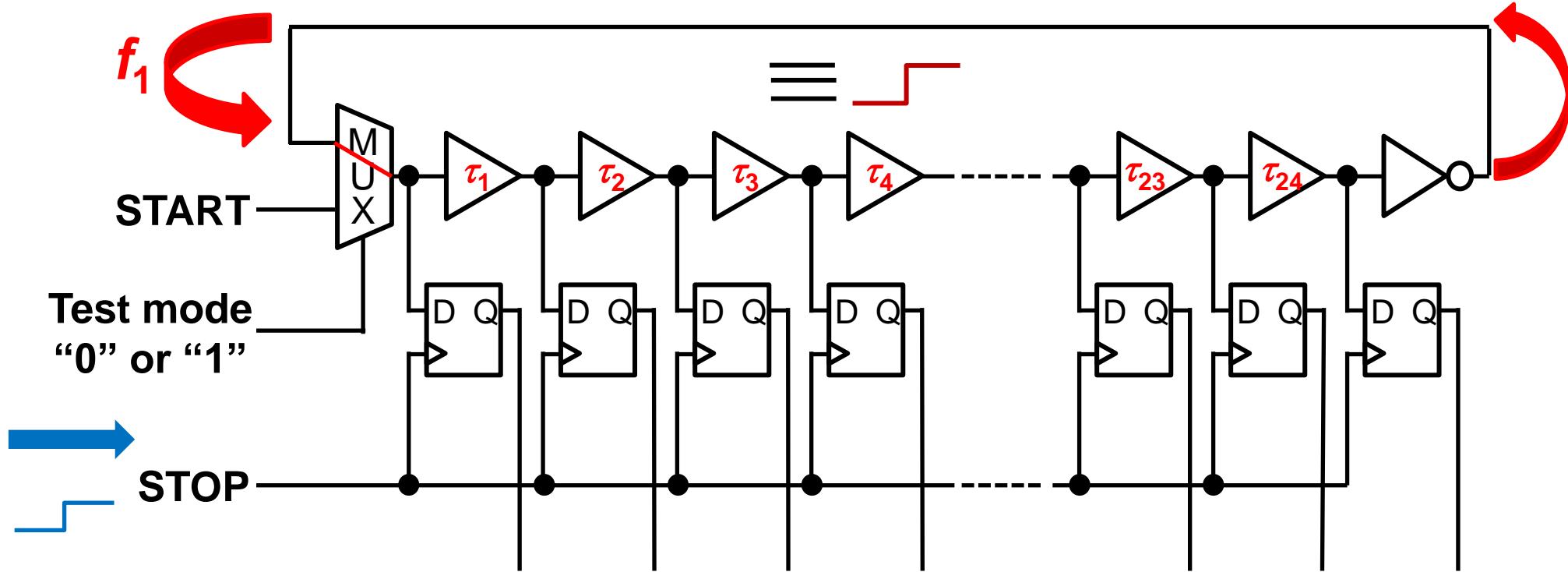

# 自己校正TDC

# 通常測定モード

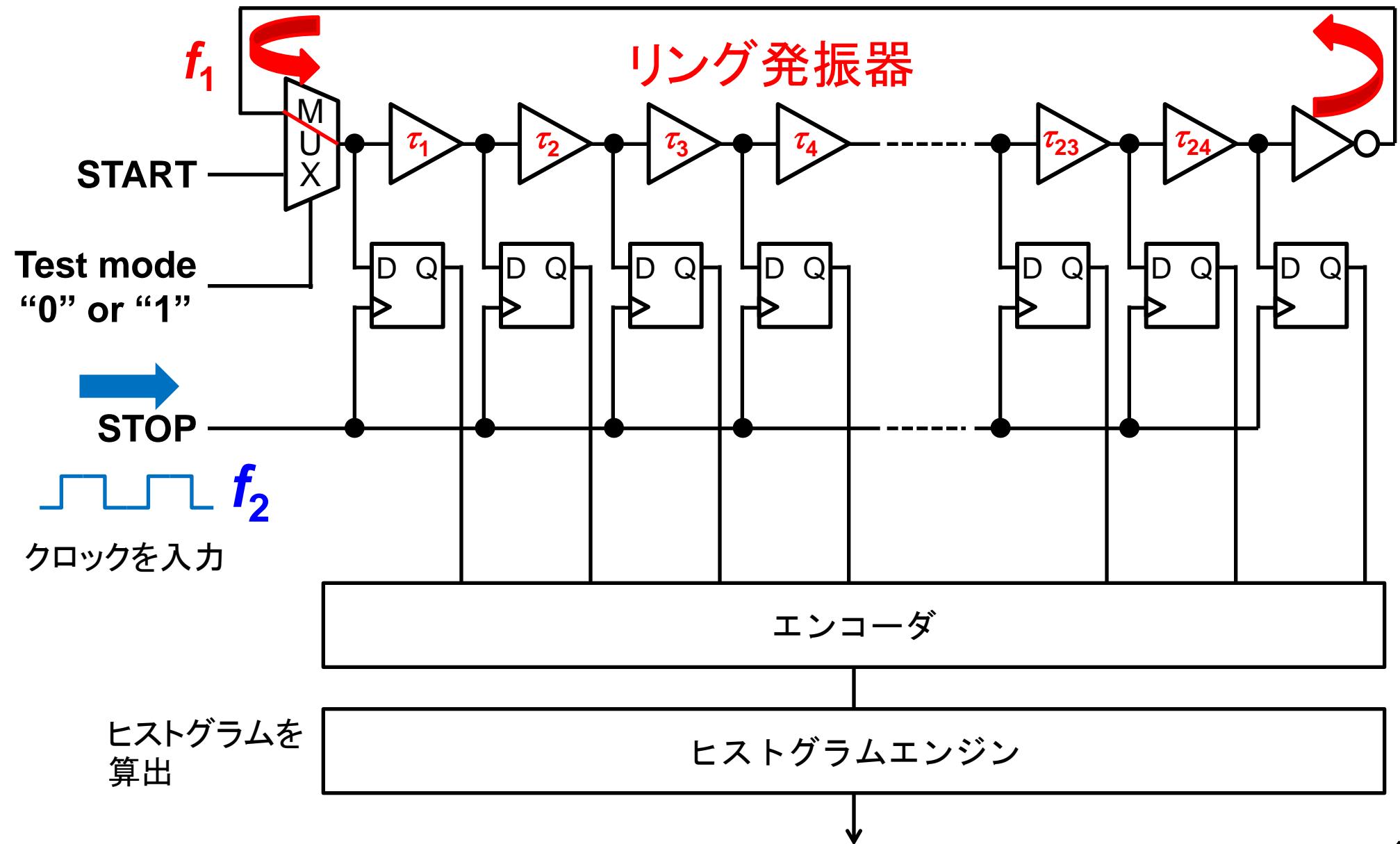

# 自己校正モード

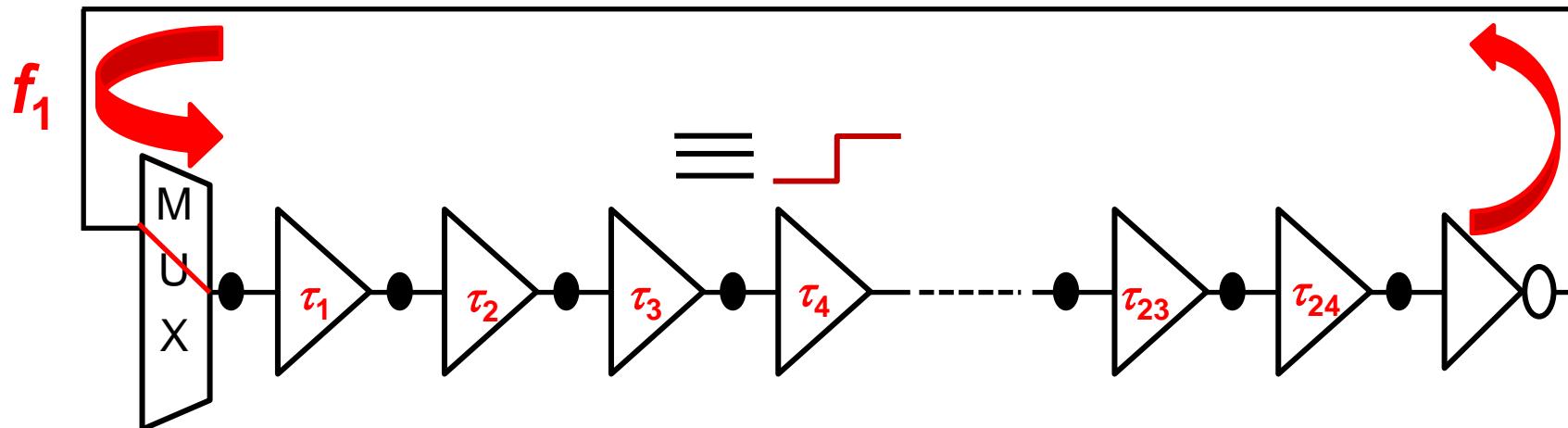

# リング発振動作

- ・ リング発振器が発振中、遅延素子の遅延量に比例して素子内に立ち上がり信号の存在時間が長くなる

1回の発振では  $\tau_1$  から  $\tau_{24}$  では遅延量の時間分立ち上がり信号が存在する

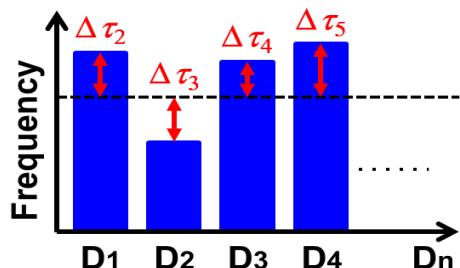

# 線形性の校正原理

- 発振が始まってから十分に時間が経過し、

start 信号と無相関/非同期なタイミングでstop信号を入力

- 遅延量の大きい遅延素子に立ち上がり信号が存在する確率は高く、

遅延量の小さい遅延素子に立ち上がり信号が存在する確率は低い

# ヒストグラムと遅延量の関係

- 発振中stop信号を多数入力し、ヒストグラムを取得すると…

Histogram is Flat

Histogram  $\propto$  Mismatch

ヒストグラムは

遅延量の相対比

# 出力校正方法

- 遅延量の相対比を利用して出力校正

$$\frac{\text{下位から指定ビットまでの測定回数合計}}{\text{全測定回数合計}} \left( = \frac{\text{指定ビットまでの遅延量}}{\text{全遅延量}} \right)$$

比率を算出、フルスケールを掛けて出力値へ

## 出力校正の式

$$\bullet \quad D_{\text{out}}(N) = \frac{\sum_{i=1}^N P_{\text{in}}(i)}{\sum_{i=1}^{\text{FS}} P_{\text{in}}(i)} \times \text{FS}$$

**N**: 校正する**bit**

**Dout(N)**: **N**番目**bit**の校正後出力値

**Pin(i)**: **i**番目遅延素子測定回数

**FS**: 出力最大デジタル値

# アウトライン

---

- 研究背景

- TDCの回路構成と線形性の自己校正原理

- アナログFPGAによる試作

- 測定結果・評価

- まとめ

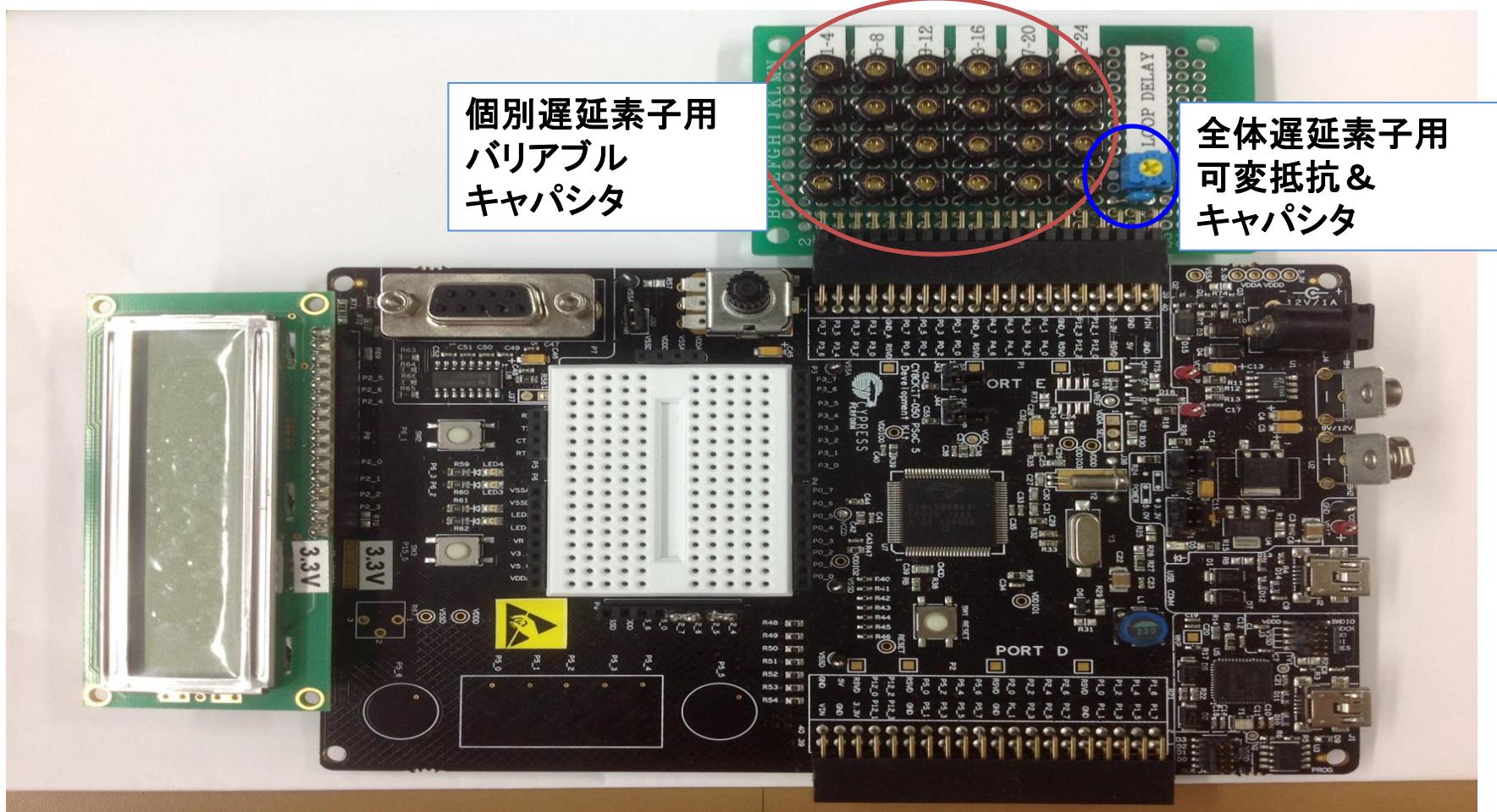

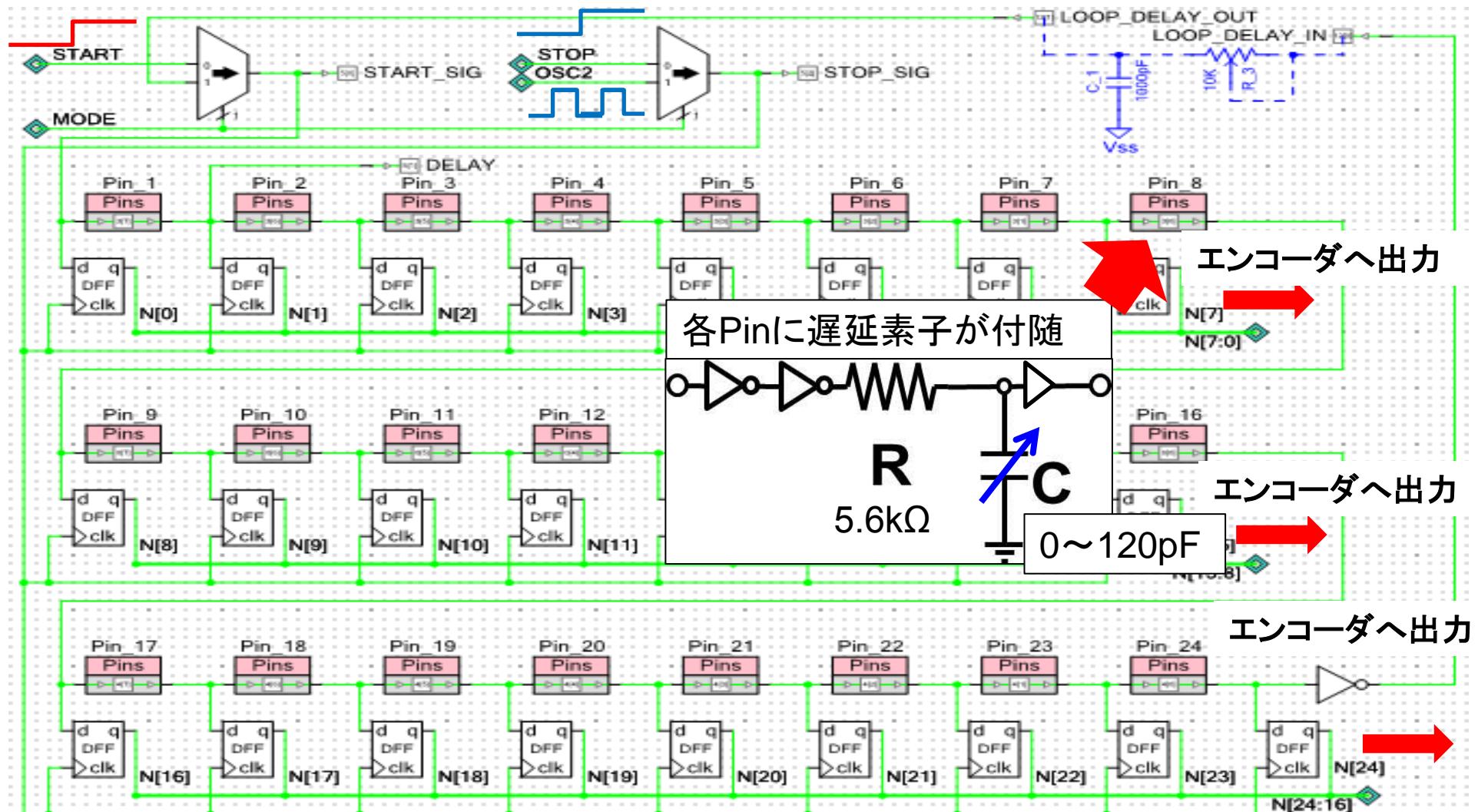

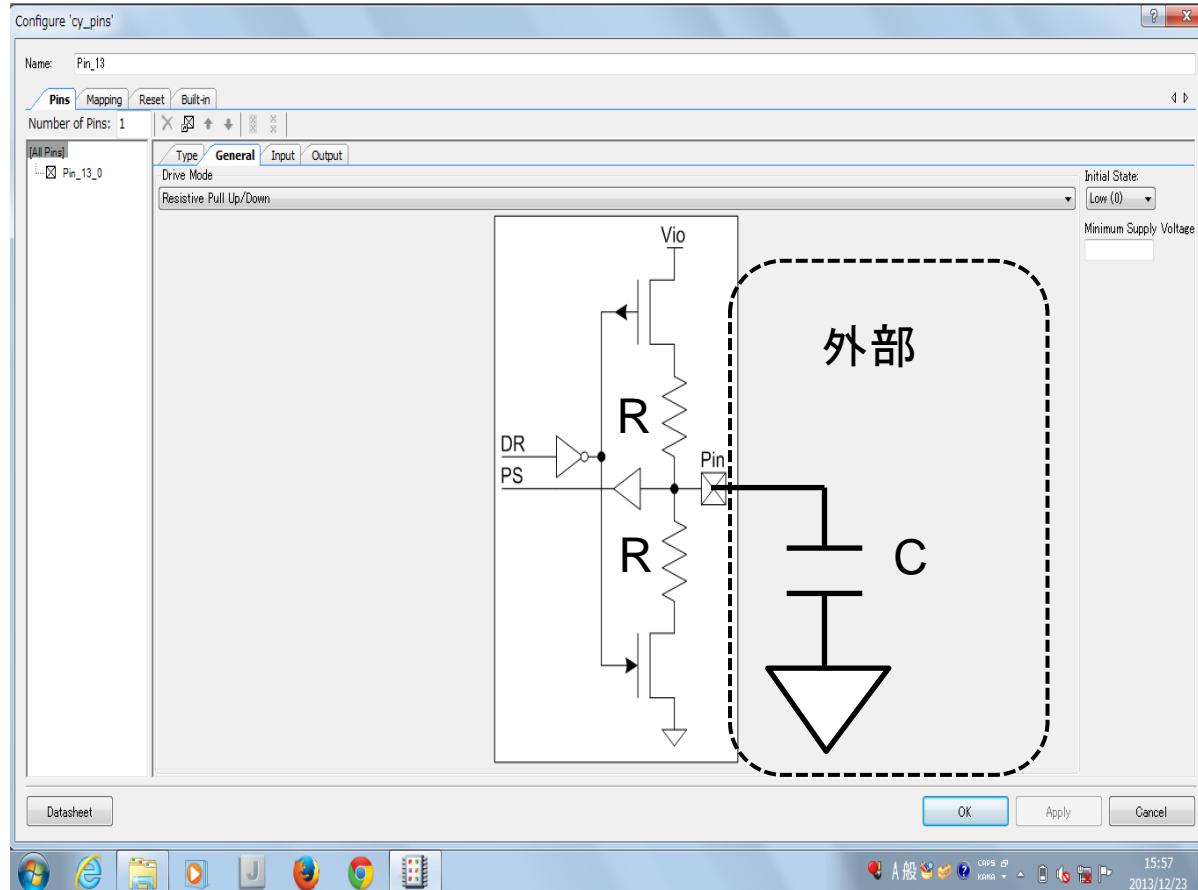

# 自己校正TDCを実装したPSoC

# PSoC (Programmable System-on-Chip) 5LP & 外付け遅延素子

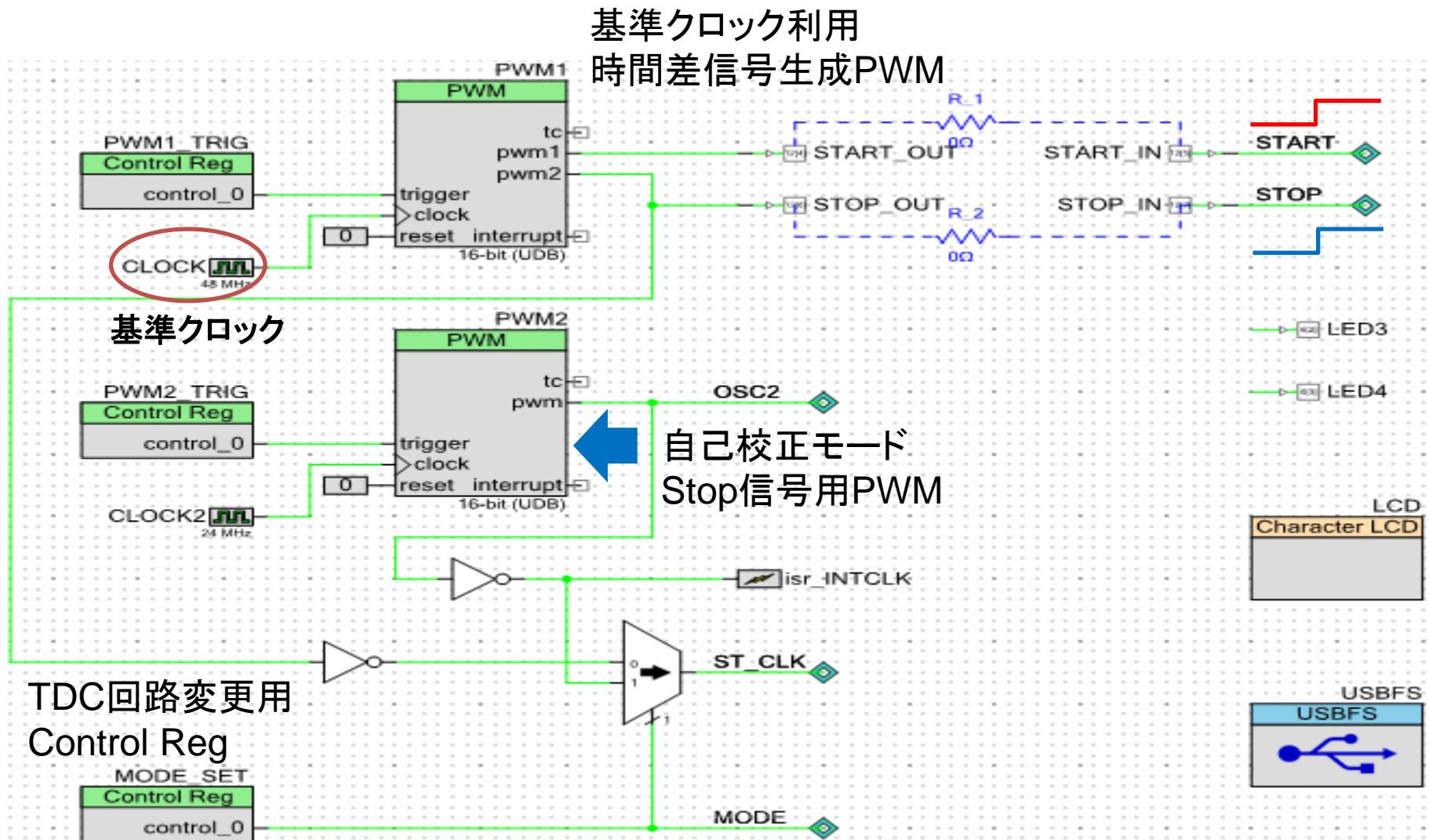

# PSoC TDC制御回路図

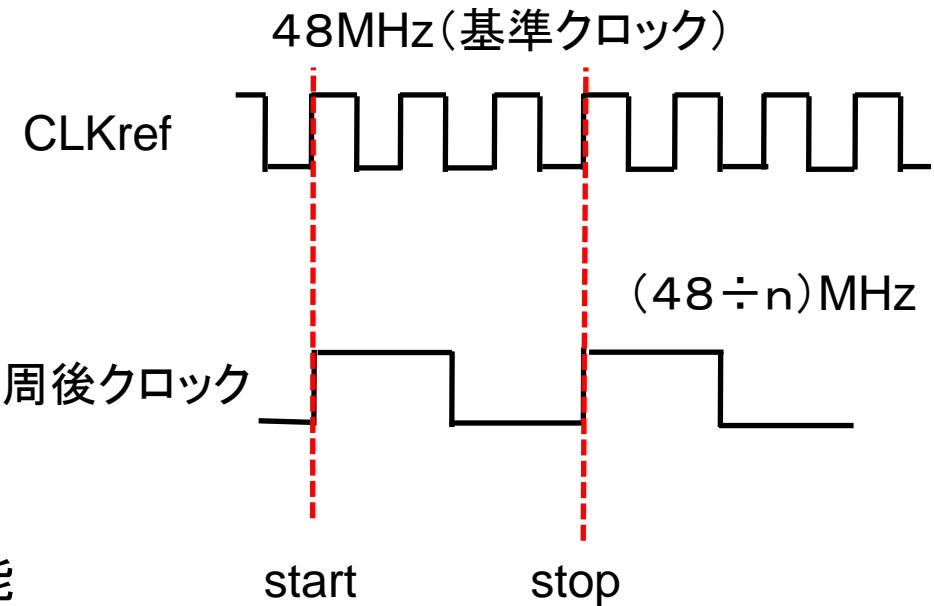

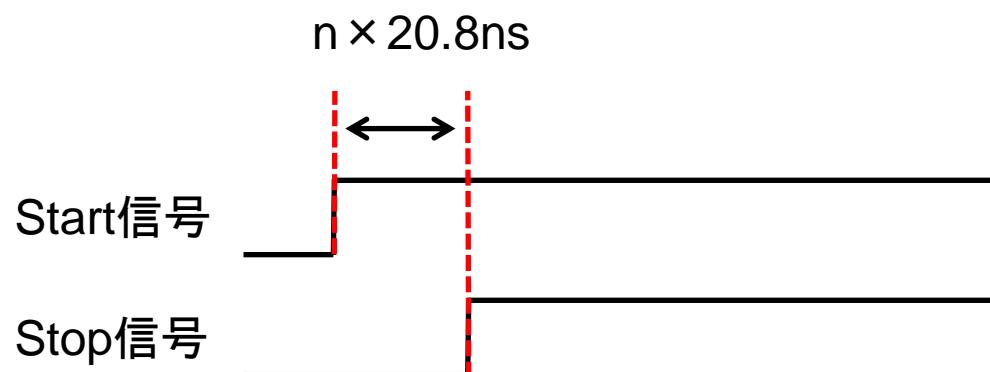

# 時間差信号の生成

PSoC内部で48MHzの基準クロックを生成

プログラムによる基準クロックの操作

- ・基準クロック周波数を $\div n$ 分周

- ・ $n \times 20.8\text{ns}$ 倍の時間差

正確な周波数・時間差のクロックを生成可能

評価用に使用可能

# フラッシュ型TDC & リング発振器回路図

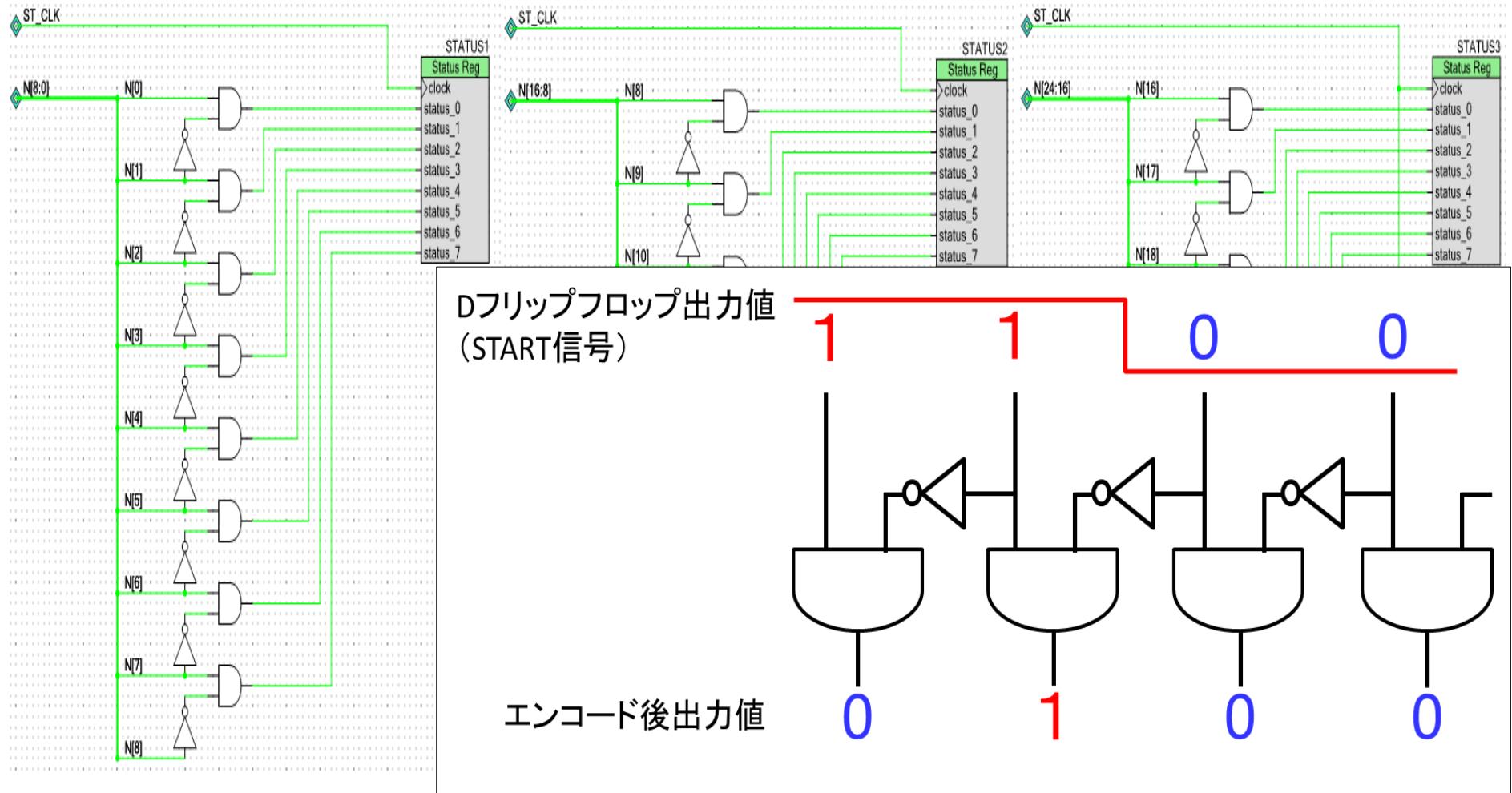

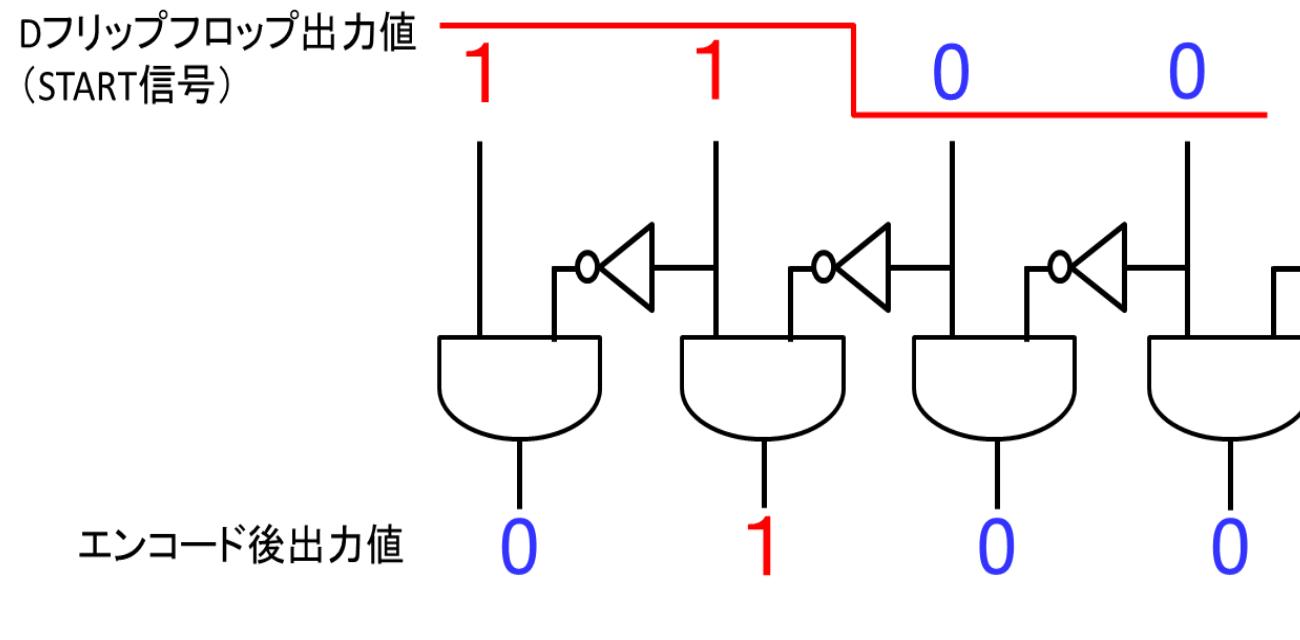

# エンコーダ回路図

1と0の切り替わり点を出力

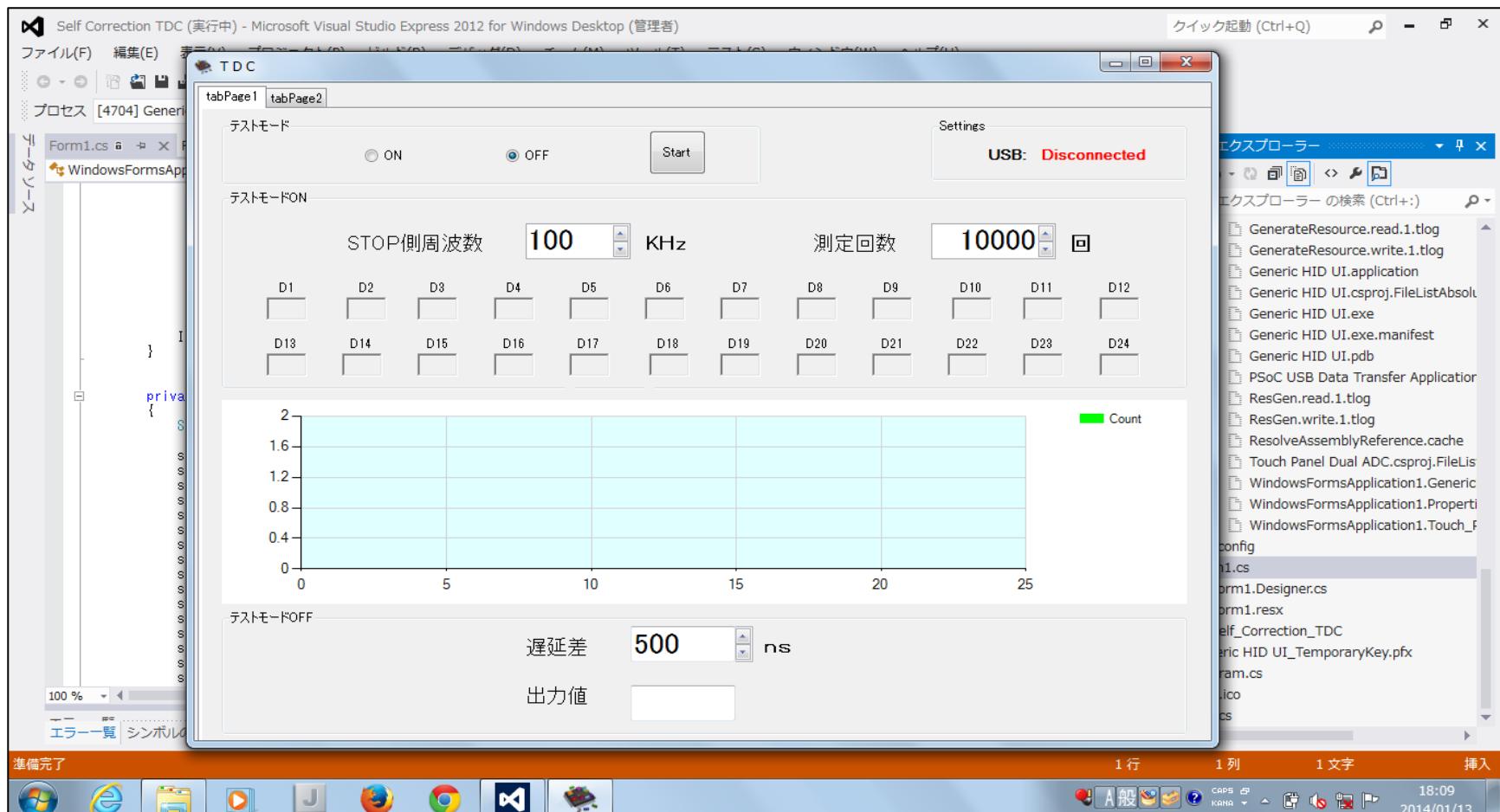

# 測定ソフトウェア

- C#で作成、USBでパソコンと接続し測定

# アウトライン

---

- 研究背景

- TDCの回路構成と線形性の自己校正原理

- アナログFPGAによる試作

- **測定結果・評価**

- まとめ

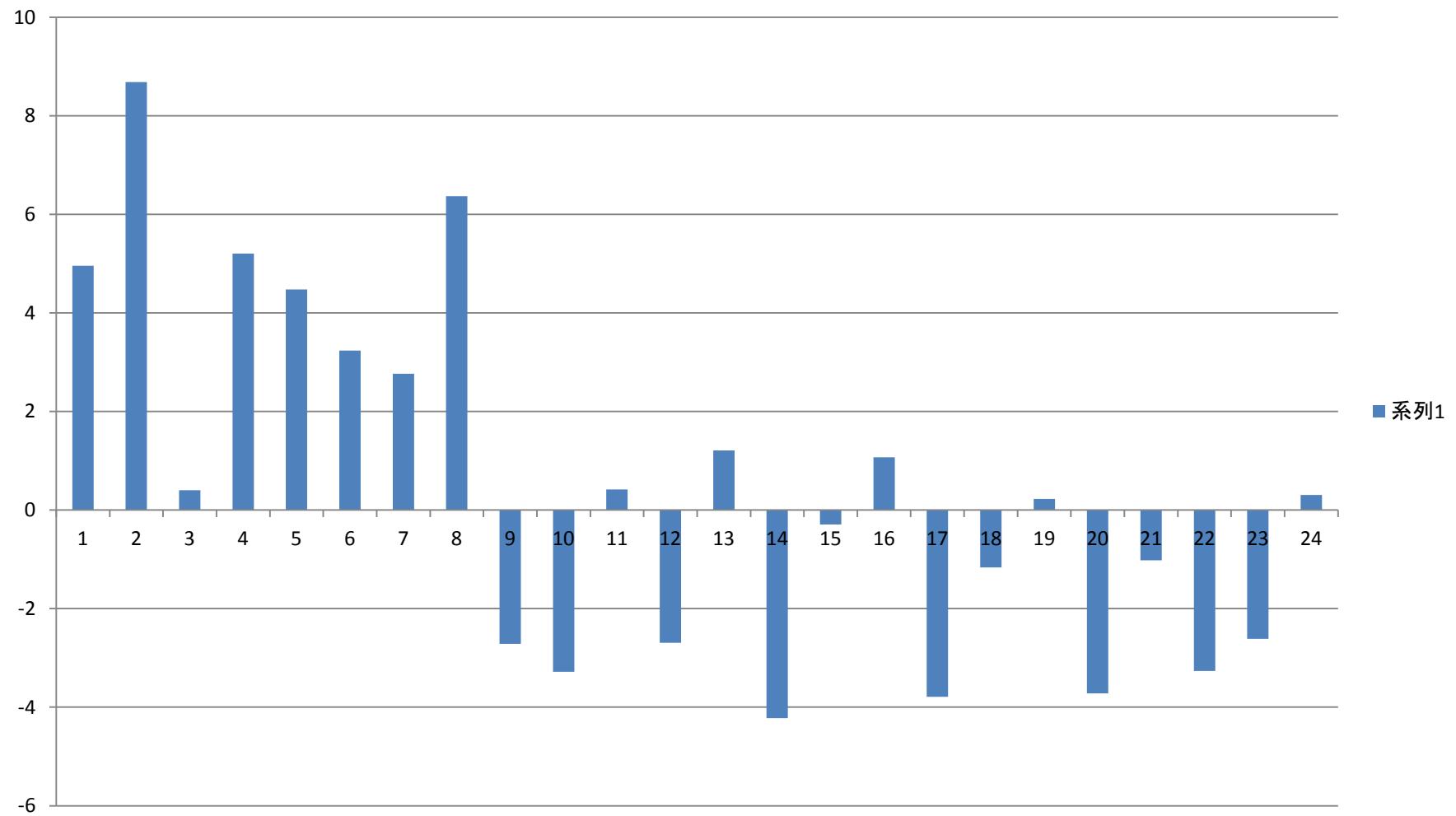

# 自己校正

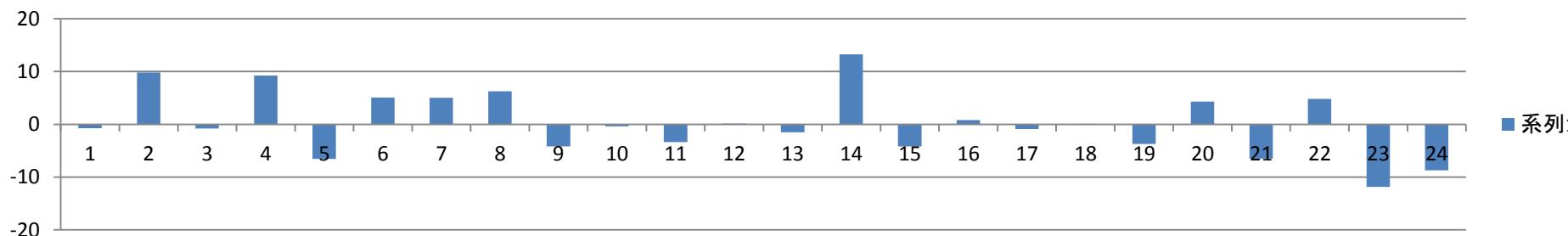

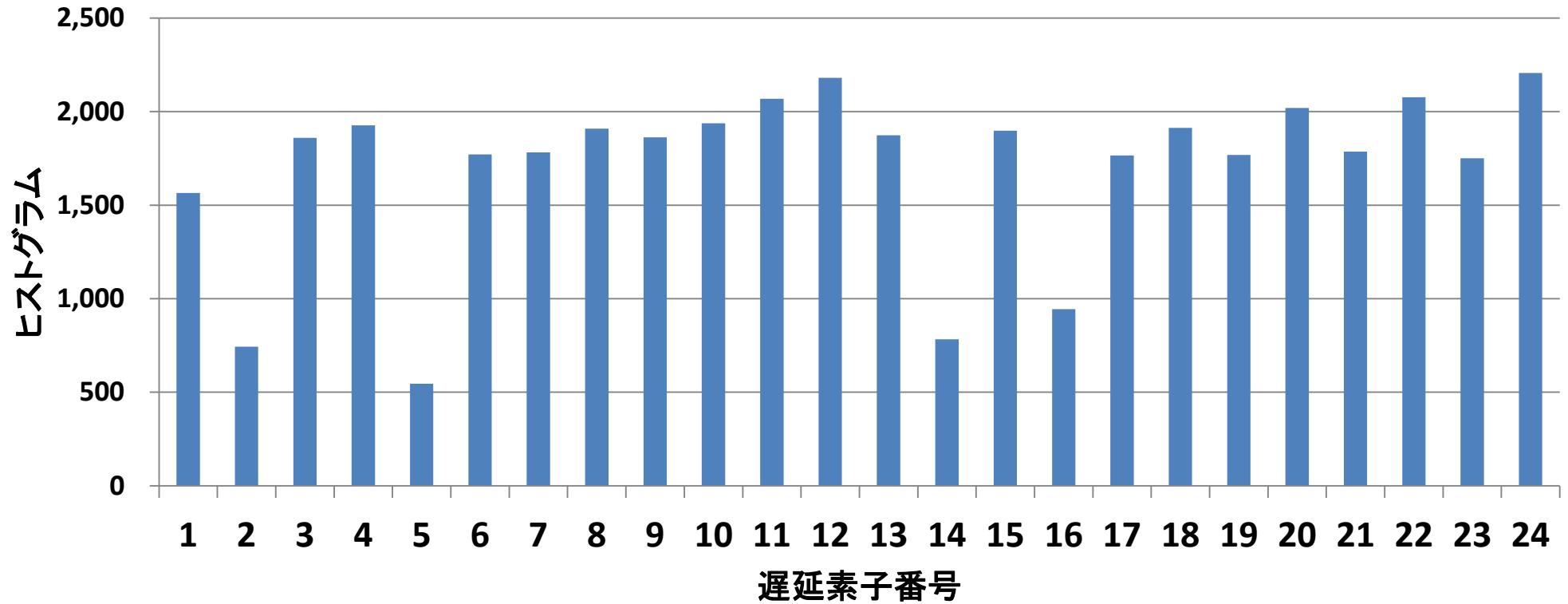

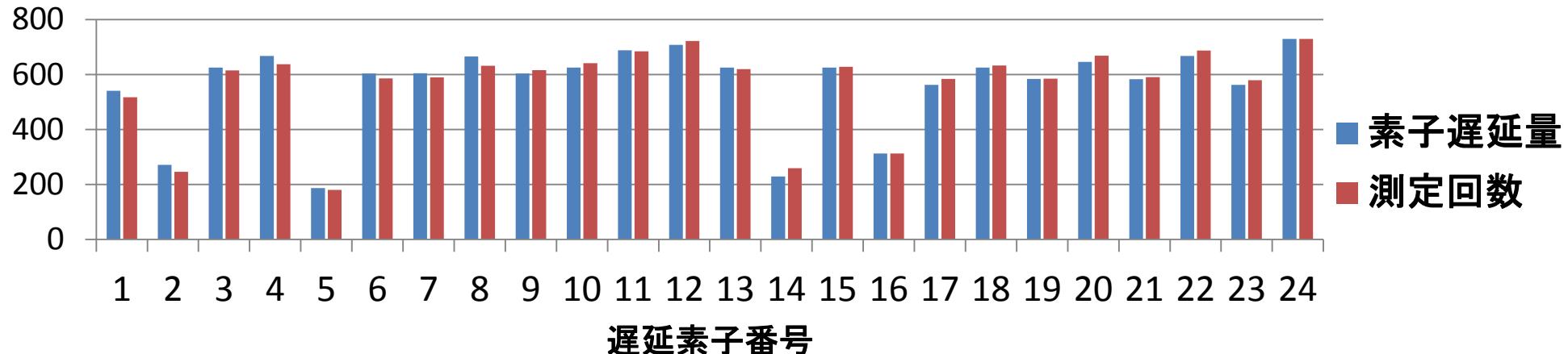

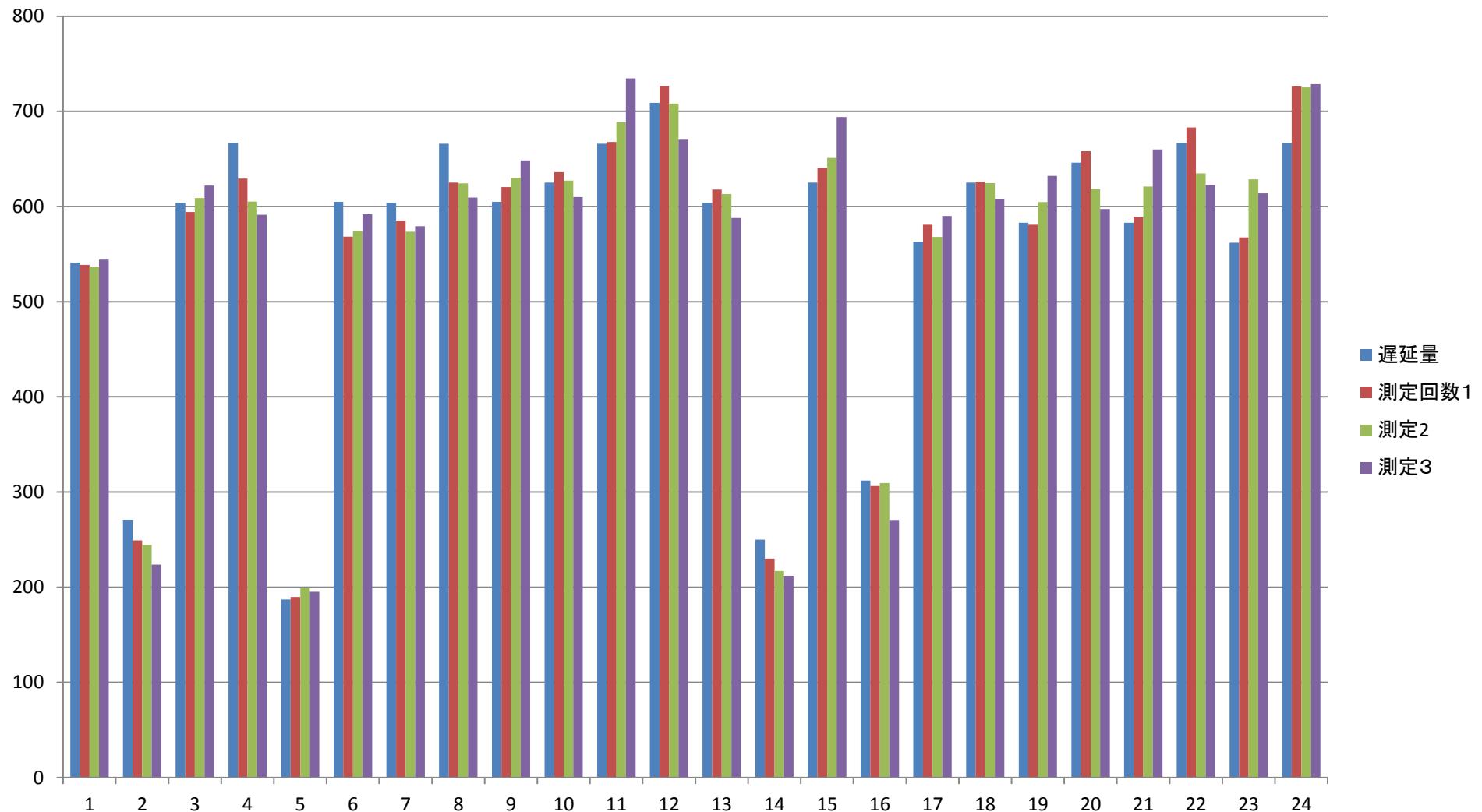

自己校正モードヒストグラム

- 合計40,934回、各ビットあたり平均1,700回を記録

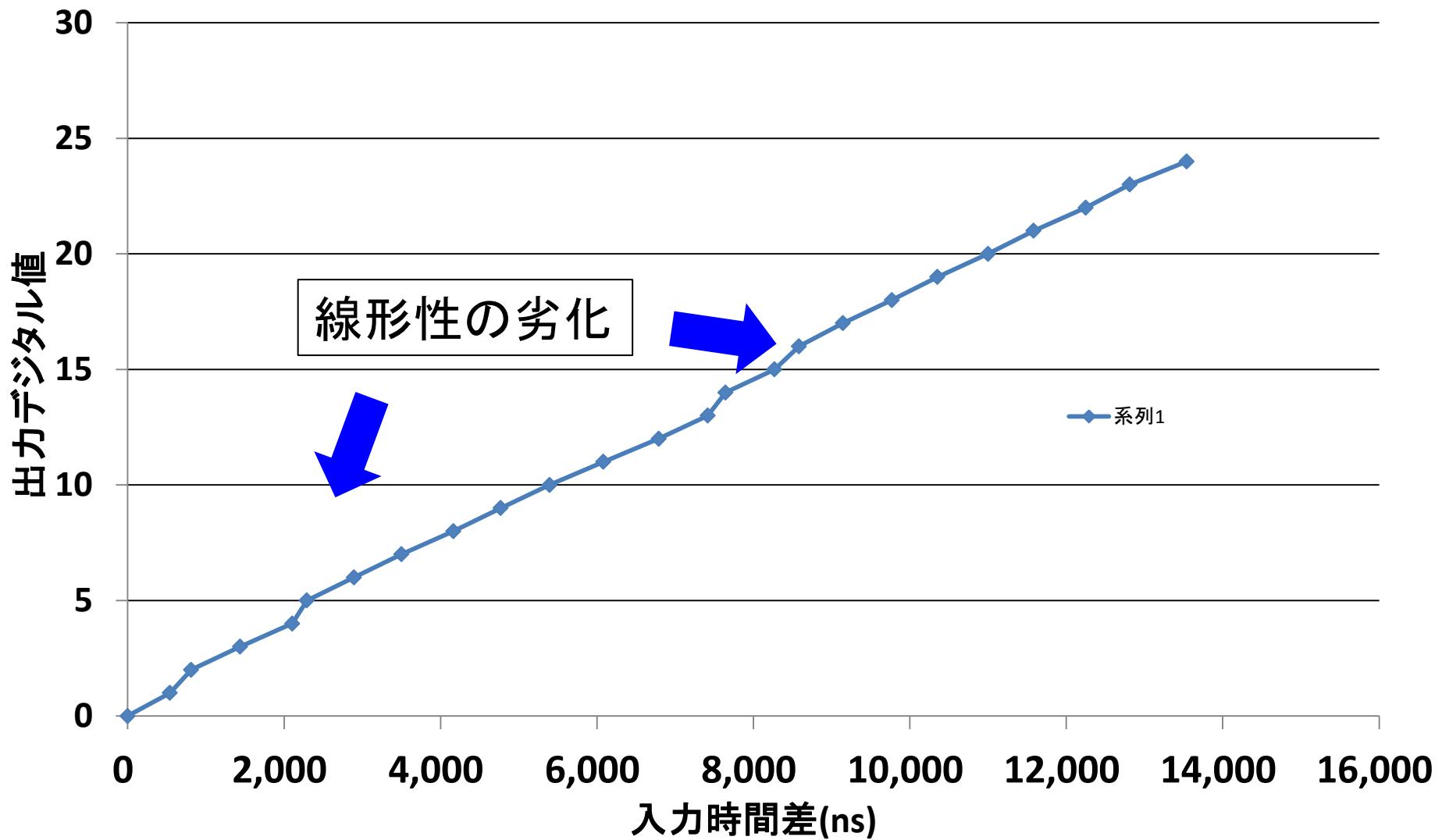

# 通常TDCモード測定結果

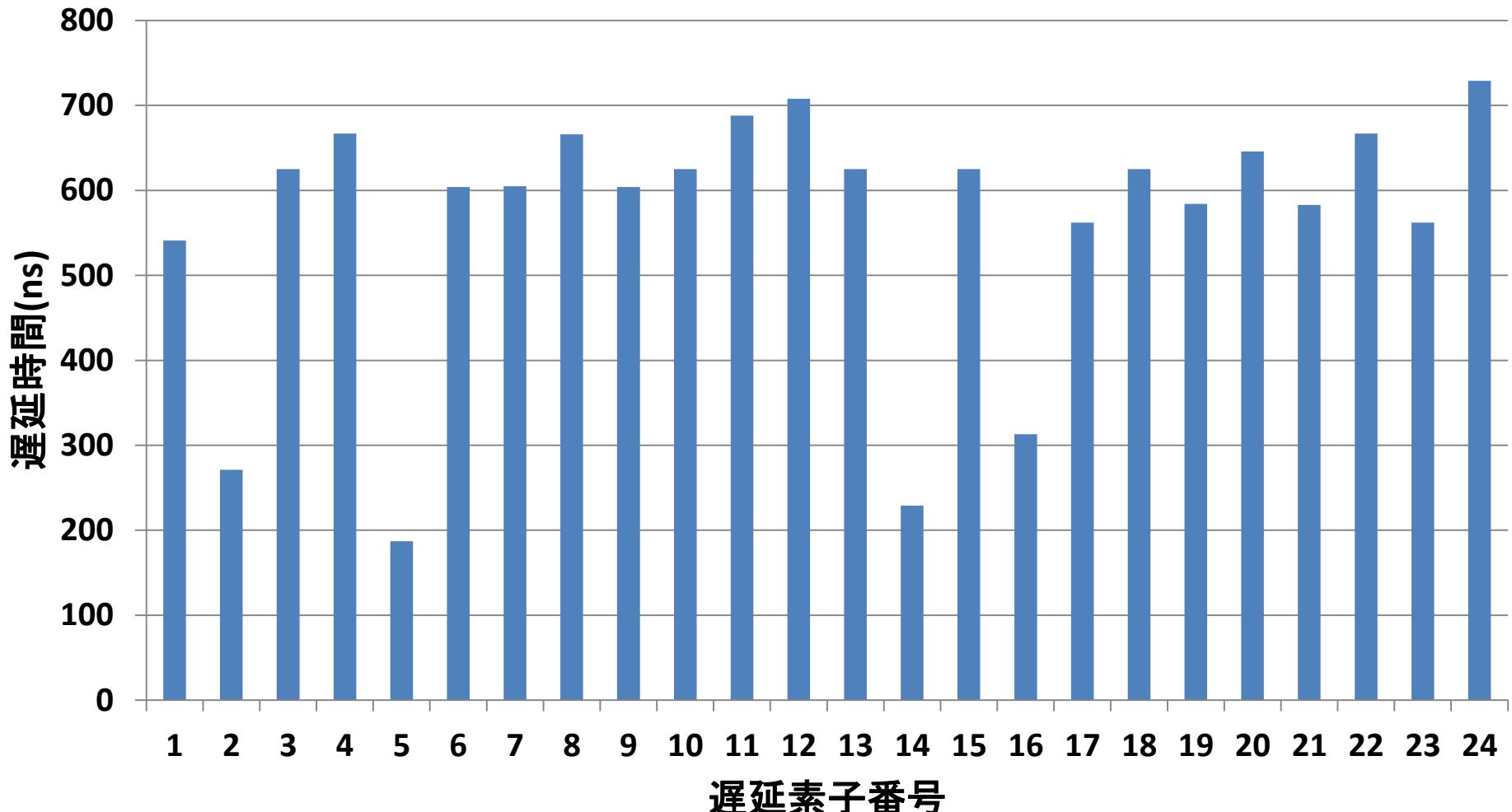

# 各素子遅延時間の計算

- TDCの通常測定モードにより時間差-デジタル値変換特性を計測

- フラッシュ型TDCでは下段から順に信号が伝搬

- (指定ビットのしきい値) – {(指定ビット – 1ビット)のしきい値}により遅延素子の遅延量を計算

# 各遅延素子の遅延時間

各遅延素子の遅延時間

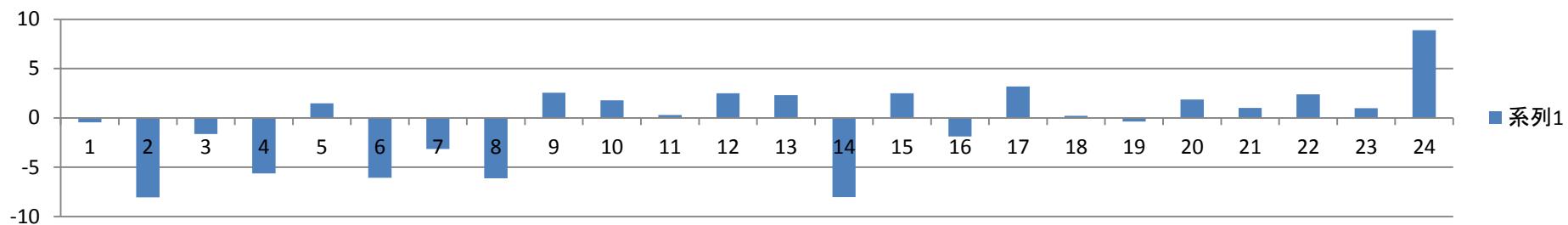

# ヒストグラムと遅延時間の相関

各素子遅延量とヒストグラム' (=ヒストグラム/3.02)

遅延量とヒストグラムの誤差(%)

# 自己校正の計算

自己校正モードで取得したヒストグラムより各遅延素子毎の総和を算出

例 :  $Pin4 = 568(Pin1) + 743(Pin2) + 1860(Pin3) + 1927(Pin4) = 6094$

校正係数 = 実際の測定回数総和 / 全測定回数総和

例 :  $Pin4 = 6094 / 40934 = 0.148898226$

校正情報

通常測定結果

(出力デジタル値)

例 : 4

校正係数 × 24 より出力値校正

例 :  $Dout(4) = 24 \times 0.148898226 \approx 3.57$

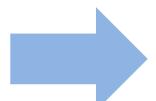

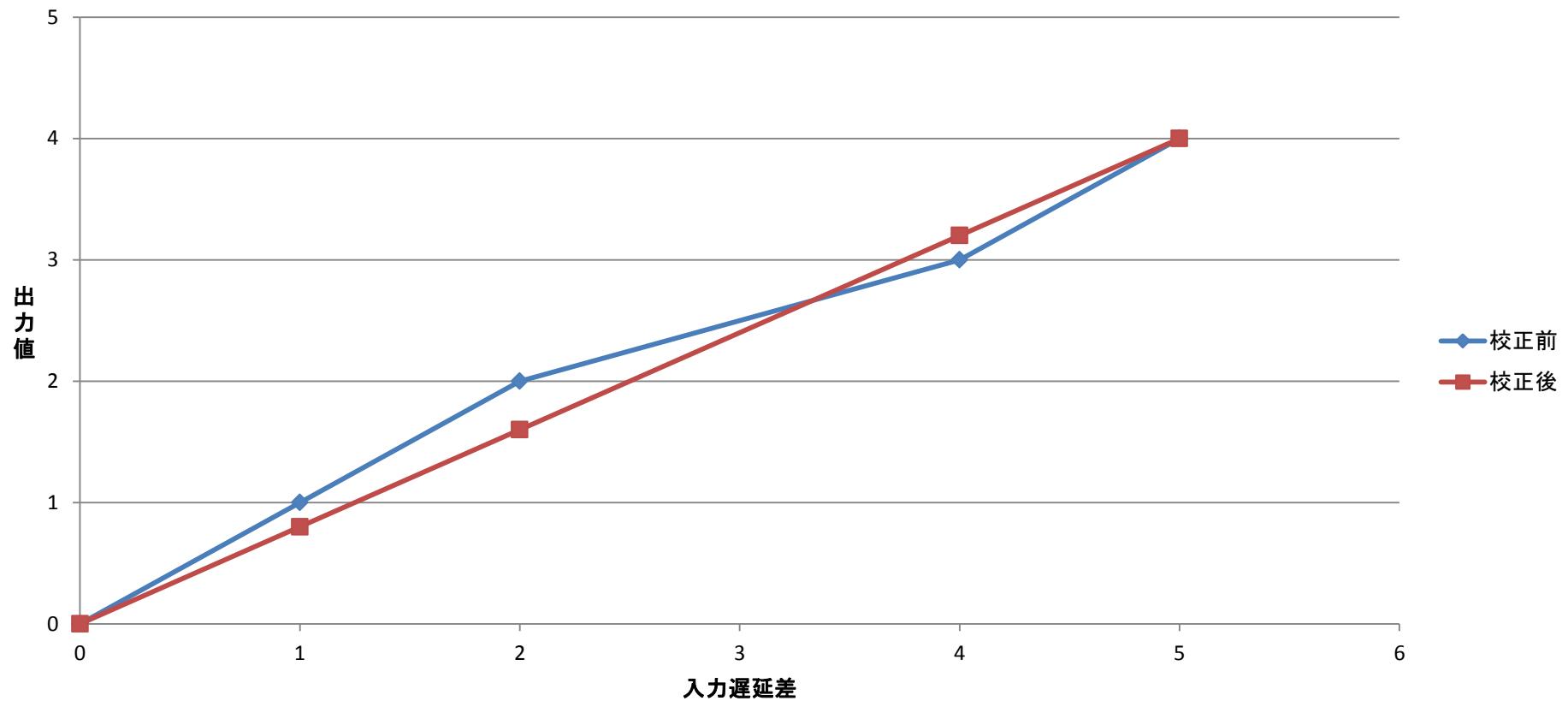

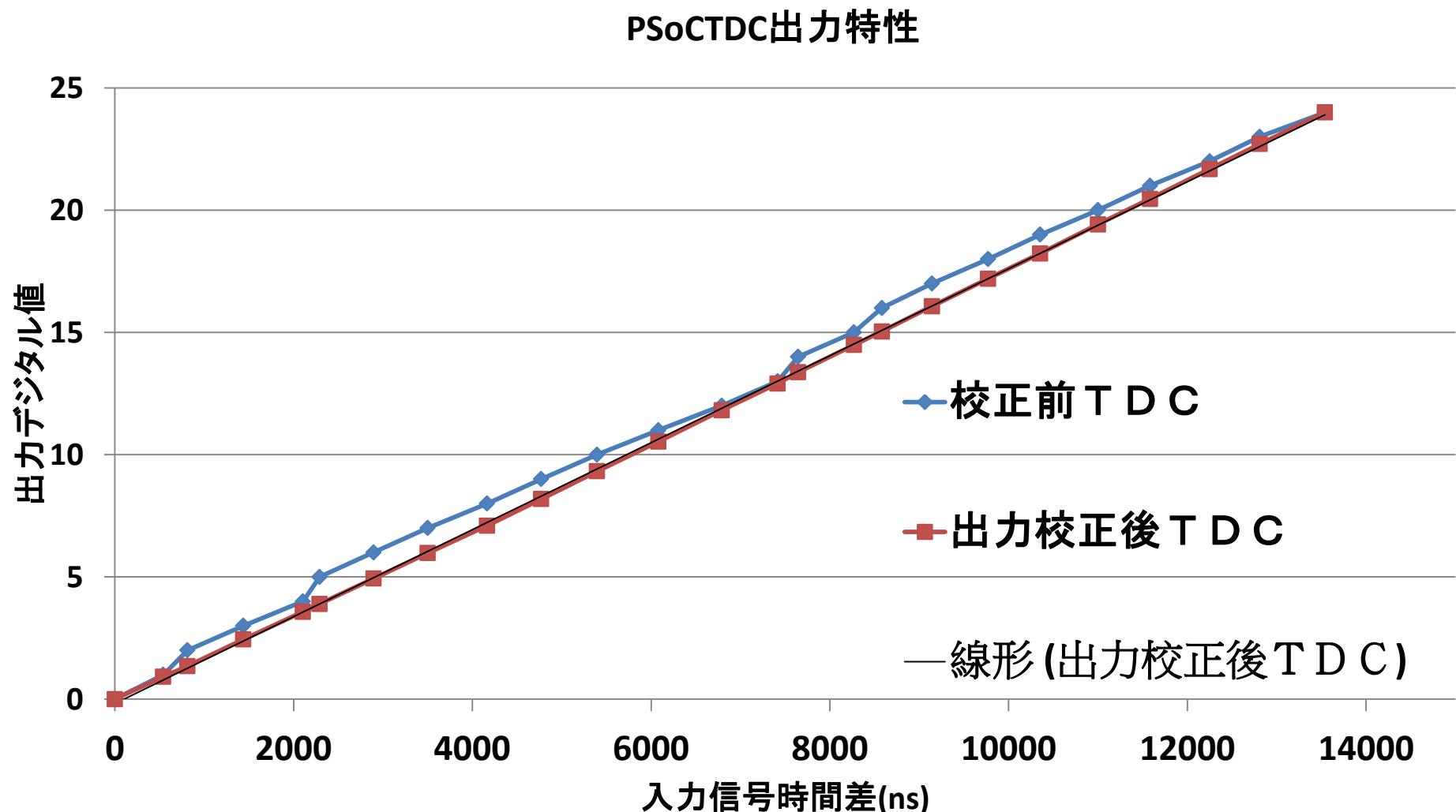

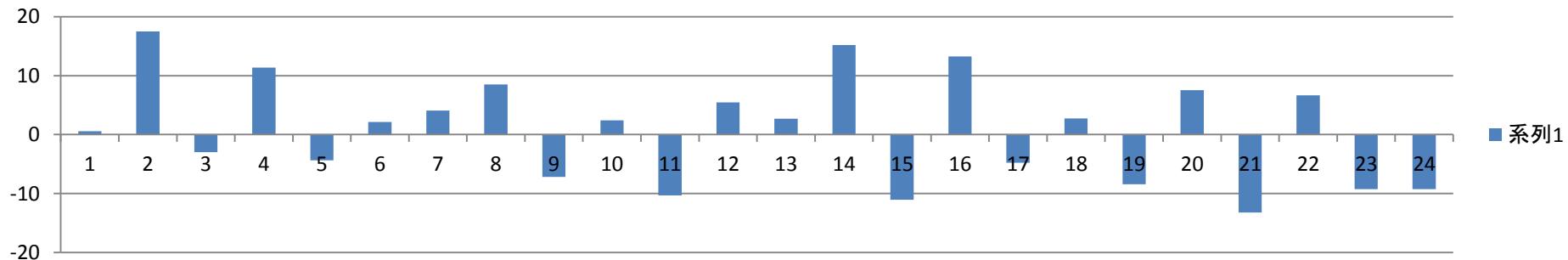

# 自己校正前後のTDC入出力特性

# 校正の評価

最小二乗法を用いて線形近似直線を求め、線形近似直線との誤差を計算

$$gain = \frac{N \times K_4 - K_1 \times K_2}{N \times K_3 - K_1^2} \quad offset = \frac{K_2}{N} - gain \times \frac{K_1}{N} \quad N : データ数(24)$$

i : 出力数

$$K_1 = \sum_{i=0}^{N-1} i \quad K_2 = \sum_{i=0}^{N-1} S(i) \quad K_3 = \sum_{i=0}^{N-1} i^2 \quad K_4 = \sum_{i=0}^{N-1} i \times S(i) \quad S(i) : \text{入力遅延差のしきい値}$$

$$INL(i) = \frac{S(i) - (gain_{bestfit} \times i + offset_{bestfit})}{V_{LSB}}$$

INL: 積分非直線性誤差

近似直線を取り、誤差を1 LSBの値で正規化

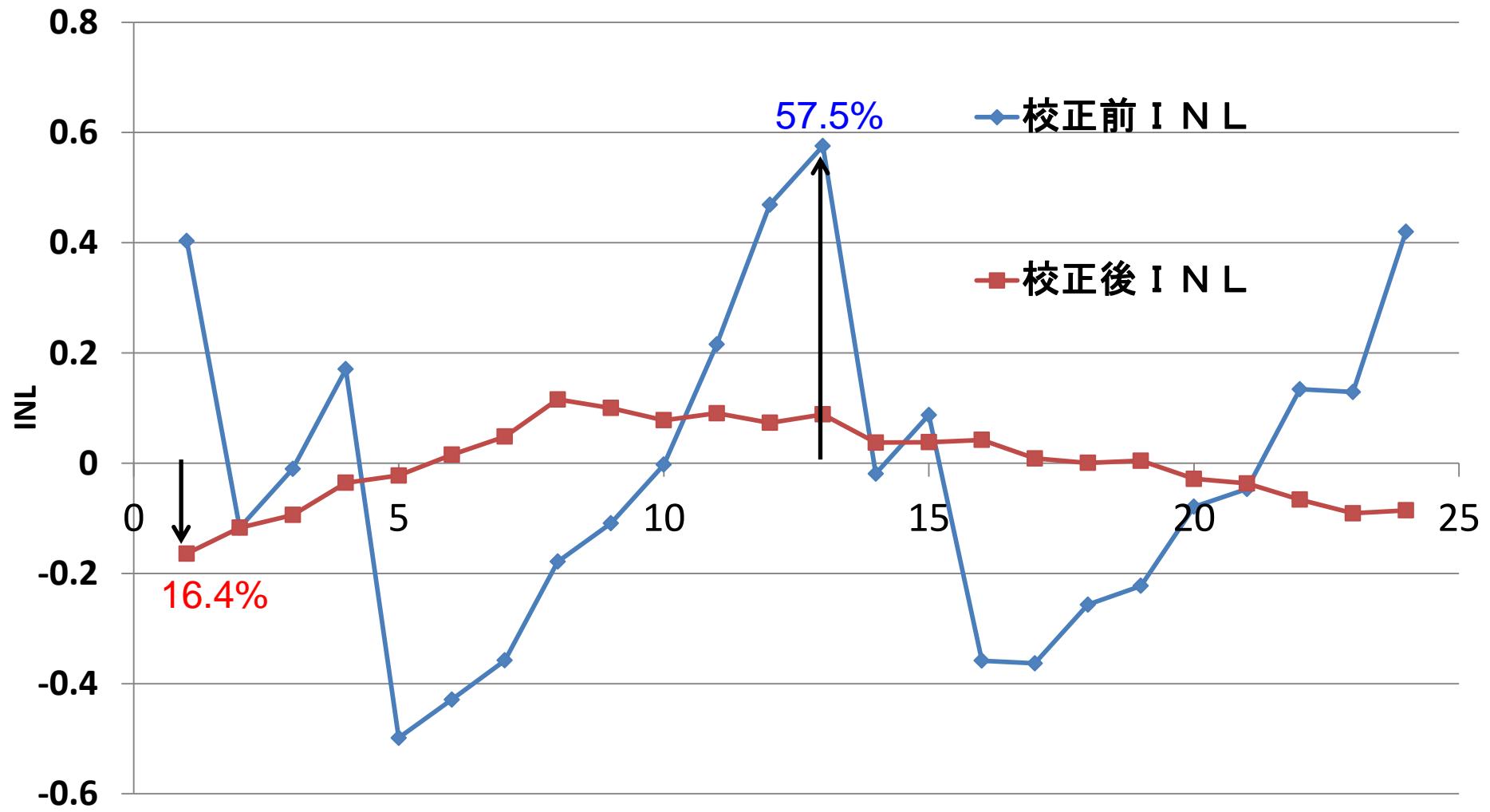

# 校正前後のINL

# アウトライン

---

- 研究背景

- TDCの回路構成と線形性の自己校正原理

- アナログFPGAによる試作

- 測定結果・評価

- まとめ

# まとめ

---

- ・ アナログFPGAで自己校正TDCを実装した

- ・ 実装したTDCにより時間-デジタル値変換測定を行った

- ・ ヒストグラム法によるTDCの線形性の出力校正によって

INL最大57.5%が校正後最大16.4%まで減少を

実測で確認できた。

# 今後の課題

完全な線形にはならず。

理由として

- 通常測定モードの入力可能な時間差信号の分解能不足

- 測定回数の不足

ヒストグラムの増加による更なる線形性の向上

LSIタイミング試験システムでの

BOST (Built-Out Self-Test)として展開していく。

# ありがとうございました

Time continues indefinitely.

We are analog designers,

but we appreciate digital technology.

- ・ 横川電機 加藤さん

ADCと同じコンセプトで良いですか？

PSoCはビルドのたびにレイアウトが変わり、遅延も

変わるために面白い研究だと思います。

– ADCと同じコンセプトだと思います。

- ・ 東京都市大学 傘先生

24レベルであったが、ADCでは2のN乗が普通、な

ぜ24レベルであったか？ハードウェアの制限か？

– はい、今回のPSoCで限界まで分解能を増やすため

24レベルとしました。

- 村田製作所

加藤先生のものよりも良い点は何？

- 可変遅延を用いたこと。

- 座長

遅延素子の方での校正は行わないのか？

- いずれは行いたい

入力可能時間差は全体の遅延素子の遅延量で制限される。

# 校正方法の詳細

- 各遅延素子の遅延量の比がヒストグラム

- フラッシュ型TDCにおいて、下位の遅延素子を通って上位の出力が出る

-

- $$\frac{\text{遅延素子の総和測定回数}}{\text{全体の総和測定回数}} (= \text{フルスケールに対する\%})$$

より、出力ビット毎の総遅延量に対する割合を導出

(これを校正係数とする)

フルスケール  $D_{FS}$  を決め校正係数を掛け出力校正

# 校正例

| 遅延量               | 1                               | 1                               | 2                               | 1               |

|-------------------|---------------------------------|---------------------------------|---------------------------------|-----------------|

| 遅延量和<br>(TDCしきい値) | 1                               | 2                               | 4                               | 5               |

| 遅延量から出る<br>測定回数   | 10                              | 10                              | 20                              | 10              |

| 校正前出力             | 1                               | 2                               | 3                               | $4 (=D_{FS})$   |

| 測定回数総和            | 10                              | 20                              | 40                              | 50              |

| 校正係数              | $\frac{10}{50}$                 | $\frac{20}{50}$                 | $\frac{40}{50}$                 | $\frac{50}{50}$ |

| 校正後出力             | $4 \times \frac{10}{50} (=0.8)$ | $4 \times \frac{20}{50} (=1.6)$ | $4 \times \frac{40}{50} (=3.2)$ | 4               |

# 校正方法例

TDC校正例

# PSoC遅延素子

- 内部の $5.6[k\Omega]$

- 外部接続の可変キャパシタで遅延を実現

# DNL

---

- $DNL(i) = \frac{(V_D - V_{D-1})}{V_{LSB}} - 1$

# DNL

# 自己校正後TDC出力校正

# 自己校正モードの端の考察

- 今回の回路図では、 $D_0$ ,  $D_{LAST}$ において測定回数が大幅に上昇せず

# 土井先輩の論文

---

- P26～31にかけて端の出力回数が高い部分は見られず

- P38～のバーニア型～においては、p39のコードヒストグラムで端の値が多い

- D0とD8の値が2倍近い

- しかし、回路図上にD0が記載されていないためD0の理由は不明

- D8はTDCの最終段にあたるため、D8→インバータがありインバーターの遅延量が大きいため測定回数が多い？

# 自己校正モードの端の考察

---

- $D_{LAST}$ ではインバータ→RC遅延の順で接続されているため、測定回数の増加が無かったのではないか

# 測定他

# 誤差の導出式

- 測定回数' = 測定回数 ÷  $\frac{\text{合計測定回数}}{\text{合計遅延量}}$

- 誤差(%) =  $100 \times \left( \frac{\text{測定回数}'}{\text{遅延量}} - 1 \right)$

# 3回の測定

## 測定1

## 測定2

## 測定3