# Multi-bit Delta-Sigma TDC for Timing Measurement

Yuta Arakawa, Yusuke Osawa, Haruo Kobayashi, Osamu Kobayashi Dept. of Electrical Engineering, Graduate School of Engineering, Gunma University Kiryu Gunma 376-8515 Japan, email: t12801604@gunma-u.ac.jp

# Background

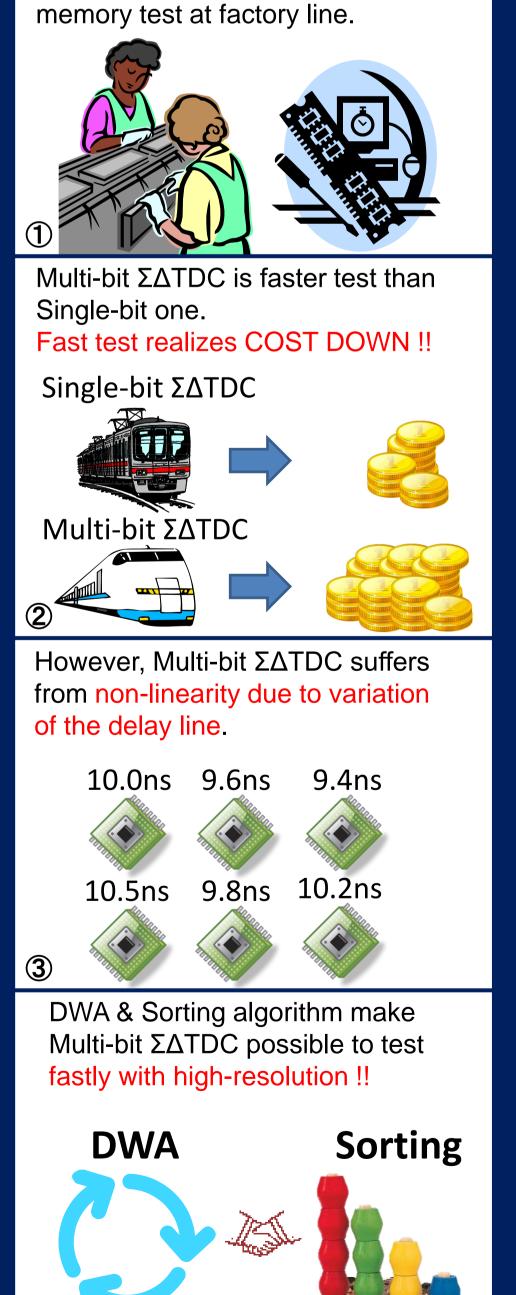

#### **Research Objective** Testing timing difference between two repetitive digital signals Ex. Data and clock in Double Data Rate (DDR) memory Short testing time Good accuracy Implement with small circuitry **Our Work** Focus on Multi-bit ΣΔTime-to-Digital Converter (TDC) Repetitive digital signals ΣΔ TDC can be used Simple circuit Fine resolution Testing time Single-bit ΣΔ TDC Long Multi-bit ΣΔ TDC Short Linearity Single-bit ΣΔ TDC Good Multi-bit ΣΔ TDC due to delay elements mismatches

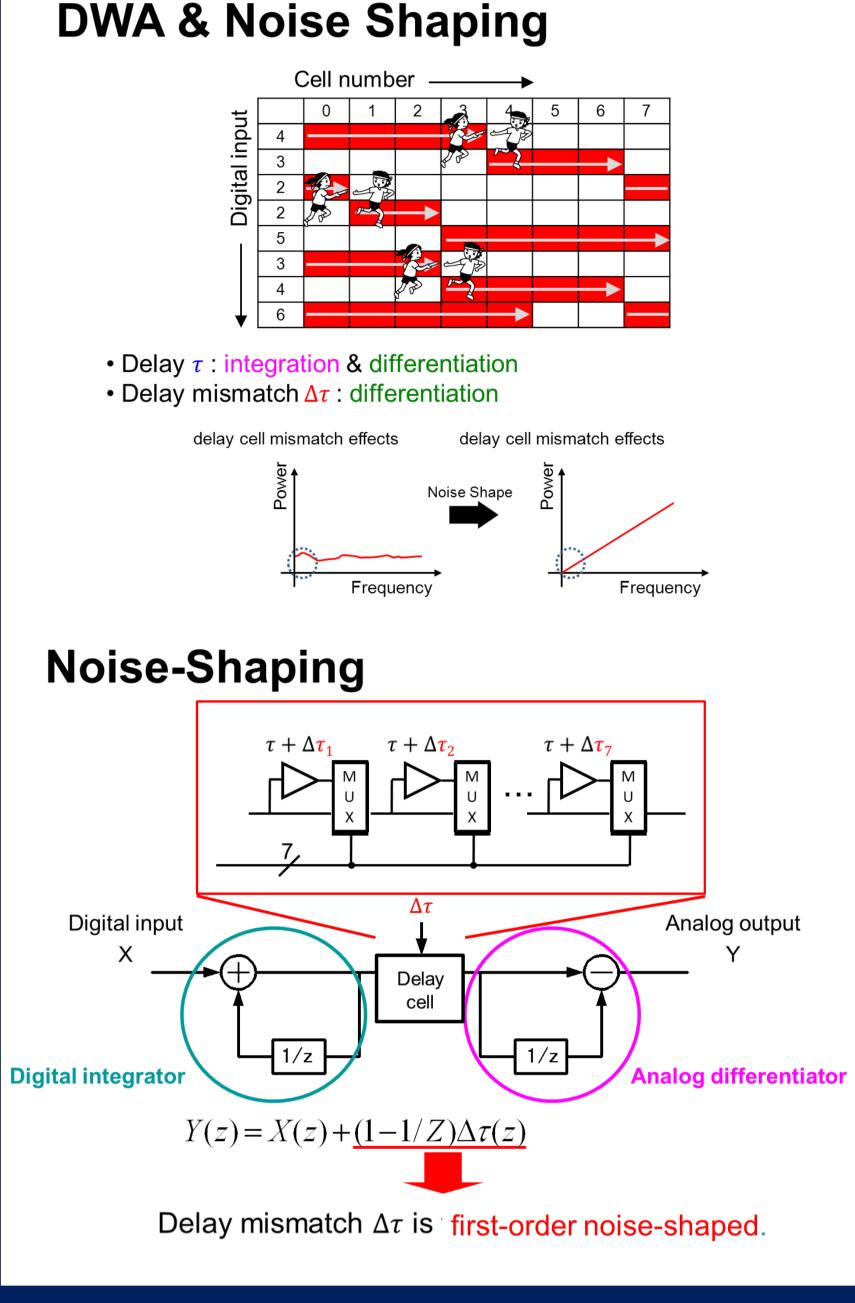

#### Mechanism of DWA

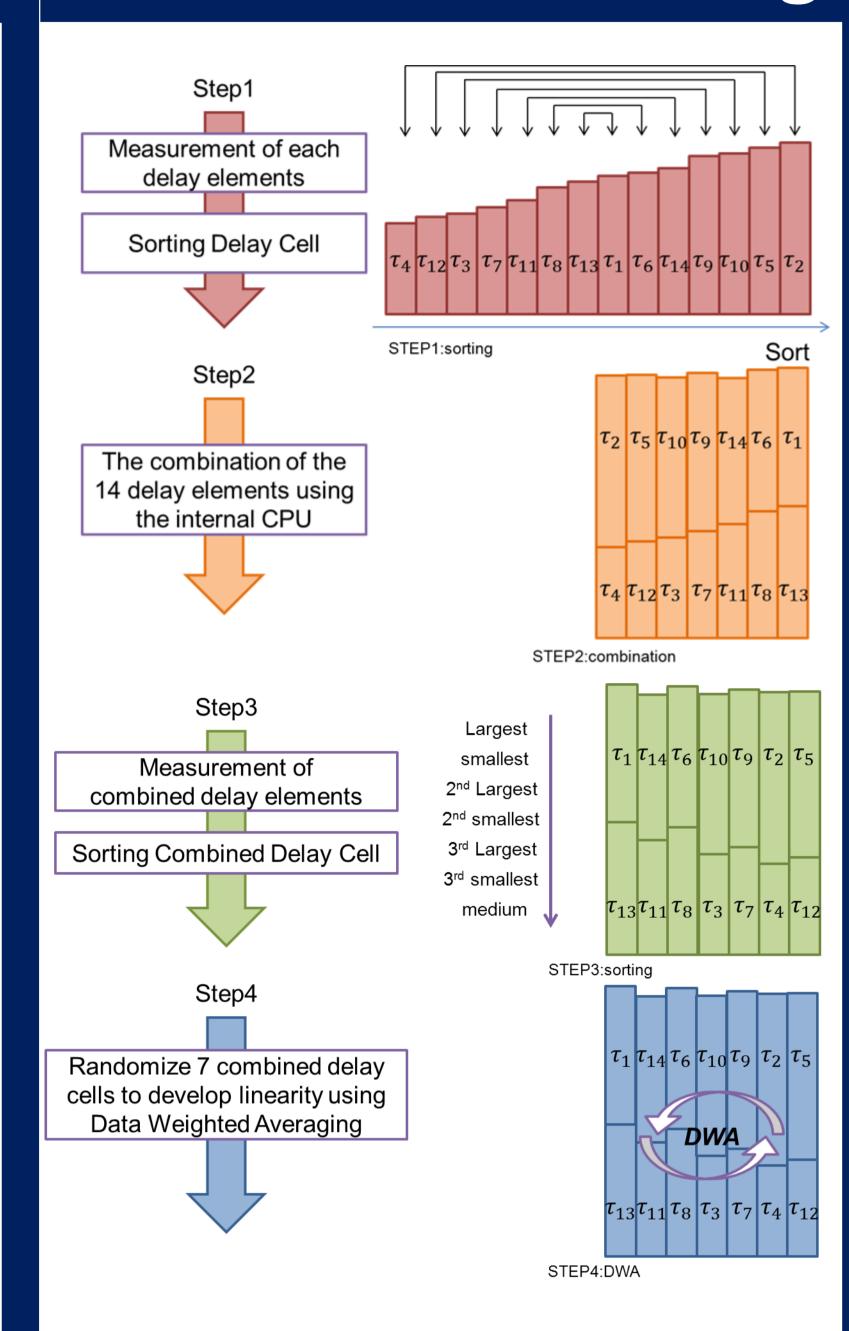

#### **Procedure of Sorting**

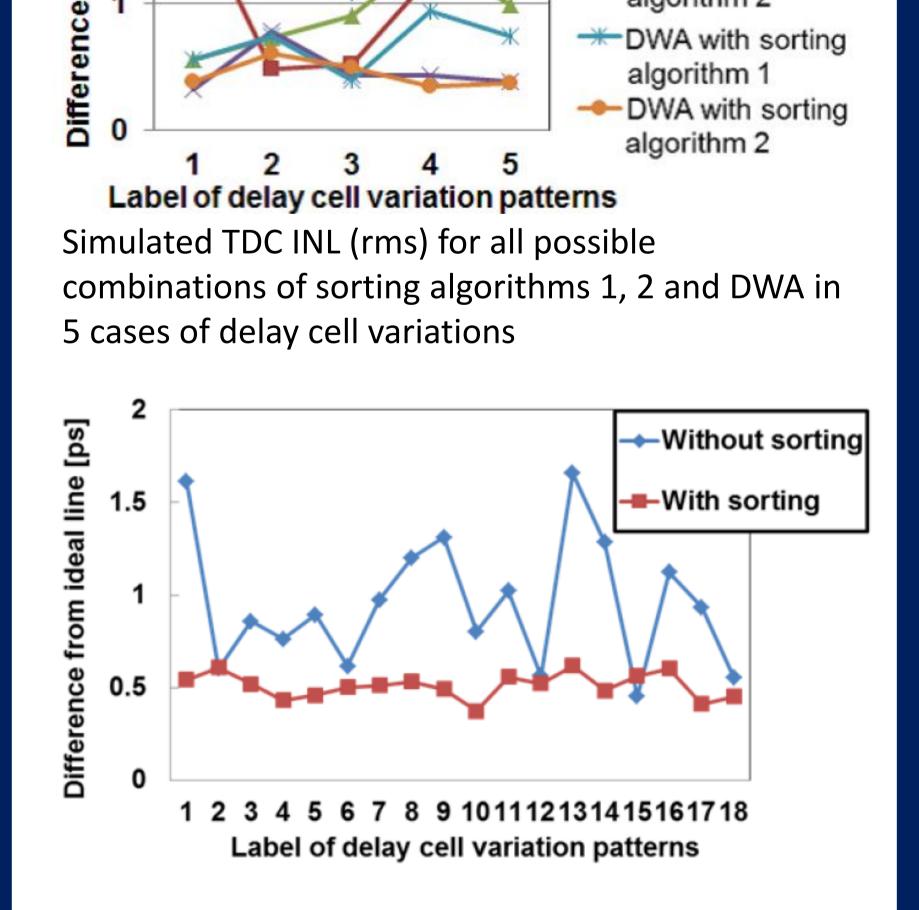

#### Matlab Simulation result

Three methods for their compensation

DWA, Self-calibration, Delay cell sorting

→ nothing

--only DWA

----only sorting

---only sorting

algorithm 1

algorithm 2

DWA with sorting

Averaged (rms) integral nonlinearity with and without sorting algorithm 2 in 18 cases of delay cell variations.

TDC circuit is widely used for timing

measurement, for example, DDR

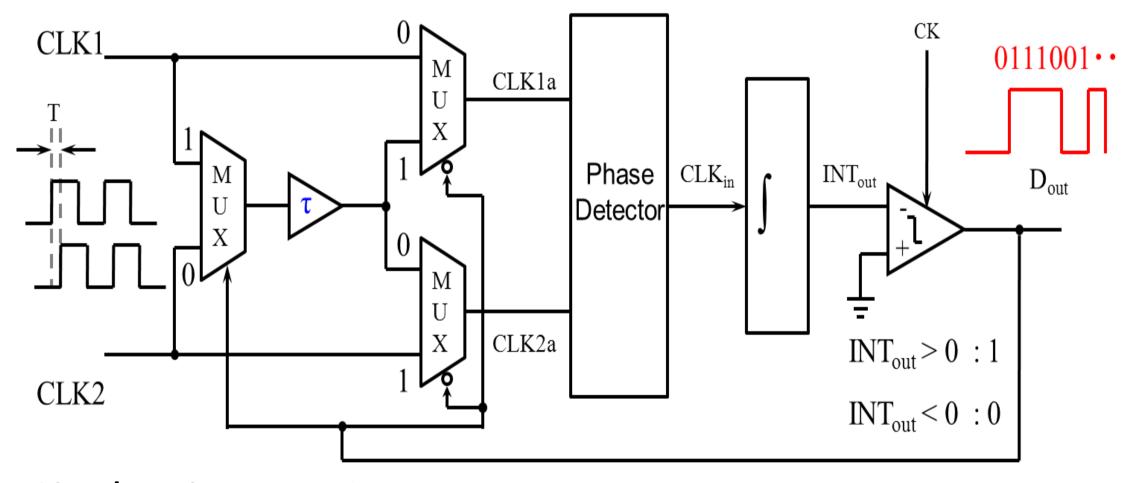

## Structure of ΔΣTDC

Single-Bit ΣΔ TDC

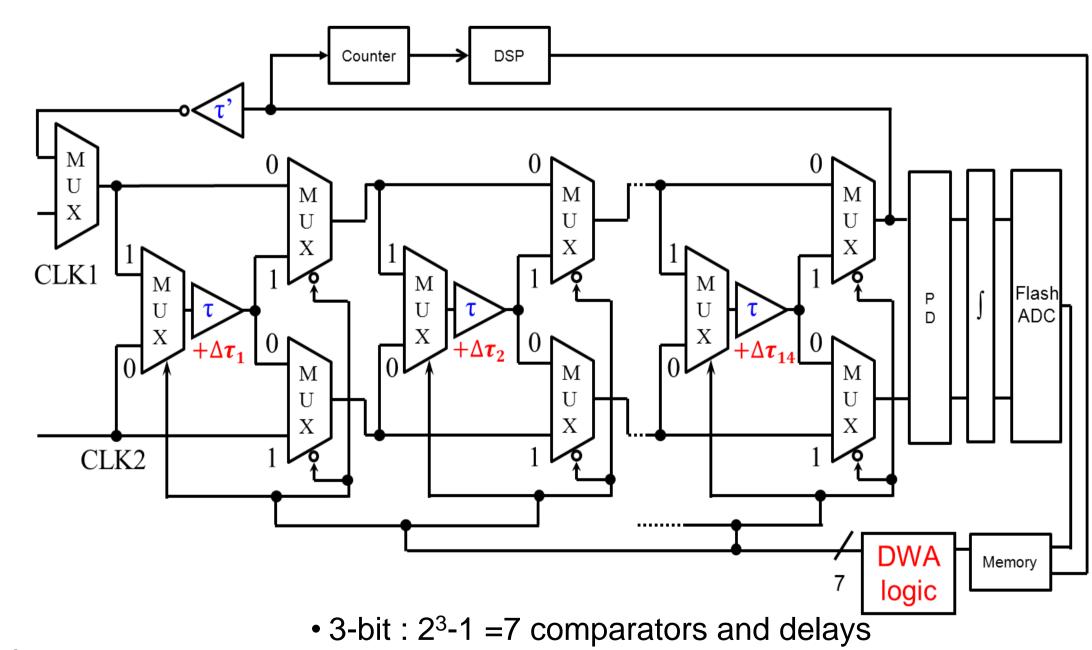

Multi-Bit ΣΔ TDC

- Fine time resolution with a given measurement time

- Shorter measurement time with a given time resolution

### Conclusion

from ideal line [ps]

|            | Flash TDC | 1-bit ΣΔ<br>TDC | Multi-Bit ΣΔ<br>TDC<br>(w/o correction) | Multi-Bit ΣΔ<br>TDC<br>(w/ correction) |

|------------|-----------|-----------------|-----------------------------------------|----------------------------------------|

| Area       | ×         | 0               | 0                                       | 0                                      |

| Resolution | ×         | 0               | 0                                       | 0                                      |

| Accuracy   | Δ         | 0               | ×                                       | 0                                      |

| Time       | 0         | ×               | 0                                       | 0                                      |

- We propose to use  $\Sigma\Delta$  TDC for digital signal timing measurement

- Multi-bit ΣΔ TDC

- Short measurement time

- > Fine time resolution

- Non-linearity due to mismatches among delay cells Three techniques to improve linearity

- -DWA

- Self-Calibration (signal is "time")

- Sorting