#### (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

テーマコード (参考)

特開2011-259219 (P2011-259219A)

(43) 公開日 平成23年12月22日(2011, 12, 22)

(51) Int.Cl. **HO3M 1/14 (2006.01)**

F I HO3M 1/14

Α

5J022

審査請求 有 請求項の数 8 OL (全 22 頁)

(21) 出願番号 (22) 出願日 特願2010-132025 (P2010-132025) 平成22年6月9日 (2010.6.9) (71) 出願人 396023993

株式会社半導体理工学研究センター神奈川県横浜市港北区新横浜3丁目17番

地2 友泉新横浜ビル6階

(74)代理人 100099759

弁理士 青木 篤

(74)代理人 100092624

弁理士 鶴田 準一

(74)代理人 100119987

弁理十 伊坪 公一

(74) 代理人 100141254

弁理士 榎原 正巳

(74)代理人 100114177

弁理士 小林 龍

最終頁に続く

(54) 【発明の名称】パイプライン・AD変換回路

#### (57)【要約】

【課題】入力範囲に応じて精度の異なるパイプライン・AD変換回路の実現。

【解決手段】直列に接続された複数のアナログ / デジタル変換ユニット30,37と、複数のアナログ / デジタル変換ユニットのサブ変換結果から、入力アナログ信号Vinのデジタル変換値Doutを算出するデジタル演算回路38と、を備え、各アナログ / デジタル変換ユニット30は、サブAD変換器32と、アナログ入力信号からサブAD値に応じたアナログ減算信号を減算して残差信号を発生し、残差信号を増幅して出力する増幅DA変換器39と、を備えるパイプライン・AD変換回路であって、初段のサブAD変換器32は、入力範囲-Vref,Vrefを少なくとも4個以上のサブ範囲に分割して、入力アナログ信号がいずれのサブ範囲に入るかを判定し、4個以上のサブ範囲の大きさが異なる。

【選択図】図5

#### 【特許請求の範囲】

#### 【請求項1】

直列に接続された複数のアナログ/デジタル変換ユニットと、

前記複数のアナログ / デジタル変換ユニットのサブ変換結果から、入力アナログ信号のデジタル変換値を算出するデジタル演算回路と、を備え、

各アナログ / デジタル変換ユニットは、

アナログ入力信号をサブAD値に変換するサブAD変換器と、

前段から入力されるアナログ入力信号から、前記サブAD値に応じたアナログ減算信号を減算して残差信号を発生し、前記残差信号を増幅して出力する増幅DA変換器と、を備えるパイプライン・AD変換回路であって、

初段の前記アナログ / デジタル変換ユニットの前記サブ A D 変換器は、前記入力アナログ信号の入力範囲を少なくとも 4 個以上のサブ範囲に分割して、前記入力アナログ信号がいずれの前記サブ範囲に入るかを判定し、

前記4個以上のサブ範囲の大きさが異なることを特徴とするパイプライン・AD変換回路。

#### 【請求項2】

前記入力アナログ信号の入力範囲の中心付近の前記サブ範囲の大きさは、前記入力アナログ信号の入力範囲の周辺の前記サブ範囲の大きさより小さい請求項1に記載のパイプライン・AD変換回路。

#### 【請求項3】

前記入力アナログ信号の入力範囲の中心付近の前記サブ範囲の大きさは、前記入力アナログ信号の入力範囲の周辺の前記サブ範囲の大きさより大きい請求項1に記載のパイプライン・AD変換回路。

#### 【請求項4】

前記サブ範囲は、11個であり、

前記サブ範囲の大きさは、前記入力アナログ信号の入力範囲の一方の端から他方の端の方向に対して、4:4:3:2:2:2:2:3:4:4である請求項2に記載のパイプライン・AD変換回路。

#### 【請求項5】

初段の前記アナログ / デジタル変換ユニットの前記サブ A D 変換器は、前記サブ範囲の境界に対応した閾値を有する 1 0 個の比較器を備える請求項 4 に記載のパイプライン・ A D 変換回路。

#### 【請求項6】

初段の前記アナログ / デジタル変換ユニットの前記サブ A D 変換器は、 2 1 個の比較器を備え、

#### 【請求項7】

初段の前記アナログ / デジタル変換ユニットの前記増幅 D A 変換器は、

前記21個の比較器のうちの6個の比較器を含む第1グループの比較結果に基づいて制御信号を発生する制御信号発生器と、

前記21個の比較器のうちの前記第1グループ以外の8個の比較器を含む第2グループの比較結果の組と、前記21個の比較器のうちの前記第1および第2グループ以外の7個の比較器を含む第3グループの比較結果と論理値ゼロの組との一方を選択するマルチプレクサと、

前記マルチプレクサの出力に基づいて、アナログシフト信号を発生するサブDACと、前記入力アナログ信号から前記アナログシフト信号を減算する減算器と、

前記減算器の出力を増幅する残差アンプと、を備える請求項6に記載のパイプライン・AD変換回路。

10

20

30

40

#### 【請求項8】

前記サブDAC、前記減算器および前記残差アンプは、一体に形成される請求項7に記載のパイプライン・AD変換回路。

#### 【発明の詳細な説明】

【技術分野】

#### [0001]

本発明は、パイプライン・AD変換回路に関する。

#### 【背景技術】

#### [0002]

現状では、高速で高精度のアナログ・デジタル(AD)変換器の変換方式は、並列型(フラッシュ型)、パイプライン型、型に限定される。その中でも、パイプライン・AD変換回路は、小型化可能で低消費電力化が可能である。

#### [00003]

パイプライン・ A D 変 換 回 路 は、 A D 変 換 を 、 複 数 段 の パイ プ ラ イン ・ ス テ ー ジ に 分 け て行い、最上位ビット(MSB)から最下位ビット(LSB)まで、各段で1ビットずつ 順 番 に A D 変 換 す る 。 各 パ イ プ ラ イ ン ・ ス テ ー ジ を 構 成 す る ア ナ ロ グ / デ ジ タ ル 変 換 ユ ニ ットは、 1 ビット A D 変換器、 1 ビット・デジタル - アナログ ( D A ) 変換器と、 残差ア ンプ、サンプルホールド回路と、を有する。アナログ入力信号は、初段のパイプライン・ ステージで、 1 ビットAD変換されてMSBが決定され、その決定されたMSBを1ビッ ト D A 変 換 器 で 一 旦 ア ナ ロ グ 信 号 に 戻 し 、 残 差 ア ン プ で ア ナ ロ グ 入 力 信 号 と の 差 を 演 算 す る。ここで得られたアナログ信号はMSBのAD変換で生じた量子化誤差になる。この量 子化誤差を次段のパイプライン・ステージで再び1ビットAD変換して2ビット目を決定 する。以下、順番にパイプライン・ステージの最終段まで同様の動作を繰り返し、LSB までの全ビットを決定する。特定のアナログ信号のサンプルに注目すると、LSBまでA D 変換が完了し、データが決定するまでにパイプライン・ステージ数だけクロック数を必 要とするので、最初にアナログ信号が入力されてからデータが確定するまでに時間を要す る。言い換えればレイテンシが長い。しかし、一旦データが確定すれば、その後はクロッ クごとに新たなアナログ信号のサンプルに対応するデジタル変換値が出力されるので、ス ル ー プ ッ ト は フ ラ ッ シ ュ 型 A D 変 換 回 路 と 同 様 に 、 1 ク ロ ッ ク で あ る 。

#### [0004]

さらに、1パイプライン・ステージのAD変換のビット数を複数ビット以上にして、上記のレイテンシが長いという問題を低減したパイプライン・AD変換回路も知られている。この場合、すべてのパイプライン・ステージのAD変換のビット数を複数ビットにするのではなく、初段と最終段のパイプライン・ステージのAD変換のみを複数ビットにするのが一般的である。

#### [0005]

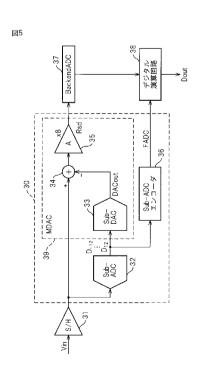

図 1 は、初段で 3 ビット A D 変換する 1 2 ビットのパイプライン・ A D 変換回路の構成を示す図である。図 1 に示すように、パイプライン・ A D 変換回路は、初段(Frontend)のパイプライン・ステージを構成するアナログ / デジタル変換ユニット 1 0 と、アナログ入力信号 V i n のサンプルホールド回路 1 1 と、後段の A D C パイプライン・ステージ(backend ADC) 1 7 と、デジタル演算回路 1 8 と、を有する。

#### [00006]

初段のアナログ / デジタル変換ユニット 1 0 は、 3 ビットサブ A D C (3bit sub-ADC) 1 2 と、 3 ビット D A C (3bit DAC) 1 3 と、減算器 1 4 と、増幅器 (A) 1 5 と、サブ A D C (subADC) エンコーダ 1 6 と、を有する。サンプルホールド回路 1 1 でサンプル & ホールドされたアナログ入力信号 V i n は、 3 ビットサブ A D C 1 2 および減算器 1 4 に入力される。増幅器 1 5 の出力は、後段の A D C パイプライン・ステージ 1 7 に入力される。一般に、 3 ビット D A C 1 3 と、減算器 1 4 と、増幅器 1 5 は、増幅 D A C (MDAC) 1 9 として一体に形成され、増幅した残差信号を保持するサンプルホールド機能を有し、これが次段のパイプライン・ステージのサンプルホールド回路として機能する。

10

20

30

#### [0007]

後段のADCパイプライン・ステージ17は、9ビットのAD変換を行い、例えば、1ビット×9段で構成される。後段のADCパイプライン・ステージ17の各段を構成するアナログ/デジタル変換ユニットは、1ビットであることを除けば、初段のものと同様の構成を有する。最終段のアナログ/デジタル変換ユニットは、サブADCのみを有すればよい。また、後段のADCパイプライン・ステージ17を1ビット×6段+3ビット×1段のパイプライン・ステージで構成する場合などもある。

#### [0008]

デジタル演算回路 1 8 は、初段のパイプライン・ステージ(SubADCエンコーダ 1 6 )の出力する 3 ビットのAD変換値FADCおよび後段のADCパイプライン・ステージ 1 7 の出力する 9 ビットのAD変換値BADCから、 1 2 ビットのAD変換出力Doutを生成する。

#### [0009]

また、2~6段目の1ビットパイプライン・ステージを、1.5ビットと称するアナログ/デジタル変換ユニットで構成して、前段のAD変換誤差を補正するように構成する場合もある。1.5ビットアナログ/デジタル変換ユニットは、比較器(コンパレータ)を2個有するサブADCで、アナログ入力信号が3つの範囲("00"、"01"、"10")のいずれかに入るかを判定する。1.5ビットアナログ/デジタル変換ユニットを使用することにより、前段のAD変換誤差をある程度補正できる。

#### [0010]

パイプライン・AD変換回路においては、増幅器15の線形性が精度に大きく影響する。増幅器15の線形性は、出力電圧範囲の中心付近の方が両端部分に比べて良好である。出力電圧の全範囲について良好な成形性を有する増幅器は、高いスルーレートを有し、その分消費電力が大きくなる。現状のパイプライン・AD変換回路では、増幅器の消費電力が大きな割合を占めており、低消費電力のパイプライン・AD変換回路を実現する上では、線形性を損なうことなく増幅器の消費電力を低減することが求められている。

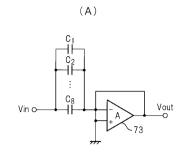

非特許文献 1 は、初段のパイプライン・ステージにおいて、増幅器の増幅率を、AD変換のビット数に対応した増幅率より小さくして、2段目に出力する残差信号の電圧範囲を制限して、低消費電力の増幅器を使用可能にすることを記載している。非特許文献 1 に記載された構成を図 1 のパイプライン・AD変換回路に適用すると、図 2 に示すような構成が得られる。なお、図 2 では、SubADCエンコーダおよびデジタル演算回路の図示を省略している。

#### [0011]

例えば、パイプライン・AD変換回路においては、初段のAD変換のビット数を3ビットとすると、アナログ入力信号の電圧範囲を8個のサブ範囲に分け、7個の比較器を有する3ビットサブADCでアナログ入力信号がいずれのサブ範囲に入るかを判定し、3ビットDACで判定したサブ範囲の中心を示す電圧を発生し、減算器でその電圧をアナログ入力信号から減算した後、増幅器で8倍に増幅する。これにより、増幅器の出力電圧の範囲は、入力電圧範囲と同じ大きさになる。

#### [0012]

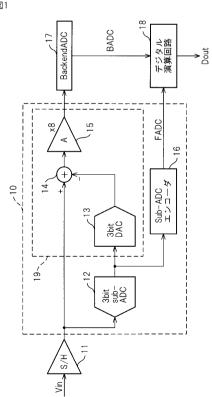

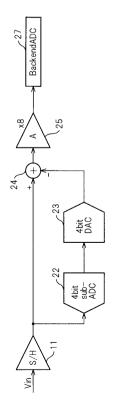

図2に示すパイプライン・AD変換回路では、初段のパイプライン・ステージのアナログ / デジタル変換ユニットは、4ビットサブADC22と、4ビットDAC23と、を有するが、増幅器25の増幅率は8倍である。このため、アナログ入力信号の電圧範囲を16個のサブ範囲に分けてアナログ入力信号がいずれのサブ範囲に入るかを判定されるが、増幅率は8倍であるために、増幅器25の出力電圧の範囲は、アナログ入力信号の電圧範囲の1/2になる。したがって、増幅器の非線形性誤差の大きな周辺部を使用しないため、精度が向上する。

#### [0013]

図1および図2で説明したように、初段のAD変換を2ビット以上で行うパイプライン・AD変換回路が知られている。これらのパイプライン・AD変換回路では、アナログ入

10

20

30

40

10

20

30

40

50

力信号の電圧範囲を複数のサブ範囲に分け、各サブ範囲の境界に対応する閾値レベルを有する複数の比較器を有するサブ A D C で、アナログ入力信号がいずれのサブ範囲に入るかを判定する。いずれの場合も、複数の比較器の閾値レベルは、等間隔である。もちろん、製造誤差により閾値レベルはばらつくが、少なくとも等間隔にすることを意図して作られている。

#### [0014]

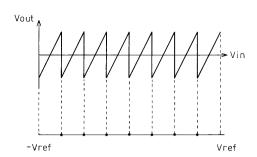

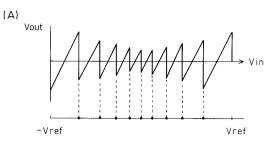

図3は、これまでのパイプライン・AD変換回路で、3ビットのAD変換を行う初段のパイプライン・ステージにおけるアナログ入力信号Vinと出力信号Vout、およびサブADCを構成する複数の比較器の閾値レベルを示す図である。図示のように、入力信号範囲はVrefから・Vrefであり、8個のサブ範囲に分けられる。各サブ範囲のアナログ入力信号Vinは、同じ出力範囲の出力信号Voutに変換されて出力される。サブADCの7個の比較器は、8個のサブ範囲の7個の境界に対応する閾値レベルを有する。8個のサブ範囲は同一の幅を有し、7個の閾値レベルは等間隔である。

#### 【先行技術文献】

#### 【非特許文献】

#### [ 0 0 1 5 ]

【非特許文献 1】Kunihiko Gotoh, Hiroshi Ando, Atsushi Iwata "A 10-b 30-MS/s3.4-mW Pipelined ADC with 2.0-Vpp Full-swing Input at a 1.0-V Supply" IEEE Asian Solid-State Circuits Conference November 3-5, 2008/Fukuoka, Japan

#### 【発明の概要】

【発明が解決しようとする課題】

#### [0016]

AD変換回路を使用する応用では、入力信号範囲の全範囲で同じ精度であることが必ずしも必要でない場合がある。例えば、AD変換値に基づいてフィードバック制御が行われ、広い入力信号範囲の信号を受け付ける必要であるが、フィードバック制御は、AD変換値が入力信号範囲の中心付近で所定の値になるように精密に制御する場合がある。このような場合、入力信号範囲の周辺(両端付近)の信号に対しては、中心付近に向かうようにフィードバック制御するので高精度のAD変換値を必要としないが、入力信号範囲の中心付近の信号に対しては精密な制御を行うために高精度のAD変換値が必要である。このような場合、これまでは、大きな入力範囲を有する低精度のAD変換回路と、中心付近に相当する狭い入力範囲を有する低精度のAD変換回路と、を組み合わせて、制御を行っていた。

#### [0017]

また、逆に入力信号範囲の周辺の信号に対して精密な制御を行うため高精度のAD変換値が必要であるが、中心付近の信号に対しては高精度のAD変換値を必要としない場合もある。このような場合、これまでは、大きな入力範囲を有する低精度のAD変換回路と、を組み合わせて、制御を行っていた。

#### [0018]

しかし、複数個のAD変換回路を使用するのは、スペースやコストの点で好ましくなく、このような要求を満たすAD変換値が得られるパイプライン・AD変換回路が望まれていた。

#### 【課題を解決するための手段】

# [0019]

本発明のパイプライン・AD変換回路は、初段のアナログ / デジタル変換ユニットのAD変換において、入力アナログ信号の入力範囲を少なくとも 4個以上のサブ範囲に分割して、入力アナログ信号がいずれのサブ範囲に入るかを判定し、この 4個以上のサブ範囲の大きさが異なることを特徴とする。

#### [0020]

すなわち、本発明のパイプライン・AD変換回路は、直列に接続された複数のアナログ

/ デジタル変換ユニットと、複数のアナログ / デジタル変換ユニットのサブ変換結果から、入力アナログ信号のデジタル変換値を算出するデジタル演算回路と、を備え、各アナログ / デジタル変換ユニットは、アナログ入力信号をサブ A D 値に変換するサブ A D 変換器と、前段から入力されるアナログ入力信号から、サブ A D 値に応じたアナログ減算信号を減算して残差信号を発生し、残差信号を増幅して出力する増幅 D A 変換器と、を備えるパイプライン・A D 変換回路であって、初段のアナログ / デジタル変換ユニットのサブ A D 変換器は、入力アナログ信号の入力範囲を少なくとも 4 個以上のサブ範囲に分割して、入力アナログ信号がいずれのサブ範囲に入るかを判定し、 4 個以上のサブ範囲の大きさが異なることを特徴とする。

#### [0021]

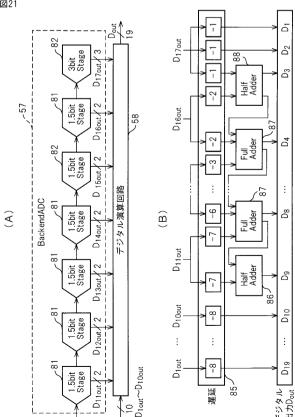

図4は、本発明のパイプライン・AD変換回路の初段のパイプライン・ステージ(アナログ/デジタル変換ユニット)におけるアナログ入力信号Vinと出力信号Vout、およびサブAD変換器を構成する複数の比較器の閾値レベルを示す図である。

#### [0022]

図4の(A)は、入力信号範囲Vrefから・Vrefの範囲を、中心付近が密で、周辺(両端付近)が疎である11のサブ範囲に分け、入力アナログ信号がいずれのサブ範囲に入るか判定してAD変換を行う。サブAD変換器を構成する10個の比較器(コンパレータ)は、サブ範囲の境界に対応する閾値をそれぞれ有する。

#### [0023]

初段のAD変換により判定されるサブ範囲が、図4の(A)に示すようなパイプライン・AD変換回路では、入力範囲の中心付近では出力Voutの範囲が小さく、増幅器の線形性が良好であるため、高精度のAD変換が可能である。これに対して、入力範囲の周辺では出力Voutの範囲が大きく、増幅器の線形性が劣化するため、AD変換の精度は中心付近に比べて劣化する。このように、初段のサブ範囲が図4の(A)であるようなパイプライン・AD変換回路は、大きな入力範囲を有し、入力範囲の中心付近では高精度のAD変換値が得られるので、上記のような入力信号範囲の周辺の信号に対しては高精度のAD変換値を必要としないが、入力信号範囲の中心付近の信号に対しては高精度のAD変換値が必要である応用に適している。

#### [0024]

初段のAD変換により判定されるサブ範囲は、図4の(A)に限らず各種の変形例が可能である。例えば、図4の(B)は、初段のAD変換により判定されるサブ範囲を、中心付近が疎で、周辺が密である11のサブ範囲に分けた例を示す。

#### [0025]

本発明を適用するには、初段のAD変換により判定されるサブ範囲を少なくとも4個以上にする必要がある。図4の(C)は、4個のサブ範囲で、中心の2個のサブ範囲A2およびA3と、周辺の2個のサブ範囲A1とA4の幅が異なる例を示す。

## 【発明の効果】

#### [0026]

本発明によれば、大きな入力範囲を有し、入力範囲内の所望の部分で高精度のAD変換値が得られるパイプライン・AD変換回路が実現される。

## 【図面の簡単な説明】

#### [0027]

【図1】図1は、初段で3ビットAD変換する12ビットのパイプライン・AD変換回路の構成を示す図である。

【図2】図2は、初段のパイプライン・ステージにおいて、増幅器の増幅率を、AD変換のビット数に対応した増幅率より小さくした場合のパイプライン・AD変換回路の構成を示す図である。

【図3】図3は、これまでのパイプライン・AD変換回路で、3ビットのAD変換を行う初段のパイプライン・ステージにおけるアナログ入力信号Vinと出力信号Vout、およびサブADCを構成する複数の比較器の閾値レベルを示す図である。

10

20

30

40

【図4】図4は、本発明のパイプライン・AD変換回路の初段のパイプライン・ステージ (アナログ / デジタル変換ユニット)におけるアナログ入力信号Vinと出力信号Vou t、およびサブAD変換器を構成する複数の比較器の閾値レベルを示す図である。

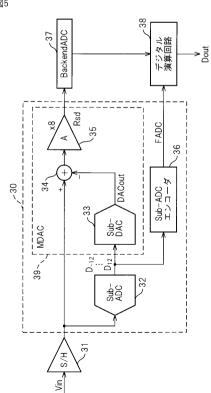

【図5】図5は、本発明の第1実施形態のパイプライン・AD変換回路の構成を示す図である。

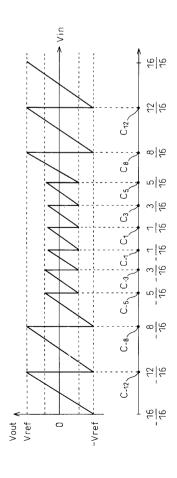

【図6】図6は、第1実施形態のパイプライン・AD変換回路の初段のアナログ/デジタル変換ユニットにおけるアナログ入力信号Vinと出力信号Vout、およびサブADCを構成する複数の比較器の閾値レベルを示す図である。

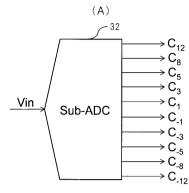

【図7】図7は、サブADCの表記と、変換特性を示す図であり、(A)が表記を、(B)が変換特性を示す。

【図8】図8は、サブADCを構成する10個の比較器と、それに供給する10個の閾値 レベルを発生する回路を示す図である。

【図9】図9は、サブADCエンコーダの表記と、エンコード特性を示す図であり、(A)が表記を、(B)がエンコード特性を示す。

【図 1 0 】図 1 0 は、サブ D A C (Sub-DAC)の表記と、変換特性を示す図であり、(A)が表記を、(B)が変換特性を示す。

【図11】図11は、MDACの構成を示す図である。

【 図 1 2 】 図 1 2 は、 M D A C のサンプルフェーズとホールドフェーズの状態を示す図である。

【図13】図13は、第1実施形態のパイプライン・AD変換回路において、アナログ入力信号Vinに対する各部の値、および範囲を示す図である。

【図14】図14は、第2実施形態のパイプライン・AD変換回路の構成を示す図である

【図15】図15は、第2実施形態におけるサブADCの構成、およびサブADCを構成する21個の比較器の閾値レベルを示す図である。

【図16】図16は、制御信号発生器で、6個のデジタル出力から制御信号を演算する演算式および制御信号の値を示す図である。

【図17】図17は、マルチプレクサ(MUX)の構成および制御信号に応じてDACに供給されるデジタル出力の組を示す。

【図18】図18は、MDACの構成を示す図である。

【図19】図19は、第2実施形態における、MDACのサンプルフェーズとホールドフェーズの状態を示す図である。

【図 2 0 】図 2 0 は、初段のアナログ / デジタル変換ユニットにおける動作を示すタイム チャートである。

【図21】図21は、後段のパイプライン・ステージ57とデジタル演算回路の構成を示す図であり、(A)がパイプライン・ステージを、(B)がデジタル演算回路の構成を示す。

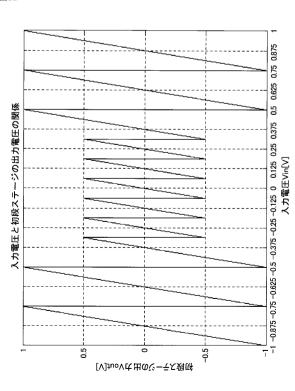

【図22】図22は、ランプ波形のアナログ信号を入力した時の初段のパイプライン・ステージの出力Voutの変化を示す図である。

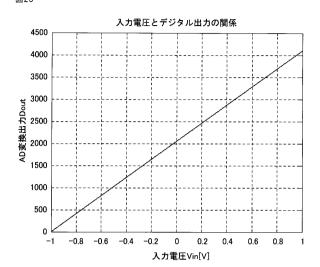

【図23】図23は、アナログ入力信号Vinに対するAD変換出力Doutの変化を示す図である。

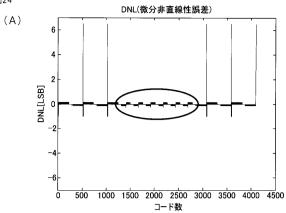

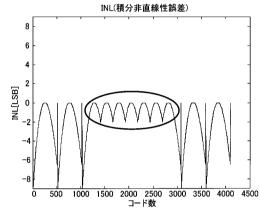

【図24】図24は、初段のアナログ/デジタル変換ユニットの増幅器の入出力特性に非線形誤差がある場合の誤差特性を示す図であり、(A)がDNL(微分非直線性誤差)を、、GB)がINL(積分非直線性誤差)を、示す。

【発明を実施するための形態】

[0028]

図 5 は、本発明の第 1 実施形態のパイプライン・A D 変換回路の構成を示す図である。 図 5 に示すように、第 1 実施形態のパイプライン・A D 変換回路は、初段のパイプライン・ステージを構成するアナログ / デジタル変換ユニット 3 0 と、アナログ入力信号 V i n のサンプルホールド回路 3 1 と、後段の A D C パイプライン・ステージ(backend ADC) 10

20

30

40

37と、デジタル演算回路38と、を有する。

#### [0029]

初段のアナログ / デジタル変換ユニット 3 0 は、サブ A D C (sub-ADC) 3 2 と、増幅 D A C (MDAC) 3 9 と、サブ A D C (sub-ADC) エンコーダ 3 6 と、を有する。 M D A C 3 9 は、一体に形成されたサプ D A C 3 3 と、減算器 3 4 と、増幅器(A) 3 5 と、を有し、増幅した残差信号を保持するサンプルホールド機能を有する。

#### [0030]

サンプルホールド回路 3 1 でサンプル & ホールドされたアナログ入力信号 V i n は、サブ A D C 3 2 および減算器 3 4 に入力される。増幅器 3 5 の出力は、後段の A D C パイプライン・ステージ 3 7 に入力される。

デジタル演算回路 3 8 は、初段のアナログ / デジタル変換ユニット 3 0 の S u b A D C エンコーダ 3 6 の出力する A D 変換値 F A D C および後段の A D C パイプライン・ステージ 3 7 の出力する 9 ビットの A D 変換値 B A D C から、 1 2 ビットの A D 変換出力 D o u t を生成する。

#### [0031]

図 6 は、第 1 実施形態のパイプライン・A D 変換回路の初段のアナログ / デジタル変換ユニット 3 0 におけるアナログ入力信号 V i n と出力信号 V o u t 、およびサブ A D C を構成する複数の比較器の閾値レベルを示す図である。図示のように、入力信号範囲は V r e f から - V r e f であり、 1 1 個のサブ範囲に分けられる。 1 1 個のサブ範囲は、入力信号範囲 V r e f から - V r e f を、 4 : 4 : 3 : 2 : 2 : 2 : 2 : 2 : 3 : 4 : 4 の比率で分割した範囲である。入力信号範囲 V r e f から - V r e f を 3 2 等分し、 V r e f を " 1 (=16/16) "に、 - V r e f を " - 1 (=-16/16) "に対応させると、 1 1 個のサブ範囲の 1 0 個の境界は、12/16,8/16,5/16,3/16,1/16,-1/16,-3/16,-5/16,-8/16,-12/16にそれぞれ対応し、これらがサブ A D C 3 2 を構成する比較器の閾値レベルに対応する。ここでは、これら 1 0 個の閾値レベルによる比較器の判定結果をサブ A D C 3 2 のデジタル出力 C  $_{12}$ 、 C  $_{8}$ 、 C  $_{5}$ 、 C  $_{3}$ 、 C  $_{1}$ 、 C  $_{-1}$ 、 C  $_{-3}$ 、 C  $_{-5}$ 、 C  $_{-8}$ 、 C  $_{-12}$  とする。

## [0032]

アナログ入力信号 Vinは、サブ範囲ごとに図 6 に示すように変換されて Voutとして出力される。したがって、サブ範囲により、出力 Voutの範囲が異なり、中心付近の5個のサブ範囲の出力範囲は Vref / 2 から - Vref / 2 と Vref / 2 から - Vref であり、周辺の 4 個のサブ範囲の出力範囲は Vref から - Vref である。

#### [0033]

図 7 は、サブADC32の表記と、変換特性を示す図であり、(A)が表記を、(B)が変換特性を示す。

図 7 の( A )に示すように、サブ A D C (Sub-ADC) 3 2 は、サンプルホールド回路 3 1 からのアナログ入力信号 V i n を受けて、デジタル出力 C  $_{12}$ 、 C  $_{8}$ 、 C  $_{5}$ 、 C  $_{3}$ 、 C  $_{1}$ 、 C  $_{12}$ を出力する。

## [0034]

入力信号範囲 V r e f および - V r e f をそれぞれ " 1 (=16/16) " および " - 1 (=-16/16) " に対応させると、アナログ入力信号 V i n がサブ範囲のいずれかに入るかに応じて、図 7 の(B)に示すデジタル出力 C  $_{12}$  、 C  $_{8}$  、 C  $_{5}$  、 C  $_{3}$  、 C  $_{1}$  、 C  $_{-1}$  、 C  $_{-3}$  、 C  $_{-5}$  、 C  $_{-8}$  、 C  $_{-12}$  が出力される。

# [0035]

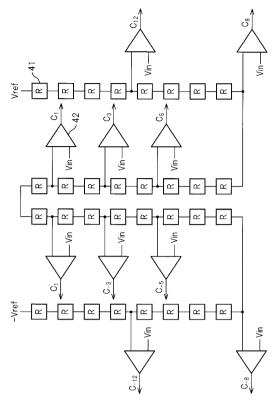

図8は、サブADC32を構成する10個の比較器42と、それに供給する10個の閾値レベルを発生する回路を示す図である。図8に示すように、アナログ入力信号の入力範囲に対応する参照電源Vrefと・Vrefの間に32個の同一抵抗値の抵抗41を直列に接続し、図示の接続ノードから閾値レベルに対応する電圧信号を取り出し、比較器42の一方の入力に供給する。比較器42の他方の入力には、アナログ入力信号Vinが供給される。

10

20

30

40

#### [0036]

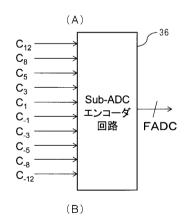

図9は、サブADCエンコーダ36の表記と、エンコード特性を示す図であり、(A)が表記を、(B)がエンコード特性を示す。

図 9 の( A )に示すように、サブ A D C エンコーダ 3 6 は、サブ A D C 3 2 からデジタル出力 C  $_{12}$ 、 C  $_{8}$ 、 C  $_{5}$ 、 C  $_{3}$ 、 C  $_{1}$ 、 C  $_{-3}$ 、 C  $_{-5}$ 、 C  $_{-8}$ 、 C  $_{-12}$ を受けて、デジタル出力 F A D C を出力する。

サブ A D C 3 2 のデジタル出力 C  $_{12}$ 、 C  $_8$ 、 C  $_5$ 、 C  $_3$ 、 C  $_1$ 、 C  $_{-1}$ 、 C  $_{-3}$ 、 C  $_{-5}$ 、 C  $_{-8}$ 、 C  $_{-12}$ に対して、図 9 の ( B ) に示すデジタル出力 F A D C が生成される。

## [0037]

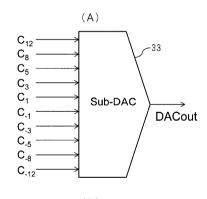

図 1 0 は、サブ D A C (Sub-DAC) 3 3 の表記と、変換特性を示す図であり、(A)が表記を、(B)が変換特性を示す。

図 1 0 の ( A ) に示すように、サブ D A C 3 3 は、サブ A D C 3 2 からデジタル出力 C  $_{12}$ 、 C  $_{8}$ 、 C  $_{5}$ 、 C  $_{3}$ 、 C  $_{1}$ 、 C  $_{-1}$ 、 C  $_{-3}$ 、 C  $_{-5}$ 、 C  $_{-8}$ 、 C  $_{-12}$ を受けて、 D A C  $_{7}$  アナログ出力 D A C o u t を出力する。

#### [0038]

サブADC32のデジタル出力  $C_{12}$ 、 $C_8$ 、 $C_5$ 、 $C_3$ 、 $C_1$ 、 $C_{-1}$ 、 $C_{-3}$ 、 $C_{-5}$ 、 $C_{-8}$ 、 $C_{-12}$ に対して、図9の(B)に示すDACアナログ出力DACoutが生成される。このDACアナログ出力DACoutは、アナログ入力信号が入ると判定されたサブ範囲の中心を、ゼロを中心するようにシフトする電圧に対応する。

#### [0039]

減算器 3 4 は、サンプルホールド回路 3 1 からのアナログ入力信号 V i n から、 D A C アナログ出力 D A C o u t を減算した信号を増幅器 3 5 に出力する。増幅器 3 5 は、入力信号を 8 倍(× 8)に増幅して出力信号 R s d を生成し、後段のパイプライン・ステージ 3 7 に出力する。

前述のように、第 1 実施形態では、サブDAC 3 3 と減算器 3 4 と増幅器 3 5 は、M DAC39として一体に形成される。

#### [0040]

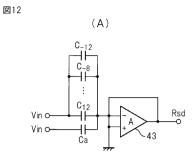

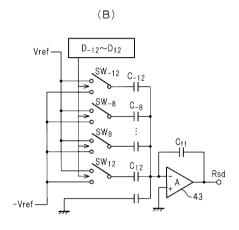

図 1 1 は、 M D A C 3 9 の構成を示す図である。

M D A C 3 9 は、非反転入力端子(+)がグランドに接続されたオペアンプ43を有する。オペアンプ43の反転入力端子(-)と非反転入力端子(+)は、スイッチSW  $_{34}$ で接続される。オペアンプ43の反転入力端子(-)と出力端子の間には、スイッチSW  $_{33}$ と演算容量 C  $_{11}$ が並列に接続される。さらに、オペアンプ43の反転入力端子(-)には、1 1 個の容量 C  $_{12}$ 、 C  $_8$ 、 C  $_5$ 、 C  $_3$ 、 C  $_1$ 、 C  $_{-1}$ 、 C  $_{-3}$ 、 C  $_{-5}$ 、 C  $_{-8}$ 、 C  $_{-12}$ 、 C aが接続される。ここで、1 0 個の容量はデジタル出力に対応するので、同じ符号を付して表す。容量 C  $_{12}$ 、 C  $_8$ 、 C  $_5$ 、 C  $_3$ 、 C  $_1$ 、 C  $_{-1}$ 、 C  $_{-5}$ 、 C  $_{-8}$ 、 C  $_{-12}$  の他方の端子は、それぞれスイッチS W  $_{12}$ 、 S W  $_8$ 、 S W  $_5$ 、 S W  $_3$ 、 S W  $_1$ 、 S W  $_{-1}$ 、 S W  $_3$ 、 S W  $_1$ 、 S W  $_{-1}$ 、 S W  $_3$ 、 S W  $_4$ 、 S W  $_5$  、 S W  $_5$  、 S W  $_5$  、 S W  $_5$  、 S W  $_5$  、 S W  $_5$  、 S W  $_5$  、 S W  $_5$  、 S W  $_5$  、 S W  $_5$  、 S W  $_5$  、 S W  $_5$  、 S W  $_5$  、 S W  $_5$  、 S W  $_5$  、 S W  $_5$  、 S W  $_5$  、 S W  $_5$  、 S W  $_5$  、 S W  $_5$  、 S W  $_5$  、 S W  $_5$  、 S W  $_5$  、 S W  $_5$  、 S W  $_5$  、 S W  $_5$  、 S W  $_5$  、 S W  $_5$  、 S W  $_5$  、 S W  $_5$  、 S W  $_5$  、 S W  $_5$  、 S W  $_5$  、 S W  $_5$  、 S W  $_5$  、 S W  $_5$  、 S W  $_5$  、 S W  $_5$  、 S W  $_5$  、 S W  $_5$  、 S W  $_5$  、 S W

#### [0041]

容量  $C_{12}$ 、  $C_{8}$ 、  $C_{5}$ 、  $C_{3}$ 、  $C_{1}$ 、  $C_{-1}$ 、  $C_{-3}$ 、  $C_{-5}$ 、  $C_{-8}$ 、  $C_{-12}$ 、  $C_{f-1}$  、  $C_{13}$  の容量値は、  $C_{12}$  は、  $C_{13}$  と  $C_{14}$  に  $C_{15}$  を  $C_{15}$  に  $C_{15}$  を  $C_{15}$  に  $C_{15}$  に

データ D  $_{12}$ 、 D  $_8$ 、 D  $_5$ 、 D  $_3$ 、 D  $_1$ 、 D  $_{-1}$ 、 D  $_{-3}$ 、 D  $_{-5}$ 、 D  $_{-8}$ 、 D  $_{-12}$ は、サブ A D C 3 2 のデジタル出力 C  $_{12}$ 、 C  $_8$ 、 C  $_5$ 、 C  $_3$ 、 C  $_1$ 、 C  $_{-1}$ 、 C  $_{-3}$ 、 C  $_{-5}$ 、 C  $_{-8}$ 、 C  $_{-12}$ に対応し、 C が " り " の時に D は " 1 " である。

#### [0042]

MDAC39は、アナログ入力信号Vinを取り込むサンプルフェーズと、残差信号を演算して増幅して出力する状態を維持するホールドフェーズと、を有する。

10

20

30

40

10

20

30

40

50

図 1 2 の ( A ) は、サンプルフェーズの M D A C 3 9 の状態を示す。サンプルフェーズでは、スイッチ S W  $_{31}$  はサンプルホールド回路 3 1 の V i n の信号線に接続され、スイッチ S W  $_{32}$  はサンプルホールド回路 3 1 の V i n の反転出力 - V i n の信号線に接続される。スイッチ S W  $_{33}$  および S W  $_{34}$  は、接続状態になる。スイッチ S W  $_{12}$  、S W  $_{8}$  、S W  $_{5}$  、S W  $_{3}$  、S W  $_{1}$  、S W  $_{11}$  、S W  $_{23}$  、S W  $_{25}$  、S W  $_{12}$  は、スイッチ S W  $_{31}$  に接続される信号線側に接続された状態になる。

#### [0043]

図 1 2 の( A )の状態で、オペアンプ 4 3 はリセットされた状態になり、容量 C  $_{12}$ 、 C  $_8$ 、 C  $_5$ 、 C  $_3$ 、 C  $_1$ 、 C  $_{-3}$ 、 C  $_{-5}$ 、 C  $_{-8}$ 、 C  $_{-12}$ 、 C a に V i n がサンプルされた状態になる。

#### [0044]

M D A C 3 9 は、オペアンプ 4 3 のゲインが無限大であると仮定すると、R s d = 8 ( V i n - ( 4 D  $_{12}$  + 4 D  $_8$  + 2 D  $_5$  + 2 D  $_3$  + 2 D  $_1$  + 2 D  $_{-1}$  + 2 D  $_{-3}$  + 2 D  $_{-5}$  + 4 D  $_{-8}$  + 4 D  $_{-12}$  ) × V r e f / 3 2 ) の式にしたがって出力 R s d を生成する。

実際には、オペアンプ43のゲインは無限大ではなく、オペアンプ43の入力依存であるから、Rsdは非線形性を有し、中心(ゼロ)から離れるにしたがって非線形性の誤差が大きくなる。第1実施形態では、高精度が要求されるアナログ入力信号の範囲については、非線形性の誤差が大きくなる周辺部は使用しないので、高精度を実現できる。

#### [0045]

図13は、第1実施形態のパイプライン・AD変換回路において、アナログ入力信号Vinに対する各部の値、および範囲を示す図である。アナログ入力信号Vinが、11個のサブ範囲のいずれかに入るかに応じて、サブADC(subADC)32の出力、サブDAC(subDAC)33の出力、増幅器の出力する残差信号Rsd、残差信号の出力範囲、および最終的なADC出力(AD変換値)が示されている。BADCは、後段のパイプライン・ステージ57の出力するAD変換値である。残差信号Rsdの出力範囲は、図6に示される値に対応する。

#### [0046]

例えば、Vinが10/16×Vrefの場合、AD変換値は2048×10/16= 1280である。第1実施形態では、Vinがこのレベルである場合、FADC=10で 、BADC=0であるから、Dout=10×128=1280となり、正しい変換が行 える。

#### [0047]

同様に、Vinが2.5/16×Vrefの場合、AD変換値は2048×2.5/16=320である。第1実施形態では、Vinがこのレベルである場合、FADC=2で、BADC=64であるから、Dout=2×128+64=320となり、正しい変換が行える。

#### [0048]

さらに、Vinが15/16×Vrefの場合、AD変換値は2048×15/16=1920である。第1実施形態では、Vinがこのレベルである場合、FADC=14で、BADC=128であるから、Dout=14×128+128=1920となり、正しい変換が行える。

#### [0049]

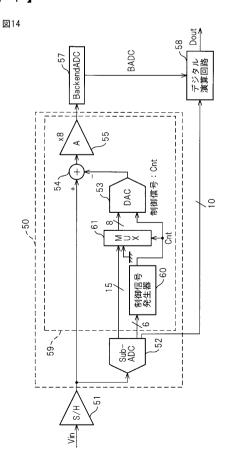

図 1 4 は、第 2 実施形態のパイプライン・A D 変換回路の構成を示す図である。 図 1 4 に示すように、第 2 実施形態のパイプライン・A D 変換回路は、初段のパイプラ イン・ステージを構成するアナログ / デジタル変換ユニット 5 0 と、アナログ入力信号 V i n のサンプルホールド回路 5 1 と、後段の A D C パイプライン・ステージ (backend ADC) 5 7 と、デジタル演算回路 5 8 と、を有する。

#### [0050]

初段のアナログ / デジタル変換ユニット 5 0 は、サブ A D C (sub-ADC) 5 2 と、増幅 D A C (MDAC) 5 9 と、を有する。初段の A D 変換値 F A D C は、サブ A D C 5 2 の発生するデジタル出力をしようするので、サブ A D C エンコーダは設けない。 M D A C 5 9 は、制御信号発生器 6 0 と、マルチプレクサ(M U X ) 6 1 と、 D A C 5 3 と、減算器 5 4 と、増幅器 (A) 5 5 と、を有する。 D A C 5 3 、減算器 5 4 および増幅器 5 5 は、一体に形成され、増幅した残差信号を保持するサンプルホールド機能を有する。

[0051]

サンプルホールド回路 5 1 でサンプル & ホールドされたアナログ入力信号 V i n は、サブ A D C 5 2 および減算器 5 4 に入力される。増幅器 5 5 の出力は、後段の A D C パイプライン・ステージ 5 7 に入力される。

#### [0052]

デジタル演算回路 5 8 は、初段のアナログ / デジタル変換ユニット 5 0 の出力する A D 変換値 F A D C および後段の A D C パイプライン・ステージ 5 7 の出力する A D 変換値 B A D C から、 1 2 ビットの A D 変換出力 D o u t を生成する。

#### [0053]

第 2 実施形態のパイプライン・A D 変換回路の初段のアナログ / デジタル変換ユニット 5 0 は、図 6 に示した第 1 実施形態と同様に、 1 1 個のサブ範囲を有し、入力信号範囲 V r e f から - V r e f を、 4 : 4 : 3 : 2 : 2 : 2 : 2 : 2 : 3 : 4 : 4 の比率で分割する。

[0054]

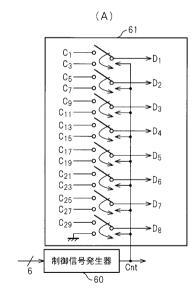

図 1 5 の ( A ) は、第 2 実施形態におけるサブ A D C 5 2 の構成を示す図であり、図 1 5 の ( B ) は、サブ A D C 5 2 を構成する 2 1 個の比較器 7 1 の閾値レベルを示す図である。

#### [0055]

図15の(A)に示すように、サブADC52は、21個の比較器71と、参照電源Vrefと・Vrefの間に直列に接続した同一抵抗値の32個の抵抗72と、を有する。そして、抵抗72同士の31個の接続ノードに、・Vref側から順に、0から30の番号をつけ、0、2、4、6、8、22、24、26、28、30以外の接続ノードから閾値レベルに対応する21個の電圧信号を取り出し、比較器71の一方の入力に供給する。比較器71の他方の入力には、アナログ入力信号Vinが供給される。21個の比較器71の比較器71の比較器71の比較器71の比較器71の比較器71の比較器71の比較器71の比較器71の比較器71の比較器71の比較品里が、デジタル出力C $_1$ 、С $_3$ 、С $_5$ 、…、С $_2$ 7、С $_2$ 9は、図15の(B)に示すように、比較の閾値レベルも表すものとする。入力信号範囲Vrefから・Vrefを32等分し、Vrefを"1(=16/16)"に、・Vrefを"・1(=-16/16)"に対応させると、21個の比較器71の閾値レベルС $_1$ 、С $_3$ 、С $_5$ 、…、С $_2$ 7、С $_2$ 9は、-14/16、-12/16、-10/16、-8/16、-6/16、-5/16、-4/16、-3/16、-2/16、-1/16、0、1/16、3/16、4/16、5/16、6/16、8/16、10/16、12/16、14/16である。

[0056]

言い換えると、サブADC52は、0番目から30番目の31個の比較器を有する5ビットのサブADCにおいて、0、2、4、6、8、22、24、26、28、30番目の比較器を除いた構成を有するものである。

## [0057]

アナログ / デジタル変換ユニット 5 0 の A D 変換値 F A D C は、  $D_{1out} \sim D_{10out}$ で構成され、  $D_{1out}$ は  $C_{27}$ を、  $D_{2out}$ は  $C_{23}$ を、  $D_{3out}$ は  $C_{20}$ を、  $D_{4out}$ は  $C_{18}$ を、  $D_{5out}$ は  $C_{16}$ を、  $D_{6out}$ は  $C_{14}$ を、  $D_{7out}$ は  $C_{12}$ を、  $D_{8out}$ は  $C_{10}$ を、  $D_{9out}$ は  $C_{7}$ を、  $D_{10out}$ は  $C_{3}$ を、それぞれ使用する。

10

20

30

10

20

30

40

50

#### [0058]

制御信号発生器 6 0 は、デジタル出力のうちの 6 個の出力  $C_{20}$ 、  $C_{18}$ 、  $C_{16}$ 、  $C_{14}$ 、  $C_{12}$ 、  $C_{10}$ を受けて、図 1 6 の ( A ) の演算式にしたがって、制御信号  $C_{n-t}$  を演算する。したがって、制御信号発生器 6 0 は、 A N D、 N O T および O R を含む論理回路で実現できる。デジタル出力  $C_{20}$ 、  $C_{18}$ 、  $C_{16}$ 、  $C_{14}$ 、  $C_{12}$ 、  $C_{10}$ に対する制御信号  $C_{nt}$  の値を、図 1 6 の ( B ) に示す。

#### [0059]

図17の(A)は、マルチプレクサ(MUX)61の構成を示す図である。図17の(A)に示すように、MUX61は、デジタル出力  $C_1$ 、 $C_5$ 、 $C_9$ 、 $C_{13}$ 、 $C_{17}$ 、 $C_{21}$ 、 $C_2$  5 および  $C_{29}$  の第1組と、 $C_3$ 、 $C_7$ 、 $C_{11}$ 、 $C_{15}$ 、 $C_{19}$ 、 $C_{23}$ 、 $C_{27}$  および "0"の第2組を受け、制御信号  $C_{nt}$  が "1"の時には第1の組を、"0"の時には第2の組を選択してデータ  $D_1$  ~  $D_8$  として出力する。

#### [0060]

したがって、制御信号  $C_{nt}$ が" 1 "の時には、図 1 7 の( B )に示すように、 D A C 5 3 には第 1 の組のデジタル出力  $C_1$ 、  $C_5$ 、  $C_9$ 、  $C_{13}$ 、  $C_{17}$ 、  $C_{21}$ 、  $C_{25}$ および  $C_{29}$ が入力される。制御信号  $C_{nt}$ が" 0 "の時には、図 1 7 の( C )に示すように、 D A C 5 3 には第 2 の組のデジタル出力  $C_3$ 、  $C_7$ 、  $C_{11}$ 、  $C_{15}$ 、  $C_{19}$ 、  $C_{23}$ 、  $C_{27}$ および" 0 "が入力される。

#### [0061]

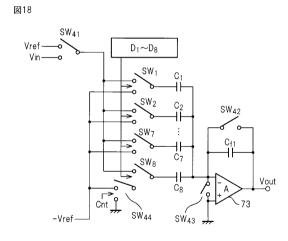

前述のように、第 2 実施形態では、 D A C 5 3 と減算器 5 4 と増幅器 5 5 は、 M D A C 5 9 として一体に形成される。

図 1 8 は、M D A C 5 9 の構成を示す図である。

MDAC59は、非反転入力端子(+)がグランドに接続されたオペアンプ73を有する。オペアンプ73の反転入力端子(-)と非反転入力端子(+)は、スイッチSW $_{43}$ で接続される。オペアンプ43の反転入力端子(-)と出力端子の間には、スイッチSW $_{42}$ と演算容量  $C_{11}$ が並列に接続される。さらに、オペアンプ43の反転入力端子(-)には、8個の容量  $C_{11}$  ~  $C_{11}$  のでをかける。容量  $C_{11}$  ~  $C_{11}$  での他方の端子は、それぞれスイッチSW $_{11}$  ~  $C_{11}$  を介してVref たはVinに接続される。スイッチSW $_{11}$  ~  $C_{11}$  を介してVref たはVinに接続される信号線と、・Vref に接続される信号線の一方に接続するように切り換えられる。また、スイッチSW $_{11}$  を介してVref またはVinに接続される信号線と、スイッチSW $_{11}$  を介してVref または Vinに接続される信号線と、スイッチSW $_{11}$  を介してVref に接続するように切り換えられる。さらに、スイッチSW $_{11}$  ないっと「接続する場合と開放(遮断) になる場合に切り換えられる。スイッチSW $_{11}$  、  $C_{11}$  により制御される。

# [0062]

容量 C<sub>1</sub> ~ C<sub>8</sub> および C<sub>f1</sub> の容量値は、同一である。

MDAC59は、アナログ入力信号Vinを取り込むサンプルフェーズと、残差信号を演算して増幅して出力する状態を維持するホールドフェーズと、を有する。

#### [0063]

図 1 9 の( A )は、サンプルフェーズの M D A C 5 9 の状態を示す。サンプルフェーズでは、スイッチ S W  $_{41}$ はサンプルホールド回路 3 1 の V i n の信号線に接続され、スイッチ S W  $_{42}$ および S W  $_{43}$ は、接続状態になる。スイッチ S W  $_1$  ~ S W  $_8$ は、スイッチ S W  $_{41}$ に接続される信号線側に接続された状態になる。

図 1 9 の ( A ) の状態で、オペアンプ 7 3 はリセットされた状態になり、容量 C  $_1$  ~ C  $_8$  に V i n がサンプルされた状態になる。

## [0064]

図 1 9 の ( B ) は、ホールドフェーズの M D A C 5 9 の状態を示す。ホールドフェーズでは、スイッチ S W  $_{42}$  は、 R 放 ( 遮断 ) 状態になる。スイッチ S W  $_1$  ~ S W  $_8$  および S W  $_{44}$  は、データ D  $_1$  ~ D  $_8$  および制御信号 C  $_{nt}$  に応じて接続が制御される。具体的には、スイッチ S W  $_1$  ~ S W  $_7$  は、データ D  $_1$  ~ D  $_7$

が " 1 " であれば V r e f l c c d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d e d

[0065]

M D A C 5 9 の出力 V o u t は、オペアンプ 4 3 のゲインが無限大であると仮定すると、次の式で表される。

[0066]

【数1】

10

$$V_{out} = \frac{\sum_{i=1}^{8} C_{i}}{C_{f1}} \left( Vin - \frac{D'_{1}C_{1} + \dots + D'_{7}C_{7} + D'_{8}C_{8}}{\sum_{i=1}^{8} C_{i}} Vref \right) \frac{1}{1 + \frac{1}{A} \left( 1 + \frac{\sum_{i=1}^{8} C_{i}}{C_{f1}} \right)}$$

$$=8\left(\operatorname{Vin}-\frac{D'_{1}+\cdots+D'_{7}+D'_{8}}{8}\operatorname{Vref}\right)$$

$$A=\infty, C_{1}=C_{2}=\cdots=C_{8}=C_{1,1} \text{ O } \succeq 3$$

$$D_1 \sim D_7 = 1$$

のとき  $D'_{1 \sim 7} = 1$   $D_1 \sim D_7 = 0$ のとき  $D'_{1 \sim 7} = -1$

30

#### [0067]

ここで、 $D_1 \sim D_7$ が" 1 "の時に、 $D_{11} \sim D_{12}$ は" 1 "であり、 $D_1 \sim D_7$ が" 0 "の時に、 $D_{11} \sim D_{12}$ が" 0 "の時に、 $D_{13} \sim D_{13}$ が" 1 "の時に、 $D_{13} \sim D_{13}$ が" 0 "で且つ $D_{11} \sim D_{13} \sim D_{13}$ が" 0 "で且つ $D_{11} \sim D_{13} \sim$

[0068]

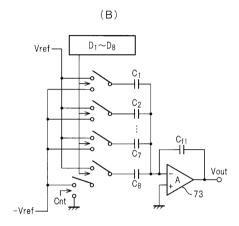

図 2 0 は、初段のアナログ / デジタル変換ユニット 5 0 における動作を示すタイムチャートである。

[0069]

中段に示すように、制御信号  $C_{nt}$  は、中心付近の 3 つの期間 " 1 " になり、それ以外の期間は " 0 " である。制御信号  $C_{nt}$  が " 1 " である期間においては第 2 組のデジタル出力が選択され、制御信号  $C_{nt}$  が " 0 " である期間においては第 2 組のデジタル出力が選択される。

そのため、出力信号Voutは、下段に示すような信号となる。これは、図6に示した

50

題1実施形態の出力信号Rsdと同じである。

#### [0070]

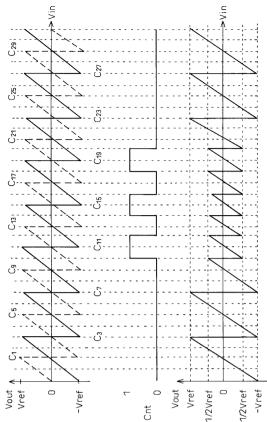

図 2 1 は、後段のパイプライン・ステージ 5 7 とデジタル演算回路 5 8 の構成を示す図であり、(A)がパイプライン・ステージ 5 7 を、(B)がデジタル演算回路 5 8 の構成を示す。

図 2 1 の ( A ) に示すように、後段のパイプライン・ステージ 5 7 は、直列に接続された 6 個の 1 . 5 ビットのパイプライン・ステージ (1.5bit Stage) 8 1 と 1 個の 3 ビットパイプライン・ステージ (3bit Stage) 8 2 を有する。 1 . 5 ビットのパイプライン・ステージ 8 1 および 3 ビットパイプライン・ステージ 8 2 は、通常使用されるものを使用でき、その構成は広く知られているので、説明は省略する。

[0071]

図 2 1 の(A)に示すように、 1 . 5 ビットのパイプライン・ステージ 8 1 は、それぞれ 2 本のデータ線で、変換結果  $D_{11out}$ 、  $D_{12out}$ 、  $D_{13out}$ 、  $D_{14out}$ 、  $D_{15out}$ 、  $D_{16out}$  を出力する。 3 ビットパイプライン・ステージ 8 2 は、 3 本のデータ線で、変換結果  $D_{17out}$  を出力する。また、前述のように、初段のアナログ / デジタル変換ユニット 5 0 は、 1 0 本のデータ線で、変換結果  $D_{1out}$  ~  $D_{10out}$  を出力する。デジタル演算回路 5 8 は、これらの出力を受けて、デジタル出力  $D_{19}$  ~  $D_{1}$  を含む出力  $D_{10}$  0 U 1 を生成する。

[0072]

図 2 1 の ( B ) に示すように、デジタル演算回路 5 8 は、遅延回路 8 5 と、半加算器 (Half Adder) 8 6 と、5 個の全加算器 (Full Adder) 8 7 と、半加算器 (Half Adder) 8 8 と、を有する。遅延回路 8 5 は、 $D_{1out} \sim D_{10out}$ を8 クロック分遅延させ、 $D_{11out} \sim D_{16out}$ を、それぞれ 7 ~ 2 クロック分遅延させ、 $D_{17out}$ を 1 クロック分遅延させる。

デジタル出力 D <sub>19</sub> ~ D <sub>10</sub> は変換結果 D <sub>10ut</sub> ~ D <sub>10out</sub> であり、デジタル出力 D <sub>2</sub> ~ D <sub>1</sub>は 変換結果 D <sub>17out</sub> の下位 2 ビットである。

[0073]

変換結果  $D_{17out}$ の最上位ビットと  $D_{16out}$  は、半加算器 8 8 で加算され、その結果がデジタル出力  $D_3$ になる。 5 個の全加算器 8 7 は、対応する変換結果  $D_{12out}$ 、  $D_{13out}$ 、  $D_{14out}$ 、  $D_{15out}$ 、  $D_{16out}$ のうちの 2 つと、下位の全加算器 8 7 または半加算器 8 8 のキャリィと、を加算する。 5 個の全加算器 8 7 の演算結果が、  $D_8$   $\sim$   $D_4$  になる。さらに、半加算器 8 6 は、  $D_{11out}$  に下位の全加算器 8 7 のキャリィを加算する。半加算器 8 6 の演算結果が、  $D_9$  になる。以上のようにして、デジタル出力  $D_{19}$   $\sim$   $D_1$  がえられる。

[0074]

デジタル演算回路 5 8 は、上記のデジタル出力  $D_{19} \sim D_1$ から 1 0 進数の A D 変換結果である D o u t を次の式にしたがって演算する。

D o u t =  $D_{19} \times 5$  1 2 +  $D_{18} \times 5$  1 2 +  $D_{17} \times 2$  5 6 + ... +  $D_{12} \times 2$  5 6 +  $D_{11} \times 5$  1 2 +  $D_{10} \times 5$  1 2 +  $D_{9} \times 2$  5 6 +  $D_{8} \times 1$  2 8 +  $D_{7} \times 6$  4 +  $D_{6} \times 3$  2 +  $D_{5} \times 1$  6 +  $D_{4} \times 8$  +  $D_{3} \times 4$  +  $D_{2} \times 2$  +  $D_{1} \times 1$

[0075]

第2実施形態のパイプライン・AD変換回路のMATLAB(登録商標)によるシミュレーションを行った。シミュレーションは、・VrefからVref(・1V~+1V)に変化するランプ波形のアナログ信号Vinを入力し、33.6MHzのサンプリング周波数でサンプリングを行った。

[0076]

図 2 2 は、上記のアナログ信号を入力した時の初段のパイプライン・ステージの出力 Voutの変化を示す図である。図示のように、図 2 0 に示した変化と同じように変化する出力 Voutが得られる。

[0077]

図23は、アナログ入力信号Vinに対するAD変換出力Doutの変化を示す図である。これにより、12ビットのAD変換結果が得られることが分かる。

図24は、初段のアナログ/デジタル変換ユニット50の増幅器55の入出力特性が、

10

20

30

40

入力をx、出力をyとした時に、y = 8 x + 2 x  $^2$  - 2 x  $^3$  で表されるとして、A D 変換値の各値における誤差を示す図であり、(A) が D N L (微分非直線性誤差)を、(B) が I N L (積分非直線性誤差)を、示す。これから、初段のアナログ / デジタル変換ユニット 5 0 の出力範囲が狭い、図 2 4 の (A) および (B) において円で囲った部分の誤差が、他の部分より小さいことが分かる。

#### 【産業上の利用可能性】

## [ 0 0 7 8 ]

本発明は、パイプライン・AD変換回路に適用される。

#### 【符号の説明】

## [ 0 0 7 9 ]

- 3 1 サンプルホールド回路

- 3 2 サブAD変換器

- 3 3 サブDC変換器

- 3 4 減算器

- 3 5 増幅器

- 36 サブADCエンコーダ

- 37 後段のパイプライン・ステージ

- 3 8 デジタル演算回路

# 【図1】

図1

図2

# 【図3】

図 3

# 【図4】

図4

Vout

Vout

Vref

Vref

Vref

-Vref Vref Vref A1 A2 A3 A4

# 【図5】

図5

# 【図6】

図6

# 【図7】

|                   |                  | (               | B)              |                 |                 |                |       |       |                |                 |

|-------------------|------------------|-----------------|-----------------|-----------------|-----------------|----------------|-------|-------|----------------|-----------------|

| アナログ入力            |                  |                 |                 | デ               | ジタ              | ル出             | 出力    |       |                |                 |

| Vin               | C <sub>-12</sub> | C <sub>-8</sub> | C <sub>-5</sub> | C <sub>-3</sub> | C <sub>-1</sub> | C <sub>1</sub> | $C_3$ | $C_5$ | C <sub>8</sub> | C <sub>12</sub> |

| (-16/16)-(-12/16) | 0                | 0               | 0               | 0               | 0               | 0              | 0     | 0     | 0              | 0               |

| (-12/16)-(-8/16)  | 1                | 0               | 0               | 0               | 0               | 0              | 0     | 0     | 0              | 0               |

| (-8/16)-(-5/16)   | 1                | 1               | 0               | 0               | 0               | 0              | 0     | 0     | 0              | 0               |

| (-5/16)-(-3/16)   | 1                | 1               | 1               | 0               | 0               | 0              | 0     | 0     | 0              | 0               |

| (-3/16)-(-1/16)   | 1                | 1               | 1               | 1               | 0               | 0              | 0     | 0     | 0              | 0               |

| (-1/16)-(1/16)    | 1                | 1               | 1               | 1               | 1               | 0              | 0     | 0     | 0              | 0               |

| (1/16)-(3/16)     | 1                | 1               | 1               | 1               | 1               | 1              | 0     | 0     | 0              | 0               |

| (3/16)-(5/16)     | 1                | 1               | 1               | 1               | 1               | 1              | 1     | 0     | 0              | 0               |

| (5/16)-(8/16)     | 1                | 1               | 1               | 1               | 1               | 1              | 1     | 1     | 0              | 0               |

| (8/16)-(12/16)    | 1                | 1               | 1               | 1               | 1               | 1              | 1     | 1     | 1              | 0               |

| (12/16)-(16/16)   | 1                | 1               | 1               | 1               | 1               | 1              | 1     | 1     | 1              | 1               |

# 【図8】

図8

# 【図9】

図9

|   |                                                                                                                                                                        |                                                |                                           |                                           |                                           |                                           | (Β.                                            | ,                                    |                                           |                                      |                                                           |

|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|-------------------------------------------|-------------------------------------------|-------------------------------------------|-------------------------------------------|------------------------------------------------|--------------------------------------|-------------------------------------------|--------------------------------------|-----------------------------------------------------------|

|   | デジタル入力<br>C <sub>-12</sub> C <sub>-8</sub> C <sub>-5</sub> C <sub>-3</sub> C <sub>-1</sub> C <sub>1</sub> C <sub>3</sub> C <sub>5</sub> C <sub>8</sub> C <sub>12</sub> |                                                |                                           |                                           |                                           |                                           |                                                |                                      |                                           |                                      | デジタル出力<br>FADC                                            |

|   | C <sub>-12</sub>                                                                                                                                                       | C <sub>-8</sub>                                | C <sub>-5</sub>                           | C <sub>-3</sub>                           | U <sub>-1</sub>                           | C <sub>1</sub>                            | $C_3$                                          | $C_5$                                | C <sub>8</sub>                            | C <sub>12</sub>                      | 1 ADO                                                     |

| • | 0<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1                                                                                                                              | 0<br>0<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1 | 0<br>0<br>0<br>1<br>1<br>1<br>1<br>1<br>1 | 0<br>0<br>0<br>0<br>1<br>1<br>1<br>1<br>1 | 0<br>0<br>0<br>0<br>0<br>1<br>1<br>1<br>1 | 0<br>0<br>0<br>0<br>0<br>1<br>1<br>1<br>1 | 0<br>0<br>0<br>0<br>0<br>0<br>0<br>1<br>1<br>1 | 0<br>0<br>0<br>0<br>0<br>0<br>0<br>0 | 0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0 | 0<br>0<br>0<br>0<br>0<br>0<br>0<br>0 | -14<br>-10<br>- 7<br>- 4<br>- 2<br>0<br>2<br>4<br>7<br>10 |

|   |                                                                                                                                                                        |                                                |                                           |                                           |                                           |                                           |                                                |                                      |                                           |                                      |                                                           |

# 【図10】

図10

| - ( |   | ١ |

|-----|---|---|

| - / | L | 1 |

|     |   |   |

|    | C <sub>-12</sub> | C <sub>-8</sub> |   | AC <del>5</del><br>C <sub>-3</sub> |   |   |   | C <sub>5</sub> | C <sub>8</sub> | C <sub>12</sub> | DAC<br>アナログ<br>出力<br>DACout |

|----|------------------|-----------------|---|------------------------------------|---|---|---|----------------|----------------|-----------------|-----------------------------|

| 0  | 0                | 0               | 0 | 0                                  | 0 | 0 | 0 | 0              | 0              | 0               | -14.0/16                    |

| 1  | 1                | 0               | 0 | 0                                  | 0 | 0 | 0 | 0              | 0              | 0               | -10.0/16                    |

| 2  | 1                | 1               | 0 | 0                                  | 0 | 0 | 0 | 0              | 0              | 0               | - 7.0/16                    |

| 3  | 1                | 1               | 1 | 0                                  | 0 | 0 | 0 | 0              | 0              | 0               | - 4.0/16                    |

| 4  | 1                | 1               | 1 | 1                                  | 0 | 0 | 0 | 0              | 0              | 0               | - 2.0/16                    |

| 5  | 1                | 1               | 1 | 1                                  | 1 | 0 | 0 | 0              | 0              | 0               | 0.0/16                      |

| 6  | 1                | 1               | 1 | 1                                  | 1 | 1 | 0 | 0              | 0              | 0               | 2.0/16                      |

| 7  | 1                | 1               | 1 | 1                                  | 1 | 1 | 1 | 0              | 0              | 0               | 4.0/16                      |

| 8  | 1                | 1               | 1 | 1                                  | 1 | 1 | 1 | 1              | 0              | 0               | 7.0/16                      |

| 9  | 1                | 1               | 1 | 1                                  | 1 | 1 | 1 | 1              | 1              | 0               | 10.0/16                     |

| 10 | 1                | 1               | 1 | 1                                  | 1 | 1 | 1 | 1              | 1              | 1               | 14.0/16                     |

# 【図11】

#

# 【図12】

# 【図13】

図13

| ADC出力<br>Dout      | 14*128+BADC     | 10*128+BADC    | 7*128+BADC    | 4*128+BADC      | 2*128+BADC      | BADC            | -2*128+BADC     | -4*128+BADC     | -7*128+BADC     | -10*128+BADC     | -14*128+BADC         |

|--------------------|-----------------|----------------|---------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|------------------|----------------------|

| 残差信号<br>出力範囲       | (-1.0)-(1.0)    | (-1.0)-(1.0)   | (-0.5)-(1.0)  | (-0.5)- $(0.5)$ | (-0.5)- $(0.5)$ | (-0.5)- $(0.5)$ | (-0.5)- $(0.5)$ | (-0.5)- $(0.5)$ | (-1.0)- $(0.5)$ | (-1.0)-(1.0)     | (-1.0)-(1.0)         |

| 残差信号<br>Rsd        | Vin*8-14.0      | Vin*8-10.0     | Vin*8-6.0     | Vin*8-4.0       | Vin*8-2.0       | Vin*8           | $Vin^*8+2.0$    | Vin*8+4.0       | Vin*8+6.0       | Vin*8+10.0       | Vin*8+14.0           |

| sub-DAC<br>出力      | 14.0/16         | 10.0/16        | 6.0/16        | 4.0/16          | 2.0/16          | 0.0/16          | -2.0/16         | -4.0/16         | -6.0/16         | -10.0/16         | -14.0/16             |

| sub-ADC<br>エンコーダ出力 | 14              | 10             | 9             | 4               | 2               | 0               | -2              | -4              | 9-              | -10              | -14                  |

| アナログ入力<br>Vin      | (12/16)-(16/16) | (8/16)-(12/16) | (5/16)-(8/16) | (3/16)-(5/16)   | (1/16)-(3/16)   | (-1/16)-(1/16)  | (-3/16)-(-1/16) | (-5/16)-(-3/16) | (-8/16)-(-5/16) | (-12/16)-(-8/16) | (-16/16)- $(-12/16)$ |

# 【図14】

# 【図15】

図15

# 【図16】

図16

(A) 制御信号Cnt= $\overline{C_{20}}\cdot C_{18}+\overline{C_{16}}\cdot C_{14}+\overline{C_{12}}\cdot C_{10}$

(B)

| C <sub>20</sub> | C <sub>18</sub> | C <sub>16</sub> | C <sub>14</sub> | C <sub>12</sub> | C <sub>10</sub> | 制御信号Cnt |

|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|---------|

| 0               | 0               | 0               | 0               | 0               | 0               | 0       |

| 0               | 0               | 0               | 0               | 0               | 0               | 0       |

|                 |                 |                 |                 |                 |                 | ÷       |

| 0               | 0               | 0               | 0               | 0               | 0               | 0       |

| 0               | 0               | 0               | 0               | 0               | 1               | 1       |

| 0               | 0               | 0               | 0               | 1               | 1               | 0       |

| 0               | 0               | 0               | 1               | 1               | 1               | 1       |

| 0               | 0               | 1               | 1               | 1               | 1               | 0       |

| 0               | 1               | 1               | 1               | 1               | 1               | 1       |

| 1               | 1               | 1               | 1               | 1               | 1               | 0       |

|                 |                 |                 |                 |                 |                 | E       |

| 1               | 1               | 1               | 1               | 1               | 1               | 0       |

# 【図17】

3

図17

#

# 【図18】

# 【図19】

図19

【図20】

図 20

# 【図21】

図21

# 【図22】

図22

# 【図23】

図23

# 【図24】

図24

(B)

# フロントページの続き

(72)発明者 丹 陽平 群馬県桐生市天神町 1 - 5 - 1

(72)発明者 小林 春夫 群馬県桐生市相生町 2 - 6 2 0 - 1 2 相生住宅 1 - 2 0 2 F ターム(参考) 5J022 AA15 BA01 CB02 CB06 CC02 CD03 CF01 CF02