#### (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2013-13166 (P2013-13166A)

(43) 公開日 平成25年1月17日(2013.1.17)

(51) Int.Cl. HO2M 7/12 (2006.01) F I HO2M 7/12 HO2M 7/12

S A テーマコード (参考) 5HOO6

審査請求 未請求 請求項の数 7 OL (全 12 頁)

(21) 出願番号 特願2011-142438 (P2011-142438) (22) 出願日 平成23年6月28日 (2011.6.28) (71) 出願人 000004606

ニチコン株式会社

京都府京都市中京区烏丸通御池上る二条殿

町551番地

(71) 出願人 504145364

国立大学法人群馬大学

群馬県前橋市荒牧町四丁目2番地

(74)代理人 110000475

特許業務法人みのり特許事務所

(72)発明者 ▲けい▼ 林

群馬県桐生市天神町一丁目5番1号 国立

大学法人群馬大学内

(72) 発明者 高 虹

群馬県桐生市天神町一丁目5番1号 国立

大学法人群馬大学内

最終頁に続く

## (54) 【発明の名称】 AC/DC変換装置

## (57)【要約】

【課題】従来のものよりも効率に優れ、任意の正の出力電圧を出力可能なAC/DC変換装置を提供する。

【解決手段】AC/DC変換装置1Aは、第1入力端6aと第1出力端7aとの間に、入力側から出力側にかけて順にSW1、コイルLおよびSW2が直列に接続され、SW3の一端がSW1とコイルLとの接続部位に接続され、SW3の他端が第2入力端6bおよび第2出力端7bに接続され、SW4の他端が第2入力端6bおよび第2出力端7bに接続され、SW4の他端が第2入力端6bおよび第2出力端7bに接続され、コンデンサCoがSW2の出力側であって、第1出力端7aと第2出力端7bとの間に接続され、SW5の他端が第1出力端7aに接続される。

【選択図】図1

#### 【特許請求の範囲】

#### 【請求項1】

第1入力端および第2入力端からなる入力端子対に入力される交流入力電圧を所望の目標電圧値を有する直流出力電圧に変換して第1出力端および第2出力端からなる出力端子対から出力させるAC/DC変換装置において、

コイル、コンデンサおよび第1ないし第5スイッチング素子を有するチョッパ部と、 前記交流入力電圧の電圧値を検知する入力電圧検知部と、

前記直流出力電圧の電圧値を検知する出力電圧検知部と、

前記入力電圧検知部および前記出力電圧検知部が検知した電圧値に基づいて、前記直流出力電圧の電圧値が前記目標電圧値となるように前記チョッパ部の前記第1ないし前記第5のスイッチング素子をオン/オフ制御する制御部とを備え、

前記第1入力端と前記第1出力端との間に、入力側から出力側にかけて順に前記第1スイッチング素子、前記コイルおよび前記第2スイッチング素子が直列に接続され、

前記第3スイッチング素子の一端が前記第1スイッチング素子と前記コイルとの接続部位に接続され、前記第3スイッチング素子の他端が前記第2入力端および前記第2出力端に接続され、

前記第4スイッチング素子の一端が前記コイルと前記第2スイッチング素子との接続部位に接続され、前記第4スイッチング素子の他端が前記第2入力端および前記第2出力端に接続され、

前記コンデンサが前記第2スイッチング素子の出力側であって、前記第1出力端と前記第2出力端との間に接続され、

前記第5スイッチング素子の一端が前記第1スイッチング素子と前記コイルとの接続部位に接続され、前記第5スイッチング素子の他端が前記第1出力端に接続され、

前記制御部は、前記第1ないし前記第5スイッチング素子をオン/オフ制御して、前記チョッパ部に昇圧チョッパ動作、降圧チョッパ動作、昇降圧チョッパ動作および反転昇降圧チョッパ動作のいずれかを選択的に実行させることで、前記交流入力電圧を前記目標電圧値を有する直流出力電圧に変換することを特徴とするAC/DC変換装置。

#### 【請求項2】

前記制御部は、

前記交流入力電圧の電圧値が正であり、かつ前記目標電圧値よりも低い場合は、前記チョッパ部に昇圧チョッパ動作を行わせ、

前記交流入力電圧の電圧値が正であり、かつ前記目標電圧値よりも高い場合は、前記チョッパ部に降圧チョッパ動作を行わせ、

前記交流入力電圧の電圧値が負の場合は、前記チョッパ部に反転昇降圧チョッパ動作を行わせることを特徴とする請求項1に記載のAC/DC変換装置。

## 【請求項3】

前記昇圧チョッパ動作においては、前記第1スイッチング素子がオン状態、前記第3および第5スイッチング素子がオフ状態とされ、かつ前記第2スイッチング素子と前記第4スイッチング素子とが交互にオン/オフ制御され、

前記降圧チョッパ動作においては、前記第2スイッチング素子がオン状態、前記第4および第5スイッチング素子がオフ状態とされ、かつ前記第1スイッチング素子と前記第3スイッチング素子とが交互にオン/オフ制御され、

前記反転昇降圧チョッパ動作においては、前記第4スイッチング素子がオン状態、前記第2および第3スイッチング素子がオフ状態とされ、かつ前記第1スイッチング素子と前記第5スイッチング素子とが交互にオン/オフ制御されることを特徴とする請求項2に記載のAC/DC変換装置。

## 【請求項4】

前記交流入力電圧の入力が開始されてから所定の時間が経過するまでの間および/または前記直流出力電圧の電圧値が所定の電圧値に到達するまでの間、前記制御部は、前記昇

10

20

30

40

圧チョッパ動作における前記第2スイッチング素子のオン時間を短くする、および/または前記第1スイッチング素子のオフ時間を長くすることにより、デューティを低く設定することを特徴とする請求項2または3に記載のAC/DC変換装置。

#### 【請求項5】

前記制御部は、

前記交流入力電圧の電圧値が正の場合は、前記チョッパ部に昇降圧チョッパ動作を行わせ、

前記交流入力電圧の電圧値が負の場合は、前記チョッパ部に反転昇降圧チョッパ動作を行わせることを特徴とする請求項1に記載のAC/DC変換装置。

#### 【請求項6】

前記昇降圧チョッパ動作においては、前記第5スイッチング素子がオフ状態とされ、かつ前記第1および第4スイッチング素子と、前記第2および第3スイッチング素子とが交互にオン/オフ制御され、

前記反転昇降圧チョッパ動作においては、前記第4スイッチング素子がオン状態、前記第2および第3スイッチング素子がオフ状態とされ、かつ前記第1スイッチング素子と前記第5スイッチング素子とが交互にオン/オフ制御されることを特徴とする請求項5に記載のAC/DC変換装置。

#### 【請求項7】

前記交流入力電圧の入力が開始されてから所定の時間が経過するまでの間および/または前記直流出力電圧の電圧値が所定の電圧値に到達するまでの間、前記制御部は、前記昇降圧チョッパ動作における第1および第4スイッチング素子のオン時間を短くすることにより、デューティを低く設定することを特徴とする請求項5または6に記載のAC/DC変換装置。

【発明の詳細な説明】

#### 【技術分野】

## [0001]

本発明は、交流入力電圧を所望の目標電圧値を有する直流出力電圧に変換するAC/DC変換装置に関する。

#### 【背景技術】

## [0002]

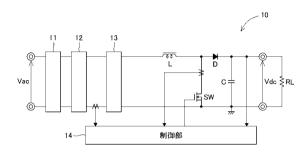

従来のAC/DC変換装置として、例えば非特許文献1には図7に示すAC/DC変換装置10が開示されている。同図に示すように、AC/DC変換装置10は、交流入力電圧Vacを所望の目標電圧値を有する直流出力電圧Vdcに変換するものであって、ノイズフィルタ11と、突入防止回路12と、ダイオードブリッジ回路13と、スイッチング素子SW等からなるチョッパ回路と、直流出力電圧Vdcの電圧値および各部の電流値に基づいてスイッチング素子SWを制御する制御部14とを備えている。

## [0003]

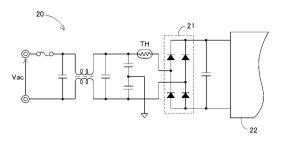

また、従来の別のAC/DC変換装置として、例えば非特許文献2には図8に示すAC/DC変換装置20が開示されている。同図に示すように、AC/DC変換装置20は、ノイズを除去するためのフィルタ回路の後段に突入防止回路として機能するパワーサーミスタTHと、ダイオードブリッジ回路21とを備えている。AC/DC変換装置20は、ダイオードブリッジ回路21により整流された後の直流電圧がチョッパ回路22に入力される点が図7に示すAC/DC変換装置10と共通している。

【先行技術文献】

# 【非特許文献】

## [0004]

【非特許文献1】山崎浩、「アクティブフィルタの特徴と開発・応用現状」、電子技術、日刊工業新聞社、平成2年3月発行、第32巻、第3号、p.76(図9)

【 非 特 許 文 献 2 】 杉 本 雅 俊 、 城 山 博 伸 、 「 昇 圧 コ ン バ ー タ に よ る 力 率 改 善 回 路 の 設 計 」 、 電 源 回 路 設 計 2 0 0 9 、 C Q 出 版 社 、 平 成 2 1 年 5 月 発 行 、 p . 1 8 4 ( 図 3 3 ) 10

20

30

40

10

20

30

40

50

#### 【発明の概要】

【発明が解決しようとする課題】

#### [0005]

しかしながら、上記AC/DC変換装置10、20は、突入防止回路12、THとダイオードブリッジ回路13、21に常に入力電流が流れるため、出力電力が増加して入力電流が増加すると、それに応じて上記回路において発生する損失が増加し、効率が悪化するという問題があった。また、上記AC/DC変換装置10、20は、直流出力電圧Vdcの電圧値を交流入力電圧Vacの電圧値よりも低くできないという問題があった。

## [0006]

本発明は上記事情に鑑みてなされたものであって、その課題とするところは、従来のものよりも効率に優れ、任意の正の出力電圧を出力可能なAC/DC変換装置を提供することにある。

#### 【課題を解決するための手段】

## [0007]

上記課題を解決するために、本発明に係るAC/DC変換装置は、

第 1 入 力 端 お よ び 第 2 入 力 端 か ら な る 入 力 端 子 対 に 入 力 さ れ る 交 流 入 力 電 圧 を 所 望 の 目 標 電 圧 値 を 有 す る 直 流 出 力 電 圧 に 変 換 し て 第 1 出 力 端 お よ び 第 2 出 力 端 か ら な る 出 力 端 子 対から出力させるAC/DC変換装置において、コイル、コンデンサおよび第1ないし第 5 スイッチング素子を有するチョッパ部と、交流入力電圧の電圧値を検知する入力電圧検 知部と、直流出力電圧の電圧値を検知する出力電圧検知部と、入力電圧検知部および出力 電圧検知部が検知した電圧値に基づいて、直流出力電圧の電圧値が目標電圧値となるよう にチョッパ部の第 1 ないし第 5 のスイッチング素子をオン / オフ制御する制御部とを備え 、第1入力端と第1出力端との間に、入力側から出力側にかけて順に第1スイッチング素 子、 コイルおよび第 2 スイッチング素子が直列に接続され、第 3 スイッチング素子の一端 が 第 1 ス イ ッ チ ン グ 素 子 と コ イ ル と の 接 続 部 位 に 接 続 さ れ 、 第 3 ス イ ッ チ ン グ 素 子 の 他 端 が第2入力端および第2出力端に接続され、第4スイッチング素子の一端がコイルと第2 ス イ ッ チ ン グ 素 子 と の 接 続 部 位 に 接 続 さ れ 、 第 4 ス イ ッ チ ン グ 素 子 の 他 端 が 第 2 入 力 端 お よび第2出力端に接続され、コンデンサが第2スイッチング素子の出力側であって、第1 出力端と第2出力端との間に接続され、第5スイッチング素子の一端が第1スイッチング 素 子 と コ イ ル と の 接 続 部 位 に 接 続 さ れ 、 第 5 ス イ ッ チ ン グ 素 子 の 他 端 が 第 1 出 力 端 に 接 続 され、制御部は、第1ないし第5スイッチング素子をオン/オフ制御して、チョッパ部に 昇 圧 チ ョ ッ パ 動 作 、 降 圧 チ ョ ッ パ 動 作 、 昇 降 圧 チ ョ ッ パ 動 作 お よ び 反 転 昇 降 圧 チ ョ ッ パ 動 作のいずれかを選択的に実行させることで、交流入力電圧を目標電圧値を有する直流出力 電圧に変換することを特徴としている。

## [ 0 0 0 8 ]

この構成によれば、交流入力電圧の電圧値に基づいて制御されるチョッパ部が昇圧チョッパ動作、降圧チョッパ動作、昇降圧チョッパ動作および反転昇降圧チョッパ動作のいずれかを選択的に実行することで、各チョッパ動作により交流入力電圧を直接スイッチングするので、ダイオードブリッジ回路を不要とすることができ、該回路による損失の発生を防ぐことができる。また、この構成によれば、交流入力電圧よりも高い電圧値を有する直流出力電圧だけでなく、交流入力電圧よりも低い電圧値を有する直流出力電圧も出力することができる。

#### [0009]

上記発明に係るAC/DC変換装置の第1態様として、制御部は、交流入力電圧の電圧値が正であり、かつ目標電圧値よりも低い場合は、チョッパ部に昇圧チョッパ動作を行わせ、交流入力電圧の電圧値が正であり、かつ目標電圧値よりも高い場合は、チョッパ部に反転昇降圧チョッパ動作を行わせ、交流入力電圧の電圧値が負の場合は、チョッパ部に反転昇降圧チョッパ動作を行わせることを特徴とする。

### [0010]

より具体的には、昇圧チョッパ動作においては、第1スイッチング素子がオン状態、第

3 および第 5 スイッチング素子がオフ状態とされ、かつ第 2 スイッチング素子と第 4 スイッチング素子とが交互にオン / オフ制御され、降圧チョッパ動作においては、第 2 スイッチング素子がオン状態、第 4 および第 5 スイッチング素子がオフ状態とされ、かつ第 1 スイッチング素子と第 3 スイッチング素子とが交互にオン / オフ制御され、反転昇降圧チョッパ動作においては、第 4 スイッチング素子がオン状態、第 2 および第 3 スイッチング素子がオフ状態とされ、かつ第 1 スイッチング素子と第 5 スイッチング素子とが交互にオン / オフ制御される。

#### [0011]

第1態様に係るAC/DC変換装置の制御は、交流入力電圧の入力が開始されてから所定の時間が経過するまでの間および/または直流出力電圧の電圧値が所定の電圧値に到達するまでの間、制御部は、昇圧チョッパ動作における第2スイッチング素子のオン時間を短くする、および/または第1スイッチング素子のオフ時間を長くすることにより、デューティを低く設定することが好ましい。

[0012]

この構成によれば、いずれかのスイッチング素子のデューティを変えるだけでソフトスタート機能を実現することができるので、突入防止回路を不要とすることができ、該回路による損失の発生を防ぐことができる。

[0013]

また、上記課題を解決するために、本発明に係るAC/DC変換装置の第2態様として、制御部は、交流入力電圧の電圧値が正の場合は、チョッパ部に昇降圧チョッパ動作を行わせ、交流入力電圧の電圧値が負の場合は、チョッパ部に反転昇降圧チョッパ動作を行わせることを特徴とする。

[0014]

より具体的には、昇降圧チョッパ動作においては、第5スイッチング素子がオフ状態とされ、かつ第1および第4スイッチング素子と、第2および第3スイッチング素子とが交互にオン/オフ制御され、反転昇降圧チョッパ動作においては、第4スイッチング素子がオン状態、第2および第3スイッチング素子がオフ状態とされ、かつ第1スイッチング素子と第5スイッチング素子とが交互にオン/オフ制御される。

[0015]

第2態様に係るAC/DC変換装置の制御は、交流入力電圧の入力が開始されてから所定の時間が経過するまでの間および/または直流出力電圧の電圧値が所定の電圧値に到達するまでの間、制御部は、昇降圧チョッパ動作における第1および第4スイッチング素子のオン時間を短くすることにより、デューティを低く設定することが好ましい。

[0016]

この構成によれば、昇降圧チョッパ動作における第1および第4スイッチング素子のデューティを変えるだけでソフトスタート機能を実現することができるので、突入防止回路を不要とすることができ、該回路による損失の発生を防ぐことができる。

【発明の効果】

[0017]

本発明によれば、ダイオードブリッジ回路および突入防止回路を省略することができるので、該回路における損失の発生を防ぎ、従来のものよりも効率に優れ、任意の正の出力電圧を出力可能なAC/DC変換装置を提供することができる。

【図面の簡単な説明】

[0018]

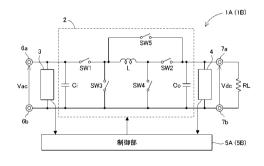

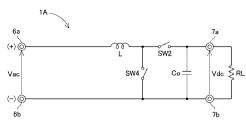

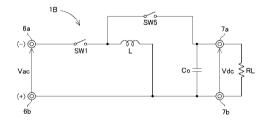

【図1】本発明に係るAC/DC変換装置の概略構成図である。

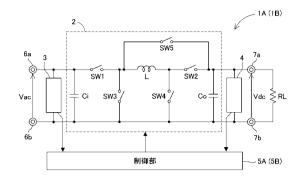

【図2】交流入力電圧の電圧値と第1実施形態における3つのチョッパ動作との対応関係を示す図である。

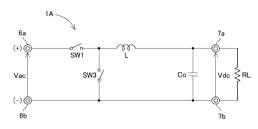

【図3】第1実施形態に係るAC/DC変換装置の等価回路図であって、(A)は昇圧チョッパ動作時、(B)は降圧チョッパ動作時、(C)は反転昇降圧チョッパ動作時の等価回路図である。

10

20

30

40

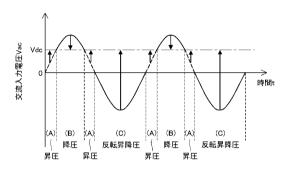

【図4】交流入力電圧の電圧値と第2実施形態における2つのチョッパ動作との対応関係を示す図である。

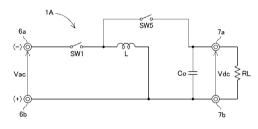

- 【図5】第2実施形態に係るAC/DC変換装置の等価回路図であって、(A)は昇降圧チョッパ動作時、(B)は反転昇降圧チョッパ動作時の等価回路図である。

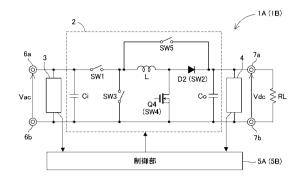

- 【図6】図1の第2および第4スイッチング素子を実際の半導体素子に置き換えた場合の 構成図である。

- 【図7】従来のAC/DC変換装置の概略構成図である。

- 【図8】従来のAC/DC変換装置の概略構成図である。

- 【発明を実施するための形態】

- [0019]

以下、添付図面を参照して、本発明に係るAC/DC変換装置の好ましい実施形態について説明する。

[0020]

[第1実施形態]

図1は、本発明の第1実施形態に係るAC/DC変換装置1Aの概略構成図である。同図に示すように、AC/DC変換装置1Aは、対をなす第1入力端6aおよび第2入力端6bから入力された交流入力電圧Vacを所望の目標電圧値を有する直流出力電圧Vdcに変換し、該直流出力電圧Vdcを対をなす第1出力端7aおよび第2出力端7bから負荷RLに出力するものであって、複数のスイッチング素子SW1~SW5を有するチョッパ部2と、交流入力電圧Vacの電圧値を検知する入力電圧検知部3と、直流出力電圧Vdcの電圧値を検知する出力電圧検知部4と、入力電圧検知部3および出力電圧検知部4が検知した電圧値に基づいて、直流出力電圧Vdcの電圧値が目標電圧値となるようにチョッパ部2を制御する制御部5Aを備えている。

[0021]

チョッパ部2は、第1入力端6aに一端が接続された第1スイッチング素子SW1と、第1スイッチング素子SW1の他端にそれぞれ一端が接続された第3スイッチング素子SW3、第5スイッチング素子SW5およびコイルLと、コイルLの他端にそれぞれ一端が接続された第2スイッチング素子SW2および第4スイッチング素子SW4と、第2スイッチング素子SW2の他端に一端が接続されたコンデンサCoとを有する。また、第3スイッチング素子SW3、第4スイッチング素子SW4およびコンデンサCoの他端はそれぞれ第2入力端6bおよび第2出力端7bに接続され、第2スイッチング素子SW2および第5スイッチング素子SW5の他端はそれぞれ第1出力端7aに接続されている。各スイッチング素子SW1~5は、制御部5AによりON/OFF制御される。

[0022]

なお、チョッパ部 2 は、第 1 入力端 6 a および第 2 入力端 6 b に接続されたコンデンサ C i も備えているが、該コンデンサ C i はコンデンサ C o に比べて容量が非常に小さく、チョッパ部 2 の動作にはほとんど影響を与えないので、以下では、説明を簡単化するためにコンデンサ C i を無視する。

[0023]

図2に示すように、本発明では、交流入力電圧Vacの電圧値に応じて制御部5Aが各スイッチング素子SW1~SW5の制御を変更する。言い換えると、本発明では、交流入力電圧Vacの電圧値に応じてチョッパ部2のチョッパ動作が変更される。

[0024]

具体的には、本実施形態に係るAC/DC変換装置1Aのチョッパ部2は、(1)交流入力電圧Vacの電圧値(第2入力端6bを基準とした場合の第1入力端6aの電位)が正であり、かつ目標電圧値Vt(負荷RLに出力すべき直流出力電圧Vdcの電圧値)よりも低い場合は昇圧チョッパ動作を行い、(2)交流入力電圧Vacの電圧値が正であり、かつ目標電圧値Vtよりも高い場合は降圧チョッパ動作を行い、(3)交流入力電圧Vacの電圧値が負の場合は反転昇降圧チョッパ動作を行う。これらの動作により、直流出力電圧Vdcの電圧値は、目標電圧値Vtに維持(安定化)される。

10

20

30

40

#### [ 0 0 2 5 ]

チョッパ部2の3つのチョッパ動作のうち、まず、昇圧チョッパ動作について説明する。本動作においては、第1スイッチング素子SW1が常にON状態、第3スイッチング素子SW3および第5スイッチング素子SW5が常にOFF状態とされる。したがって、本動作中のAC/DC変換装置1Aは、図3(A)に示す簡素な等価回路で表現される。

#### [0026]

また、本動作においては、第4スイッチング素子SW4と整流ダイオードの役割を果たす第2スイッチング素子SW2とが交互にON/OFF制御される。すなわち、第4スイッチング素子SW4がON状態からOFF状態に切り替わると、同期的に第2スイッチング素子SW2がOFF状態からON状態に切り替わる。1スイッチング周期Tにおける第4スイッチング素子SW4のON時間をTon4とすると、第4スイッチング素子SW4のデューティ (=Ton4/T)は次式で求めることができる。

デューティ = 1 - Vacの電圧値 / Vdcの電圧値

#### [0027]

降圧チョッパ動作においては、第2スイッチング素子SW2が常にON状態、第4スイッチング素子SW4および第5スイッチング素子SW5が常にOFF状態とされる。したがって、本動作中のAC/DC変換装置1Aは、図3(B)に示す簡素な等価回路で表現される。

## [0028]

また、本動作においては、第1スイッチング素子SW1と整流ダイオードの役割を果たす第3スイッチング素子SW3とが交互にON/OFF制御される。すなわち、第1スイッチング素子SW1がON状態からOFF状態に切り替わると、同期的に第3スイッチング素子SW3がOFF状態からON状態に切り替わる。1スイッチング周期Tにおける第1スイッチング素子SW1のON時間をTon1とすると、第1スイッチング素子SW1のデューティ (=Ton1/T)は次式で求めることができる。

デューティ = V d c の電圧値 / V a c の電圧値

## [0029]

反転昇降圧チョッパ動作においては、第4スイッチング素子SW4が常にON状態、第 2スイッチング素子SW2および第3スイッチング素子SW3が常にOFF状態とされる 。したがって、本動作中のAC/DC変換装置1Aは、図3(C)に示す簡素な等価回路 で表現される。

## [0030]

また、本動作においては、第1スイッチング素子SW1と整流ダイオードの役割を果たす第5スイッチング素子SW5とが交互にON/OFF制御される。すなわち、第1スイッチング素子SW1がON状態からOFF状態に切り替わると、同期的に第5スイッチング素子SW5がOFF状態からON状態に切り替わる。1スイッチング周期Tにおける第1スイッチング素子SW1のON時間をTon1とすると、第1スイッチング素子SW1のデューティ (=Ton1/T)は次式で求めることができる。ただし、交流入力電圧Vacの電圧値は負である。

デューティ = V d c の電圧値 / ( V d c の電圧値 - V a c の電圧値 )

## [0031]

以上のように、本実施形態に係るAC/DC変換装置1Aでは、制御部5Aがチョッパ部2のチョッパ動作を(1)昇圧チョッパ動作、(2)降圧チョッパ動作、および(3)反転昇降圧チョッパ動作に切り替える。また、各チョッパ動作においては、チョッパ部2が交流入力電圧Vacを直接スイッチングする。したがって、本実施形態に係るAC/DC変換装置1Aによれば、ダイオードブリッジ回路(図7の符号13、図8の符号21)を不要とすることができるので、該回路による損失の発生を防ぐことができ、効率を改善

10

20

30

40

することができる。

### [0032]

## 「第2実施形態]

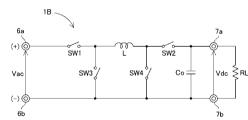

続いて、本発明の第2実施形態に係るAC/DC変換装置1Bについて説明する。図1に示すように、本実施形態に係るAC/DC変換装置1Bは、制御部5Bを備えている以外の点において第1実施形態に係るAC/DC変換装置1Aと何ら変わりがない。このため、回路構成についての詳細な説明は省略する。

#### [0033]

図4に示すように、本実施形態においても、交流入力電圧Vacの電圧値に応じて制御部5Bが各スイッチング素子SW1~SW5のON/OFF制御を変更する。言い換えると、交流入力電圧Vacの電圧値に応じてチョッパ部2のチョッパ動作が変更される。

[0034]

具体的には、本実施形態に係るAC/DC変換装置1Bのチョッパ部2は、(1)交流入力電圧Vacの電圧値が正である場合は昇降圧チョッパ動作を行い、(2)交流入力電圧Vacの電圧値が負の場合は反転昇降圧チョッパ動作を行う。これにより、直流出力電圧Vdcの電圧値は、目標電圧値Vtに維持(安定化)される。

[0035]

昇降圧チョッパ動作においては、第5スイッチング素子SW5が常にOFF状態とされる。したがって、本動作中のAC/DC変換装置1Bは、図5(A)に示す簡素な等価回路で表現される。

[0036]

また、本動作においては、第1および第4スイッチング素子SW1、SW4と、整流ダイオードの役割を果たす第2および第3スイッチング素子SW2、SW3とが交互にON/OFF制御される。すなわち、第1および第4スイッチング素子SW1、SW4がON状態からOFF状態に切り替わると、同期的に第2および第3スイッチング素子SW2、SW3がOFF状態からON状態に切り替わる。1スイッチング周期Tにおける第1および第4スイッチング素子SW1、SW4のON時間をTon14とすると、第1および第4スイッチング素子SW1、SW4のデューティ (=Ton14/T)は次式で求めることができる。

デューティ = V d c の電圧値 / ( V d c の電圧値 + V a c の電圧値 )

## [0037]

反転昇降圧チョッパ動作においては、第1実施形態の反転昇降圧チョッパ動作と同様の制御が行われる。すなわち、第4スイッチング素子SW4が常にON状態、第2スイッチング素子SW2および第3スイッチング素子SW3が常にOFF状態とされ、かつ第1スイッチング素子SW1と整流ダイオードの役割を果たす第5スイッチング素子SW5とが交互にON/OFF制御される(図5(B)参照)。

[0038]

以上のように、本実施形態に係るAC/DC変換装置1Bでは、制御部5Bがチョッパ部2のチョッパ動作を(1)昇降圧チョッパ動作、および(2)反転昇降圧チョッパ動作に切り替える。また、各チョッパ動作においては、チョッパ部2が交流入力電圧Vacを直接スイッチングする。したがって、本実施形態に係るAC/DC変換装置1Bによれば、ダイオードブリッジ回路を不要とすることができるので、該回路による損失の発生を防ぐことができ、効率を改善することができる。

[0039]

さらに、模式的に示したスイッチング素子を実際の半導体素子に置き換えた例を図6に示す。同図では、第2スイッチング素子SW2をダイオードD2に、第4スイッチング素子SW4をnチャネルMOSFETのQ4に置換している。図6に示す回路によれば、ダイオードD2のアノードとFETQ4のドレインをコイル側に接続することにより、第1実施形態および第2実施形態の全動作を効率的に実施することができる。

10

20

30

50

#### [0040]

なお、本発明に係るAC/DC変換装置は上記構成に限定されるものではなく、種々の変形例が考えられる。

#### [0041]

例えば、効率をさらに改善するためには、交流入力電圧Vacの入力が開始されてから 所定の時間が経過するまでの間および/または直流出力電圧Vdcの電圧値が所定の電圧 値(例えば、Vtの約95%)に到達するまでの間、各チョッパ動作におけるデューティ を通常時とは異なったデューティとすることが好ましい。これによれば、突入防止回路( 図7の符号12、図8の符号TH)がなくても突入電流の量を制限することができるので 、該回路による損失の発生を防ぐことができる。

[0042]

より詳しくは、第1実施形態の昇圧チョッパ動作においては、第2スイッチング素子SW2がON状態のときに第1入力端6a コイルL 第2スイッチング素子SW2 コンデンサCoの経路で突入電流が流れるので、通常時よりも第2スイッチング素子SW2のON時間を短くすることで、突入電流の量を制限することができる。また、第1スイッチング素子SW1がOFFしている状態を長くして、第1実施形態の昇圧チョッパ動作が実質的に行われないようにすることでも突入電流の量を制限することができる。すなわち、直流出力電圧Vdcの電圧値を緩やかに上昇(ソフトスタート)させることにより、突入電流の量を制限することができる。同様に、第1実施形態の降圧チョッパ動作においては、通常時よりもデューティ (=Ton1/T)を低めに設定し、第1スイッチング素子SW1のON時間を短くすればよい。

[ 0 0 4 3 ]

また、第1実施形態および第2実施形態の反転昇降圧チョッパ動作においては、第1スイッチング素子SW1がOFF状態に切り替えられたときにコイルLに蓄積されたエネルギーが第5スイッチング素子SW5を通じてコンデンサCoに供給される。したがって、通常時よりもデューティ (=Ton1/T)を低めに設定して第1スイッチング素子SW1のON時間を短くし、コイルLに蓄積されるエネルギーを減らすことで、突入電流の量を制限することができる。同様に、第2実施形態の昇降圧チョッパ動作においては、通常時よりもデューティ (=Ton14/T)を低めに設定して第1および第4スイッチング素子SW1、SW4のON時間を短くし、コイルLに蓄積されるエネルギーを減らすことで、突入電流の量を制限することができる。

[0044]

また、別の変形例として、入力電流検出回路を設けることにより、制御部 5 A 、 5 B は、力率改善および高調波対策のために、入力電流波形を正弦波に近づけるような各スイッチング素子 S W 1 ~ S W 5 の制御を追加的に行ってもよい。

【符号の説明】

[0045]

1 A 、 1 B A C / D C 変換装置

2 チョッパ部

3 入力電圧検知部

4 出力電圧検知部

5 A 、 5 B 制御部

10

20

30

# 【図1】

## 【図2】

# 【図4】

# 【図3】

## (A) 昇圧

## (B) 降圧

## (C) 反転昇降圧

# 【図5】

## (A) 昇降圧

# (B) 反転昇降圧

【図6】

【図8】

【図7】

## フロントページの続き

(72)発明者 小堀 康功

群馬県桐生市天神町一丁目5番1号 国立大学法人群馬大学内

(72)発明者 小林 春夫

群馬県桐生市天神町一丁目5番1号 国立大学法人群馬大学内

(72)発明者 岡本 直久

京都府京都市中京区烏丸通御池上る二条殿町551番地 ニチコン株式会社内

(72)発明者 大島 正樹

京都府京都市中京区烏丸通御池上る二条殿町551番地 ニチコン株式会社内

F ターム(参考) 5H006 CA01 CB09 CC02 DA04 DB01 DC05