# (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2013-143857 (P2013-143857A)

(43) 公開日 平成25年7月22日(2013.7.22)

(51) Int.Cl.

FΙ

テーマコード (参考)

HO2M 7/12 (2006.01)

HO2M 7/12

F

5H006

審査請求 未請求 請求項の数 6 OL (全 12 頁)

|                    |                                                    | _        |                                                        |

|--------------------|----------------------------------------------------|----------|--------------------------------------------------------|

| (21) 出願番号 (22) 出願日 | 特願2012-3261 (P2012-3261)<br>平成24年1月11日 (2012.1.11) | (71) 出願人 | 000004606<br>ニチコン株式会社<br>京都府京都市中京区烏丸通御池上る二条殿<br>町551番地 |

|                    |                                                    | (71)出願人  | 504145364                                              |

|                    |                                                    |          | 国立大学法人群馬大学                                             |

|                    |                                                    |          | 群馬県前橋市荒牧町四丁目2番地                                        |

|                    |                                                    | (74)代理人  | 110000475                                              |

|                    |                                                    |          | 特許業務法人みのり特許事務所                                         |

|                    |                                                    | (72) 発明者 | ▲けい▼ 林                                                 |

|                    |                                                    |          | 群馬県桐生市天神町一丁目5番1号 国立                                    |

|                    |                                                    |          | 大学法人群馬大学内                                              |

|                    |                                                    | (72) 発明者 | 高虹                                                     |

|                    |                                                    |          | 群馬県桐生市天神町一丁目5番1号 国立                                    |

|                    |                                                    |          | 大学法人群馬大学内                                              |

|                    |                                                    |          | 最終百に続く                                                 |

# (54) 【発明の名称】AC/DC変換装置

# (57)【要約】

【課題】従来のものよりも効率に優れ、かつ、簡単な構成で安定化された直流出力電圧を得ることができるAC/DC変換装置を提供することができる。

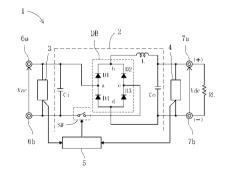

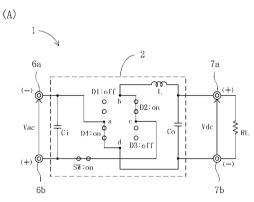

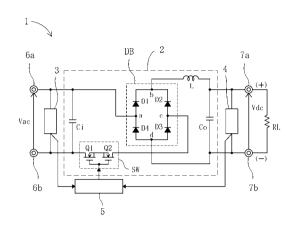

【解決手段】チョッパ部2と、入力電圧検知部3と、出力電圧検知部4と、制御部5とが備えられ、第1入力端6aと第2入力端6bの間にダイオードブリッジDBとスイッチング素子SWが直列接続され、ダイオードブリッジの対角頂点部cと第2入力端6bとの間にスイッチング素子が接続され、ダイオードブリッジの対角頂点部bと第1出力端7aとの間にコイルLが接続され、ダイオードブリッジの対角頂点部dと第2出力端7bとが接続され、コンデンサCoが第1出力端と第2出力端7bとが接続され、コンデンサCoが第1出力端と第2出力端との間に接続され、制御部は、スイッチング素子をオン/オフ制御して、交流入力電圧Vacを目標電圧値を有する直流出力電圧Vdcに変換する。

【選択図】図1

#### 【特許請求の範囲】

# 【請求項1】

第1入力端および第2入力端からなる入力端子対に入力される交流入力電圧を所望の目標電圧値を有する直流出力電圧に変換して第1出力端および第2出力端からなる出力端子対から出力させるAC/DC変換装置において、

コイル、コンデンサ、ダイオードブリッジおよびスイッチング素子を有するチョッパ部と、

前記交流入力電圧の電圧値を検知する入力電圧検知部と、

前記直流出力電圧の電圧値を検知する出力電圧検知部と、

前記入力電圧検知部および前記出力電圧検知部が検知した電圧値に基づいて、前記直流出力電圧の電圧値が前記目標電圧値となるように前記チョッパ部の前記スイッチング素子をオン/オフ制御する制御部と

を備え、

前記第1入力端と前記第2入力端との間に前記ダイオードブリッジおよび前記スイッチング素子からなる直列回路が接続され、

前記ダイオードブリッジの入力側にある一対の対角頂点部の一方と、前記第1入力端および前記第2入力端の少なくとも一方との間に前記スイッチング素子が接続され、

前記ダイオードブリッジの出力側にある一対の対角頂点部の一方に前記コイルの一端が接続され、前記コイルの他端が前記第1出力端に接続され、

前記ダイオードブリッジの出力側にある一対の対角頂点部の他方と前記第2出力端とが接続され、

前記コンデンサが、前記第1出力端と前記第2出力端との間に接続され、

前記制御部は、前記交流入力電圧の電圧値および前記目標電圧値に応じて、前記スイッチング素子をオン/オフ制御して、前記交流入力電圧を前記目標電圧値を有する直流出力電圧に変換することを特徴とするAC/DC変換装置。

## 【請求項2】

前記制御部は、

前記交流入力電圧の電圧値が正であって、かつ、該電圧値が前記目標電圧値以上である場合には、前記チョッパ部を正の降圧チョッパ動作状態にし、

前記交流入力電圧の電圧値が負であって、かつ、該電圧値の絶対値が前記目標電圧値以上である場合には、前記チョッパ部を負の降圧チョッパ動作状態にし、

前記交流入力電圧の電圧値の絶対値が前記目標電圧値未満である場合には、前記チョッパ部をチョッパ動作停止状態にすることを特徴とする請求項 1 に記載のAC/DC変換装置。

# 【請求項3】

前記交流入力電圧の入力が開始されてから所定の時間が経過するまでの間および/または前記直流出力電圧の電圧値が所定の電圧値に到達するまでの間、前記制御部は、前記正の降圧チョッパ動作状態において、前記スイッチング素子のオン時間を短くすることにより、デューティを低く設定することを特徴とする請求項1または2に記載のAC/DC変換装置。

【請求項4】

前記交流入力電圧の入力が開始されてから所定の時間が経過するまでの間および / または前記直流出力電圧の電圧値が所定の電圧値に到達するまでの間、前記制御部は、前記負の降圧チョッパ動作状態において、前記スイッチング素子のオン時間を短くすることにより、デューティを低く設定することを特徴とする請求項 1 ~ 3 のいずれかに記載の A C / D C 変換装置。

#### 【請求項5】

前記スイッチング素子は、互いに逆直列接続された一対のMOSFETからなり、 前記一対のMOSFETの各ゲートが前記制御部に共通接続され、ソース同士が接続され、一方のドレインが前記第1入力端および前記第2入力端のいずれか一方に接続され、 10

20

30

40

他方のドレインが前記ダイオードブリッジの入力側にある一対の対角頂点部の一方に接続されていることを特徴とする請求項1~4のいずれかに記載のAC/DC変換装置。

## 【請求項6】

前記ダイオードブリッジを構成するダイオードは、SiC、GaNまたはダイヤモンドのワイドギャップ半導体からなるショットキーバリアダイオードからなることを特徴とする請求項1~5のいずれかに記載のAC/DC変換装置。

【発明の詳細な説明】

# 【技術分野】

# [0001]

本発明は、交流入力電圧を所望の目標電圧値を有する直流出力電圧に変換するAC/DC変換装置に関する。

# 【背景技術】

# [0002]

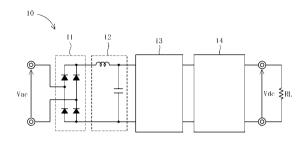

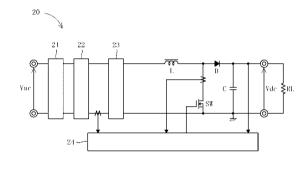

従来のAC/DC変換装置として、例えば特許文献1には図7に示すAC/DC変換装置10が開示されている。同図に示すように、AC/DC変換装置10は、交流入力電圧 Vacを所望の目標電圧値を有する直流出力電圧Vdcに変換するものであって、ダイオードブリッジ回路11と、高周波フィルタ回路12と、昇圧チョッパ回路からなる力率改善回路13と、降圧チョッパ回路からなるDC-DC変換回路14とを備えている。

# [0003]

このAC/DC変換装置10は、昇圧チョッパ回路および降圧チョッパ回路の両方を備えているので、上記目標電圧値を交流入力電圧Vacの電圧値よりも低い電圧値に設定することも、高い電圧値に設定することもできる。

#### [0004]

また、従来の別のAC/DC変換装置として、例えば非特許文献1には図8に示すAC /DC変換装置20が開示されている。同図に示すように、AC/DC変換装置20は、 交流入力電圧Vacを所望の目標電圧値(ただし、交流入力電圧Vacの電圧値以上)を 有する直流出力電圧Vdcに変換するものであって、ノイズフィルタ回路21と、突入防 止回路22と、ダイオードブリッジ回路23と、スイッチング素子SW等からなるチョッ パ回路と、直流出力電圧Vdcの電圧値および各部の電流値に基づいてスイッチング素子 SWを制御する制御部24とを備えている。

【先行技術文献】

#### 【特許文献】

#### [0005]

【特許文献1】特開2001-86737号公報

# 【非特許文献】

# [0006]

【非特許文献1】山崎浩、「アクティブフィルタの特徴と開発・応用現状」、電子技術、日刊工業新聞社、平成2年3月発行、第32巻、第3号、p.76(図9)

## 【発明の概要】

【発明が解決しようとする課題】

#### [0007]

しかしながら、上記AC/DC変換装置10、20は、ダイオードブリッジ回路11、 23に常に入力電流が流れるため、出力電力が増加して入力電流が増加すると、それに応 じてダイオードブリッジ回路11、23で発生する損失が増加し、効率が悪化するという 問題があった。そして、AC/DC変換装置20については、突入防止回路22にも常に 入力電流が流れるため、当該回路においても損失が発生していた。

#### [0008]

また、目標電圧値を広い範囲で設定できるAC/DC変換装置10の効率は、直列接続された力率改善回路(昇圧チョッパ回路)13およびDC-DC変換回路(降圧チョッパ回路)14の効率の積となるので、一般的に低く、改善の余地は限定的であった。そして

20

10

30

40

、上記の通り、AC/DC変換装置20は、目標電圧値を交流入力電圧Vacよりも低く 設定することができない。

# [0009]

また、特に上記AC/DC変換装置10では、昇圧チョッパ動作および降圧チョッパ動作が行われるので、安定化された直流出力電圧Vdcを得るための制御が複雑化していた

#### [0010]

本発明は上記事情に鑑みてなされたものであって、その課題とするところは、従来のものよりも効率に優れ、かつ、簡単な構成で安定化された直流出力電圧を得ることができるAC/DC変換装置を提供することにある。

【課題を解決するための手段】

## [0011]

上記課題を解決するために、本発明に係るAC/DC変換装置は、第1入力端および第 2 入力端からなる入力端子対に入力される交流入力電圧を所望の目標電圧値を有する直流 出力電圧に変換して第1出力端および第2出力端からなる出力端子対から出力させるAC / D C 変 換 装 置 に お い て 、 コ イ ル 、 コ ン デ ン サ 、 ダ イ オ ー ド ブ リ ッ ジ お よ び ス イ ッ チ ン グ 素子を有するチョッパ部と、交流入力電圧の電圧値を検知する入力電圧検知部と、直流出 力電圧の電圧値を検知する出力電圧検知部と、入力電圧検知部および出力電圧検知部が検 知した電圧値に基づいて、直流出力電圧の電圧値が目標電圧値となるようにチョッパ部の ス イ ッ チ ン グ 素 子 を オ ン / オ フ 制 御 す る 制 御 部 と を 備 え 、 第 1 入 力 端 と 第 2 入 力 端 と の 間 にダイオードブリッジおよびスイッチング素子からなる直列回路が接続され、ダイオード ブ リ ッ ジ の 入 力 側 に あ る 一 対 の 対 角 頂 点 部 の 一 方 と 、 第 1 入 力 端 お よ び 第 2 入 力 端 の 少 な くとも一方との間にスイッチング素子が接続され、ダイオードブリッジの出力側にある一 対 の 対 角 頂 点 部 の 一 方 に コ イ ル の 一 端 が 接 続 さ れ 、 コ イ ル の 他 端 が 第 1 出 力 端 に 接 続 さ れ 、 ダ イ オ ー ド ブ リ ッ ジ の 出 力 側 に あ る 一 対 の 対 角 頂 点 部 の 他 方 と 第 2 出 力 端 と が 接 続 さ れ コンデンサが、第1出力端と第2出力端との間に接続され、制御部は、交流入力電圧の 電 圧 値 お よ び 目 標 電 圧 値 に 応 じ て 、 ス イ ッ チ ン グ 素 子 を オ ン / オ フ 制 御 し て 、 交 流 入 力 電 圧を目標電圧値を有する直流出力電圧に変換することを特徴としている。

# [0012]

この構成によれば、交流入力電圧の電圧値および目標電圧値に応じてスイッチング素子がオン / オフ制御されることにより、交流入力電圧が直接スイッチングされるので、常に交流入力電圧を整流するダイオードブリッジ回路を不要とすることができ、該回路による損失の発生を防ぐことができる。また、この構成によれば、2以上のチョッパ回路を直列接続する必要がないので、効率が悪化するのを防ぐことができる。

# [0013]

ここで、上記AC/DC変換装置の制御部は、交流入力電圧の電圧値が正であって、かつ、該電圧値が目標電圧値以上である場合には、チョッパ部を正の降圧チョッパ動作状態にし、交流入力電圧の電圧値が負であって、かつ、該電圧値の絶対値が目標電圧値以上である場合には、チョッパ部を負の降圧チョッパ動作状態にし、交流入力電圧の電圧値の絶対値が目標電圧値未満である場合には、チョッパ部をチョッパ動作停止状態にすることが好ましい。

[0014]

この構成によれば、チョッパ部が降圧チョッパ動作を行うのみであるため、制御部が簡単な構成となるAC/DC変換装置を提供することができる。

#### [0015]

また、上記AC/DC変換装置の制御部は、交流入力電圧の入力が開始されてから所定の時間が経過するまでの間および/または直流出力電圧の電圧値が所定の電圧値に到達するまでの間、正の降圧チョッパ動作状態において、スイッチング素子のオン時間を短くすることにより、デューティを低く設定することが好ましい。

# [0016]

10

20

30

この構成によれば、正の降圧チョッパ動作状態におけるデューティを変えるだけでソフ トスタート機能を実現することができるので、突入防止回路を不要とすることができ、該 回路による損失の発生を防ぐことができる。

#### [0017]

また、上記AC/DC変換装置の制御部は、交流入力電圧の入力が開始されてから所定 の時間が経過するまでの間および/または直流出力電圧の電圧値が所定の電圧値に到達す るまでの間、負の降圧チョッパ動作状態において、スイッチング素子のオン時間を短くす ることにより、デューティを低く設定することが好ましい。

# [0018]

この構成によれば、負の降圧チョッパ動作状態におけるデューティを変えるだけでソフ トスタート機能を実現することができるので、突入防止回路を不要とすることができ、該 回路による損失の発生を防ぐことができる。

#### [0019]

また、上記AC / DC変換装置のスイッチング素子は、互いに逆直列接続された一対の MOSFETからなり、一対のMOSFETの各ゲートが制御部に共通接続され、ソース 同 士 が 接 続 さ れ 、 一 方 の ド レ イ ン が 第 1 入 力 端 お よ び 第 2 入 力 端 の い ず れ か 一 方 に 接 続 さ れ、他方のドレインがダイオードブリッジの入力側にある一対の対角頂点部の一方に接続 されていることが好ましい。

## [0020]

この構成によれば、互いに逆直列接続された一対のMOSFETはスイッチング素子の 中でも動作効率が特に良好なため、より効率に優れたAC/DC変換装置を実現できる。

また、上記AC/DC変換装置のダイオードブリッジを構成するダイオードは、SiC GaNまたはダイヤモンドのワイドギャップ半導体からなるショットキーバリアダイオ ードからなることが好ましい。

# [0022]

この構成によれば、SiC、GaNまたはダイヤモンドのワイドギャップ半導体からな るショットキーバリアダイオードはダイオードの中でも特に低損失であるため、より低損 失で低ノイズのAC/DC変換装置を実現できる。

# 【発明の効果】

[0023]

本発明によれば、従来のものよりも効率に優れ、かつ、簡単な構成で安定化された直流 出力電圧を得ることができるAC/DC変換装置を提供することができる。

# 【図面の簡単な説明】

[0024]

- 【図1】本発明に係るAC/DC変換装置の概略構成図である。

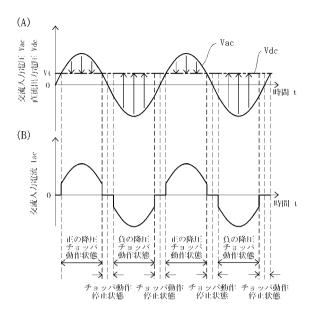

- 【図2】(A)は、交流入力電圧と直流出力電圧の対応関係を示す時間波形であり、(B )は、交流入力電流を示す時間波形である。

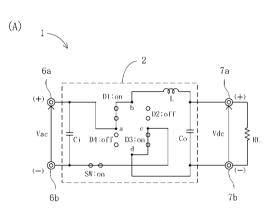

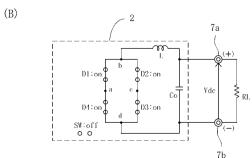

- 【 図 3 】 本 発 明 に 係 る A C / D C 変 換 装 置 の 正 の 降 圧 チ ョ ッ パ 動 作 状 態 の 等 価 回 路 図 で あ る。

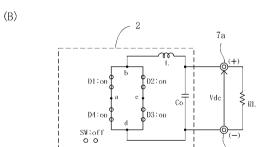

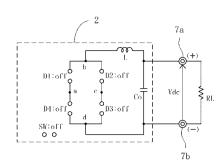

- 【 図 4 】 本 発 明 に 係 る A C / D C 変 換 装 置 の 負 の 降 圧 チ ョ ッ パ 動 作 状 態 の 等 価 回 路 図 で あ

- 【 図 5 】 本 発 明 に 係 る A C / D C 変 換 装 置 の チ ョ ッ パ 動 作 停 止 状 態 の 等 価 回 路 図 で あ る 。

- 【図6】本発明に係るAC/DC変換装置の変形例を示す概略構成図である。

- 【図7】従来のAC/DC変換装置の概略構成図である。

- 【図8】従来のAC/DC変換装置の概略構成図である。

# 【発明を実施するための形態】

# [0025]

以下、添付図面を参照して、本発明に係るAC/DC変換装置の好ましい実施形態につ いて説明する。

10

20

30

40

#### [0026]

図1は、本発明に係るAC/DC変換装置1の概略構成図である。同図に示すように、AC/DC変換装置1は、第1入力端6aおよび第2入力端6bからなる入力端子対に入力された交流入力電圧Vacを所望の目標電圧値Vtを有する直流出力電圧Vdcに変換し、該直流出力電圧Vdcを第1出力端7aおよび第2出力端7bからなる出力端子対から負荷RLに出力するものであって、チョッパ部2と、交流入力電圧Vacの電圧値を検知する入力電圧検知部3と、直流出力電圧Vdcの電圧値を検知する出力電圧検知部4と、入力電圧検知部3および出力電圧検知部4が検知した電圧値に基づいて、直流出力電圧Vdcの電圧値が目標電圧値Vtとなるようにチョッパ部2を制御する制御部5とを備えている。

[0027]

チョッパ部 2 は、第 1 入力端 6 a と第 2 入力端 6 b との間に接続されたダイオードブリッジ D B およびスイッチング素子 S W の直列回路と、コイル L と、コンデンサ C o とを有する。

[0028]

ダイオードブリッジDBは、第1~第4ダイオードD1~D4から構成され、入力側にある一対の対角頂点部a、cと、出力側にある一対の対角頂点部b、dとを有する。

ダイオードブリッジDBの入力側にある対角頂点部 a には、第1ダイオードD1のアノードおよび第4ダイオードD4のカソードが接続され、ダイオードブリッジDBの入力側にある対角頂点部 c には、第2ダイオードD2のアノードおよび第3ダイオードD3のカソードが接続されている。

一方、ダイオードブリッジDBの出力側にある対角頂点部bには、第1ダイオードD1のカソードおよび第2ダイオードD2のカソードが接続され、ダイオードブリッジDBの出力側にある対角頂点部dには、第3ダイオードD3のアノードおよび第4ダイオードD4のアノードが接続されている。

また、ダイオードブリッジDBの入力側にある対角頂点部 a と第 1 入力端 6 a とが接続され、ダイオードブリッジDBの出力側にある対角頂点部 d と第 2 出力端 7 b とが接続されている。

[0029]

スイッチング素子SWは、制御部5によりオン/オフ制御されるものであって、ダイオードブリッジDBの入力側にある対角頂点部cと第2入力端6bとの間に接続されている。なお、スイッチング素子SWは、対角頂点部aと第1入力端6aとの間に接続されていてもよい。また、制御を容易にするために、対角頂点部aと第1入力端6aとの間および対角頂点部cと第2入力端6bとの間の両方にスイッチング素子SWを挿入するようにしてもよい。

[0030]

コイル L の一端は、ダイオードブリッジ D B の出力側にある対角頂点部 b に接続され、コイル L の他端は、第 1 出力端 7 a に接続されている。

コンデンサ С о は、第 1 出力端 7 a と第 2 出力端 7 b との間に接続されている。

[0031]

なお、チョッパ部 2 は、第 1 入力端 6 a と第 2 入力端 6 b との間に接続されたコンデンサ C i も備えているが、該コンデンサ C i はコンデンサ C o に比べて容量が非常に小さく、チョッパ部 2 の動作状態にはほとんど影響を与えないので、以下では、説明を簡単化するためにコンデンサ C i を無視する。

[0032]

図2(A)および(B)に示すように、本発明では、交流入力電圧Vac(第2入力端6bを基準とした場合の第1入力端6aの電位)の電圧値と目標電圧値Vt(負荷RLに出力すべき直流出力電圧Vdcの電圧値)とに応じて制御部5がスイッチング素子SWの制御を変更する。言い換えると、本発明では、交流入力電圧Vacの電圧値および目標電圧値Vtに応じてチョッパ部2のチョッパ動作状態が変更される。

10

20

30

40

#### [0033]

具体的には、本発明に係るAC/DC変換装置1のチョッパ部2は、図2(A)および(B)に示すように、(1)交流入力電圧Vacの電圧値が正であって、かつ、該電圧値が目標電圧値Vt以上である場合には、入力電圧が正である場合における降圧チョッパ動作状態(以下「正の降圧チョッパ動作状態」という)になり、(2)交流入力電圧Vacの電圧値が負であって、かつ、該電圧値の絶対値が目標電圧値Vt以上である場合には、入力電圧が負である場合における降圧チョッパ動作状態(以下「負の降圧チョッパ動作状態」という)になり、(3)交流入力電圧Vacの電圧値の絶対値が目標電圧値Vt未満である場合には、チョッパ動作停止状態になる。これらの動作状態により、直流出力電圧Vdcの電圧値は、目標電圧値Vtに維持(安定化)される。なお、図2(A)は、上記の制御により直流出力電圧Vdcの電圧値が目標電圧値Vtとなった状態を示している。

[0034]

次に、チョッパ部2の3つの動作状態のうち、まず正の降圧チョッパ動作状態について 説明する。本動作状態におけるAC/DC変換装置1は、図3(A)および(B)に示す 簡素な等価回路で表現される。なお、図3(A)においては、スイッチング素子SWがオ ン状態になっており、図3(B)においては、スイッチング素子SWがオフ状態になって いる。

# [0035]

図3(A)に示すように、スイッチング素子SWがオン状態とされると、ダイオードブリッジDBを構成する第1~第4ダイオードD1~D4のうち、第1および第3ダイオードD1、D3が導通状態となり、コイルLにエネルギーが蓄えられる。一方、図3(B)に示すように、スイッチング素子SWがオフ状態とされると、第1~第4ダイオードD1~D4が導通状態となり、コイルLに蓄えられたエネルギーが放出される。

[0036]

この正の降圧チョッパ動作状態において、1スイッチング周期Tにおけるスイッチング素子SWのオン時間をTonとすると、スイッチング素子SWのデューティ (=Ton/T)は次式で求めることができる。

デューティ = Vdcの電圧値/Vacの電圧値

# [0037]

したがって、この正の降圧チョッパ動作状態において、適切なデューティ でスイッチング素子SWをオン状態またはオフ状態にして、交流入力電圧Vacを降圧することによって、電圧値が目標電圧値Vtである直流出力電圧Vdcを得、該直流出力電圧Vdcを 負荷RLに供給することができる。

[0038]

次に、負の降圧チョッパ動作状態について説明する。本動作状態におけるAC/DC変換装置1は、図4(A)および(B)に示す簡素な等価回路で表現される。なお、図4(A)においては、スイッチング素子SWがオン状態になっており、図4(B)においては、スイッチング素子SWがオフ状態になっている。また、図4(B)は、図3(B)と同じ等価回路を示している。

[ 0 0 3 9 ]

図4(A)に示すように、スイッチング素子SWがオン状態とされると、第2および第4ダイオードD2、D4が導通状態となり、コイルLにエネルギーが蓄えられる。一方、図4(B)に示すように、スイッチング素子SWがオフ状態とされると、図3(B)と同様、第1~第4ダイオードD1~D4が導通状態となり、コイルLに蓄えられたエネルギーが放出される。

## [0040]

また、この負の降圧チョッパ動作において、1スイッチング周期Tにおけるスイッチング素子SWのオン時間をTonとすると、スイッチング素子SWのデューティ ( = Ton / T)は次式で求めることができる。

10

20

30

40

デューティ = V d c の電圧値 / V a c の電圧値の絶対値

## [0041]

したがって、この負の降圧チョッパ動作状態においても、適切なデューティ でスイッチング素子SWをオン状態またはオフ状態にして、交流入力電圧Vacを降圧することによって、電圧値が目標電圧値Vtである直流出力電圧Vdcを得、該直流出力電圧Vdcを負荷RLに供給することができる。

## [0042]

最後に、チョッパ動作停止状態におけるAC/DC変換装置1は、図5に示す簡素な等価回路で表現される。

交流入力電圧Vacの電圧値の絶対値が目標電圧値Vt未満である場合には、チョッパ部2の降圧チョッパ動作によって目標電圧値Vtである直流出力電圧Vdcを得ることはできないため、このチョッパ動作停止状態においては、スイッチング素子SWがオフ状態に維持されて、チョッパ部2のチョッパ動作が停止される。

#### [0043]

以上のように、本発明に係るAC/DC変換装置1では、制御部5が、(1)交流入力電圧Vacの電圧値が正であって、かつ、該電圧値が目標電圧値Vt以上である場合には、チョッパ部2を正の降圧チョッパ動作状態にし、(2)交流入力電圧Vacの電圧値が負であって、かつ、該電圧値の絶対値が目標電圧値Vt以上である場合には、チョッパ部2を負の降圧チョッパ動作状態にし、(3)交流入力電圧Vacの電圧値の絶対値が目標電圧値Vt未満である場合には、チョッパ部2をチョッパ動作停止状態にする。

したがって、本発明に係るAC/DC変換装置1によれば、交流入力電圧Vacの電圧値および目標電圧値Vtに応じてスイッチング素子SWがオン/オフ制御されることにより、交流入力電圧Vacが直接スイッチングされるので、従来技術のような常に交流入力電圧を整流するダイオードブリッジ回路(図7の符号11、図8の符号23)を不要とすることができるので、該回路による損失の発生を防ぐことができ、効率を改善することができる。

# [0044]

また、図1および図3~図5から明らかなように、本発明に係るAC/DC変換装置1は、2つ以上のチョッパ回路を直列接続した構成とはなっていない。したがって、本発明に係るAC/DC変換装置1によれば、2つ以上のチョッパ回路のそれぞれが効率を悪化させることによる装置全体の効率の悪化を防ぐことができる。

#### [0045]

さらに、本発明に係るAC/DC変換装置1によれば、チョッパ部2は降圧チョッパ動作を行うのみであるため、制御部5が簡単な構成となる。

#### [0046]

なお、本発明に係るAC/DC変換装置1は上記構成に限定されるものではなく、種々の変形例が考えられる。

# [0047]

# (変形例1)

上記AC/DC変換装置1のスイッチング素子SWは、例えば、図6に示すような、互いに逆直列接続された一対のNチャネルMOSFETQ1およびQ2からなり、一対のNチャネルMOSFETQ1およびQ2は、各ゲートが制御部5に共通接続され、ソース同士が接続され、一方のドレインが第2入力端6bに接続され、他方のドレインが対角頂点部cに接続されていることが好ましい。

# [ 0 0 4 8 ]

この構成によれば、互いに逆直列接続された一対のNチャネルMOSFETQ1およびQ2はスイッチング素子の中でも動作効率が特に良好なため、より効率に優れたAC/DC変換装置1を実現できる。なお、効率が許容できれば、制御の容易さからNチャネルMOSFETに代えてPチャネルMOSFETを用いてもよい。

10

20

30

40

#### [0049]

# (変形例2)

また、上記 A C / D C 変換装置 1 のダイオードブリッジ D B を構成する各ダイオード D 1 ~ D 4 は、 S i C (シリコンカーバイド)、 G a N (ガリウムナイトライド)またはダイヤモンドのワイドギャップ半導体からなるショットキーバリアダイオードからなることが好ましい。

#### [0050]

この構成によれば、SiC、GaNまたはダイヤモンドのワイドギャップ半導体からなるショットキーバリアダイオードはダイオードの中でも特に低損失であるため、より低損失で低ノイズのAC/DC変換装置1を実現できる。

10

# [0051]

#### (変形例3)

また、効率をさらに改善するためには、交流入力電圧 Vacの入力が開始されてから所定の時間が経過するまでの間および / または直流出力電圧 Vdcの電圧値が所定の電圧値 (例えば、目標電圧値 Vtの約95%)に到達するまでの間、各チョッパ動作状態におけるデューティを通常時とは異なったデューティとすることが好ましい。

## [0052]

例えば、正の降圧チョッパ動作状態においては、スイッチング素子SWがオフ状態に切り替えられたときに、コイルLに蓄積されていたエネルギーがコンデンサCoに供給され、また、負の降圧チョッパ動作状態においても、スイッチング素子SWがオフ状態に切り替えられたときに、コイルLに蓄積されていたエネルギーがコンデンサCoに供給されるので、通常時よりもデューディ (=Ton/T)を低めに設定してスイッチング素子SWのオン時間Tonを短くし、コイルLに蓄積されるエネルギーを減らすことで、突入電流の量を制限することができる。

20

# [0053]

したがって、この構成によれば、突入防止回路(図8の符号22)がなくても突入電流の量を制限することができるので、該回路による損失の発生を防ぐことができる。

#### [0054]

# (変形例4)

さらに、図示しない入力電流検出回路を設けて、制御部5が、入力電流波形を入力電圧 波形に近づけるようにスイッチング素子SWの制御を行うように構成されてもよい。 30

この構成によれば、高調波電流が抑制され、力率が改善され、より安定化された直流出力電圧 V d c を得ることのできる A C / D C 変換装置 1 が実現できる。

# 【符号の説明】

# [0055]

- 1 A C / D C 変換装置

- 2 チョッパ部

- 3 入力電圧検知部

- 4 出力電圧検知部

- 5 制御部

【図1】

【図2】

【図3】

# 【図4】

# 【図5】

# 【図7】

【図6】

【図8】

# フロントページの続き

(72)発明者 小堀 康功

群馬県桐生市天神町一丁目5番1号 国立大学法人群馬大学内

(72)発明者 小林 春夫

群馬県桐生市天神町一丁目5番1号 国立大学法人群馬大学内

(72)発明者 志々目 卓治

京都府京都市中京区烏丸通御池上る二条殿町551番地 ニチコン株式会社内

(72)発明者 大島 正樹

京都府京都市中京区烏丸通御池上る二条殿町551番地 ニチコン株式会社内

F ターム(参考) 5H006 CA07 CB01 CC02 DA04 DB02 DC05