# Digital Calibration for Current-Steering DAC Linearity Enhancement

Faculty of Science and Technology, Division of Electronics & Informatics Gunma University Shaiful Nizam Mohyar, Haruo Kobayashi

- Introduction

- Problem Statement

- Proposed Techniques

- Half-Unary Current-Steering DAC

- Outlier Elimination

- Current Source Sorting

- Circuit

- Layout

- Simulation Result

- Conclusion

- Introduction

- Problem Statement

- Proposed Techniques

- Half-Unary Current-Steering DAC

- Outlier Elimination

- Current Source Sorting

- Circuit

- Layout

- Simulation Result

- Conclusion

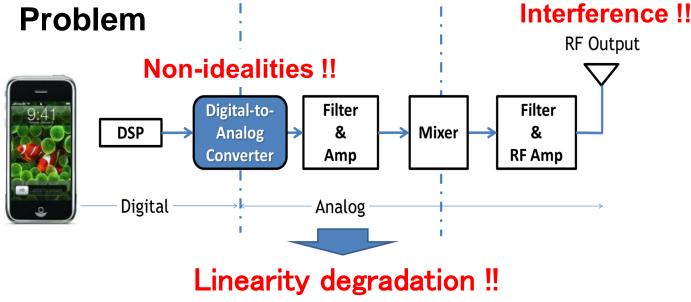

## Introduction

Background

•

Telecommunication devices

- Mobile phones, wireless modems & avionics

- High-speed, high-accuracy

- **Digital-to-Analog Converter (DAC)**

## **Objective & Investigated Method**

#### Objective

High SFDR current-steering DAC for communication application SFDR: Spurious Free Dynamic Range DAC: Digital-to-Analog Converter

#### Proposed method

- Current source mismatch effect reduction

- ① Half-unary DAC architecture

- ② Current source outlier elimination

- ③ Current source sorting

Static linearity improvement

- · Layout strategy

- D Clock-tree-like layout of current sources & switches

Dynamic linearity improvement

- Introduction

- Problem Statement

- Proposed Techniques

- Half-Unary Current-Steering DAC

- Outlier Elimination

- Current Source Sorting

- Circuit

- Layout

- Simulation Result

- Conclusion

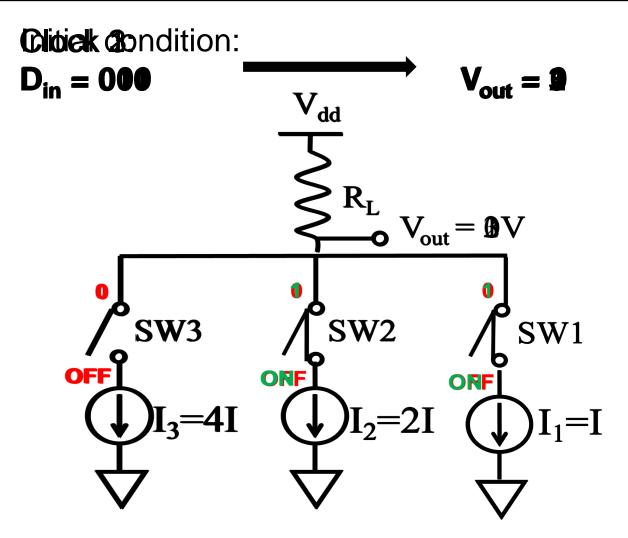

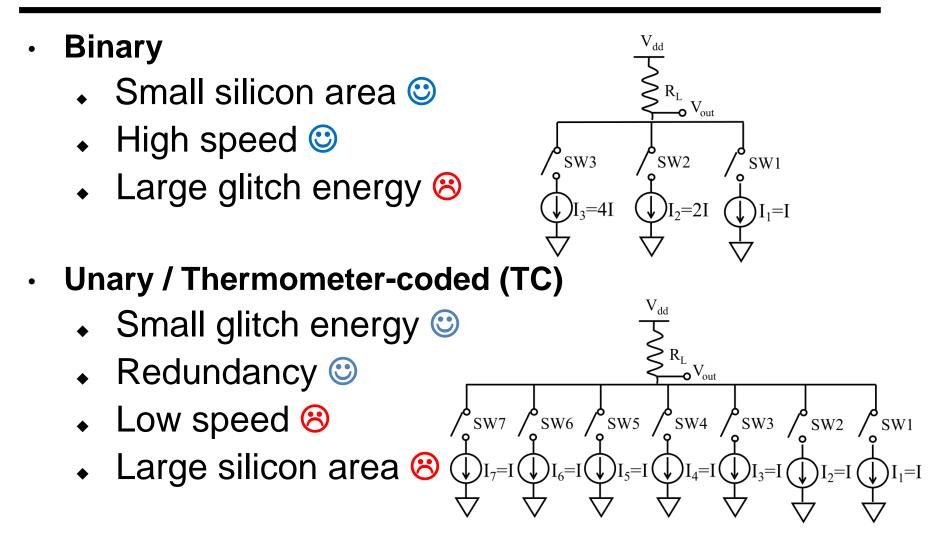

#### **Current-Steering DAC**

### 3b binary weighted DAC

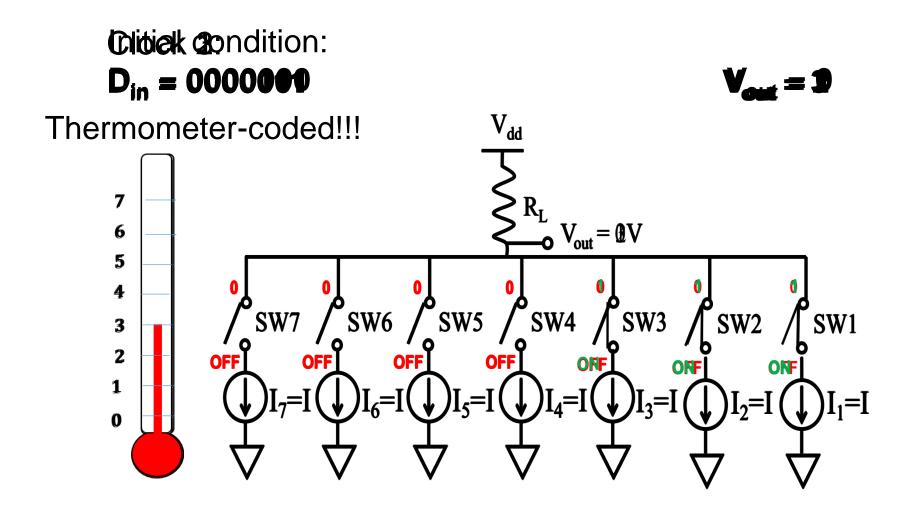

## 3b Unary weighted DAC

### Binary versus Unary CS DAC

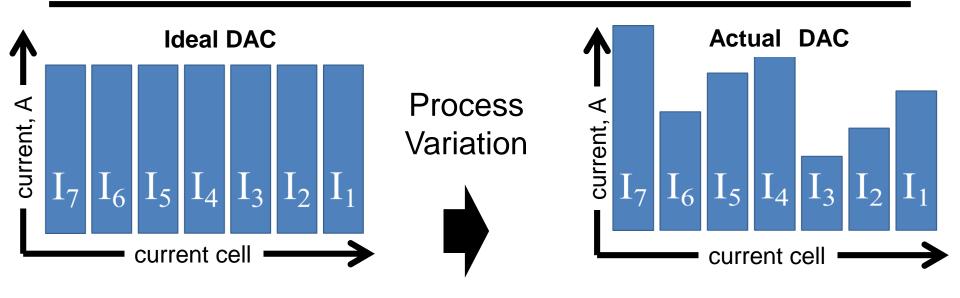

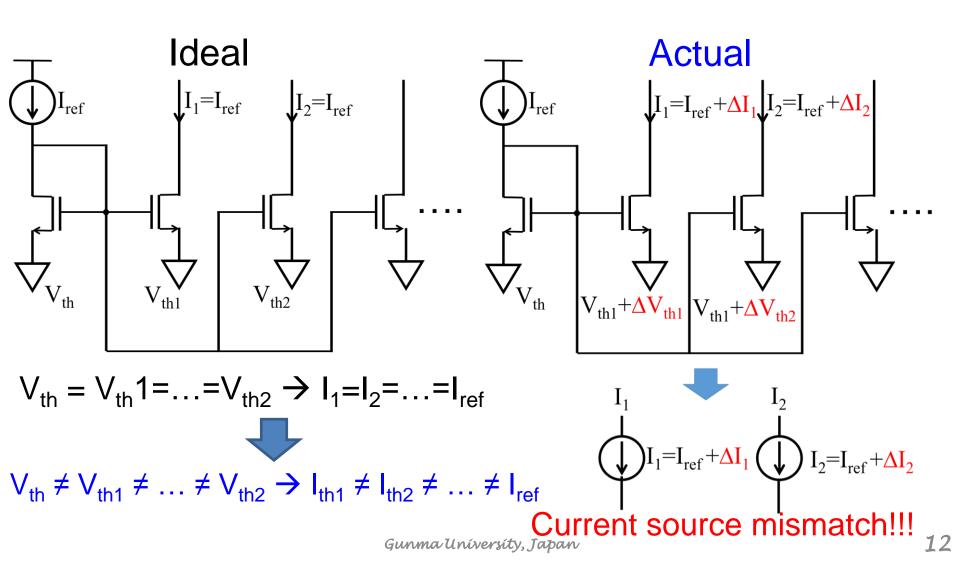

#### **Current Source Mismatch**

$$I_1 = I_2 = I_3 = I_4 = I_5 = I_6 = I_7 = I_6$$

$$\begin{aligned} I_{\text{ave}} &= (I_1 + I_2 + I_3 + I_4 + I_5 + I_6 + I_7)/7 \\ I_k &= I_{\text{ave}} + \mathbf{dI}_k \qquad (k = 1, 2, ..., 7) \end{aligned}$$

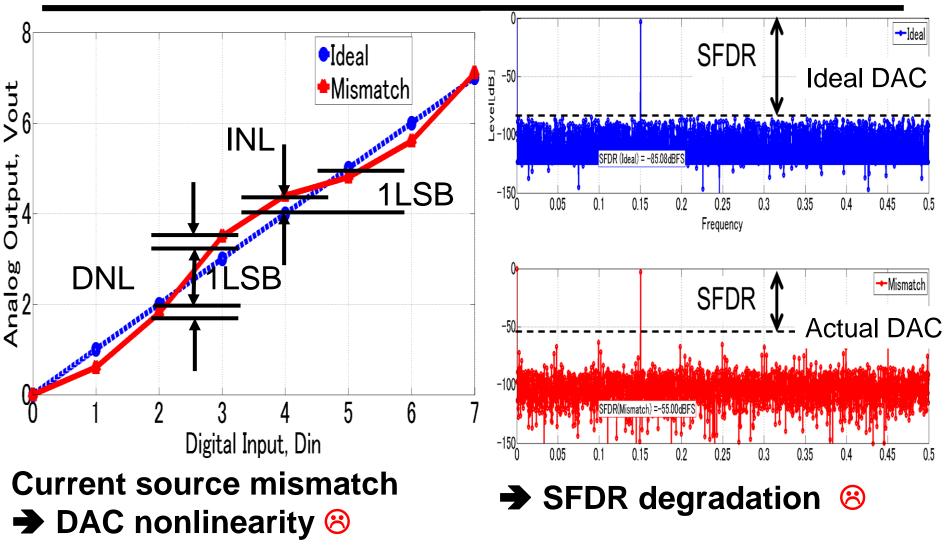

→ DAC nonlinearity ⊗!!!

#### **Current Source Mismatch**

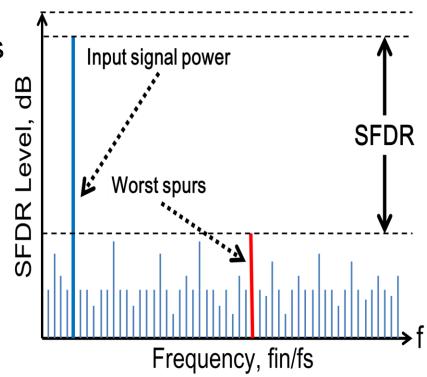

## Spurious Free Dynamic Range (SFDR)

#### **SFDR Degradation Sources**

- Unit current source mismatches

- ➔ Static nonlinearity

- Data-dependent output load variations

- ➔ Dynamic nonlinearity

## Nonlinearity & SFDR degradation

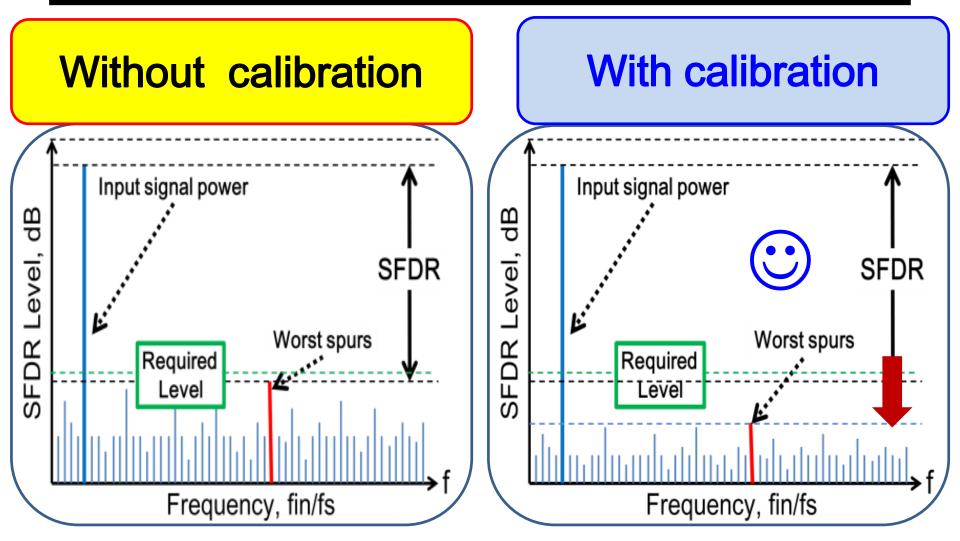

### SFDR Improvement With Calibration

## **Current-steering DAC Limitation**

- Transistor mismatch

- Current source mismatch

- Timing errors

DAC static & dynamic non-linearity

- Better transistor matching

- Iarge size → Power loss ⊗

- Laid out close to each other → Complicated ⊗

## **Design Approach**

#### Analog

- Complex hardware

- Not programmable

- Costly

- Digital

- Simple

- Programmable

- Low-cost

- → Digital rich approach

for fine CMOS implementation

17

- Introduction

- Problem Statement

- Proposed Techniques

- Half-Unary Current-Steering DAC

- Outlier Elimination

- Current Source Sorting

- Circuit

- Layout

- Simulation Result

- Conclusion

- Introduction

- Problem Statement

- Proposed Techniques

- Half-Unary Current-Steering DAC

- Outlier Elimination

- Current Source Sorting

- Circuit

- Layout

- Simulation Result

- Conclusion

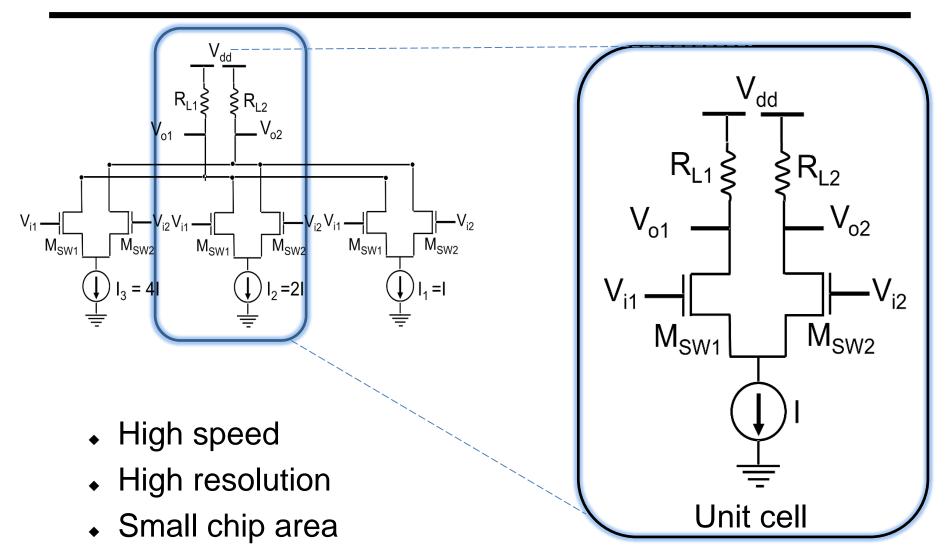

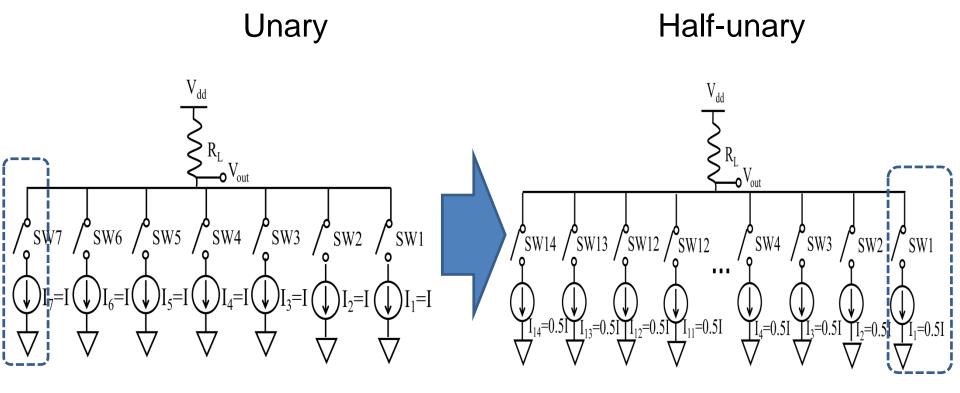

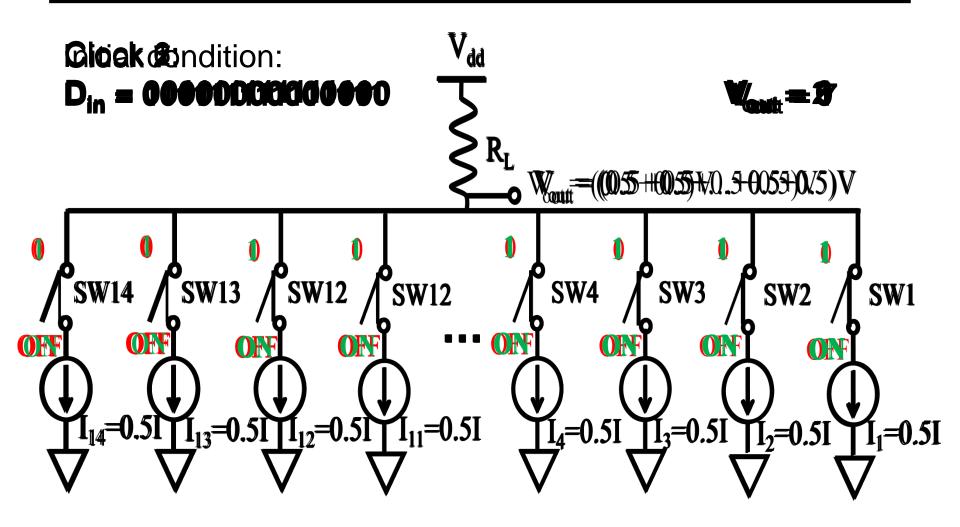

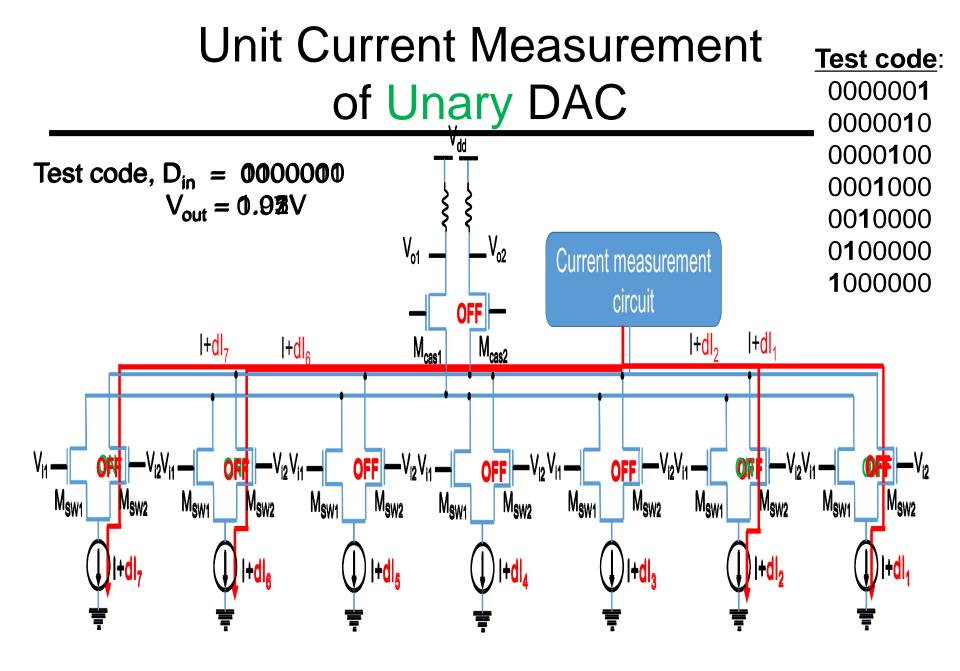

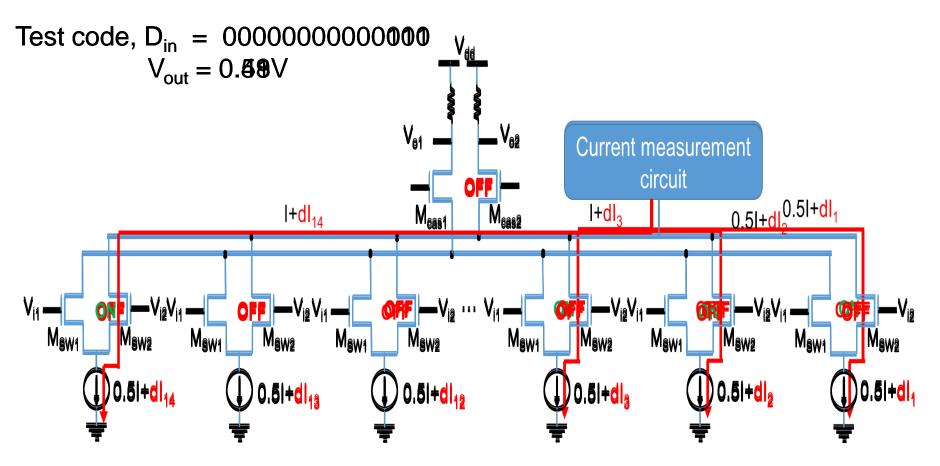

#### What is half-unary?

Each current source cell =

Each current source cell = 0.5IPair of 0.5I & 0.5I for output of I

### Half-unary current steering DAC

- Introduction

- Problem Statement

- Proposed Techniques

- Half-Unary Current-Steering DAC

- Outlier Elimination

- Current Source Sorting

- Circuit

- Layout

- Simulation Result

- Conclusion

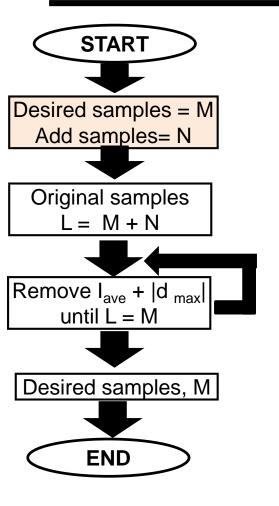

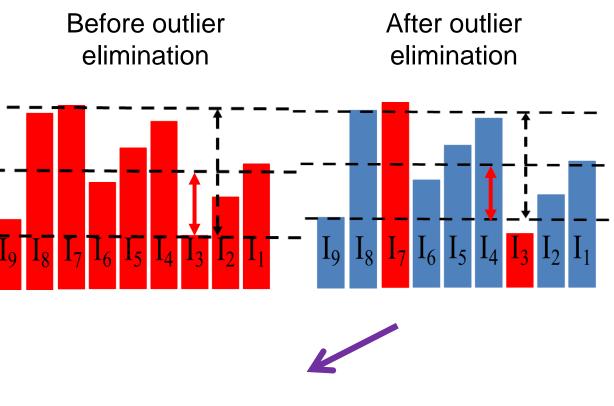

## **Current Source Outlier Elimination**

Current source deviation reduction

➔ Better DAC linearity☺!!!

#### Current Source Outlier Elimination Example

- Introduction

- Problem Statement

- Proposed Techniques

- Half-Unary Current-Steering DAC

- Outlier Elimination

- <u>Current Source Sorting</u>

- Circuit

- Layout

- Simulation Result

- Conclusion

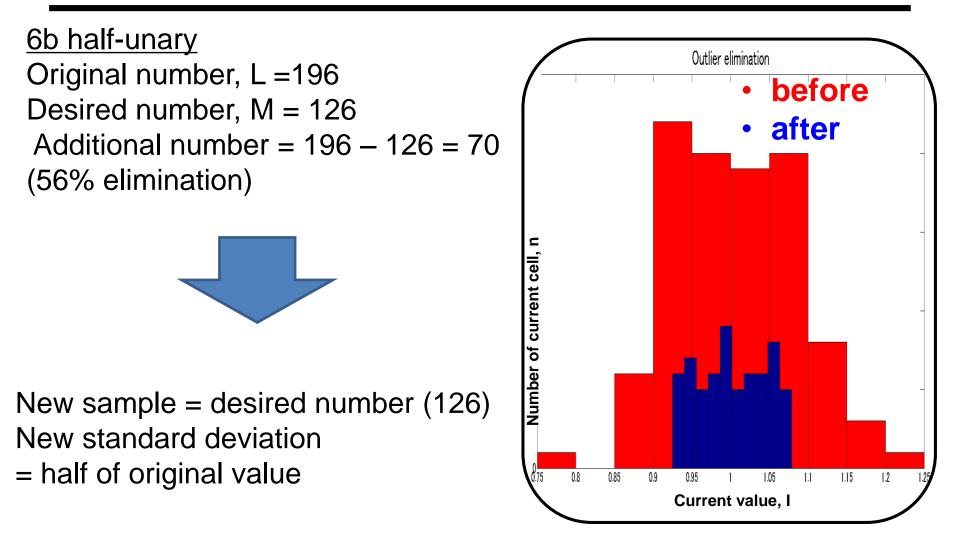

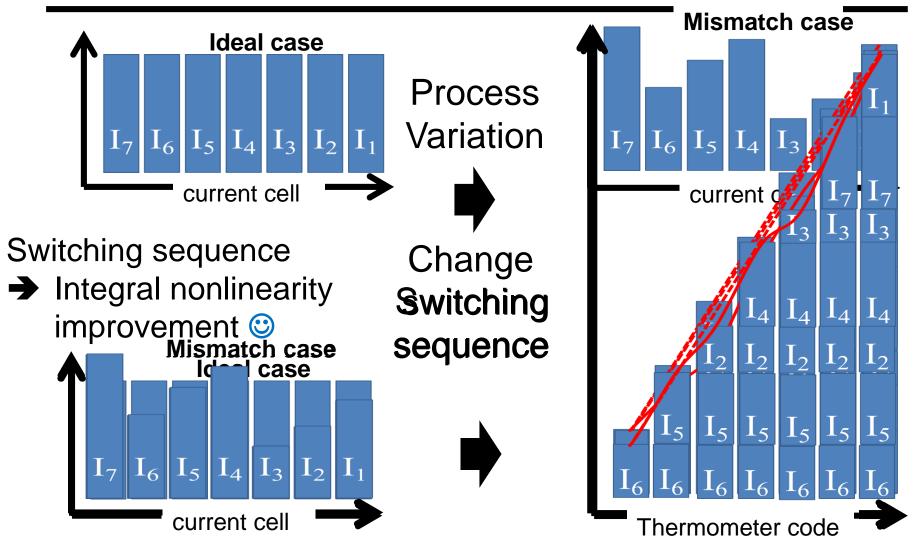

## Unit Current Cell Switching Sequence

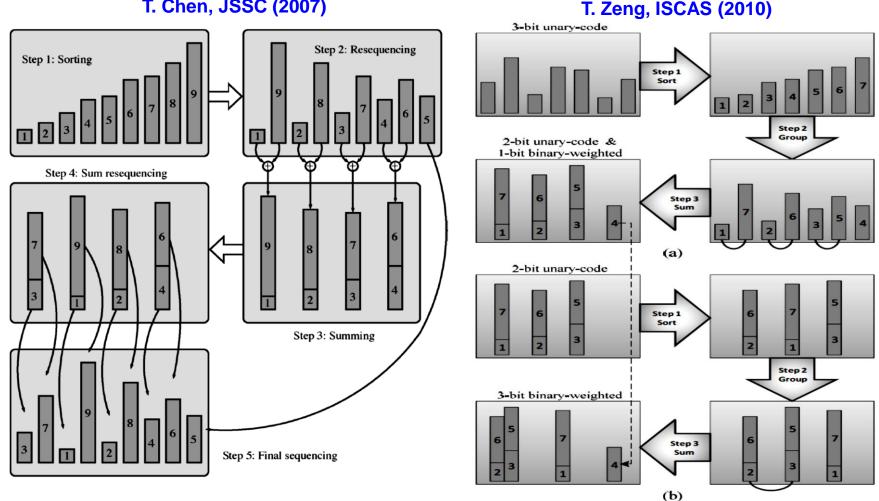

### Published Sort & Group Procedures

T. Chen, JSSC (2007)

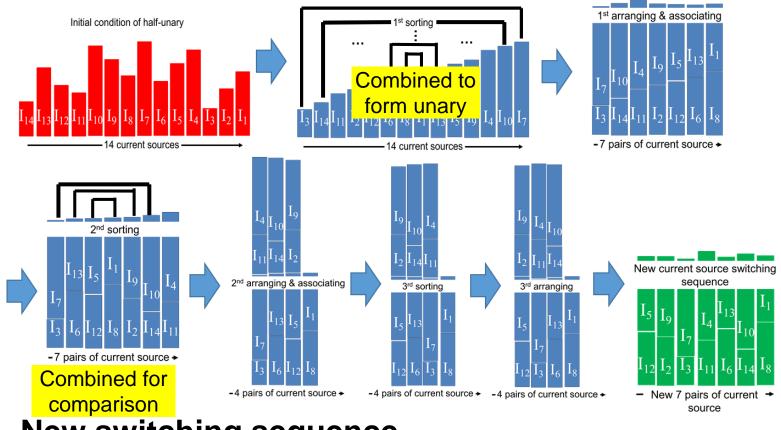

#### Proposed Current Source 3-stage Sort & Group Algorithm

#### New switching sequence

➔ More linearity improvement ☺!!!

## Sort & Group Techniques Comparison

| Technique                          | Features                                                                                                                         | Advantages                                                                                               | Drawbacks                                                              |

|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|

| SSPA<br>JSSC 2007 [2]              | <ul> <li>2-stage<br/>sort &amp; group</li> <li>Change switching<br/>sequence</li> </ul>                                          | Improve INL only                                                                                         | <ul> <li>Require<br/>additional current<br/>sources</li> </ul>         |

| Complete-folding<br>ISCAS 2010 [3] | <ul> <li>Convert<br/>unary to binary</li> </ul>                                                                                  | <ul> <li>Improve<br/>INL &amp; DNL</li> </ul>                                                            | <ul> <li>Procedure steps<br/>increase<br/>by DAC resolution</li> </ul> |

| This work                          | <ul> <li>3-stage<br/>sort &amp; group</li> <li>Convert<br/>half-unary to unary</li> <li>Change switching<br/>sequence</li> </ul> | <ul> <li>Improve more<br/>INL &amp; DNL</li> <li>Less procedure<br/>steps compared<br/>to [3]</li> </ul> | <ul> <li>Require twice<br/>current sources</li> </ul>                  |

SSPA –Switching sequence post-adjustment

- Introduction

- Problem Statement

- Proposed Techniques

- Half-Unary Current-Steering DAC

- Outlier Elimination

- Current Source Sorting

- <u>Circuit</u>

- Layout

- Simulation Result

- Conclusion

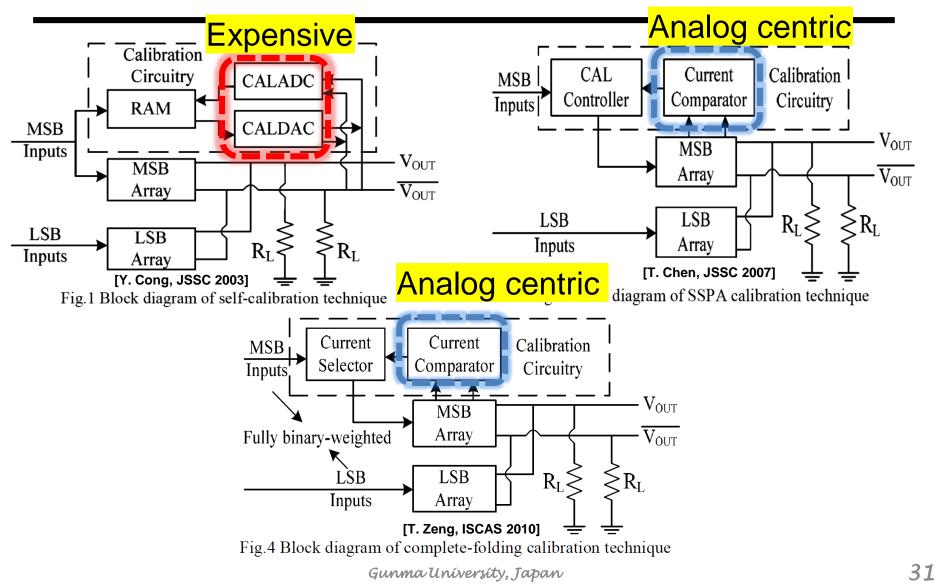

### **Previous Calibration Circuits**

## Published Calibration Circuit Comparison

| Technique                                            | Advantages                                                                                                                                  | Drawbacks                                                                     |

|------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|

| Self calibration<br>[JSSC 2003]<br>[14-b 100MHz] [1] | <ul> <li>High precision calibration</li> </ul>                                                                                              | <ul> <li>Require high precision<br/>calibration ADC</li> </ul>                |

| SSPA<br>[JSSC 2007]<br>[14-b 200MHz] [2]             | <ul> <li>Minimum additional<br/>analog &amp; digital circuit</li> <li>Defect current source<br/>replacement</li> <li>Improve INL</li> </ul> | <ul> <li>No DNL improvement</li> <li>Analog<br/>current comparator</li> </ul> |

| Complete-folding<br>[ISCAS 2010]<br>[14-b ] [3]      | <ul> <li>Minimum additional<br/>analog &amp; digital circuit</li> <li>Improve INL &amp; DNL</li> <li>Low voltage</li> </ul>                 | <ul> <li>Analog<br/>current comparator</li> </ul>                             |

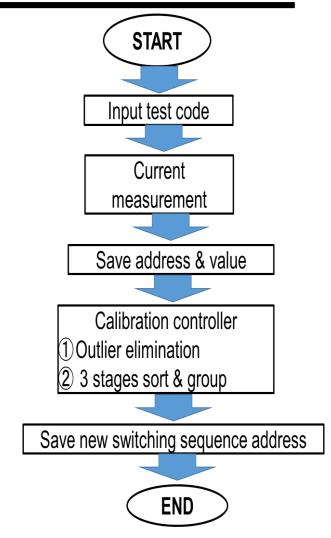

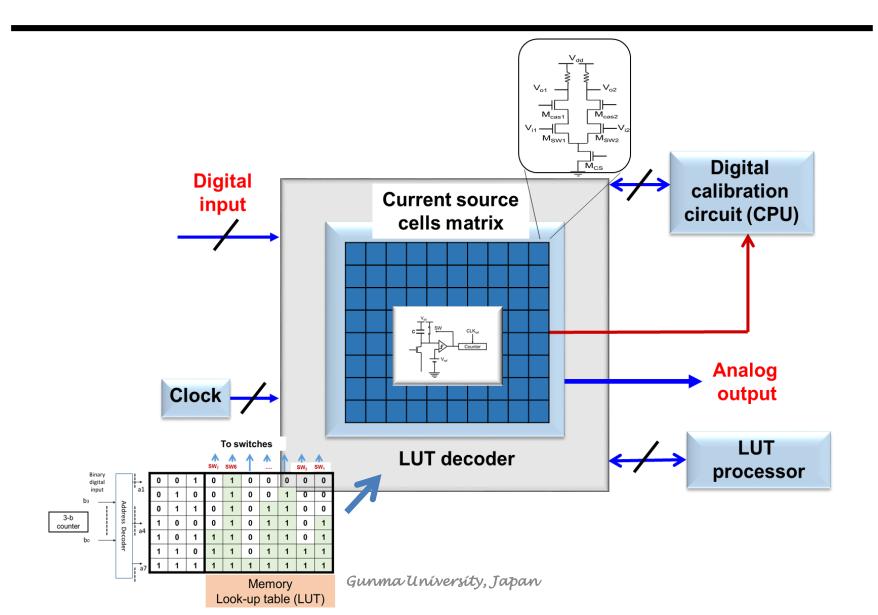

## **Proposed Calibration**

- Foreground Calibration

- Measure each current source

- Saving its value in memory (RAM).

- Calibration controller

- Outlier elimination

- 3-stage sort & group

- Obtained switching sequence is stored in look-up-table based decoder.

- Use during normal conversion operation.

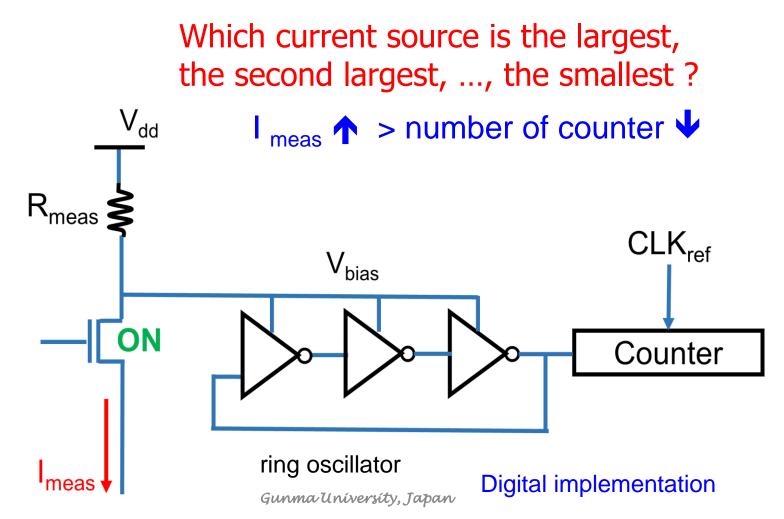

#### **Current Measurement Circuit**

Only need order of current values.

## Unit Current Measurement of Half-Unary DAC

No additional analog circuit (switches or routing).

Only add digital circuit for switch control

Gunma University, Japan

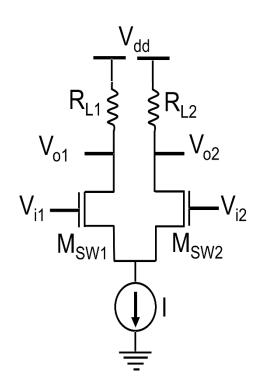

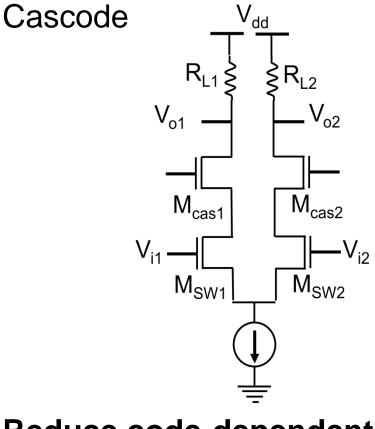

## **Current Source & Current Switch**

•

Basic

#### → Reduce code-dependent load variation <sup>©</sup> !!!

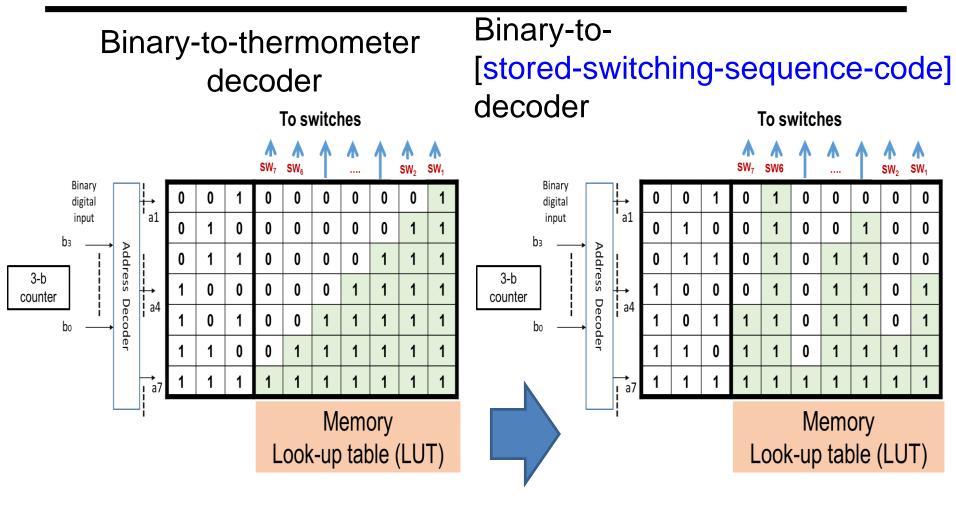

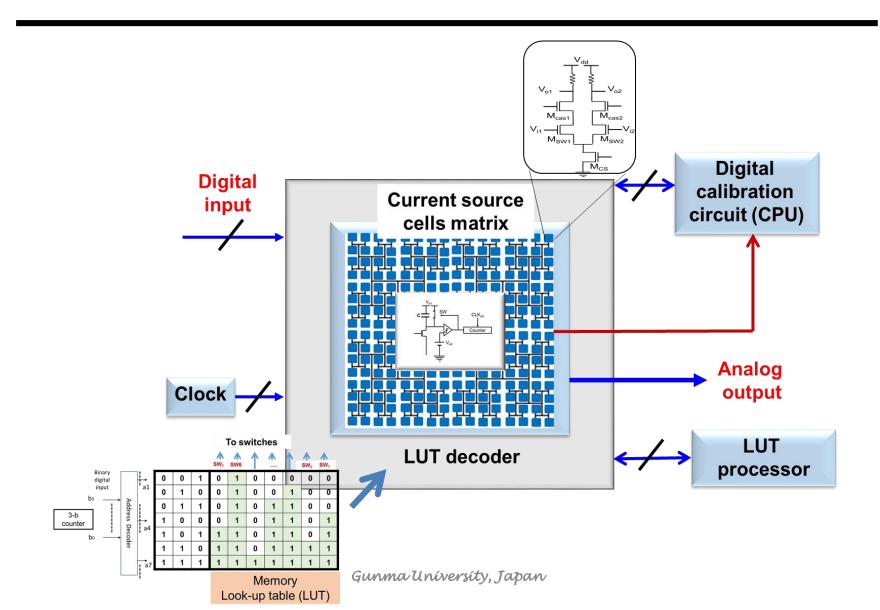

## Look Up Table-based Decoder

For conventional unary DAC

For proposed half-unary DAC

#### Whole DAC Block Diagram

# Outline

- Introduction

- Problem Statement

- Proposed Techniques

- Half-Unary Current-Steering DAC

- Outlier Elimination

- Current Source Sorting

- Circuit

- Layout

- Simulation Result

- Conclusion

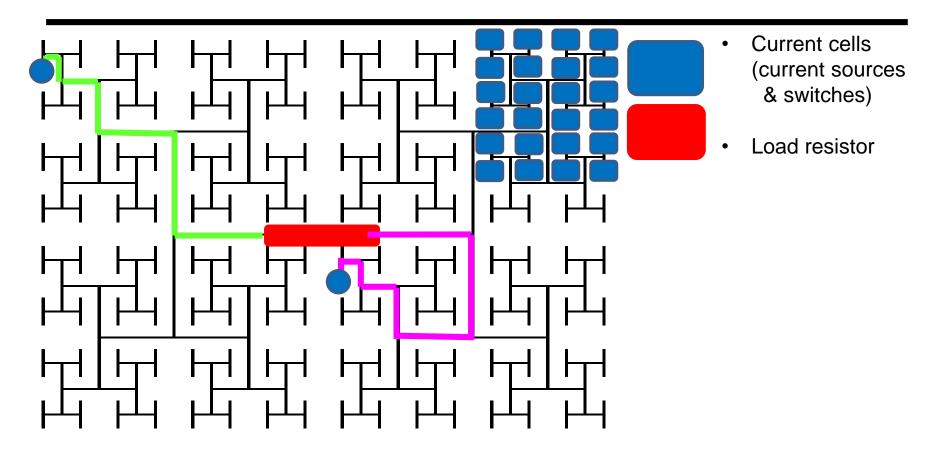

## Layout of Current Cells

For every cell, equal length of interconnection to load resistor. Minimum timing skew ☺!!!

#### Floor Plan of Whole DAC

# Outline

- Introduction

- Problem Statement

- Proposed Techniques

- Half-Unary Current-Steering DAC

- Outlier Elimination

- Current Source Sorting

- Circuit

- Layout

- <u>Simulation Result</u>

- Conclusion

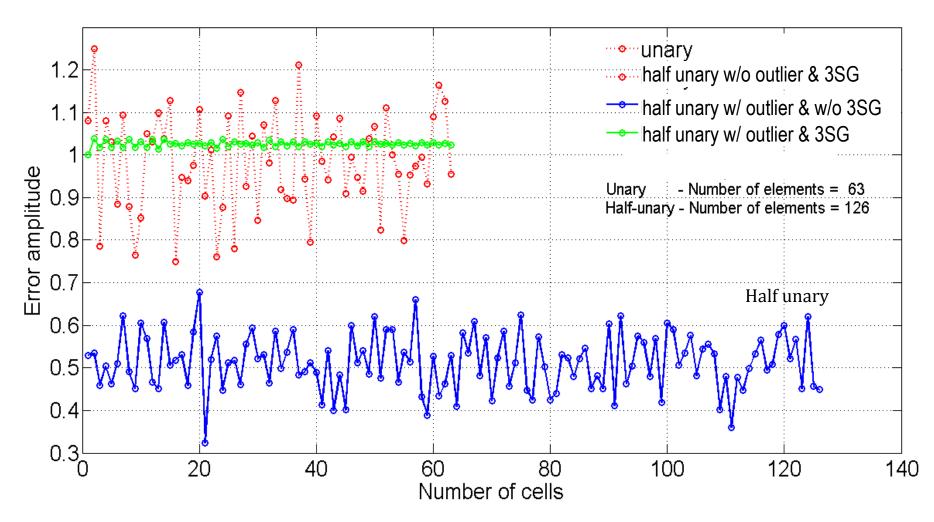

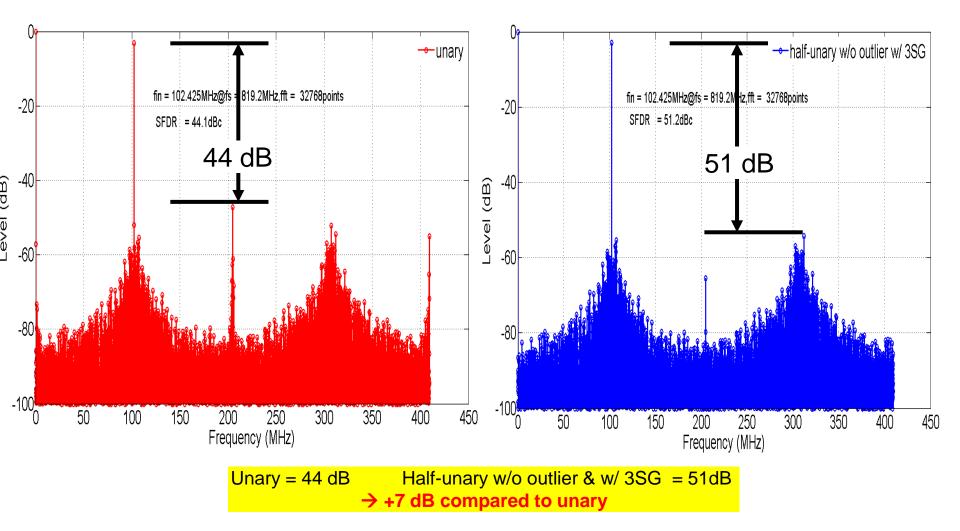

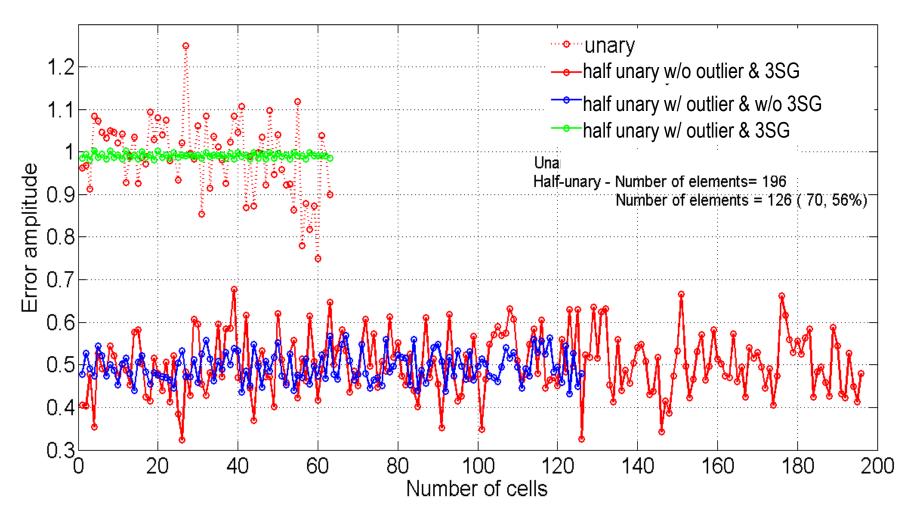

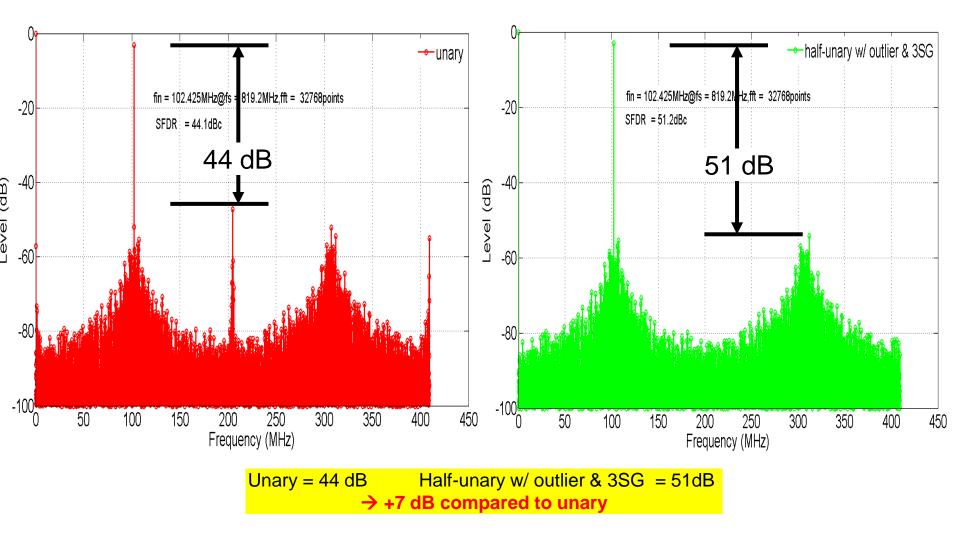

### **MATLAB** simulation

- Case of unary DAC

- Case of half-unary w/o additional current sources

- Case of half-unary w/ additional current sources

- Simulation condition

Fin = 102.4MHz, Fs = 819.2MHz fft = 32768 point Error range =  $[-0.25 \sim 0.25]$ Unary = 63 & 100 Half-unary = 126 & 196 Ideal SFDR = 51.3 dB

## Simulation result Error distribution w/o outlier

## Simulation result (half-unary w/o outlier w/ 3SG)

## Simulation result Error distribution w/ outlier

## Simulation result (half-unary w/ outlier & 3SG)

#### Summary

#### Simulation condition

Fin = 102.4MHz, Fs = 819.2MHz fft = 32768 point Error range = [-0.25 ~0.25] Unary = 63 Half-unary = 126 & 196

| Architecture               | SFDR, dBc<br>Ideal = 51.3 dB | Compared to average<br>Compared to unary |

|----------------------------|------------------------------|------------------------------------------|

| Unary                      | 45 dB                        | -                                        |

| Half-unary +<br>3SG        | <mark>46</mark> - 51 dB      | +5 dB<br>+ 6 dB                          |

| Half-unary+<br>outlier+3SG | <mark>49</mark> – 51 dB      | +2 dB<br>+6 dB                           |

## **Calibration Technique Comparison**

| Technique                                            | Advantages                                                                                                                                  | Drawbacks                                                                     |

|------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|

| Self calibration<br>[JSSC 2003]<br>[14-b 100MHz] [1] | <ul> <li>High precision calibration</li> </ul>                                                                                              | <ul> <li>Require high precision<br/>calibration ADC</li> </ul>                |

| SSPA<br>[JSSC 2007]<br>[14-b 200MHz] [2]             | <ul> <li>Minimum additional<br/>analog &amp; digital circuit</li> <li>Defect current source<br/>replacement</li> <li>Improve INL</li> </ul> | <ul> <li>No DNL improvement</li> <li>Analog<br/>current comparator</li> </ul> |

| Complete-folding<br>[ISCAS 2010]<br>[14-b ] [3]      | <ul> <li>Minimum additional<br/>analog &amp; digital circuit</li> <li>Improve INL &amp; DNL</li> <li>Low voltage</li> </ul>                 | <ul> <li>Analog<br/>current comparator</li> </ul>                             |

| This work                                            | <ul><li>Digital centric</li><li>More INL improvement</li></ul>                                                                              | Twice or more current cells                                                   |

# Outline

- Introduction

- Problem Statement

- Proposed Techniques

- Half-Unary Current-Steering DAC

- Outlier Elimination

- Current Source Sorting

- Circuit

- Layout

- Simulation Result

- <u>Conclusion</u>

### Conclusion

- High SFDR current-steering DAC for communication application with fine digital CMOS

- For DAC static linearity improvement

- 1 Half-unary DAC architecture

- ② Current source outlier elimination

- 3 3-stage sort & group algorithm for current sources

- Performed MATLAB simulation

- For DAC dynamic linearity improvement

- Well-balanced layout of current cells for interconnection R, C skew minimization.

#### Reference

<u>Calibration</u> (sort & group)

- [1] Y. Cong and R. Geiger, "A 1.5-V 14-bit 100-MS/s self-calibrated DAC," *IEEE J. Solid-State Circuits*, vol. 38, pp. 2051-2060, Dec. 2003.

- [2] T. Chen and G. Gielen, "A 14-bit 200-MHz current-steering DAC with switchingsequence post-adjustment calibration," *IEEE J. Solid-state Circuits*, vol. 42, No. 11, pp. 2386-2394, Nov. 2007. (SSPA)

- [3] T. Zeng and D. Chen, "New Calibration Technique for Current-Steering DACs", *Int. Symposium on Circuits Syst. (ISCAS),* pp. 573-576, 2010. (CF)

Switching sequence

- [4] T. Miki, Y. Nakamura, M. Nakaya, S. Asai, Y. Akasaka, and Y. Horiba, "An 80-MHz 8-bit CMOS D/A converter," *IEEE J. Solid-State Circuits*, vol. SSC-21, no. 12, pp. 983–988, Dec. 1986.

- [5] Y. Cong and R. L. Geiger, "Switching sequence optimization for gradient error compensation in thermometer-decoded DAC arrays," *IEEE Trans. Circuits Syst. II, Analog Digit. Signal Process.*, Vol. 47, No. 7, pp. 585–595, Jul. 2000.

- [6] K. C. Kuo and C. W. Wu, "Switching Sequence for Linear Gradient Error Compensation in the DAC Design", *IEEE Trans. Circuits Syst. II: Express Briefs*, Vol. 58, No. 8, pp. 502-506, Aug. 2011.

Thank you very much for your kindly attention

J&A

#### Presentation:

Page 36:

Q: Why are you include the measurement circuit? Is it will increase another mismatch from the measurement circuit itself?

A : Measurement circuit is used to measure error of each current sources. It is digital implementation, so I don't think that it will produces another error.

Q: Did you believe that your measurement circuit is accurate enough to measure such a current with the small value?

A:Yes. Because our measurement circuit use counter that realize in digital circuit.

### Q&A

#### Kenichi Okada sensei, Tokyo Institute Tech, Univ

<u>Page 49:</u>

Q: Why are you need calibration? DAC with the resolution less than 10 bit is not necessary to calibrate.

A: Actually, I plan these research to imply in segmented DAC as a MSB with resolution more than 10 bits.

Q:Did you think that current source is the main problem of the DAC? A: Yes.

Advice: Actually, current source is not a main problem but the mismatch is related to current which is determined by the length L & width W of the current source.

## Q&A

Kenichi Okada sensei, Tokyo Institute Tech, Univ

<u>Page 49:</u>

Q: What is assumption that you did in this analysis? What kind of error distribution? How about the standard deviation?

A: I used the random distribution but I don't really know about the standard deviation (show equation that being used)

Advice: If you used the flat distribution error, it will be a strange result. Page10:

Q: Why you said that binary DAC has small chip area compared to unary?

A: I think, it is due to the number of current sources.

Advice: Binary & unary has almost the same of current source chip area but the different is L & W.

J&A

Poster session:

Q: Why you don't use another algorithm such as DEM because it is more easy and require more less hardware implementation?A: Before this, I had used DEM method such DWA & OES but I thought that by using such algorithm it can only be used for certain error type.By using measurement circuit, I can obtained more accurate error value.

Q: How long the calibration time?

A: I don't know but that why calibration did in calibration mode. May be once during manufacturing.

Q:What the clock speed that you want to use for your calibration circuit?

A: I still don't think about that.

#### Q&A

Q: What is the SFDR means? How to relate between nonlinearity and SFDR ?

- Q: What the meaning of 3-stages sort & group?

- A: First sorting for combining the current source while 2<sup>nd</sup> & 3<sup>rd</sup> for switching sequence arrangement.