# 剰余系を用いた タイミング測定用回路の検討

李从兵(群馬大学) 加藤健太郎(鶴岡高専) 王俊善小林春夫(群馬大学)

Supported by STARC

## 研究背景

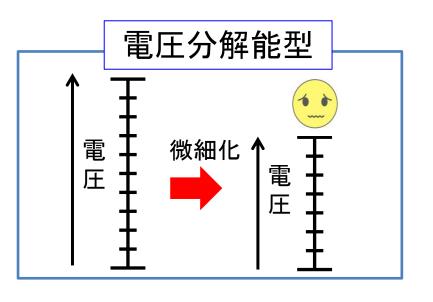

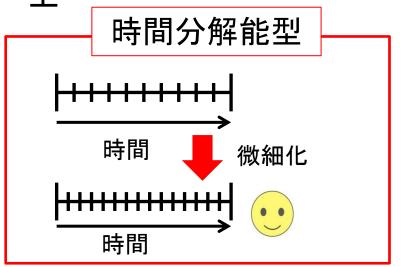

微細化CMOS LSI

電源電圧の低下 動作スイッチングスピードの向 上

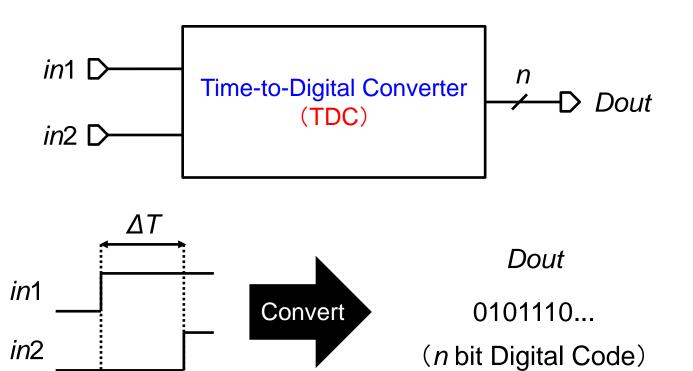

TDC(Time-to-Digital Converter)は2つのデジタル信号の時間差をデジタル値に変換

微細化CMOS LSIにおいて、TDCは時間領域アナログ回路のカギとなる

(センサ回路, All-Digital PLL,ADC,変調回路等)

## タイムデジタイザ回路

2つのディジタル信号間の時間差 ATをディジタル値に変換

出力のディジタル値よりATを測定可能

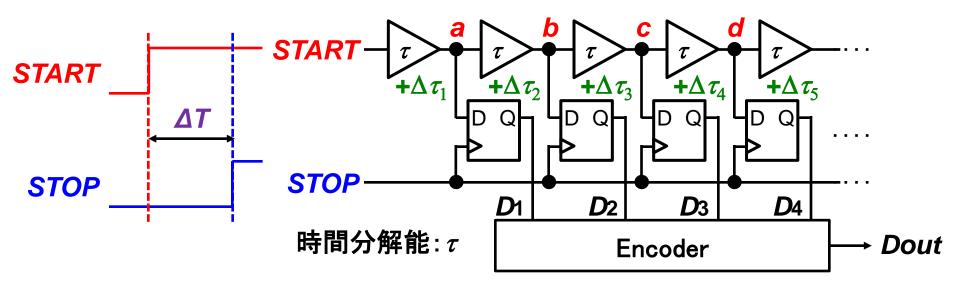

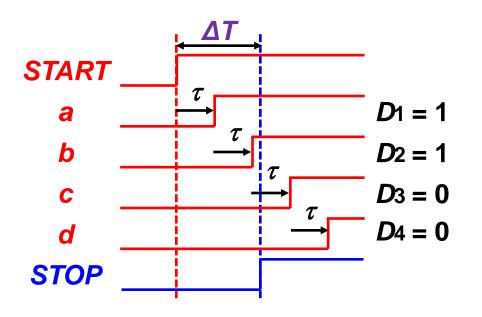

## フラッシュ型 TDCの構成と動作

- ▲T の大きさに比例したデジタル値 Dout を出力

- $lacksymbol{lack}$  時間分解能 au

高エネルギー加速器研究機構 素粒子原子核研究所 新井康夫氏による発明

## フラッシュ型TDCの回路規模の問題

START とSTOP の立ち上がりエッジ間の時間差 **ΔT** 測定範囲 0 < **ΔT** < N τ 時間分解能 τ

N = 1001 (千一)のとき フラッシュ型TDC では大きな回路規模、大きな消費電力

提案する剰余系TDC 1001= 7x11x13 同じ測定範囲、時間分解能で 7+11+13=31 個の 遅延セル、フリップフロップで実現できる

## 研究の目的

#### 時間測定回路TDC

- LSIテストシステムのキーコンポーネント

- 時間信号であることを利用

- → "剰余"が容易に得られる

- 剰余系を利用すると フラッシュ型TDCに比べ、同等性能で 小回路規模・低消費電力TDCが 実現できる可能性あり

剰余系TDC回路を検討する

# 「孫子兵法(孫子算経)」と剰余系

中国の剰余定理(Chinese remainder theorem)は 算術書『孫子算経』に由来する 整数の剰余に関する定理。 孫子の定理とも呼ばれる。

#### 『孫子算経』には

「3で割ると2余り、5で割ると3余り、7で割ると2余る数は何か」 という問題とその解法が書かれている。 中国の剰余定理は、この問題を他の整数についても 適用できるように一般化したもの。

## 剰余系の例

基数 2,3,5 互いに素

N=2x3x5 = 30

0からN-1(=29) までの整数の一つを k

a: kを2 で割った余り a= mod2 (k)

b: k を3で割った余り b= mod3(k)

c: k を5 で割った余り c= mod5(k)

kと (a, b, c) の組は1対1に対応する。

kを (a, b, c)で表現 **■**

剰余表現

| 「京文学」 | 「京

中国人の剰余定理 (Chinese Remainder Theorem) (a, b, c) から kを求めるアルゴリズム

#### 剰余系の例

基数 2, 3, 5 互いに素

N=2x3x5 = 30

0からN-1(=29) までの整数の一つを k

a: kを2 で割った余り a= mod2 (k)

b: k を3で割った余り b= mod3(k)

c: k を5 で割った余り c= mod5(k)

k と (a, b, c) の組は1対1に対応する。 k を (a, b, c) で表現 → 剰余表現

剰余定理 (Chinese Remainder Theorem) (a, b, c) から k を求めるアルゴリズム

自然数 k と剰余表現 (m1, m2, m3) は 1 対 1 対応

| mı | m2 | m3 | k  |  |

|----|----|----|----|--|

| 0  | 0  | 0  | 0  |  |

| 1  | 1  | 1  | 1  |  |

| 0  | 2  | 2  | 2  |  |

| 1  | 0  | 3  | 3  |  |

| 0  | 1  | 4  | 4  |  |

| 1  | 2  | 0  | 5  |  |

| 0  | 0  | 1  | 6  |  |

| 1  | 1  | 2  | 7  |  |

| 0  | 2  | 3  | 8  |  |

| 1  | 0  | 4  | 9  |  |

| 0  | 1  | 0  | 10 |  |

| 1  | 2  | 1  | 11 |  |

| 0  | 0  | 2  | 12 |  |

| 1  | 1  | 3  | 13 |  |

| 0  | 2  | 4  | 14 |  |

| mı | m2 | m3 | k  |  |

|----|----|----|----|--|

| 1  | 0  | 0  | 15 |  |

| 0  | 1  | 1  | 16 |  |

| 1  | 2  | 2  | 17 |  |

| 0  | 0  | 3  | 18 |  |

| 1  | 1  | 4  | 19 |  |

| 0  | 2  | 0  | 20 |  |

| 1  | 0  | 1  | 21 |  |

| 0  | 1  | 2  | 22 |  |

| 1  | 2  | 3  | 23 |  |

| 0  | 0  | 4  | 24 |  |

| 1  | 1  | 0  | 25 |  |

| 0  | 2  | 1  | 26 |  |

| 1  | 0  | 2  | 27 |  |

| 0  | 1  | 3  | 28 |  |

| 1  | 2  | 4  | 29 |  |

剰余定理は、

この問題を他の整数についても適用できるように一般化したもの。

#### 剰余系TDCの原理

三つのリング発振回路(遅延2t, 3t, 5t)を利用し、 発振している状態から経過時間Tの測定を行う。

Tを2τで割った余りはa

Tを3τで割った余りはb

Tを5τで割った余りはc

Kを計算する

$T = k \times \tau$

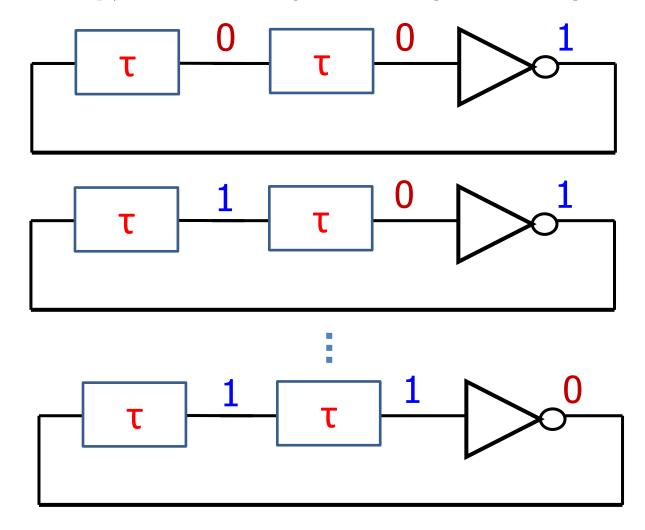

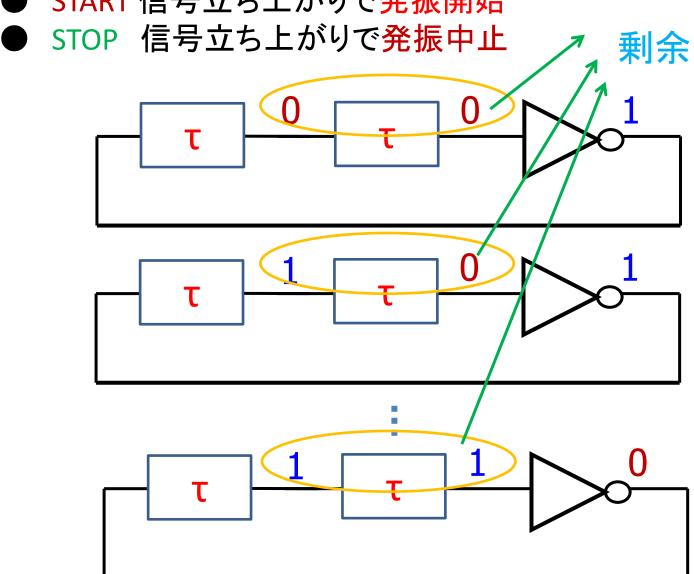

## リング発振回路で剰余が容易に得られる

考察 TDCでは取り扱う入力信号が時間信号なので リング発振回路構成により剰余が容易に得られる。 電圧信号を入力とするADCでは剰余を得るのは簡単ではない。11

#### リング発振回路で剰余を得る

● START 信号立ち上がりで発振開始

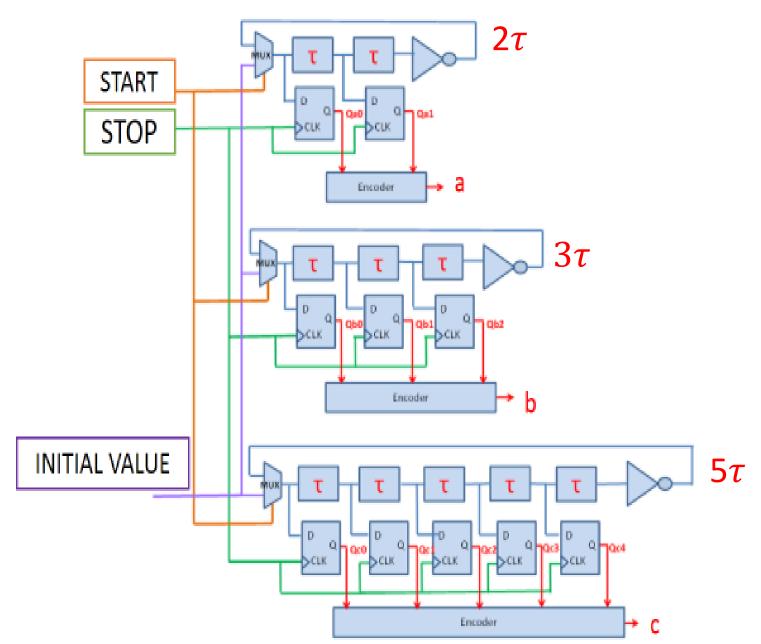

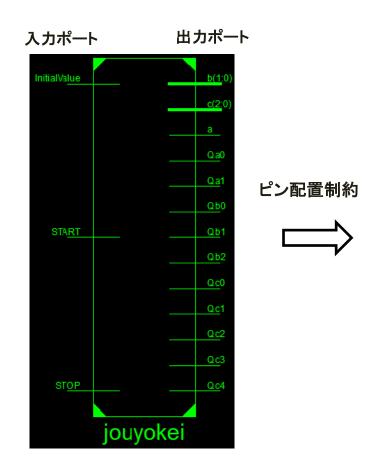

## 提案する剰余系TDCの回路図

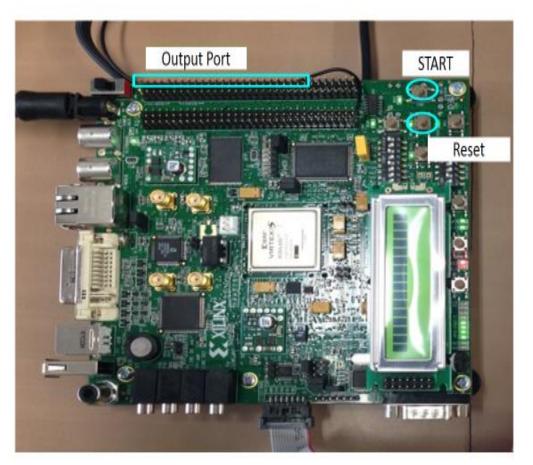

## FPGA実装(1/4)

STOPポートの入力: 100MHz FPGA クロック

Buffer\_CLKポートの入力: 33MHz FPGA クロック(バッファの

遅延  $\tau = 30.30 \text{ns}$ )

Xilinx社 Virtex5 XC5VLX50-FFG6764

## FPGA実装(2/4)

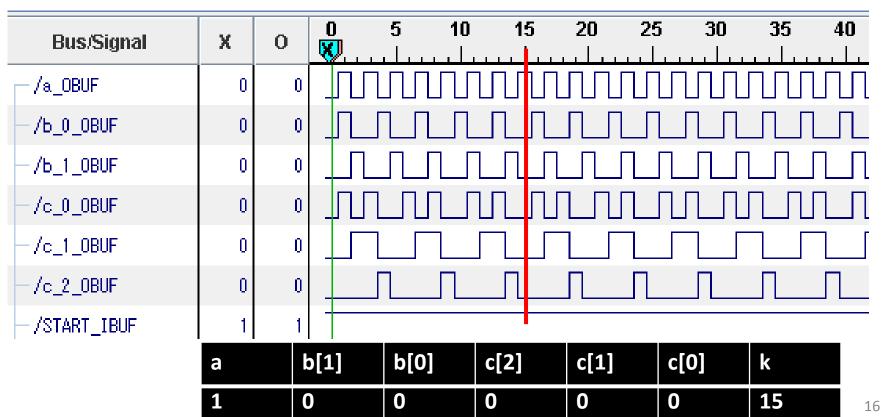

#### FPGA実装(3/5)

三つのTDC回路(遅延は2クロック周期、3クロック周期、5クロック周期)を利用

- Tを2クロック周期で割った余りはa

- Tを3クロック周期で割った余りはb

- Tを5クロック周期で割った余りはc

- ⇒剰余定理でT=kXクロック周期

#### FPGA実装(3/4)

ASCII データ変換

START とSTOPの時間差 = k x バッファ遅延(30.30ns)

| Sample<br>in<br>Window | Elapsed<br>Time(ns) | а | b[0] | b[1] | c[0] | c[1] | c[2] | k  |

|------------------------|---------------------|---|------|------|------|------|------|----|

| 0                      | 0.00                | 0 | 0    | 0    | 0    | 0    | 0    | 0  |

| 3                      | 30.30               | 1 | 1    | 0    | 1    | 0    | 0    | 1  |

| 6                      | 60.60               | 0 | 0    | 1    | 0    | 1    | 0    | 2  |

| 9                      | 90.90               | 1 | 0    | 0    | 1    | 1    | 0    | 3  |

| 12                     | 121.20              | 0 | 1    | 0    | 0    | 0    | 1    | 4  |

| 15                     | 151.50              | 1 | 0    | 1    | 0    | 0    | 0    | 5  |

| 18                     | 181.80              | 0 | 0    | 0    | 1    | 0    | 0    | 6  |

| 21                     | 212.10              | 1 | 1    | 0    | 0    | 1    | 0    | 7  |

| 24                     | 242.40              | 0 | 0    | 1    | 1    | 1    | 0    | 8  |

| 27                     | 272.70              | 1 | 0    | 0    | 0    | 0    | 1    | 9  |

| 30                     | 303.00              | 0 | 1    | 0    | 0    | 0    | 0    | 10 |

| 33                     | 333.30              | 1 | 0    | 1    | 1    | 0    | 0    | 11 |

| 36                     | 363.60              | 0 | 0    | 0    | 0    | 1    | 0    | 12 |

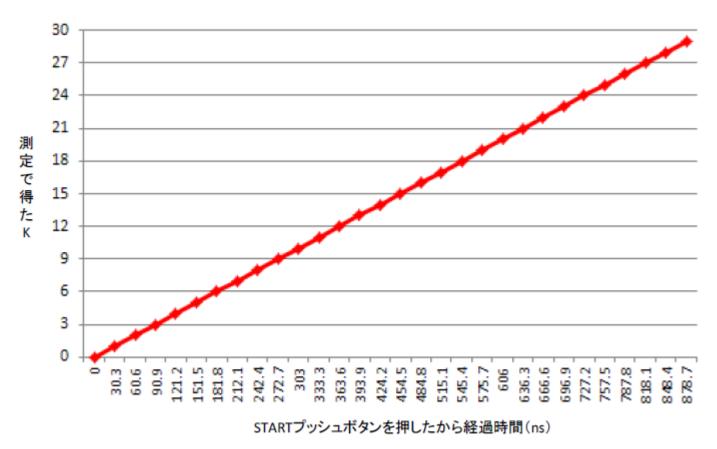

#### FPGA実装(4/4)

#### 剰余系TDC回路はFPGAで実現できることが示された。

経過時間 VS. 測定で得た k

#### まとめと今後の課題

- 提案剰余系TDC回路は時間測定が可能であることを確認し、 FPGA で実現できることを示した。

- バッファの個数とリング発振回路の個数を増減すると、 提案TDC 回路は他の剰余数系にも適用できる。他の剰余数系のTDC 回路もFPGA で実現可能である。

- 提案TDC回路で、使用した遅延バッファとフリップフロップの数は10個。

同等性能フラッシュ型TDC回路では、29個である。

剰余系を利用したTDC回路は、回路面積、消費電力が低減できる。

- 今後の課題:

- 三つのチャネルTDC 間の特性ばらつきの影響の検討

- 大きな誤差を生じる可能性があるかどうか、

- 冗長構成で対応可能かどうか

- 一般論として、現状産業界では

- アナログBISTは実用化が限定。

- アナログBOST は現実的選択。

Analog BIST or BOST? That is the question.

Hamlet

集積回路分野の研究者 フルカスタムIC重視、(アナログ)FPGAに関心少ない傾向

(アナログ)FPGAは「破壊的イノベーション」になる(?)

ご清聴ありがとうございます

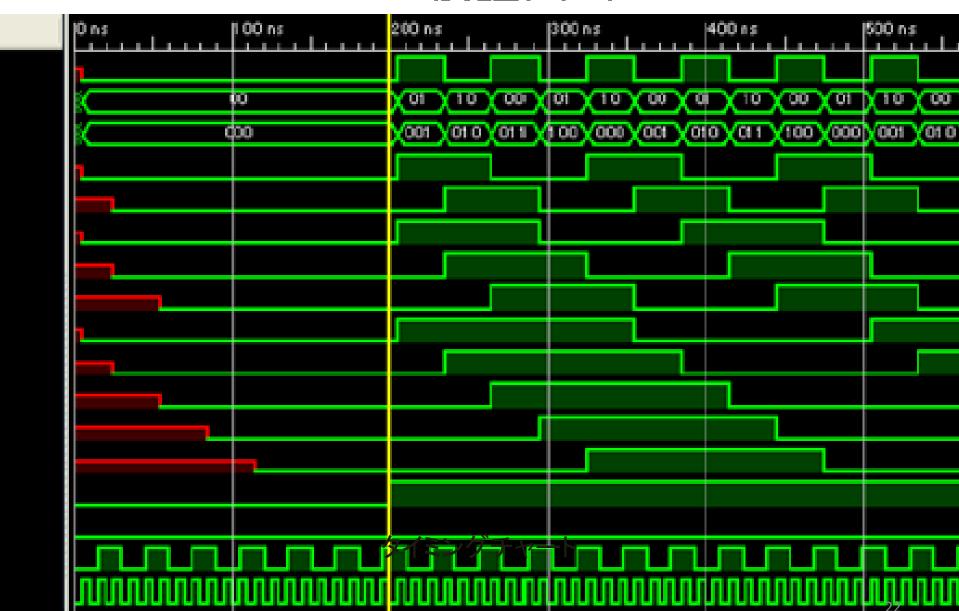

## RTL検証(1/2)

# RTL検証(2/2)

| STOP 信号<br>の値(ns) | 発振から<br>経過時間 | а | b  | O   | 計算<br>した k |

|-------------------|--------------|---|----|-----|------------|

| 200               | 0 x 30.30ns  | 0 | 00 | 000 | 0          |

| 230.30            | 1 x 30.30ns  | 1 | 01 | 001 | 1          |

| 260.60            | 2 x 30.30ns  | 0 | 10 | 010 | 2          |

| 290.90            | 3 x 30.30ns  | 1 | 00 | 011 | 3          |

| 321.20            | 4 x 30.30ns  | 0 | 01 | 100 | 4          |

| 351.50            | 5 x 30.30ns  | 1 | 10 | 000 | 5          |

| 381.80            | 6 x 30.30ns  | 0 | 00 | 001 | 6          |

| 412.10            | 7 x 30.30ns  | 1 | 01 | 010 | 7          |

| 442.40            | 8 x 30.30ns  | 0 | 10 | 011 | 8          |

| 472.70            | 9 x 30.30ns  | 1 | 00 | 100 | 9          |

| 503.00            | 10 x 30.30ns | 0 | 01 | 000 | 10         |

| 533.30            | 11 x 30.30ns | 1 | 10 | 001 | 11         |

| 563.60            | 12 x 30.30ns | 0 | 00 | 010 | 12         |

| 593.90            | 13 x 30.30ns | 1 | 01 | 011 | 13         |

| 624.20            | 14 x 30.30ns | 0 | 10 | 100 | 14         |

| 654.50            | 15 x 30.30ns | 1 | 00 | 000 | 15         |

| 684.80            | 16 x 30.30ns | 0 | 01 | 001 | 16         |

| 715.10            | 17 x 30.30ns | 1 | 10 | 010 | 17         |

| 745.40            | 18 x 30.30ns | 0 | 00 | 011 | 18         |

| 775.70            | 19 x 30.30ns | 1 | 01 | 100 | 19         |

| 806.00            | 20 x 30.30ns | 0 | 10 | 000 | 20         |

| 836.30            | 21 x 30.30ns | 1 | 00 | 001 | 21         |

| 866.60            | 22 x 30.30ns | 0 | 01 | 010 | 22         |

| 896.90            | 23 x 30.30ns | 1 | 10 | 011 | 23         |

| 927.20            | 24 x 30.30ns | 0 | 00 | 100 | 24         |

| 957.50            | 25 x 30.30ns | 1 | 01 | 000 | 25         |

| 987.80            | 26 x 30.30ns | 0 | 10 | 001 | 26         |

| 1018.10           | 27 x 30.30ns | 1 | 00 | 010 | 27         |

| 1048.40           | 28 x 30.30ns | 0 | 01 | 011 | 28         |

| 1078.70           | 29 x 30.30ns | 1 | 10 | 100 | 29         |