1<sup>st</sup> International Symposium of Gunma University Medical Innovation and 6<sup>th</sup> International Conference on Advanced Micro - Device Engineering (GUMI&AMDE 2014)

# **Linearity Improvement Algorithm for Current-Steering DAC Based on 3-Stage Sorting of Half-Unary Current Sources**

Shaiful Nizam Mohyar and Haruo Kobayashi

Division of Electronics & Informatics, Graduate School of Science & Technology, Gunma University Kiryu, Gunma 376-8515 Japan, email:K\_haruo@el.gunma-u.ac.jp

## Introduction

#### Background

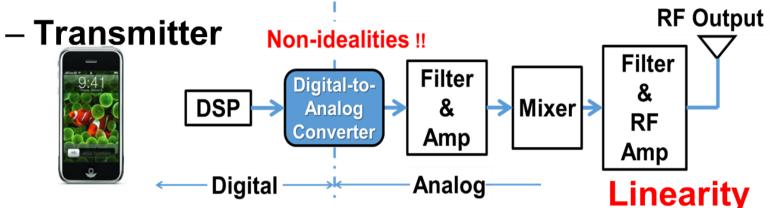

- Telecommunication devices

- Mobile phones, wireless modems & avionics

- High-speed, high-accuracy digital-to-analog converter (DAC)

#### Problem

#### Interference !

#### Objective

- Objective

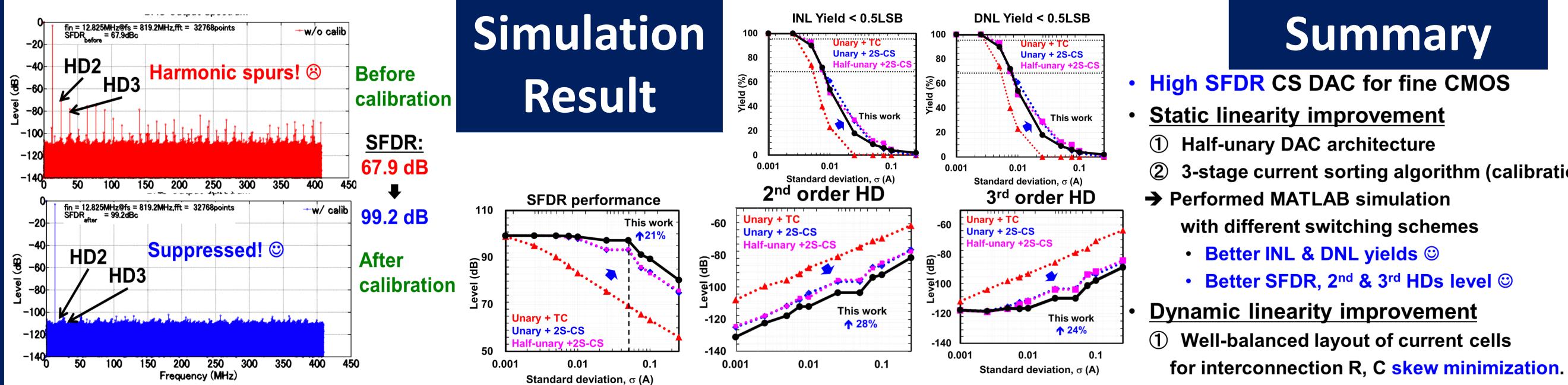

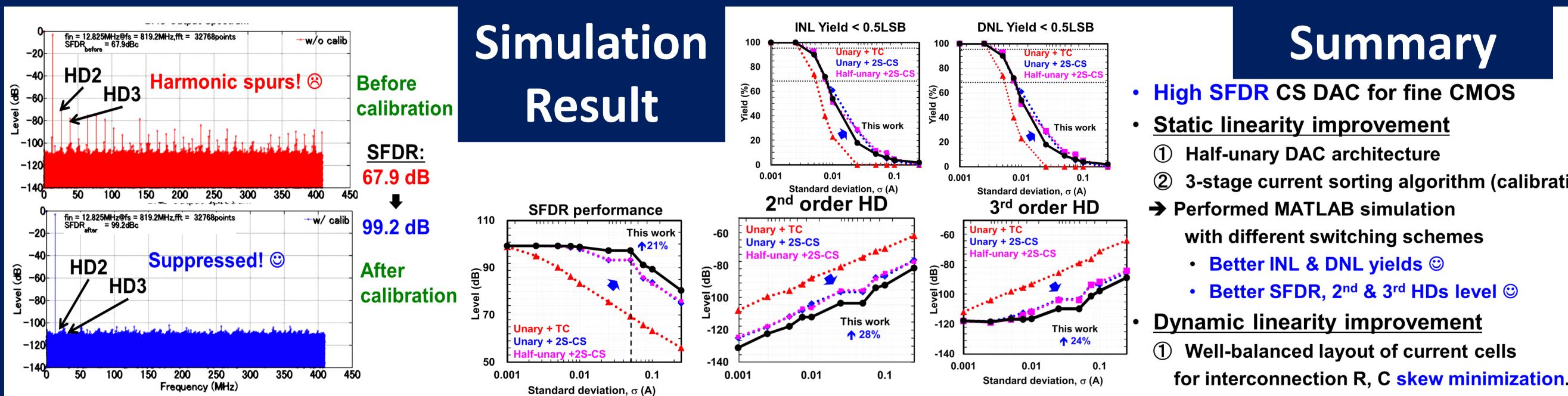

- High SFDR current-steering DAC for communication

- Proposed method

- Current source mismatch effect reduction

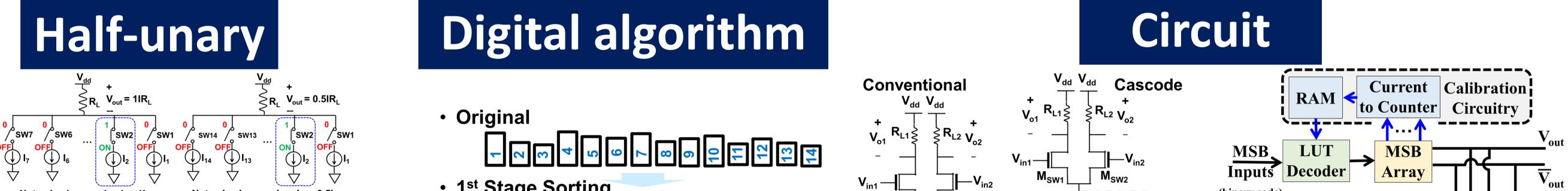

- Half-unary DAC architecture (1)

- **Current source sorting algorithm** (2)

- → Static linearity improvement

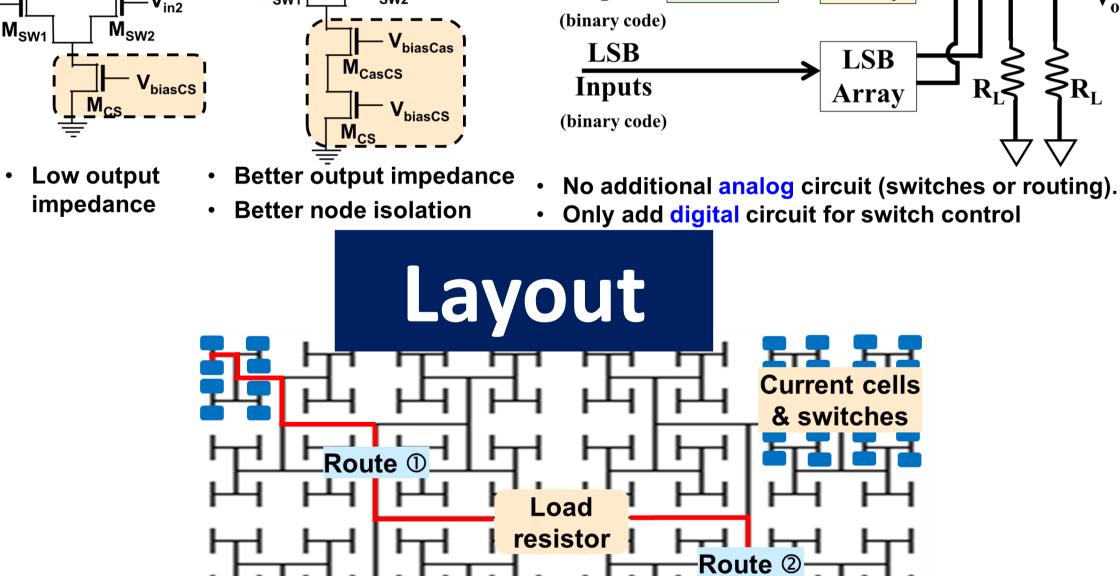

- Layout strategy

- ① Clock-tree-like layout

- of current sources & switches

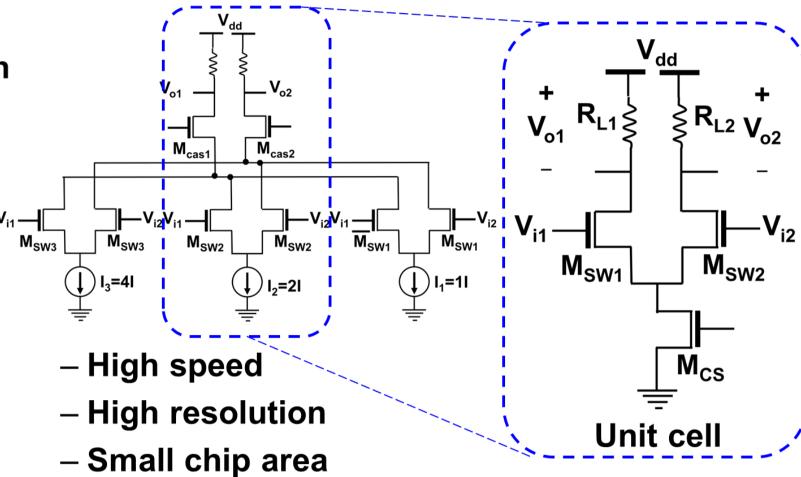

## **Current-steering DAC**

degradation!!! ⊗

→ Dynamic linearity improvement

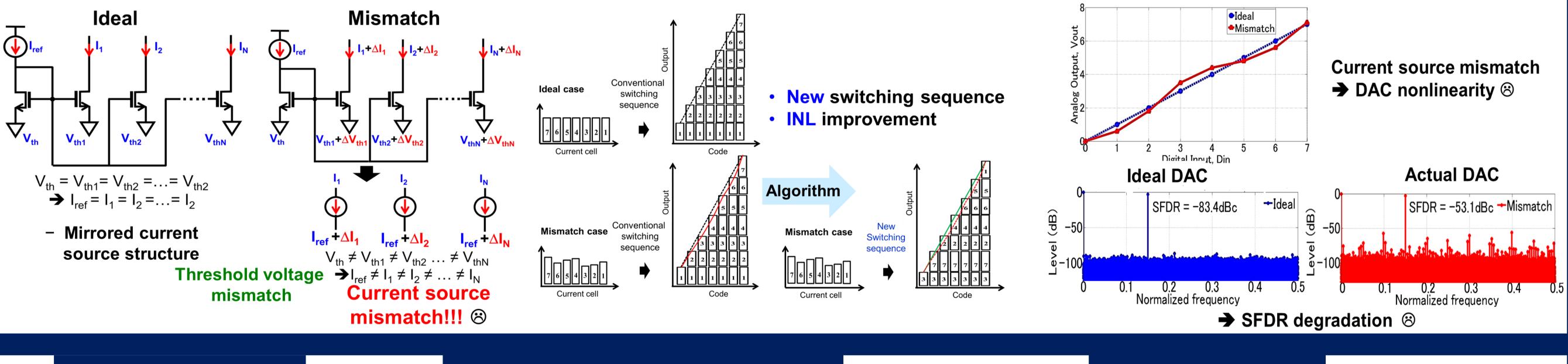

#### Mismatch

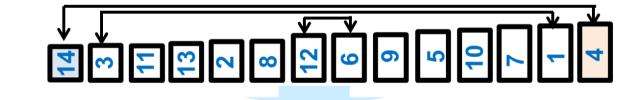

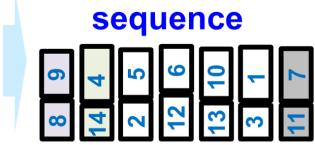

### **Switching Sequences**

## Nonlinearity

M<sub>SW1</sub>

| Note : $I_1 = I_2 = = I_6 = I_7 =$ | : 11              | Note : $I_1 = I_2 = = I_{13} = I_{14} = 0.5I$ |  |  |

|------------------------------------|-------------------|-----------------------------------------------|--|--|

|                                    | Unary             | Half-unary                                    |  |  |

| Number of CS                       | 2 <sup>N</sup> -1 | 2(2 <sup>N</sup> -1)                          |  |  |

| Current value                      | - 1               | 0.51                                          |  |  |

N : number of bit

Initial condition B<sub>in</sub> = 000 (Binary code)  $V_{out} = 0$ (Decoded binary code) / 0 0 0 0 / sw4 / sw3 / sw2 / sw1 / sw13 / sw12 / sw11

| $ \frac{\text{Clock 1:}}{B_{in} = 001} \\ \downarrow \\ H_{in} = 000000000011 \qquad \frac{V_{dd}}{\leq} + \\ R_{L} \qquad V_{out} = 2(0.5I)R_{L} $                                                                                                                                                                                                                                                 | $\frac{\text{Clock 2:}}{B_{\text{in}} = 010} \\ \downarrow \\ H_{\text{in}} = 0000000001111 \qquad \frac{V_{\text{dd}}}{R_{\text{l}}} + \\ R_{\text{l}} \qquad V_{\text{out}} = 4(0.51)R_{\text{L}}$                                                                                                                                                                                                                                                                                                          |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     0     0     0     0     1     1       /SW14 / SW13 / SW12 / SW11     /SW4 / SW3 [SW2 ] SW1       OFF     OFF     OFF     OFF     ON                                                                                                                                                                                                                                                           | 0 0 0 0 1 1 1 1 1<br>/SW14 / SW13 / SW12 / SW11 SW4 SW3 SW2 SW1<br>OFFL OFFL OFFL ON ON ON ON                                                                                                                                                                                                                                                                                                                                                                                                                 |

| $ \begin{array}{c} ( \downarrow) I_{14} ( \downarrow) I_{13} ( \downarrow) I_{12} ( \downarrow) I_{11} \cdots ( \downarrow) I_4 ( \downarrow) I_3 ( \downarrow) I_2 ( \downarrow) I_1 \\ ( \downarrow) \downarrow $ | $ \begin{array}{c} \bigoplus_{l_{14}} \bigoplus_{l_{13}} \bigoplus_{l_{12}} \bigoplus_{l_{11}} \cdots \bigoplus_{l_{4}} \bigoplus_{l_{3}} \bigoplus_{l_{2}} \bigoplus_{l_{1}} \\ \bigtriangledown & \bigtriangledown & \bigtriangledown & \bigtriangledown & \checkmark & \bigtriangledown & \bigtriangledown \\ \end{array} $ $ \begin{array}{c} \text{Note} : I_{1} = I_{2} = \dots = I_{13} = I_{14} = 0.5I \\ \hline \\ $ |

| $B_{in} = 110$ $= 0011111111111111111111111111111111111$                                                                                                                                                                                                                                                                                                                                            | $\begin{array}{c} \underline{UOCK \ 7.} \\ B_{in} = 111 \\ \blacksquare \\ H_{in} = 1111111111111 \\ H_{in} = 1111111111111 \\ \hline \\ R_{L} \\ V_{out} = 14(0.51)R_{L} \end{array}$                                                                                                                                                                                                                                                                                                                        |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                               | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                               | $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| - | • | age | 00 | <br>'Y |  |

|---|---|-----|----|--------|--|

|   |   |     |    |        |  |

3<sup>rd</sup> Stage

Sorting

0

| 4  | -              | 7  | 10 | 5 | 6        | 12 6 |

|----|----------------|----|----|---|----------|------|

| 14 | <mark>3</mark> | 11 | 13 | 2 | $\infty$ | 12   |

2<sup>nd</sup> Stage Grouping • 2<sup>nd</sup> Stage Sorting 3<sup>rd</sup> Stage Disassociating Grouping

Isometric of interconnection to load resistor →Minimum timing skew ©!!!

**Clock tree-based**

layout

- - 3-stage current sorting algorithm (calibration)