# 黄金分割法を用いた SAR ADC 冗長設計

小林 佑太朗\* 小林 春夫(群馬大学)

ADC Redundancy Design Using Golden Search Method

Yutaro Kobayashi\*, Haruo Kobayashi (Gunma University)

キーワード: 黄金分割法, ADC, 冗長性, 校正, フィボナッチ数列, 黄金比 (Keywords: Golden Section search, ADC, redundancy, calibration, Fibonacci sequence, golden ratio)

#### 1. はじめに

車載用エレクトロニクス技術は自動車に付加価値や競争力を生む一つの方法として注目を集めている。AD変換器には数多くの方式が存在するが車載用のマイコンと組み合わせて使用されるAD変換器には分解能、消費電力、チップ面積の面で優れた逐次比較型ADCが広く使用される。しかし車載用エレクトロニクスの発展に伴い、AD変換器への性能要求が厳しくなっている。

そこで筆者らはこの逐次比較型 ADC の高性能化を目指したアルゴリズム研究を行っている。本論文では単峰関数の極値を求めるアルゴリズムである"黄金探索法"を利用した逐次比較型 AD 変換器の設計方法を提案する。フィボナッチ数列を用いて空間的、時間的冗長設計をすることにより実現を検討し、車載用マイコンのための高信頼性化、高速化を目標とする。

## 2. 逐次比較型 ADC の構成と動作

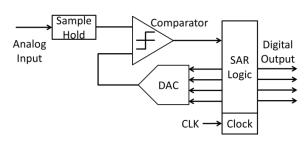

逐次比較型 AD 変換器 (SAR ADC) は天秤の原理を利用してアナログ値をディジタル値へ変換する方式である。図 1 に構成図を示す。SAR ADC はオペアンプを使用せず回路の大部分がディジタル回路で構成できるため、微細 CMOS での実現に適する。産業界で広く使用され、車載用マイコン、工業用制御装置などに利用される。他の方式の ADC と比べた際の特徴として高分解能・低消費電力・小チップ面積・中速が挙げられる[1]。

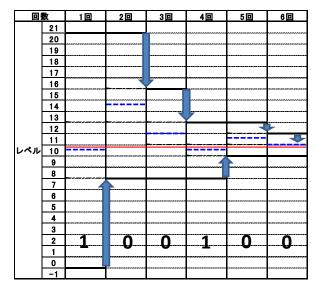

動作原理は、アナログ入力をサンプルホールド回路で保持し、コンパレータ(天秤)を用いて DAC 出力の比較電圧(重り)と比較する。二つの入力の比較結果から SAR ロジック回路によって 0 か 1 のディジタル出力を生成する。さらに結果に応じて比較電圧の大きさを SAR ロジック回路で変更、DAC でアナログ信号へ戻しまた比較する。これらの操作を繰り返してアナログ信号をディジタル信号へ変換する方式である。図 2 に 4bit (16 レベル)

の二進探索アルゴリズム逐次比較型 ADC の動作(入力が 10.7)の例を示す。図 2 で太線の部分が比較電圧の大きさであり、逐次比較を行っていくことで最終的にディジタル値 10 を得る。一般的な比較電圧の大きさは二進重みから構成される数字を使って比較しており、時間(ステップ数)的に無駄がなく、効率は一番良いとされる。

しかしながら現実には参照電圧の揺れ、DAC 出力の有限整定時間などの原因により、比較の際に出力を誤ってしまう可能性がある。そして二進重みを用いる二進探索アルゴリズムでは一度判定を誤ると、その二進の性質(十進数と二進数が1対1に対応する)から正しい出力を得ることはできない。

そこで本論文ではこのような誤りを自己校正する一つの方法として時間冗長性を用いた非二進探索アルゴリズムを利用した SAR ADC を検討した。

#### 3. 黄金分割法について

SAR ADC に非二進型探索アルゴリズムを用いることは時間の冗長性を使うことである[1,2,3]。すなわち余分に時間を利用して、コンパレータの判定回数(ステップ数)を増やすことで十進数に対応する出力コードを増加させて判定誤りを補正する。ここでは非二進探索アルゴリズムとして黄金分割法を考える。

図 1. 逐次比較近似型 ADC の構成図. Fig.1 Block diagram of an SAR ADC.

| 回数    |    | 1 | 2 | 3 | 4 |

|-------|----|---|---|---|---|

| 電圧算   |    | 8 | 4 | 2 | 1 |

|       | 15 |   |   |   |   |

|       | 14 |   |   |   |   |

|       | 13 |   |   |   |   |

|       | 12 |   |   |   |   |

|       | 11 |   |   |   |   |

|       | 10 |   |   |   |   |

| レベル   | 9  |   |   |   |   |

|       | 8  |   |   |   |   |

| יייטן | 7  |   |   |   |   |

|       | 6  |   |   |   |   |

|       | 5  |   |   |   |   |

|       | 4  |   |   |   |   |

|       | 3  |   |   |   |   |

|       | 2  | 1 | Ω | 1 | n |

|       | 1  | 4 | 0 | 4 | J |

|       | 0  |   |   |   |   |

図 2. 4-bit SAR ADC の二進探索アルゴリズム. Fig.2 Binary search algorithm of a 4bit SAR ADC.

## 3.1 黄金分割法

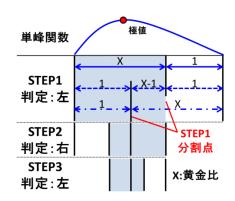

黄金分割法は、単峰関数の極値を求める際に用いられるアルゴリズムである。関数の極値が存在する区間を定めると、区間内の二点の関数値を比較することができれば、極値の存在する区間を縮小していくことで極値を求めることができる。区間を一定の比率で無限に分割する方法を考えると区間を X:1=1:X-1 すなわち  $X^2-X-1=0$  満たされるように分割する。この X は黄金比(=1.61803...)となるため、この極値探索アルゴリズムは黄金分割法と呼ばれる[4]。

黄金分割法の極値探索を図3に示す。図3において薄塗の部分が極値の存在範囲と判定さる。黄金分割法は一定の比率で区間を縮小するため収束性が約束され、測定回数が限られているとき最も小さい区間に縮小できることが証明されている。

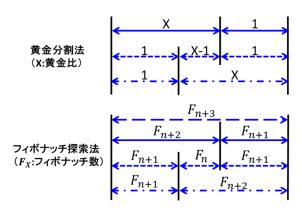

#### 3.2 フィボナッチ探索法

黄金分割法は整数区間を小数である黄金比で分割するために、一般に整数のみを扱う ADC と相性が悪い。そこで ADC 設計への応用にフィボナッチ探索法の適用を検討した。フィボナッチ数列とは以下の漸化式で定義される数列である(1202年にフィボナッチが発行した『算盤の書』(Liber Abaci) に記載された数列[5])。

$$F_0 = 0$$

$$F_1 = 1$$

$$F_{n+2} = F_n + F_{n+1}$$

初めの数項を計算すると以下の整数値となる。

0, 1, 1, 2, 3, 5, 8, 13, 21, 34, 55, 89, 144, 233… また隣り合う項の比率は以下に収束する(黄金比)。

$$\lim_{n \to \infty} \frac{F_n}{F_{n-1}} = 1.618033988749895$$

上記からフィボナッチ数列において隣り合う項の和が次の項になること、隣り合う項の比率が黄金比であることが知られている。

図 3. 黄金探索法の極値探索. Fig.3 Golden Section search algorithm.

図 4. 黄金探索法とフィボナッチ探索法. Fig.4 Golden Section search algorithm and Fibonacci search algorithm.

フィボナッチ探索法はこれらの性質を利用し、黄金分割をフィボナッチ数の並びによって置き換える。その様子を図4に示す。フィボナッチ数法は黄金分割法を整数で行う方法であり、黄金分割法を用いたADCの実現はフィボナッチ探索法を用いると容易に設計できると考えている。

#### 4. 黄金分割法を用いた SAR ADC

SAR ADC 設計に黄金分割法を利用するのは AD 変換の際にディジタル誤差補正とノイズ耐性向上を可能にするためである。黄金分割法のアルゴリズムでは二点の関数値を比較することで極値の存在する区間を縮小するが、SAR ADC に適用する場合はコンパレータによって直接的に極値の存在範囲を決定することができるため比較電圧は一つでよい。その比較電圧はノイズ耐性を高めるために二つの分割点の中心点を使用する。黄金分割を用いた 4bit の AD 変換の解探索を図 5 に示す(入力10.7)。図 5 において外側の二本の実線が解の存在可能範囲を表し、それらの内側にある二本の鎖線が分割点、分割点の中心にある破線が比較電圧である。

図 5. 黄金探索法を用いた 4-bit SAR ADC.

Fig. 5 Golden Section search algorithm of a 4bit SAR ADC.

動作は黄金分割法と同様となる。どちらの分割点で縮小するかをコンパレータが入力電圧と比較電圧の大きさを比較することにより決定し入力の存在可能区間を縮小する。この操作を繰り返すと入力存在可能区間は縮小されていく。フィボナッチ数の性質より最後は必ず整数の比較が行われディジタル値へ変換することができる。出力コードは高い分割点より小さいと判定したとき 0、低い分割点より大きいと判定したとき 1 とする。

図5は時間冗長性を利用してコンパレータ判定回数を増加させているため出力されるコードは二進コードよりもビット数の大きなものとなる。二進重みを用いるSAR ADCは一判定毎に極値存在区間を0.5倍に縮小する二分探索であるが、黄金分割法を用いたSAR ADCは一判定毎に区間を約0.618倍に縮小する黄金分割探索である。すなわち一回の判定で縮小できる範囲が二分探索と比較して小さいために相対的に収束速度が遅く、出力ビット数が増えるのである。出力ビット数が増加すると十進数とディジタルコードの対応が1対1ではなくなり一種類の入力に対し複数の表現方法を持つことになるため、前段でコード反転があったとしても違う種類のコードを出力することで正しい出力を得ることができる。これはディジタル誤差補正が可能であることを示す。

黄金分割法で出力されるコードは二進数ではなく出力の計算は各ディジタル値のフィボナッチ数重みの加算で表現される。MSB より i 番目 (i=1,2,3...) のディジタル値を d(i)、x 番目のフィボナッチ数を  $F_x$  とすると、N 桁のディジタルコードを持つ出力 Dout は以下の(1)式で表現される。

$$D_{out} = \sum_{i=1}^{N} d(i) F_{N+1-i} \qquad \cdots (1)$$

図 6. 黄金探索法 SAR ADC の DAC 構成. Fig.6 DAC structure of Golden Section search algorithm SAR ADC.

たとえば4bit 6step ADC の入力が10ならば(100100)、(100011)、(011100)、(011011)の出力コードの種類がある。これらの出力コードをルックアップテーブルなどで二進コードへ変換すれば最終結果を得られる。

さらに比較電圧を分割点間の中心に置くことで、判定電圧と縮小する範囲を別々にすることができるので入力のずれに対する耐性を高められる。一般的な SAR ADCでは範囲の決定と範囲の縮小を同じ点で行うため、入力電圧と比較電圧が近い値でノイズによって出力が反転してしまった場合は誤った方向へ範囲を縮小し、正しい値を得ることはできない。しかし黄金分割法を用いた SAR ADCでは入力電圧と比較電圧が近い値でノイズによって出力が反転してしまった場合も、比較電圧に近い値は入力存在可能区間として縮小するので問題にならない。このようにしてノイズ耐性の向上が可能である。

これらの考え方によりディジタル誤差補正とノイズ耐性向上の実現ができるために信頼性を向上させた SAR ADC を設計することができる。誤り耐性を向上させたことを利用して、不完全整定の考え方を適用することも可能である。すなわち、前段での DAC 出力が完全に整定するまで待たずに判定を行い、後段で補正することで一回の判定時間を削減し最終的な AD 変換速度を向上させることが可能である。

これらの考え方を適用することで、黄金分割法を用いた SAR ADC は二進アルゴリズムを用いた SAR ADC より速度と信頼性に優れた SAR ADC を実現できる可能性がある。

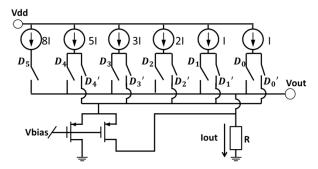

#### 5. 黄金分割法を用いた SAR ADC の実現

黄金分割法を用いた SAR ADC 回路の実現を考える。 動作は一般的な二進重み SAR ADC と同様に、入力電圧 と比較電圧のコンパレータを用いた比較であるため基 本構成は全く変えずに実現できる。しかしながら比較電 圧の大きさに関しては二進重み DAC を用いると実現が できないため黄金分割 SAR ADC のための DAC を提案 し、図 6 に示す。図 6 はフィボナッチ数の重みをもった 電流源 DAC[3]にサブスイッチ D4'~D0'と電流分割回路 をつけたものである。フィボナッチ電流源はフィボナッチ数の合計がビット数により決まる出力表現レベル数 を上回るまで並べる。サブスイッチが on にされるとサブスイッチが on された電流源の電流の半分だけが出力電流に加算されるように設計する。

ここで比較電圧を出力する方法を考える。 黄金分割法 を用いた SAR ADC では判定ステップ k 回目の比較電圧 Vcom は(2)式の様に表現できる。ここで MSB より i (i=1,2,3...)番目のディジタル値を d(i)、x 番目のフィボナッチ数を  $F_x$ 、N 桁のディジタルコード出力としている。

$$V_{com} = \frac{F_{N-k}}{2} + \sum_{i=1}^{k} F_{N+1-i} d(i)$$

… (2)

ただし  $d(\mathbf{k}) = 1$

すなわち黄金分割法を実現するには、この式で表現される Vcom を DAC が出力できればよい。

上式において右辺第一項はサブスイッチによって実現できる。右辺第一項を見てわかるとおりk回目の判定では $D_{N-k-1}$ 'のサブスイッチを on にすれば良い。すなわちカウンタなどを用いてサブスイッチは上位から順々に一つだけ on にすれば良い。第一項が $F_0$ となる最終ステップではサブスイッチはすべて off とする。右辺第二項は一般的なSARADCの動作と全く同様でよく、コンパレータの出力に合わせてメインスイッチD5~D0を決定させればよい。サブスイッチとメインスイッチは同時にonすることはない。

サブスイッチ回路及び電流分割部は回路的冗長部分となるが、このような構成はフィボナッチ数重みを用いることでしか実現することができず、シンプルな回路で冗長性を持った回路の実現ができることは、黄金分割法の優位性を示すものである。

#### 6. シミュレーション

C 言語を用いた理論シミュレーションで黄金分割法を用いた SAR ADC によって信頼性がどれだけ向上するのかを検証した。シミュレーションの想定は、サンプルホールド回路の出力電圧の値が一定値以下のノイズを保持している状態での変換を考え、そのノイズの値を変化させることで効果を調べた。

シミュレーション条件は、8bitSAR ADC に周波数 100Hz の単一正弦波を入力しディジタル値へ変換することを考える。サンプルホールド回路の出力電圧の揺れが平均値  $\mu$ 標準偏差  $\sigma$  の正規分布に従うとして、 $\mu$  をサンプルホールド回路の入力電圧値、 $3\sigma$  を 0.5LSB・3LSB・10LSB と設定し、シミュレーションを行った。ノイズに対するシミュレーションを行うためにバイナリ型 ADC と黄金分割型 ADC で SNR を測定し比較した。結果を表 1に示す。

表 1. 黄金探索法 SAR ADC の SNR 比較.

Table.1 SNR Comparisons of Golden Section search algorithm SAR ADC.

|   | ADC種類        | ノイズ要因無し | S/H回路<br>ノイズ<br>0.5LSB | S/H回路<br>ノイズ<br>3LSB | S/H回路<br>ノイズ<br>10LSB |

|---|--------------|---------|------------------------|----------------------|-----------------------|

| , | バイナリ型<br>ADC | 49.6dB  | 43.8dB                 | 39.2dB               | 31.3dB                |

| す | 黄金分割型<br>ADC | 49.6dB  | 48.0dB                 | 41.1dB               | 33.3dB                |

表 1 より明らかに SNR を向上することができたと言える。ノイズ最大値 0.5LSB において黄金分割 SAR ADC でサンプルホールド回路のノイズがほとんど見られないのは、比較値と縮小範囲を同じ値にしていないために原理的に最終ステップ以外では判定間違いが起こっていないからである。さらにノイズの大きさを増加させても同様に SNR の向上を実現しており効果を実証できたと言える。

## 7. まとめ

本論文では、単峰関数の極値を求めるアルゴリズムである黄金分割法及びフィボナッチ探索法を逐次比較型ADCへ応用することを提案した。黄金分割探索を利用した非二進探索アルゴリズムによるコードの種類の増加からディジタル誤差補正を、判定点と縮小範囲を一致させないという提案を用いてノイズ耐性向上を示した。実装に対する提案と動作シミュレーションを行い、黄金分割SARADCの優位性を確認した。

今後は DAC の不完全整定による高速化の定量的な検討も行う。そこでは DAC アナログ出力の整定時間に加え、「コンパレータ比較時間+逐次比較ロジック回路+DAC デコーダ回路」の遅延時間を考慮することにより、どの程度の速度向上を実現できるかを示す。

**謝辞:** 有意義なご討論をいただきました浅見幸司氏に 感謝の意を表します。

### 文 献

- (1) 小林春夫:「ディジタルアシスト・アナログ技術 微細CMOSの 強みを生かす回路設計 -」大阪大学 高度人材育成センター 先端 アナログ技術セミナー,大阪 (2012年1月).

- (2) T. Ogawa, H. Kobayashi, Y. Takahashi, N. Takai, M. Hotta, H. San, T. Matsuura, A. Abe, K. Yagi, T. Mori: "SAR ADC Algorithm with Redundancy and Digital Error Correction", IEICE Trans. Fundamentals, vol.E93-A, no.2, (Feb. 2010).

- (3) 小林佑太朗, 香積正基, 楊志翔, 小林春夫: "ADC/DAC のフィボナッチ数列を用いた冗長性設計の検討"電子回路研究会(2013年10月).

- (4) 中村 滋 (著):「フィボナッチ数の小宇宙」, 日本評論社 (2002 年 9 月).

- (5) A. S. Posamentier, I. Lehmann (著)、松浦俊輔(訳):「不思議な数列フィボナッチの秘密」、日経 BP 社 (2010 年 8 月).