栃木•群馬支所合同研究発表会 (2015/3/2)

ETT-15-8 FTG-15-8

# ΔΣDA変調器のデジタルディザ信号による 性能改善の検討

群馬大学大学院 2年 理工学府 電子情報・数理教育プログラム 新井 薫子

### アウトライン

- 研究背景•目的

- ・ 提案構成の動作

- シミュレーション結果

- ・提案構成の出力の考察

## アウトライン

- 研究背景•目的

- ・ 提案構成の動作

- シミュレーション結果

- 提案構成の出力の考察

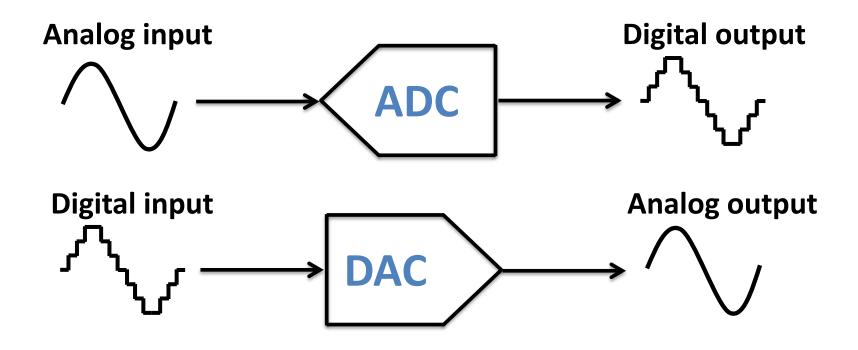

## 研究背景

集積回路の小型化 → デジタル回路に恩恵

高精度のAD/DA変換器の要求

量子化誤差の低減が必要

### 研究目的

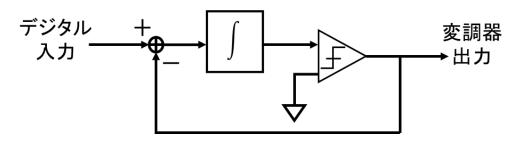

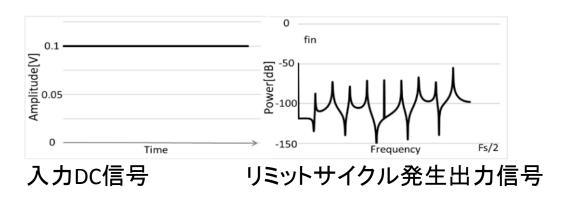

### ΔΣDA変調器での低振幅信号生成

簡単なデジタル回路で高分解能・高線形性が実現可

→周期的に高調波成分が発生 リミットサイクル

デジタルディザ信号を用いてリミットサイクルを低減

### アウトライン

- 研究背景 目的

- ・ 提案構成の動作

- シミュレーション結果

- 提案構成の出力の考察

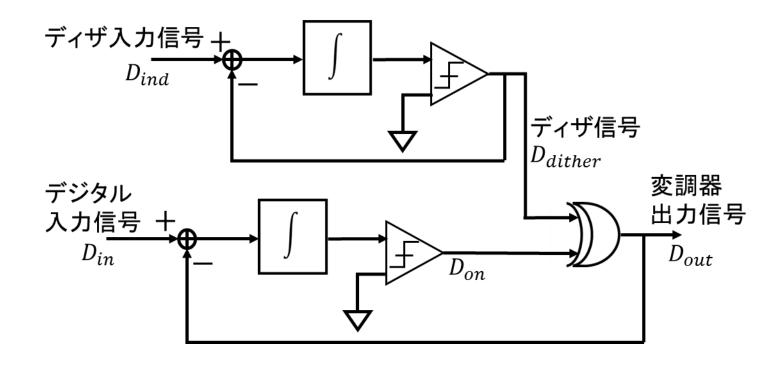

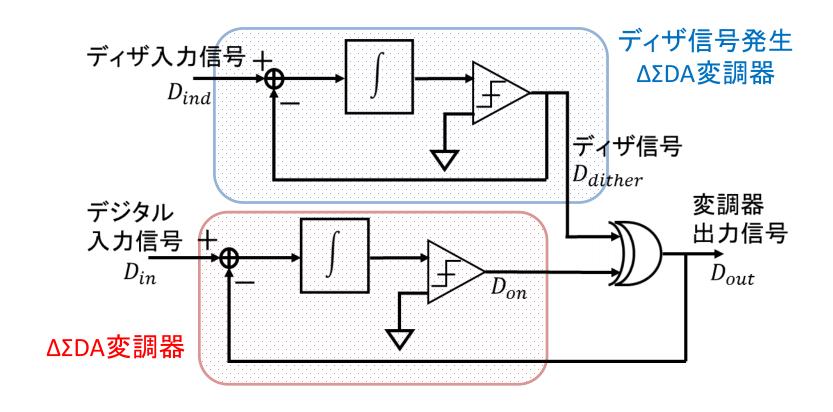

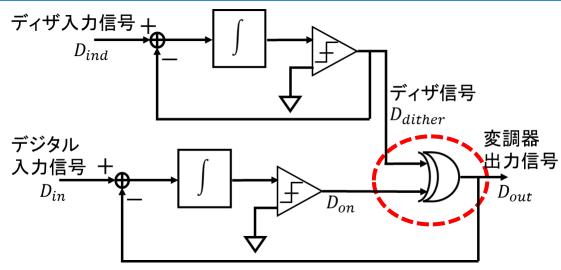

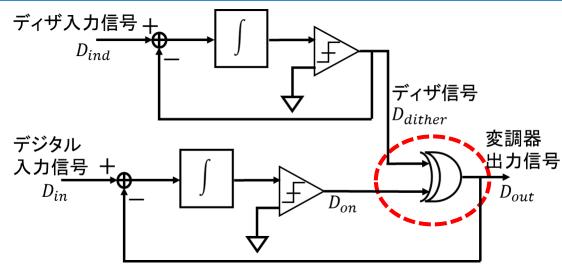

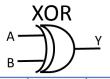

### ディザ信号:前後の相関なくランダムに発生させた0,1信号

| Α | В | Υ |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

#### 排他的論理和

ディザ信号が1のとき、信号反転

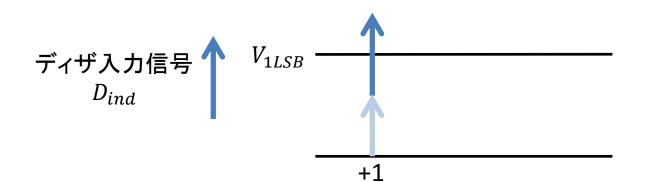

ディザ入力信号の振幅・中心値により、 反転させる数を制御

| Α | В | Υ |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | Λ |

#### 排他的論理和

ディザ信号が1のとき、信号反転

ディザ入力信号の振幅・中心値により、 反転させる数を制御

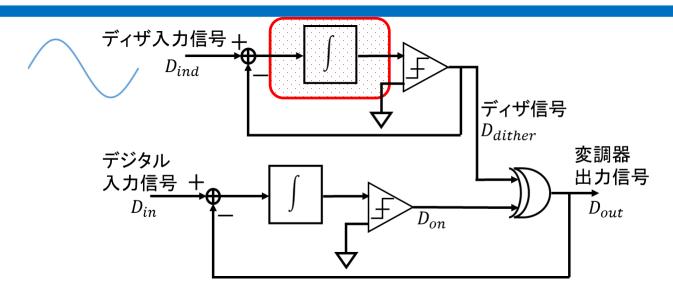

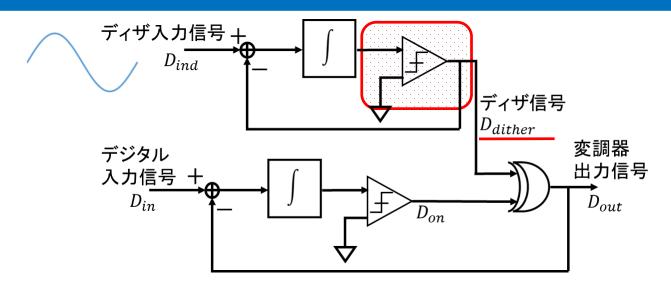

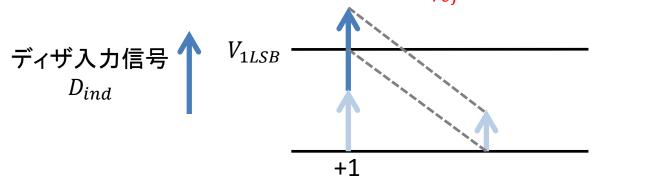

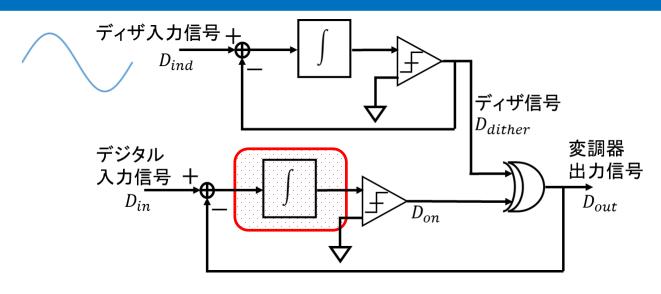

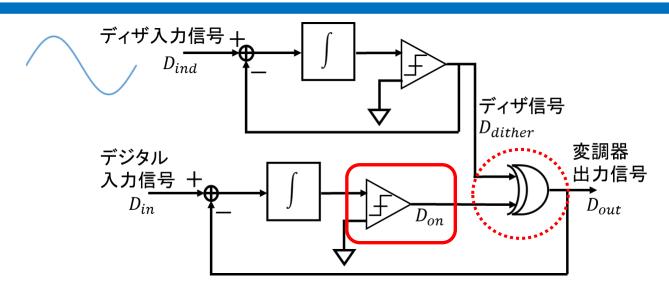

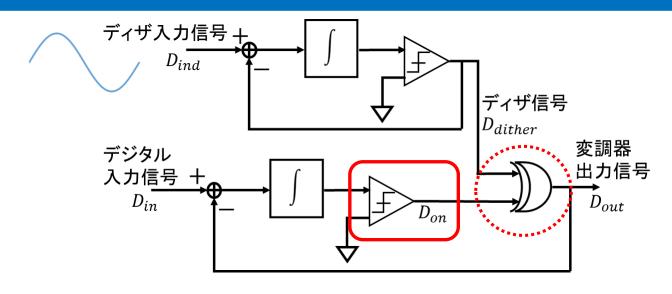

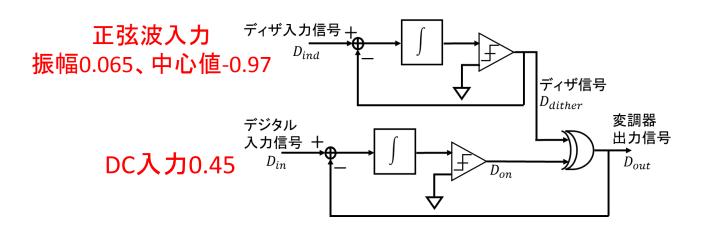

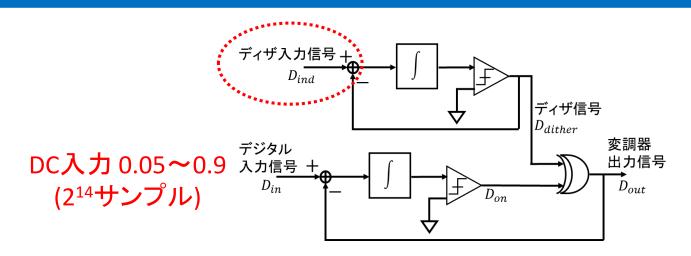

### ディザ信号発生ΔΣデジタル変調器の動作①

### ▶ 入力Vinを累積

$$accd(n) = accd(n-1) + D_{ind}(n)$$

### ディザ信号発生ΔΣデジタル変調器の動作②

### > コンパレータで比較

accd(n) > 0のとき  $D_{dither}(n) = 1$ ,  $accd(n) = accd(n) - D_{ref}$  ディザ信号1を出力、累積値から $D_{ref}$ を引く

accd(n) < 0のとき  $D_{dither}(n) = 0$ ,  $accd(n) = accd(n) + D_{ref}$  ディザ信号0を出力、累積値に $D_{ref}$ を足す

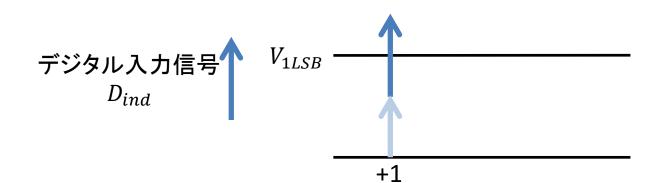

### 本体のΔΣデジタル変調器の動作①

### ▶ 入力Vinを累積

$$acc(n) = acc(n-1) + D_{in}(n)$$

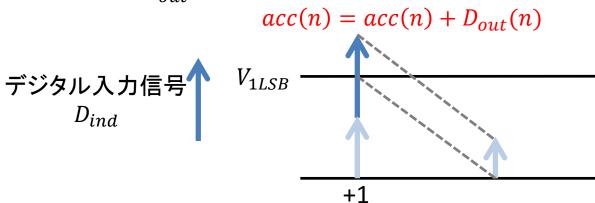

### 本体のΔΣデジタル変調器の動作②

#### > コンパレータで比較

acc(n) > 0のとき  $D_{on}(n) = 1$  ディザ信号との排他的論理和をとる

$$D_{out}(n) = XOR(D_{on}(n), D_{dither}(n))$$

累積値からD<sub>out</sub>を引く

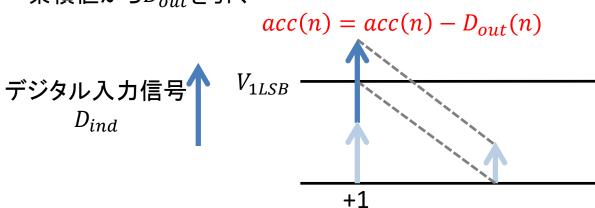

### 本体のΔΣデジタル変調器の動作③

#### > コンパレータで比較

acc(n) < 0のとき  $D_{on}(n) = 0$  ディザ信号との排他的論理和をとる

$$D_{out}(n) = XOR(D_{on}(n), D_{dither}(n))$$

累積値からDoutを足す

## アウトライン

- 研究背景 目的

- ・ 提案構成の動作

- シミュレーション結果

- 提案構成の出力の考察

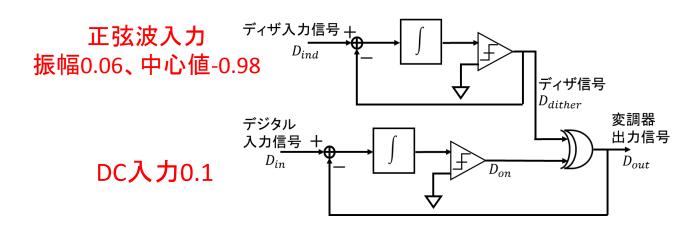

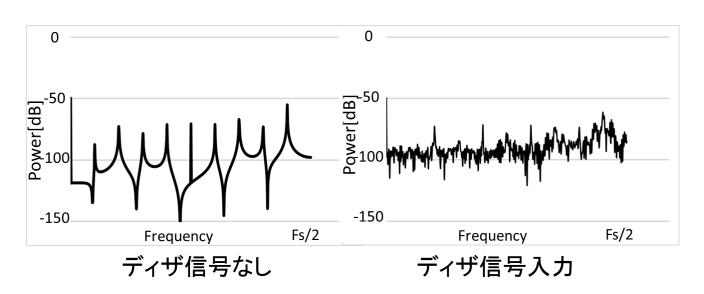

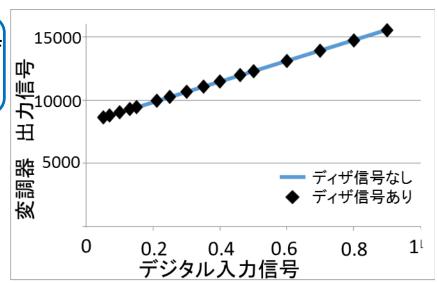

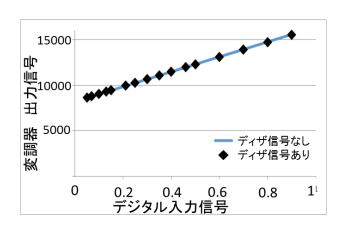

### シミュレーション結果

## シミュレーション結果

ディザ信号入力によりリミットサイクルが低減

## アウトライン

- 研究背景•目的

- ・ 提案構成の動作

- シミュレーション結果

- ・提案構成の出力の考察

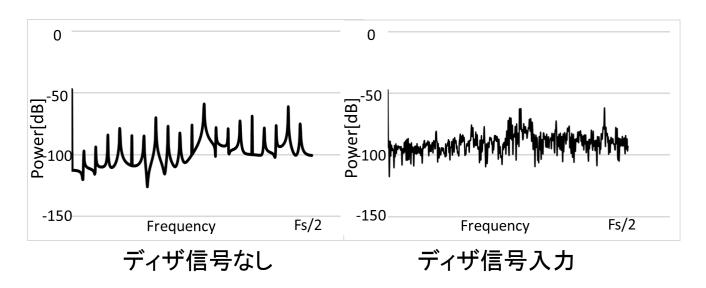

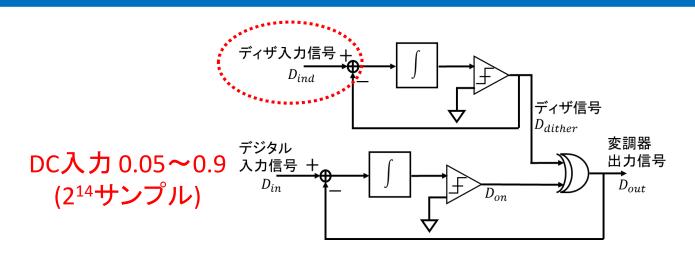

# シミュレーション結果の考察

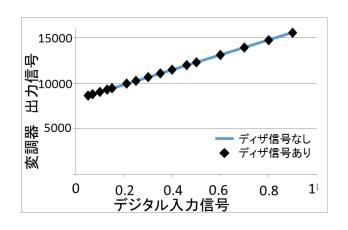

ディザ信号を入力した時・入力しない時 変調器出力の1をカウント

## シミュレーション結果の考察

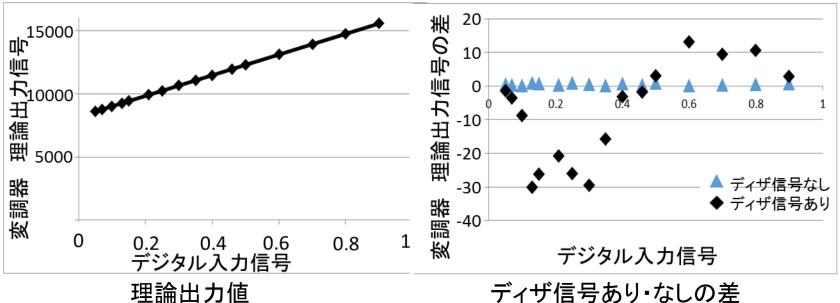

ディザ信号を入力した時・入力しない時変調器出力の1をカウント

#### ディザ信号あり:

ディザ入力信号の振幅·中心値を調節 ディザ信号の1の出現回数を変えた

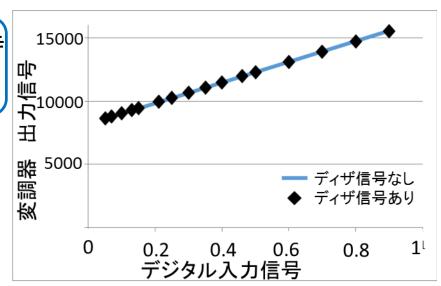

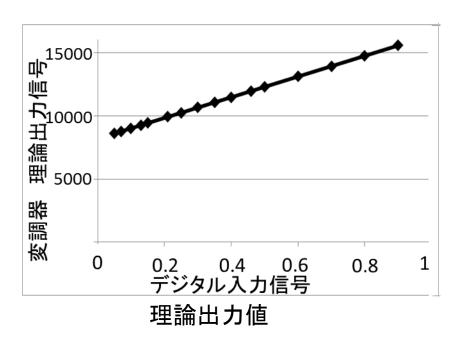

### 理論出力値との比較

▶ シミュレーションと理論値を比較

デジタル入力信号1:理論出力値214

デジタル入力信号0:理論出力値213

### 理論出力値との比較

> シミュレーションと理論値を比較

デジタル入力信号1:理論出力値214

デジタル入力信号0:理論出力値213

### 理論出力値との比較

▶ シミュレーションと理論値を比較

デジタル入力信号1:理論出力値214

デジタル入力信号0:理論出力値213

<u>ディザ信号あり・なしの差は約0.2%</u>

少しのディザ信号でリミットサイクル低減

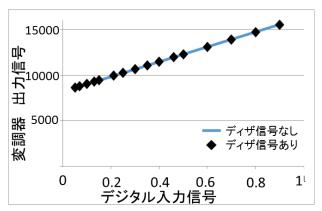

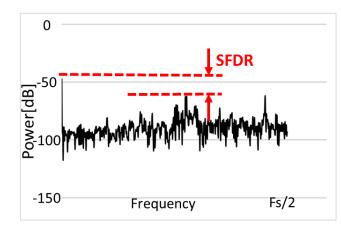

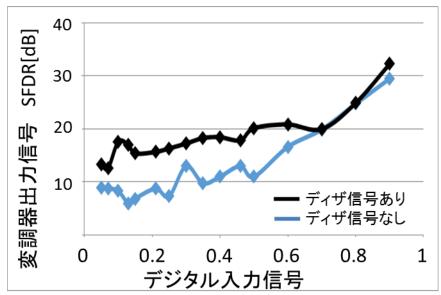

### SFDR比較

Spurious Free Dynamic Range(SFDR) 信号電力と最大高調波の電力の比

ディザ信号によりリミットサイクルが低減 SFDRが向上

### まとめ

ΔΣDA変調器: 低振幅信号生成でリミットサイクルが発生

デジタルディザ信号との排他的論理和を用いた構成

- デジタル処理によるディザ信号発生

- ΔΣ変調後にディザを入力するので、出力へは影響ない

- 排他的論理和により1ビット出力

リミットサイクル低減、SFDR向上

### Q&A

- Q. デジタル入力信号でDC入力 0.1などとあり、デジタルなら0,1 の並びとなるはずだが、どういう値を表しているのか。

- A. 1の出現頻度と関係している。DC入力値が大きいときは、デジタル値での1の出現が多く、DC入力値が小さいときは、デジタル値での1の出現が少ないことを表している。

- Q. 既存のDitherを使った回路はあるのか。

- A. ΔΣDA変調の前後にDitherを入力することがあるが、ノイズが増加したり、後段に多ビットのDACが必要となる。XORを使った構成は新しい構成である。