# HCI による LDMOS の信頼性シミュレーションに使用する 最大電界モデルの研究

東野 将史\*, 青木 均, 築地 伸和, 香積 正基, 戸塚 拓也 新井 薫子. 轟 俊一郎. 小林 春夫(群馬大学)

> Study on Maximum Electric Field Modeling Used for HCI Induced Degradation Characteristic of LDMOS Transistors

Masashi Higashino\*, Hitoshi Aoki, Nobukazu Tsukiji, Masaki Kazumi, Takuya Totsuka, Yukiko Arai, Shunichiro Todoroki, Haruo Kobayashi (Gunma University) t15804080@gunma-u.ac.jp, h.aoki@oak.gunma-u.ac.jp

This paper reports a maximum electric field model of laterally diffused MOSFET (LDMOS) transistors under the condition of high current injection effect used for reliability simulations. LDMOSs operate under high-voltage and large-current biases, where electric field increases with biases at the gate edge. We present the investigation, formulations, and verifications of our maximum electric field model.

キーワード:信頼性解析,経時劣化,経時劣化モデル,LDMOS,デバイスモデリング (Reliability Analysis, Time Degradation, Aging Model, LDMOS, Device Modeling,)

#### 1. はじめに

Laterally Diffused MOSFET (LDMOS)は、ドレイン領域を横方向に拡張することによりドレイン・ゲート間の電界強度を緩和する構造の MOSトランジスタである。オン抵抗が比較的小さく、高耐圧であることが特徴である。このことから、携帯用基地局のパワーアンプなどの出力段として用いられる。LDMOSは、高電圧・大電流で利用するため、ドレイン側ゲート端で電界強度が集中してしまい、Hot Carrier Injection (HCI) 現象が顕著となる。これにより、経時・温度劣化が問題となる。これらの劣化現象を予測することは、デバイスの信頼性に重要な課題である。

本研究では、n チャネル LDMOS の信頼性シミュレーションに用いる最大電界モデルの研究を行った。n チャネル MOSFT の経時・温度劣化は、飽和領域において高ドレイン電圧によって起こる HCI や、高温・正電圧のストレスによって発生する Positive Bias Temperature Instability (PBTI) 現象がある。n チャネル MOSFET は、HCI 現象がより顕著に現れる。n チャネル LDMOS においても同様のことが言えることから、HCI による劣化現象について検証を行った。

n チャネル LDMOS の HCI 劣化現象は、文献[1]によると、"ドリフト層のキャリアの減少からのオン抵抗増加によ

る"ものと記されている。文献[2]では、オン抵抗増加の原因は、ゲート端の横方向の最大電界と相関があると報告されている。このことから、劣化現象を検証する上で、最大電界強度を予測することは重要である。しかし、回路シミュレータ用のコンパクトモデルにおいて、最大電界 $E_m$ は測定データによる完全なフィッティング関数モデルになっており、未公開である。そこで、オン抵抗による HCI 劣化現象の解析と、最大電界 $E_m$ のモデル関数を開発したので報告する。開発した関数モデルを用いることにより、信頼性・経年劣化を考慮した LDMOS 回路設計が可能となる。

### 2. HCI 劣化現象

HCI 現象のモデル[1]は、Luck Electron Model (LEM) に基づいて考えられている。代表的な HCI モデルは、Hu 教授により考案された Hu model である。一般的な n チャネル MOSFET にバイアス電圧 $V_{gs}$ ,  $V_{ds}$ を印加する。ゲート電圧により、反転層が形成されてキャリアが移動する。ピンチオフした飽和領域において、ドレイン電界により加速されたキャリアは、高いエネルギーを持ったホットキャリアとなる。加速されてホットキャリアは、反転層のイオンと衝突し、電離衝突が起こる。これにより電子・正孔対が発生する。発生したホットキャリアの一部は、酸化膜にトラ

ップされ、酸化膜の劣化を引き起こす。キャリアがトラップされることによって、キャリアが減少しオン抵抗が増加する。これにより、移動度の減少によるドレイン電流 $I_D$ の低下や、しきい値電圧 $V_{TH}$ の増加を引き起こす。

# 3. LDMOS 構造と HiSIM-HV モデル [3]

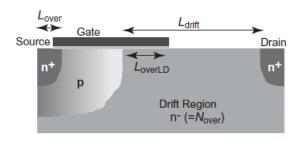

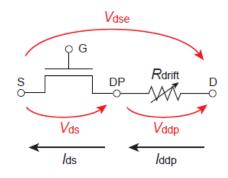

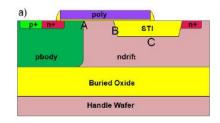

図 1 に LDMOS の構造、図 2 に HiSIM-HV モデルによる LDMOS モデル・コンセプトを示す。LDMOS は、高耐圧 を実現するために、ゲート・ドレイン間のドリフト領域を 横方向に拡張している。ゲート・ソース間電圧 $V_{gs}$ を印加すると、反転層が形成される。ドレイン・ソース間電圧 $V_{ds}$ を 印加することにより、キャリアはソースから供給され、ドリフト領域からドリフトによりドレインへ達する。大部分のドレイン・ソース間電圧 $V_{gs}$ は、ドリフト領域で電圧降下する。HiSIM-HV モデルでは、ドリフト領域をドリフト抵抗 $V_{drift}$ は、(1)~(3)式で定義される。

$$R_{drift} = \left(R_d + V_{ds}R_{DVD}\right) \left(1 + RDVG11 - \frac{RDVG11}{RDVG12}V_{gs}\right)$$

$$(1 - V_{bs}RDVB) (1)$$

$$R_{d} = \frac{R_{do}}{W_{eff,LD} \cdot NF} \left( 1 + \frac{RDS}{\left( W_{gate} \cdot 10^{6} \cdot L_{gate} \cdot 10^{6} \right)^{RDSP}} \right)$$

(2)

$$R_{d0} = (RD + R_{d0,temp})f_1 \cdot f_2 \tag{3}$$

#### 4. モデルパラメータ抽出とシミュレーション

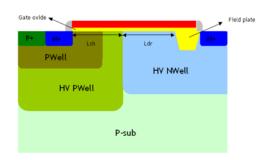

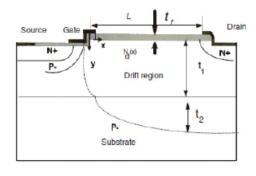

ここでは、文献[4]で報告されている直流電流・電圧特性を数値化し、測定データとした。図 3 は、測定に使用された n チャネル LDMOS の断面図である。この LDMOS のプロセスは、プロセス長0.18umで作成されている。ゲート長は 20um,ゲート幅は 0.4um,ゲート酸化膜圧は 115 Å である。

### $\langle 4\cdot 1 \rangle$ $I_d - V_{ds}$ 測定データ解析

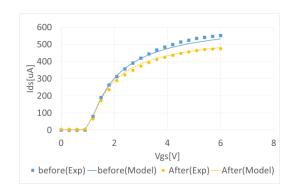

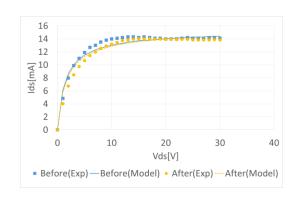

文献[4]の HCI 劣化前後の特性を観ると、しきい値電圧は変化せずにドレイン電流Idが減少している。このことから、実効移動度減少、またはドレイン抵抗の増加によりドレイン電流が減少していると予測される。この二つの要因を仮定して、HiSIM-HV モデルのモデル式を解析し、劣化特性のモデルパラメータ選択を行った。図 4 に測定データから抽出したモデルと測定データのドレイン電流・ゲート電圧特性の比較を示す。抽出したモデルは、ストレス前後の測定データと一致していることが分かる。これより、HiSIM-HVモデルのドリフト抵抗パラメータRDが劣化していることが判明した。

# $\langle 4\cdot 2 \rangle$ $I_d - V_{as}$ 測定データ解析

文献[4,5]の HCI 劣化前後の特性を観ると、飽和領域のドレイン電流は変化せずに、ピンチオフ領域のみ変化して

いることが分かる。図 5 に測定データから抽出したモデルと測定データのドレイン電流・電圧特性の比較を示す。ストレス印加前後においてモデルパラメータは、RD のみを変化させている。抽出したモデルは、測定データと完全に一致はしていないが、飽和領域のドレイン電流は変化せず、ピンチオフ領域のみ変化するという特徴を再現していることが確認できることから、HiSIM-HV モデルのRDが劣化していることが分かる。

図 1 LDMOS の構造[3] Fig.1. Schematic of the LDMOS[3]

図 2 LDMOS モデル・コンセプト[3] Fig.2. LDMOS Model concept in HiSIM-HV[3]

図 3 測定に用いた n チャネル LDMOS の断面図[4] Fig.3. Schematic cross section of the n-type LDMOS transistor used in [4]

図 4 抽出モデルと測定データの $I_d - V_{gs}$ 特性比較 Fig.4. Ids vs Vgs characteristics of an n-type LDMOS before and after hot-carrier induced degradation.

図 5 抽出モデルと測定データの $I_d - V_{ds}$ 特性比較 Fig.5. Ids vs Vds characteristics of an n-type LDMOS before and after hot-carrier induced degradation.

# 5. 最大電界E<sub>m</sub>のモデル開発

LDMOS の HCI 劣化現象は、ドリフト層のキャリアの減少におけるオン抵抗の増加によるものだと解明できた。文献[2]によると、オン抵抗の増加はゲート端の横方向の電界強度と相関があると報告されている。時間依存におけるオン抵抗(Ron) の劣化モデル式は、以下の式で表される。

$$\frac{\Delta R_{\rm on}}{R_{\rm on}} = A_1 \cdot \ln\left(1 + \frac{t}{\tau}\right) + A_2 \cdot \ln\left(1 + \frac{t}{\gamma \cdot \tau}\right) \tag{4}$$

$A_1$ ,  $A_2$ ,  $\gamma$ は、フィッティングパラメータ, t はストレス時間,  $\tau$ は特性時間である。

τは、以下の式で表される。

$$\tau = \frac{\alpha \cdot W}{I_D} \cdot \frac{\phi_b}{E_m \lambda} e^{\frac{\phi_b}{E_m \lambda}} \tag{5}$$

$\alpha$ は、フィッティングパラメータ、Wは、チャネル幅、 $E_m$ は、最大電界の大きさ、 $\emptyset_b$ は、 $Si-O_2$ のエネルギー障壁を乗り越えるために必要な電子のエネルギーである。(4),(5)式より、 $R_{on}$ の劣化は最大電界の大きさが関わっていることが分かる。

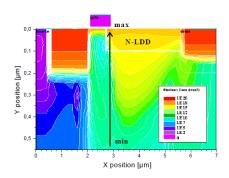

T-CAD シミュレータによる電界分布の解析では、図 6 に示した LDMOS の断面図におけるドリフト層(B, C) 位置で電界ピークが生じていると報告されている。文献[6]におい

ても同様に、ゲート端におけるドリフト層で電界ピークが生じていることが分かる(図 7)。しかし、最大電界が測定データによる完全なフィッティング関数モデルとなっている。ゲート・ソース間電圧及びドレイン・ソース間電圧のストレス電圧依存は、最大電界に影響することから、最大電界のモデル関数を開発した。

図 6 n チャネル LDMOS の断面図[2]

Fig.6. Schematic cross section of the n-type LDMOS[2]

図 7 n チャネル LDMOS の電界強度分布[6] Fig.7. Electric field distribution of n-type LDMOS[6]

図 8. 電界導出のための MOSFET Fig.8. MOSFT by introduced electric field

#### $\langle 5\cdot 1 \rangle$ 最大電界 $E_m$ の導出

最大電界の $E_m$ ゲート、ドレイン・ストレス電圧依存式を 算出する。MOSFETの断面図を図8に示す。

二次元ポアソン方程式は、(3)式で示される。

$$\frac{\partial^2 \phi(x,y)}{\partial x^2} + \frac{\partial^2 \phi(x,y)}{\partial y^2} = -\frac{qN_d(x)}{\varepsilon_{si}}$$

(6)

これをy方向( $0\sim t_1$ )に積分し、一次元ポアソン方程式を求める。

$$\int_0^{t_{si}} \frac{\partial^2 \phi(x, y)}{\partial x^2} dy + E_y(x, 0) - E_y(x, t_1) = -\frac{q N_d(x)}{\varepsilon_{ci}} t_1$$

(7)

Si-SiO<sub>2</sub>界面の境界条件より、

$$E_y(x,o) = -\frac{\epsilon_o}{\epsilon_{si}} \frac{\phi_f(x) - V_{gs} - V_{FB,f}}{t_f} \ (\phi_f(x) \equiv \phi(x,)) \ \ (8)$$

$$E_{y}(x,0) \approx -\frac{\varepsilon_{0}}{\varepsilon_{si}} \frac{\phi_{f}(x)}{t_{f}}$$

(9)

以上の方程式を解くと $V_{DS}$ による横方向の最大電界の方程式が求まる。

$$E_{\rm m} = \frac{V_{\rm DS} - \emptyset_{\rm b}}{t_1} + \frac{q N_{\rm d}(x) t_1}{2 \varepsilon_{\rm si}} \tag{10}$$

以上より、ホットキャリア・ストレス電圧印加時の最大 電界は以下の式になる。

$$E_{\rm m}(V_{\rm DS}, V_{\rm GS}) \approx \frac{V_{\rm DS} - V_{\rm dsat}}{I_{\rm t} + w_{\rm d}(V_{\rm GS})}$$

(11)

ここで、RD モデル[1]について着目する。RD モデルとは、MOSFET の DC モデルにおける HCI 劣化現象をモデル化したものである。2004年に Kuflluoglu と Alam により発見された。トランジスタのドレイン近傍で発生するホットキャリア効果を、修復されることなくモデル化することができる。RD モデルは、チャネル/酸化膜界面及びゲート接合部分付近の水素拡散粒子の生成を方程式で表している。これにより、劣化現象を単純化することができる。RD モデルにおける DC HCI モデルは、MOSFET のしきい値電圧劣化をモデル化したものである。しきい値電圧劣化は以下の式で表される。

$$\Delta V_{\rm TH} = A_{HCI} t^{\frac{1}{1+n_{\chi}}} \tag{12}$$

$n_x$ は、水素粒子あたりの水素原子数を示している。 $A_{HCI}$ は以下の式で表される。

$$A_{HCI} = C_{HCI}[(V_{GS} - V_{TH})K_{V}]^{\frac{n_{X}}{1 + n_{X}}} \left(\frac{n_{X}}{I}\right)^{\frac{1}{1 + n_{X}}}$$

(13))

定数Kvとそこで用いられている係数を以下の式に示す。

$$K_{v} = \exp\left(\frac{E_{ox}}{E_{o}}\right) \exp\left(\frac{-\emptyset_{IT}}{q\lambda E_{lat}}\right) \exp\left(-\frac{E_{a}}{kT}\right)$$

(14)

$$E_{\rm ox} = \frac{(V_{\rm GS} - V_{\rm TH})}{t_{\rm ox}} \tag{15}$$

$$E_{lat} = \frac{(V_{DS} - V_{DSAT})}{l} \tag{16}$$

$E_{ox}$ は、ゲート酸化膜における電界の強さ, $E_{o}$ は技術依存のパラメータ, $\phi_{IT}$ は衝突電離により生じた電子のエネルギー, $\lambda$ はチャネルを通過する電子の自由運動, $E_{lat}$ は横方向の電界強度を示している。

(14)式の飽和電圧 $V_{DSAT}$ は、

$$V_{DSAT} = \frac{E_{sat}L(V_{GS} - V_{TH})}{E_{sat}L + (V_{GS} - V_{TH})}$$

(17)

L はチャネル長, $E_{sat}$ は飽和電圧における飽和電界である。 $E_{sat}$ は以下の式で表される。

$$E_{sat} = \frac{2v_{sat}}{\mu_{eff}} \tag{18}$$

$v_{sat}$ は飽和速度, $\mu_{eff}$ は実行移動度である。

(12)~(18)式より、RD モデルのしきい値劣化の劣化現象は、横方向の電界の大きさに依存することが分かる。DC HCI モデルの理論は、LDMOS でも同様である。式(9)に式(15)の RD モデルを導入すると $E_m$ は以下の式で表される。

$$E_{\rm m}(V_{\rm DS}, V_{\rm GS}) \approx \frac{V_{\rm DS} - \frac{E_{\rm sat}L(V_{\rm GS} - V_{\rm TH})}{E_{\rm sat}L + (V_{\rm GS} - V_{\rm TH})}}{l_{\rm t} + w_{\rm d}(V_{\rm GS})}$$

(19)

#### 〈5·2〉 最大電界Emの関数モデル開発

(8)式における $\mathbf{w_d}$ は、空乏層幅を示している。しかし、空 乏層幅を LDMOS の構造で導出するのは困難である。そこで、統計学における peak 関数の一つである Extreme 関数を用いて、モデル開発を行った。 Extreme 関数とは、任意の位置にピークを持つ関数である。これにより、電界強度が最大となるゲート・ソース電圧 $\mathbf{V_{GS,max}}$ を任意の値でピークを持つ関数となる。これにより、ゲート・ソース間電圧及びドレイン・ソース間電圧のストレス電圧依存における、最大電界 $\mathbf{E_m}$ の関数モデルを開発した。以下に関数モデルを示す。

$$E_{m} = Ae^{(-e^{-z}-z+1)}$$

(20)

$$A = \frac{(V_{DS} - V_{dsat})}{L_{eff}} \tag{21}$$

$$z = \frac{V_{GS} - V_{TH} - V_{GS\_max}}{\beta}$$

(22)

$\alpha$ ,  $\beta$  は、フィッティングパラメータである。 A はピーク値の振幅を表している。横方向の電界強度は、 $V_{gs}$ に依存することが報告[2]されている。これより、開発した関数モデルにおいても電界強度が $V_{gs}$ に依存するようにした。 z の項の $V_{GS\_max}$ の値を変える事により電界のピーク値を自由に動かすことができ、あらゆるピーク位置に対応することが可能である。

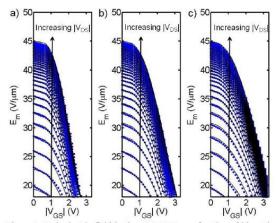

図 9 に文献[2]の T-CAD による Em の算出結果を示す。 図 9 は、図 2 の B 点における電界強度のグラフである。 T-CAD シミュレーションで用いた n チャネル LDMOS のプロセスは、チャネル幅 $W=40\mu m$ のみ記載されていた。開発したモデル式では、実効チャネル長に依存したモデルを考案したが、チャネル長が記載されていなかったため、チャネル幅を用いた。 $E_{sat}$ における $V_{sat}$ と $\mu_{eff}$ も記載されていなかったため、文献[1]の 65nm の CMOS プロセスデータを用いた。以上の条件でモデル式の検証を行った。

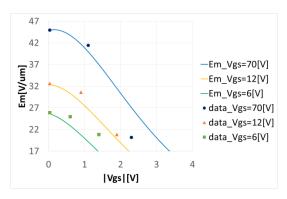

図 9 中の(a)における $V_{DS} = 70,12,6[V]$ での数値計算結果を測定データとした。今回開発した Em 関数モデルと測定データを比較した結果を図 10 に示す。

図 10 より、電界のピーク値はバイアス電圧を変化させても一致していることが確認できる。電界減少後の傾向も形状が近いことから、開発した Em の関数モデルは、有効であると考えられる。

Figure 4: Peak electric field in the nLDMOS as a function of bias. The symbols represent  $E_m$  at location B as it follows from TCAD simulations. The solid lines represent the results of an empirical fitting function to describe  $E_m$  for use in a circuit reliability simulator.  $|V_{DS}|$  is varied from 10 V to 70 V in steps of 2 V. a):  $T_m=233$  K; b):  $T_m=333$  K; c):  $T_m=433$  K.

# 図 9 論文掲載 n チャネル LDMOS の電界ピーク[2] Fig.9. Peak electric field of an nLDMOS sample [2]

図 10 測定データと提案する関数モデルの比較

Fig.10. Comparison between measured data and the proposed function model in the maximum electric field of an nLDMOS

#### 6. まとめ

本研究では、nチャネル LDMOS の HCI 劣化前後の直流電圧・電流特性を解析した。そして、回路シミュレータ SPICE を用いて、事前に劣化前後の直流電圧・電流特性に 予想するためのモデルを開発した。HCI 劣化現象は、ドリフト層のキャリアの減少からのオン抵抗増加が原因であり、それらはゲート端における横方向の電界強度と相関がある。そこで、最大電界のモデル関数を開発した。開発した関数モデルを用いることにより、信頼性・経年劣化を考慮した LDMOS 回路設計が可能となる。

#### 7. 謝辞

本研究を遂行するにあたり、MoDeCH 関係者の方々に心より感謝申し上げます。

#### 文 献

- E. Maricau and G. Gielen, : "Analog IC Reliability in Nanometer CMOS", Springer Science+Business Media New York (2013)

- (2) Guido T. Sasse, Jan A.M.Claes and Bart Dev Vries: "An LDMOS hot carrier model for circuit reliability simulation" (2014)

- (3) Hisim-HV 2.2.0 User's manual http://home.http://home.hiroshima-u.ac.jp/usdl/HiSIM\_HV/C-Cod e/HiSIM\_HV\_C.html

- (4) N. Soin.S.S.Shahabudin and K.K.Goh, et al,: "Measurement and Characterization of Hot Carrier Safe Operating Area (HCI-SOA) in 24V n-type Lateral DMOS Transistors",10th IEEE International Conference on Semiconductor Electronics, pp.659-663 (2012)

- (5) 築地伸和, 青木均,新井薫子, 轟俊一郎,香積正基,戸塚拓也,東 野将史:"LDMOSの経時・温度劣化特性解析とモデル化に関する研 究"第5回電気学会 東京支部 栃木・群馬支所合同研究発表会

- (6) M.A.Belaid and K.Ketata :"Hot-Carrier Effects on Power RF LDMOS Device Reliability" EDA Publishing THERMINIC 2008