# フィボナッチ数列重み付け SAR ADC のための DAC の検討

荒船 拓也\* 濵谷 将平 小林 佑太朗 小林 春夫 (群馬大学)

## DAC Topologies for Fibonacci Sequence Weighted SAR ADC

Takuya Arafune\*, Shohei Shibuya, Yutaro Kobayashi, Haruo Kobayashi (Gunma University)

**Abstract-** This paper describes several DAC topologies with Fibonacci sequence (or Golden ratio) weights for redundant successive approximation register (SAR) ADC which enables high-reliability and high-speed AD conversion using digital error correction. We showed previously that applying Fibonacci sequence and its property called Golden ratio to SAR ADC design leads to well-balanced redundant search algorithms, and here we present that the corresponding internal DAC can be realized with simple topology such as R-R network, C-C network or their combination, which is another beautiful feature of the Fibonacci sequence weighted SAR ADC.

**キーワード :** DAC, SAR ADC, フィボナッチ数列, 黄金比, 冗長性

(Keywords: DAC, SAR ADC, Fibonacci Sequence, Golden ratio, Redundancy)

## 1- はじめに

近年、自動車のエレクトロニクス化は著しく、車載用エレクトロニクス技術に大きな関心が集まっている。その中でマイコンと組み合わせたAD変換器では逐次比較方式が広く使われている。その高速化、高精度化、低消費電力化、低コスト化、高信頼性化の要求が年々厳しくなっている。そこで高信頼性化・高速化実現のために冗長設計がある。[1-8] 時間冗長システムをAD変換過程に組み込むことでデジタル誤差の補正を実現し、性能の向上を図る。

筆者らはフィボナッチ数列重み付けを用いた冗長アルゴリズム逐次比較近似AD変換器は従来の方式に比べて誤差補正力・速度を向上させることを示した。[4-6] 本論文ではフィボナッチ数列重み付け冗長逐次比較近似AD変換器 (Successive Approximation Register Analog-to-Digital Converter: SAR ADC) の内部で用いるDA変換器(DAC)が簡単なR-Rネットワーク、C-Cネットワークもしくはそれらの組み合わせで実現することを検討したので報告する。即ちフィボナッチ数列重み付け冗長 SAR ADC の一つの特長として簡単な構成で内部DACが実現できることを示す。

これまでの非二進冗長アルゴリズムSAR ADC ではDACを完全ユナリ構成にする [1, 2]、基数を推定する[7, 8] 回路方式が用いられてきたが、回路規模が大きくなってしまう。それに比べてフィボナッチ数列重み付けアルゴリズムではDACが簡単な構成で実現でき、大きなアドバンテージになる。

## 2- 逐次比較近似AD変換器

### 2-1. 逐次比較近似AD変換器の構成

AD変換器を実現する手法の中で SAR ADC は高分解能 (10~18bit) で中速サンプリング (数100k~数10MSps) のAD変換器を実現できる。低消費電力・小チップ面積・オペアンプ不要で実現可能なので自動車やファクトリオートメーション等に広く用いられている。

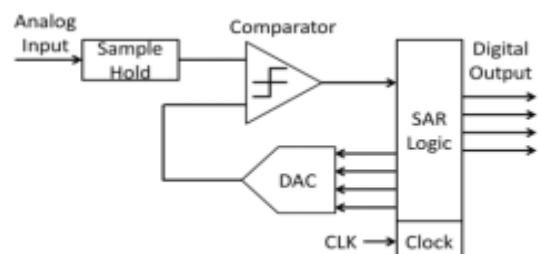

SAR ADC の主な構成要素は図1のようにサンプル&ホールド回路、コンパレータ、DAC、逐次比較レジスタ (SAR)、クロック生成回路の5つである。SAR ADC の動作は天秤の原理を用いている。入力電圧と比較電圧 (錘) とを比較して、釣り合いが取れるよう DAC出力電圧を生成する。

図1 逐次比較近似 AD 変換器の構成。

Fig.1. Block diagram of an SAR ADC.

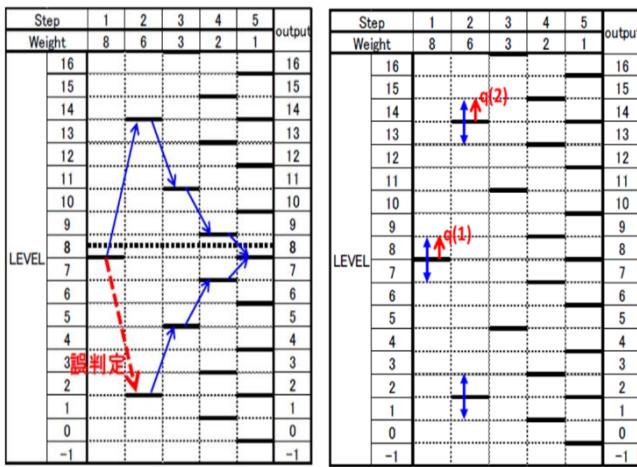

図2 4-bit 5-step SAR ADC の非二進探索アルゴリズムと誤差補正範囲  $q(k)$ の図表示.

Fig.2. Redundant search algorithm of a 4-bit 5-step SAR ADC and representation of error correction ranges  $q(k)$ .

## 2-2. 逐次比較近似AD変換器の冗長アルゴリズム設計

冗長とは予備や余裕のことで、ここでは比較回数に余裕を持たることでADCの性能の向上を図る。[1-8] すなわち、比較回数を増加させデジタル誤差補正を可能にする。例として、入力電圧8.3LSB相当のアナログ入力電圧での4bitのAD変換での冗長性を持たせた探索アルゴリズム(5step)の解探索動作を図2 左に示す。

1ステップ目の判定でコンパレータが誤判定を起こしても後段のステップで補正され、結果として正しい変換ができる。比較回数に余裕があるので誤差補正が可能となり、AD変換の信頼性が高まる。また、変換過程で誤差補正ができるため、DA変換器の出力が完全に整定するまで待たずに次のステップの判定に移ることができ、判定回数を増やしても全体のAD変換速度を向上できる。[1-8] このように冗長設計によって信頼性と変換速度に優れたAD変換器が実現できる。

しかし、この冗長アルゴリズムSAR ADC 設計には次のような課題がある。

一つ目の問題として冗長設計での比較電圧の小数重みの出現がある。比較電圧重みは変換精度や設計容易化のために整数であることが望ましい。アルゴリズム設計で整数が得られなければ整数值への丸めが必要であるが、この処理で各ステップでの補正力にばらつきが生じ、結果として性能向上を妨げる要因となる。

二つ目の問題は基數 (radix) 決定の難しさである。基數は比較電圧重みを決定する数字であり、(1)式で表される。

$$p(k) = x^{M-k} \quad (1)$$

ここで  $x$  が基數、 $M$ :総ステップ数、 $p(k)$ :  $k$  step目の比較電圧重みを表している。この比較電圧重みが補正可能範囲を決定するため、

基數の決定によって補正可能範囲が決まる。図2 右に基數を適当に設定した時の誤差補正範囲を示す。この例では補正可能範囲に制限がかかり、補正範囲外の入力値は補正できない。補正範囲を考慮しつつ基數を決定するのは難しい。これらの要因により冗長設計の効果が十分に発揮できない。

三つ目は内部DA変換器の構成の問題である。二進重み付けSAR ADC では R-2R 抵抗ネットワークDAC等により簡単な構成で二進重み付けDACを実現できる。冗長アルゴリズムを使用するとセグメント型 (Unary型) DA変換器を用いる [1, 2]、基數を推定する[7, 8] ことが必要となり回路規模が大きくなってしまう。

筆者らは [4, 5, 6] でフィボナッチ数列重み付けSAR ADC で一つ目、二つ目の問題が解決できることを示したが、この論文では三つ目の問題も解決できることを示す。

## 3- 整数論を用いた冗長アルゴリズムの設計

### 3-1. フィボナッチ数列 [9]

フィボナッチ数列とは式(2)の漸化式で定義される数列である。式(2)中の  $n$  は  $n \geq 0$  を満たす任意の自然数である。1202年にイタリアの数学者レオナルド・フィボナッチが発行した『算盤の書』(Liber Abaci) に記載されている。

$$F_{n+2} = F_n + F_{n+1} \quad (2)$$

$$\text{ただし } F_0 = 0, F_1 = 1$$

式(2)に従って、いくつかの項を計算すると以下の値となる。

0, 1, 1, 2, 3, 5, 8, 13, 21, 34, 55, 89, 144, 233, 377, 610, 987, ...

すなわち隣り合う二項の和が次の項になる。式(2)から得られる整数値はフィボナッチ数と呼ばれ、隣り合う二つのフィボナッチ数の比率は式(3)で示される値へ収束する。

$$\lim_{n \rightarrow \infty} \frac{F_n}{F_{n-1}} = 1.618033988749895 = \varphi \quad (3)$$

この収束比率  $\varphi$  は“黄金比”と呼ばれ、古代より「最も美しい比率」であるといわれてきている。これらのフィボナッチ数や黄金比は簡単/単純に導くことができるが、動物・植物・美術等、様々なところにあらわれ、多くの興味深い性質を持っている。フィボナッチの発表から 800 年以上が経った現在でも研究が続けられている。

### 3-2. 整数論を用いた冗長アルゴリズム 逐次比較AD変換器

筆者らは 2-2節に記述した問題を解決するために整数論(フィボナッチ数列)を応用した冗長アルゴリズムを研究してきた。[3-6, 11] 多くの場合は二進探索の電圧比較重みを用いるが、このアルゴリズムではフィボナッチ数列重み付け(約1.6進)電圧比較重みを用いる。

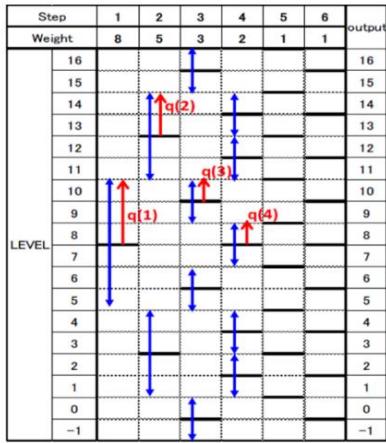

図3 4-bit 6-step のフィボナッチ数列を用いた逐次比較近似AD変換器の冗長探索アルゴリズム。

Fig.3. Redundant search algorithm of a 4-bit 6-step SAR ADC using Fibonacci sequence.

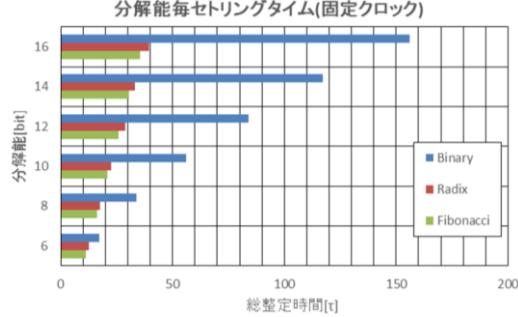

図4 各分解能でのADCの整定時間の比較

Fig.4. the comparison of the settling time of ADC at each resolution

これまでの研究 [3-6] により次のことを明らかにした。フィボナッチ数列は整数のみで構成されているため、比較電圧重みの整数への丸めが不要になる。また、(2)式より、数列の  $k$  項目は前項と前々項の加算で表されるため、 $k$  step目の補正可能範囲は  $k+1$  step目の補正可能範囲と必ず接する(図3参照)。この性質から、すべての入力値を補正する最も効率の良い設計であることがわかる。また、フィボナッチ冗長設計は補正面だけでなく速度面においても有効である。図4に分解能毎の整定時間を示した。各設計の中でフィボナッチ冗長設計が最も速いことがわかる。すなわちフィボナッチ冗長設計(radix = 約1.62)を行うことで補正面・速度面で特に優れたADCを実現できる。

しかし、比較電圧重みを変えると(R-2R抵抗ラダーのような)二進重みのDACが使えない問題が生ずる。その比較電圧重みに対応したDAC構成が必要である。以下の節でフィボナッチ数重みDACを簡単な回路で実現できることを示す。

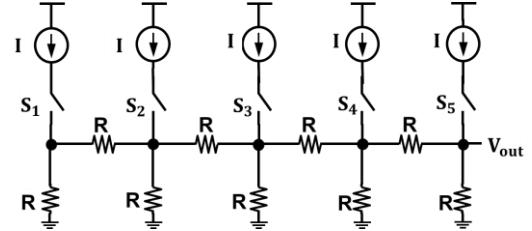

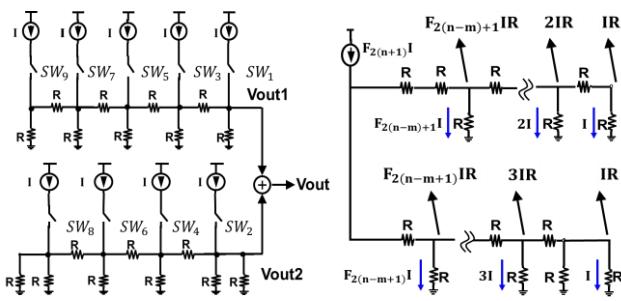

図5 提案するR終端R-RラダーDAC構成。

Fig.5. R-R ladder DAC circuit with R termination.

#### 4- フィボナッチ数列重み付けDA変換器の検討

式(2)で計算されるフィボナッチ数を再掲する(初項0は除く)。

(0, 1, 1, 2, 3, 5, 8, 13, 21, 34, 55, 89, 144, 233, 377, 610, 987,...

奇数項は次のようにになる。

$$1, 2, 5, 13, 34, 89, 233, 610, \dots$$

偶数項は次のようにになる。

$$1, 3, 8, 21, 55, 144, 377, 987, \dots$$

#### 4-1. 抵抗ネットワークによるDAC構成

##### A. R終端R-RラダーDAC構成(フィボナッチ数列奇数項重み)

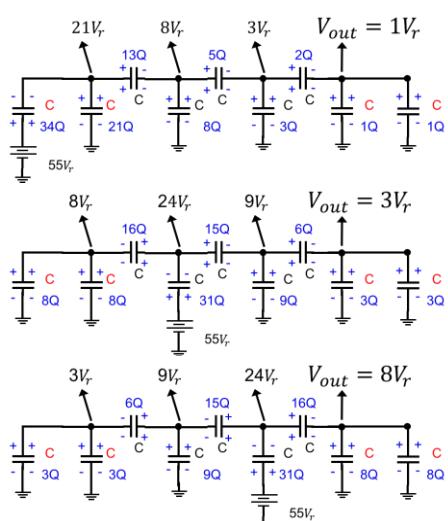

提案回路構成を図5に、その動作例を図6に示す。二進重み付けR-2Rラダーハル回路と異なり、抵抗はすべてRに変更した点である。

図6の最上段の回路では各抵抗Rにフィボナッチ数に重み付けされた電流が流れていることがわかる。また各ノードからGNDにフィボナッチ数の奇数項に重み付けされた電流が流れている、すなわち各ノードにフィボナッチ数の奇数項に重み付けされた電圧が生成されている。また、図6より電流源をVout側に一つずつノードをずらしていくと、出力電圧Voutにフィボナッチ数の奇数項に重み付けされた電圧が生じる。

電流は各ノードでフィボナッチ数( $F_x$ )に基づいて分割される。

$n$ 点ノードを持つ抵抗ラダーハル回路を考える。各ノードから右側を見たときの合成抵抗は右のノードから次のようにになる。

$$(1/1)R, (2/3)R, (5/8)R, (13/21)R, \dots$$

$$\dots, \left(\frac{F_{2(n-m)+1}}{F_{2(n-m)}}\right)R, \dots, \left(\frac{F_{2n+1}}{F_{2n}}\right)R \quad (4)$$

フィボナッチ数に基づいた抵抗比が出現する。左端のノードから電流を流した時のノード毎の電流分割は次のようにになる。

$$\left(\frac{F_{2(n-1)}}{F_{2n}}\right)I, \dots, \left(\frac{F_{2(n-m)}}{F_{2n}}\right)I, \dots, \left(\frac{21}{F_{2n}}\right)I, \left(\frac{8}{F_{2n}}\right)I, \left(\frac{3}{F_{2n}}\right)I, \left(\frac{1}{F_{2n}}\right)I \quad (5)$$

GND側へ流れる電流は次のようにになる。

$$\left(\frac{F_{2(n-1)+1}}{F_{2n}}\right)I, \dots, \left(\frac{F_{2(n-m)+1}}{F_{2n}}\right)I, \dots$$

$$\dots, \left(\frac{13}{F_{2n}}\right)I, \left(\frac{5}{F_{2n}}\right)I, \left(\frac{2}{F_{2n}}\right)I, \left(\frac{1}{F_{2n}}\right)I \quad (6)$$

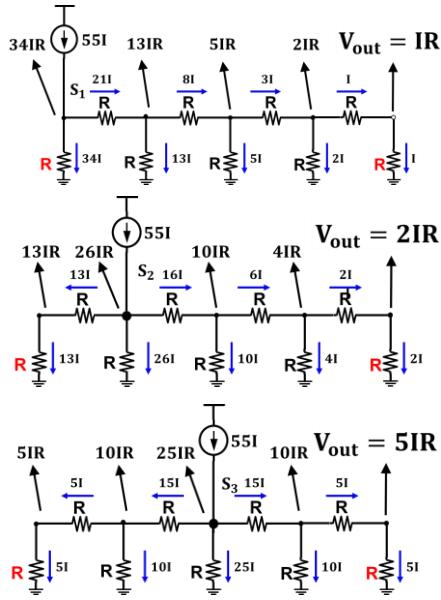

図6 R 終端 R-R ラダーDAC 動作例.

Fig.6. Operation examples of R-R ladder DAC circuit with R termination.

(5) (6) 式の分子からノード毎に電流をフィボナッチ数に基づいて、GND側と次段側に分割していることが確認できる。左側からm番目のノード電圧V(m)は次のようになる。

$$V(m) = \left( \frac{F_{2(n-m)+1}}{F_{2n}} \right) IR \quad (7)$$

分母は電流や抵抗値を調節することで取り去ることが可能である。例として図6では電流源を55Iとして用いている。

図6の回路は重ね合わせの理により、フィボナッチ数列奇数項重みDACが実現できる。

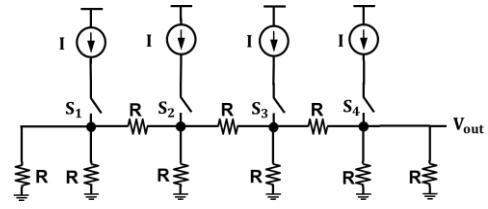

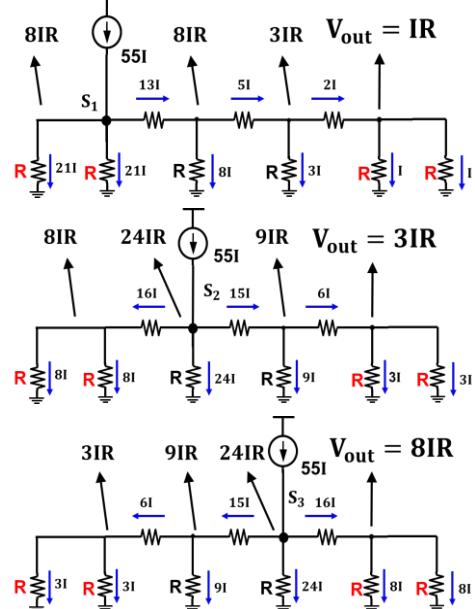

#### B. R|R 終端R-R ラダーDAC構成(フィボナッチ数列偶数項重み)

提案回路構成を図7に、その動作例を図8に示す。図6の回路では両端が抵抗Rで終端されているが、図7では両端が2つの抵抗の並列結合 R|R で終端されている。

図8に示すように各ノードからGNDにフィボナッチ数の偶数項に重み付けされた電流が流れている。すなわち各ノードの電圧がフィボナッチ数の偶数項に重み付けされた電圧が生成される。また、電流源をVout側に一つずつノードをずらしていくと、出力電圧Voutにフィボナッチ数の偶数項に重み付けされた電圧が生じる。

図7,8で各ノードから右側を見た合成抵抗は右のノードから(1/1)R, (3/2)R, (5/8)R, ...

$$\dots, \left( \frac{F_{2(n-m+1)}}{F_{2(n-m)+1}} \right) R, \dots, \left( \frac{F_{2(n+1)}}{F_{2n+1}} \right) R \quad (8)$$

図7 提案する R|R 終端 R-R ラダーDAC 構成.

Fig.7. R-R ladder DAC circuit with R|R termination.

図8 R|R 終端 R-R ラダーDAC 動作例.

Fig.8. Operation examples of R-R ladder DAC circuit with R|R termination.

左側からm番目のノード電圧V(m)は次のようになる。

$$V(m) = \left( \frac{F_{2(n-m+1)}}{F_{2(n+1)}} \right) IR \quad (9)$$

図7の回路は重ね合わせの理により、フィボナッチ数列偶数項重みDACが実現できる。

図5、図7の回路により、すべてのフィボナッチ数列重みが出力可能となった。

#### C. R-R抵抗ラダーフィボナッチ数列重みDAC構成

図5、図7の回路を組み合わせた図9左の構成の回路でフィボナッチ数列重みDACを実現できる。また、図9右の上段はRで終端され、下段はR|Rで終端されたR-Rネットワークであるが、各ノードはフィボナッチ数列重み付けされた電圧を生成することができる。この回路と容量配列を組み合わせてフィボナッチ数列重みDACを生成することができる.[11]

図 9 R-R 抵抗ラダー DA 変換器の構成

Fig.9. The DA converter configuration of the ladder resistor.

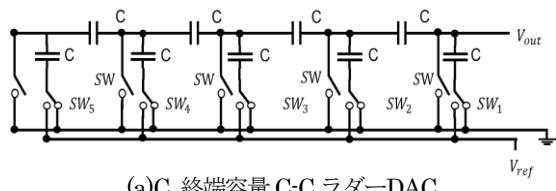

(a) C 終端容量 C-C ラダー-DAC.

(3) CTC 終端 CTC 着量ノリ DRC.

図 10 日〇〇君量ノノ BRG

#### 4.2 容量为 12 位的 DAC 模式

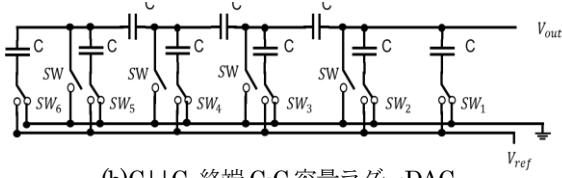

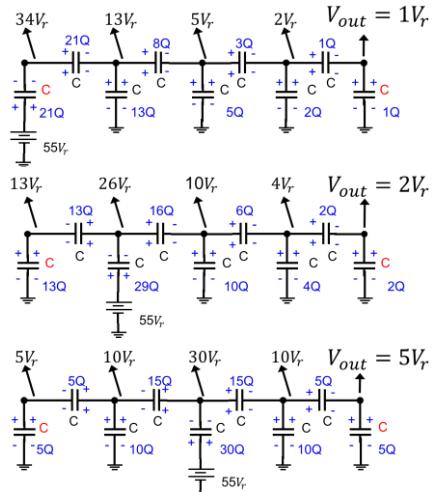

図 10 (a) に C 終端容量 C-C ラダー-DAC (フィボナッチ数列奇数項重み) の構成, 図 11 にその動作例を示す. 図 10 (b) に C || C 終端容量 C-C ラダー-DAC (フィボナッチ数列奇数項重み) の構成, 図 12 にその動作例を示す. R-R 抵抗ネットワークの場合と同じようにこれらからフィボナッチ数列重み付け DAC を構成できる.

容量ネットワークで実現できれば定常電流が流れず低消費電力化できる。一方、一端がグランドに接続していない容量を I C 内で実現し DAC に用いると両電極ノードからグランドへの寄生容量の影響で高精度 DAC の実現が難しいことに注意が必要である。

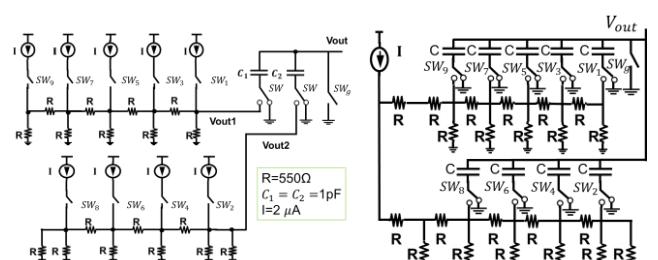

## 5- シミュレーションによる提案DAC回路の動作確認

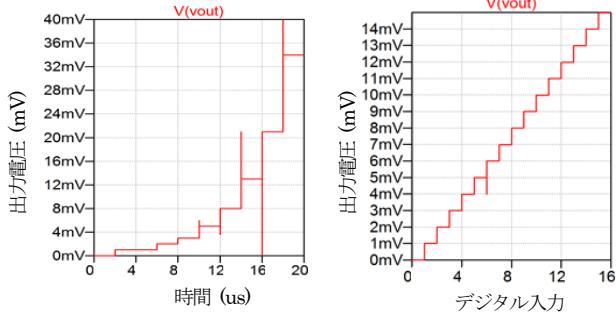

図 9 の回路のシミュレーションによる動作確認を LTSpice と Scilab の 2 つのシミュレーションソフトを用いて行った。図 13 (a)の回路では  $V_{out1}$  と  $V_{out2}$  の加算は容量を用いて実現した。 (b)の回路では容量アレイの原理で加算した。図 9 の各回路でスイッチ SW1~9 を順番に ON したときのシミュレーションを行う。 (a)の回路から得られた出力電圧のシミュレーション結果を図 14 左に示す。各回路(a), (b)において電流源値, 抵抗値, 容量はそれぞれ  $200\mu A$ ,  $550\Omega$ ,  $1\mu F$  に設定した。

図 11 C 終端 C-C 容量ラダ=DAC の動作例

Fig.11. Operation examples of C-C ladder DAC circuit with C termination

図 12 C+C 終端 C-C 容量ラダ=DAC の動作例

Fig.12. Operation examples of C-C ladder DAC circuit with  $C_1 \parallel C_2$  termination

(a)電流加算型 R-B ラダー回路 (b)単電流型 R-B ラダー回路

図 13 フィボナッチ数列重み付け DAC(図 9)

シミュレーション回路 .

図 14 フィボナッチ数列重み付け DAC(図 13)の

シミュレーション結果(DAC 出力)

Fig.14. Simulated output waveform of DAC in Fig. 13.

図 14 左の結果から各ステップでの電圧値の比を読み取ると  $0, 1, 1, 2, 3, 5, 8, 13, 21, \dots$  とフィボナッチ数に応じた出力結果が得られ、フィボナッチ重み付けができていることが確認できた。また、同様の回路で各入力値を入れることでその値に応じたアナログ値が表現でき、DAC として使用可能な回路であることも確認できる(図 14 右図参照)。

図 13(b)の回路では図 14 の 10 分の 1 の電圧の大きさでフィボナッチ重みが確認できた。使用する容量が多いためフルスケールが小さくなつたと予想されるが、どちらの回路もフィボナッチ冗長設計に用いる DAC として、有効な回路であることが確認できた。

## 6- さらなる展開

### 6-1. フィボナッチ数列の冗長性を利用したDAC線形性の向上

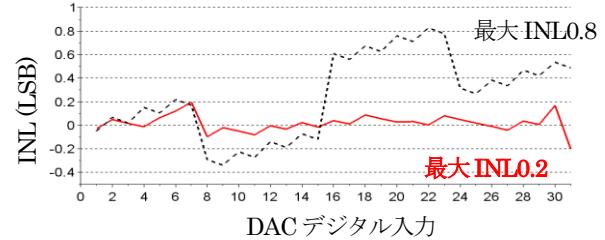

図9 の抵抗ラダーと電流源を複数使用する DAC 回路では抵抗 R 間、電流源間の電流ミスマッチが生じ、DAC 線形性が劣化する。

フィボナッチ数列ではある値を複数のパターンで表現することが可能である。筆者らはこのフィボナッチ数列の性質を利用してこの問題を軽減することを検討している。<sup>[9]</sup>

ここで各電流源に正規分布関数(平均:0、標準偏差の3倍  $3\sigma \pm 10\%$ )のばらつきを与えたときの二進重みの DA 変換器(5bit)とフィボナッチ数列 DA 変換器(図9)のステップごとの INL のシミュレーション結果を図15 に示す。結果としてバイナリの最大 INL は 0.8LSB なのに對し、フィボナッチでは最大 INL は 0.2LSB と 75% 低減出来ている。フィボナッチ数列重み付け DA 変換器を用いることで電流源ミスマッチを抑制できることが期待できる。

### 6-2. フィボナッチ数列性質利用 : SAR ロジック回路での加減算

従来手法では SAR ロジックで重み付けをしていたが、提案回路では DAC 内でフィボナッチ数重み付けができるため、ロジック回路の小規模化が期待できる。フィボナッチ数列の様々な性質<sup>[10]</sup>を利用し、SAR ロジック回路の小規模回路実現を検討している。

図 15 バイナリ(点線)/フィボナッチ(実線)DAC の

INL 比較。(シミュレーション結果)

Fig.15. INL comparison between binary and Fibonacci DACs (simulation results).

## 7- まとめ

本論文では従来の冗長アルゴリズム SAR ADC の問題を、冗長設計にフィボナッチ数列を応用することで解決できることを示した。そのフィボナッチ数列冗長設計に必要な DA 変換器を比較的簡単な回路(R-R 抵抗ネットワーク等)で実現できる方式を提案し、シミュレーションで動作を確認した。

今後はさらにフィボナッチ数列の性質を生かし、電流源や抵抗ミスマッチによる線形性劣化を低減方式、キャリブレーション方式、またこの DA 変換器を用いる SAR ロジックの基本アルゴリズムにフィボナッチ数列の性質を利用する方式を検討していきたい。

**謝辞:** 本研究をご支援いただいている半導体理工学研究センター(STARC)に感謝いたします。

## 文 献

- (1) F. Kuttner, "A 1.2V 10b 20MSample/s Non-Binary Successive Approximation ADC in 0.13μm CMOS," ISSCC (Feb. 2002)

- (2) M. Hesener, T. Eichler, A. Hanneberg, D. Herbison, F. Kuttner, H. Wenske, "A 14b 40MS/s Redundant SAR ADC with 480MHz Clock in 0.13μm CMOS," ISSCC (Feb. 2007).

- (3) T. Ogawa, H. Kobayashi, et. al., "SAR ADC Algorithm with Redundancy and Digital Error Correction", IEICE Trans. Fundamentals, vol.E93-A, no.2, pp.415-423 (Feb. 2010).

- (4) Y. Kobayashi, H. Kobayashi, "SAR ADC Algorithm with Redundancy Based on Fibonacci Sequence", IEEJ AVIC, Ho Chi Minh City, Vietnam (Oct. 2014)

- (5) 小林佑太朗, 小林春夫「逐次比較近似ADCの整数論に基づく冗長アルゴリズム設計」電気学会, 電子回路研究会, 島根 (2014年7月)

小林佑太朗, 香積正基, 楊志翔, 小林春夫「ADC/DAC のフィボナッチ数列を用いた冗長性設計の検討」電気学会 電子回路研究会, 奈良 (2013年10月)

- (7) H. Nakane, et. al., "A Fully Integrated SAR ADC Using Digital Correction Technique for Triple-Mode Mobile Transceiver," IEEE J. of Solid-State Circuits (Nov. 2014).

- (8) W. Liu, et. al., "A 12b 22.5/45MS/s 3.0mW 0.059mm<sup>2</sup>CMOS SAR ADC achieving over 90dB SFDR", ISSCC (Feb. 2010).

- (9) 楊志翔, 小林佑太朗, シャイフルニザムビンモーヤ, 小林春夫:「フィボナッチ数列を用いたDA変換回路アーキテクチャ」第4回 電気学会 東京支部 柿木・群馬支所 合同研究発表会, 桐生(2014年3月).

- (10) T. Koshy: c, Fibonacci and Lucas Numbers with Applications, John Wiley & Sons, Inc. (2001)

- (11) R. Gregorian, G. C. Temes, Analog MOS Integrated Circuits for Signal Processing, John Wiley & Sons, Inc. (1986)