### (19) **日本国特許庁(JP)**

## (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2015-95816 (P2015-95816A)

(43) 公開日 平成27年5月18日(2015.5.18)

(51) Int.Cl. FI テーマコード (参考) **HO3M 1/74 (2006.01)** HO3M 1/74 5JO22 **HO3M 1/08 (2006.01)** HO3M 1/08 B

## 審査請求 有 請求項の数 7 OL (全 30 頁)

(21) 出願番号 特願2013-235083 (P2013-235083) (22) 出願日 平成25年11月13日 (2013.11.13)

特許法第30条第2項適用申請有り ウェブサイトのアドレス: https://www.gakkai-web.net./gakkai/eiss/program/abst/MC2-5.html 掲載日:平成25年8月5日 [刊行物等] 平成25年電気学会電子・情報・システム部門大会 講演論文集 発行日:平成25年9月4日 発行所:電気学会 電子・情報・システム部門大会委員会 [刊行物等] 平成25年9月5日

(71) 出願人 396023993

株式会社半導体理工学研究センター 神奈川県横浜市港北区新横浜3丁目17番

地2 友泉新横浜ビル6階

(74)代理人 100099759

弁理士 青木 篤

(74)代理人 100092624

弁理士 鶴田 準一

(74)代理人 100114018

弁理士 南山 知広

(74)代理人 100165191

図13

弁理士 河合 章

(74)代理人 100160716

弁理士 遠藤 力

最終頁に続く

## (54) 【発明の名称】 ΔΣ D A 変調器及び ΔΣ A D 変調器

#### (57)【要約】 (修正有)

【選択図】図13

【課題】複素マルチバンドパスDA変調器を提供する。 【解決手段】複素マルチバンドパスDA変調器は、第1DA変換器11及び第2DA変換器12と、第1変換器制御部13と、第2変換器制御部14と、入力選択部15と、出力選択部16とを有する。第1変換器制御部13は、N個のポインタを使用してローパスエレメントローテーションアルゴリズムにより第1DA変換器11のセグメント素子を順次選択する。第2変換器制御部14は、N個のポインタを使用してハイパスエレメントローテーションアルゴリズムにより第2DA変換器12のセグメント素子を順次選択する。入力選択部15及び出力選択部16は、第1DA変換器11及び第2DA変換器12に入出力する信号をN個ごとに交互に選択する。

第1変換器 制御部

第1DAC 第1ポインタ

1

DAC

#### 【特許請求の範囲】

### 【請求項1】

第 1 デジタル信号を第 1 アナログ信号に D A 変調すると共に、前記第 1 デジタル信号に 直交する第 2 デジタル信号を前記第 1 アナログ信号に直交する第 2 アナログ信号に D A 変調する D A 変調器であって、

それぞれが複数のセグメント素子を有し、デジタル信号をアナログ信号に変換する第 1 DA変換器及び第 2DA変換器と、

前記第1DA変換器を制御する第1変換器制御部と、

前記第2 D A 変換器を制御する第2 変換器制御部と、

前記第1変換器制御部に前記第1デジタル信号を入力するときに前記第2変換器制御部に前記第2デジタル信号を入力し、前記第1変換器制御部に前記第2デジタル信号を入力するときに前記第2変換器制御部に前記第1デジタル信号を入力する入力選択部と、

前記第1DA変換器から前記第1アナログ信号を出力するときに前記第2DA変換器から前記第2アナログ信号を出力し、前記第1DA変換器から前記第2アナログ信号を出力するときに前記第2DA変換器から前記第1アナログ信号を出力する出力選択部と、を有し、

前記入力選択部は、前記第1デジタル信号及び前記第2デジタル信号を、2以上の整数であるN個ごとに前記第1変換器制御部及び前記第2変換器制御部に交互に入力し、

前記出力選択部は、前記第1アナログ信号及び前記第2アナログ信号を前記N個ごとに前記第1変換器制御部及び前記第2変換器制御部から交互に出力し、

前記第1変換器制御部は、入力される前記N個のデジタル信号のそれぞれに対応するN個のポインタを有し、前記N個のポインタを使用してローパスエレメントローテーションアルゴリズムにより前記第1DA変換器のセグメント素子を順次選択し、

前記第2変換器制御部は、入力される前記N個のデジタル信号のそれぞれに対応するN個のポインタを有し、前記N個のポインタを使用してハイパスエレメントローテーションアルゴリズムにより前記第2DA変換器のセグメント素子を順次選択する、

ことを特徴とする DA変調器。

#### 【請求項2】

前記第1変換器制御部は、それぞれが前記第1DA変換器の複数のセグメント素子の何れかを示すN個のポインタである第1DAC第1ポインタ~第1DAC第Nポインタを有し、前記第1DAC第1ポインタ~前記第1DAC第1ポインタ~前記第1DAC第Nポインタを順次使用し、

前記第2変換器制御部は、それぞれが前記第2DA変換器の複数のセグメント素子の何れかを示すN個のポインタである第2DAC第1ポインタ~第2DAC第Nポインタを有し、前記第2DAC第1ポインタ~前記第2DAC第1ポインタ~前記第2DAC第Nポインタを順次使用する、請求項1に記載の DA変調器。

## 【請求項3】

前記第1変換器制御部は、

入力されたデジタル信号に基づいて、選択するセグメント素子の個数を決定し、

前記第1DAC第Nポインタが示す前記第1DA変換器のセグメント素子の順方向に位置する、前記決定した個数のセグメント素子を選択し、

前記第1DAC第Nポインタが示す前記第1DA変換器のセグメント素子を、前記選択 したセグメント素子に基づいて変更する、請求項2に記載の DA変調器。

## 【請求項4】

前記第1DA変換器は、第1セグメント素子から第Mセグメント素子までのM個のセグメント素子を有し、

前記第1変換器制御部は、前記第Mセグメント素子まで順方向に順次選択したときに、次いで前記第1セグメント素子を選択する、請求項3に記載の DA変調器。

#### 【請求項5】

前記第2変換器制御部は、

10

20

30

50

40

入力されたデジタル信号に基づいて、選択するセグメント素子の個数を決定し、

前記第2DAC第Nポインタが示す前記第2DA変換器のセグメント素子の順方向又は 逆方向に位置する、前記決定した個数のセグメント素子を選択し、

前記第2DAC第Nポインタが示す前記第2DA変換器のセグメント素子を、前記選択したセグメント素子に基づいて変更し、

前記第2変換器制御部が前記第2DAC第Nポインタが示すセグメント素子の順方向に位置するセグメント素子を選択した場合、次に前記第2DAC第Nポインタを使用するときには、前記第2DAC第Nポインタが示す前記第2DA変換器のセグメント素子の逆方向に位置するセグメント素子を選択し、

前記第2変換器制御部が前記第2DAC第Nポインタが示すセグメント素子の逆方向に位置するセグメント素子を選択した場合、次に前記第2DAC第Nポインタを使用するときには、前記第2DAC第Nポインタが示す前記第2DA変換器のセグメント素子の順方向に位置するセグメント素子を選択する、請求項2~4の何れか一項に記載の DA変調器。

#### 【請求項6】

前記第2DA変換器は、第1セグメント素子から第Mセグメント素子までのM個のセグ メント素子を有し、

前記第2変換器制御部は、前記第Mセグメント素子まで順方向に順次選択したときに、更に順方向に選択する場合は前記第1セグメント素子を選択し、前記第1セグメント素子まで逆方向に順次選択したときに、更に逆方向に選択する場合は前記第Mセグメント素子を選択する、請求項5に記載の DA変調器。

#### 【請求項7】

第1アナログ信号を第1デジタル信号にAD変調すると共に、前記第1アナログ信号に直交する第2アナログ信号を前記第1デジタル信号に直交する第2デジタル信号にAD変調する AD変調器であって、

前記第1デジタル信号を第1フィードバック信号にDA変調すると共に、前記第2デジタル信号を第2フィードバック信号にDA変調するDA変調器と、

前記第1アナログ信号から前記第1フィードバック信号を減算する第1減算器と、

前 記 第 2 ア ナ ロ グ 信 号 か ら 前 記 第 2 フ ィ ー ド バ ッ ク 信 号 を 減 算 す る 第 2 減 算 器 と 、

前記第1減算器及び前記第2減算器の出力信号をフィルタリングする複素マルチバントパスフィルタと、

前記複素マルチバントパスフィルタがフィルタリングした信号を前記第 1 デジタル信号 に A D 変換する第 1 A D 変換器と、

前記複素マルチバントパスフィルタがフィルタリングした信号を前記第2デジタル信号 にAD変換する第2AD変換器と、を有し、

前記 D A 変調器は、請求項 1 ~ 6 の何れか一項に記載の D A 変調器である、ことを特徴とする A D 変調器。

【発明の詳細な説明】

### 【技術分野】

[00001]

本発明は、 DA変調器及び AD変調器に関する。

## 【背景技術】

#### [0002]

携帯電話や無線LAN等の通信システムのRF受信回路に、マルチバンドパスフィルタを用いた 変調器を適用することが検討されている。特許文献1、及び非特許文献1には、複数のセグメント素子と、複数のセグメント素子に順番に入力デジタル信号が供給されるように重み付けポインタを備えたDA変換器を有する 変調器が記載されている。このDA変換器では、マルチビットDACの特性からもたらされる非線形ノイズを効率的に除去することが可能である。

### [0003]

10

20

30

また、RF受信回路に、複素バンドパス AD変換器を適用することが検討されている。特許文献 2、並びに非特許文献 2及び 3には、第1DA変換器及び第2DA変換器と、マルチプレクサ手段と、第1論理回路手段及び第2論理回路手段とを備えるDA変調器が記載される。この変調器では、マルチプレクサ手段は、第1デジタル信号及び第2の第2ので第2ののでは、アナログ信号を得るように制御する。また、第1計を担けられるのでは、第1DA変換器及び第2DA変換器の前段に設けられる。第1論理回路手段及び第1日の路手段は、第1デジタル信号に対してハイパスエレメントローション法を用いる一方、第2のデジタル信号に対してローパスエレメントローション法を用いて複素ディジタルフィルタを実現する。また、第1論理回路手段及び第2論理回路手段は、第1コーション法を用いて複素ディジタルフィルタを実現する。また、第1論理回路手段及び第2論理回路手段は、第1コージョン法を用いて複素ディジタルフィルタを実現する。また、第1に対してロージョン法を用いて複素ディジタルフィルタを実現する。また、第1に対してロージフィルタを実現する。このDA変換器では、第1DA変換器及び第2DA変換器の非線形性を実質的にノイズシェープすることができる。

【先行技術文献】

【特許文献】

[0004]

【特許文献 1 】特表 2 0 0 7 - 0 6 6 4 3 1 号公報

【特許文献2】特開2006-13705号公報

【非特許文献】

[0005]

【非特許文献1】元澤篤史、萩原 広之、山田 佳央、小林 春夫、小室 貴紀、傘 昊、「マルチバンドパス 変調器技術とその応用」、電子情報通信学会誌 和文誌 C vol. J9 0-C, no.2, pp.143-158 (2007年2月).

【非特許文献 2】H. San, H. Kobayashi, S. Kawakami, N. Kuroiwa, 「A Noise-Shaping Algorithm of Multi-bit DAC Nonlinearities in Complex Bandpass AD Modulators」, IEICE Trans. on Fundamentals, E87-A, no. 4, pp.792-800 (April. 2004).

【非特許文献 3】H. San, A. Hagiwara, A. Motozawa, H. Kobayashi 「DWA Algorithms for Multibit Complex Bandpass — AD Modulators of Arbitrary Signal Band」,IEEJ International Analog VLSI Workshop, Hangzhou, China (Nov. 2006).

【発明の概要】

【発明が解決しようとする課題】

[0006]

消費電力をより低くするために、AD変調器及びDA変調器をそれぞれ、マルチビット 変調器で実現することが望まれている。AD変調器をマルチビット 変調器で実現すると、増幅器のスルーレート要求が緩和されるので、増幅器の消費電力を低くすることができる。また、DA変調器マルチビット 変調器で実現すると、量子化雑音が低減されることにより、DA変調器の後段に配置されるアナログフィルタの要求が緩和される。しかしながら、複素デジタル信号をマルチビットでDA変調する複素マルチバンドパスDA変調器は実現されていなかった。

[0007]

そこで、本発明は、複素デジタル信号をマルチビットでDA変調する複素マルチバンドパスDA変調器を提供することを目的とする。

【課題を解決するための手段】

[0008]

上記目的を実現するため、本発明に係る DA変調器は、第1デジタル信号を第1アナログ信号にDA変換すると共に、第1デジタル信号に直交する第2デジタル信号を第1アナログ信号に直交する第2アナログ信号にDA変換する DA変調器であって、それぞれが複数のセグメント素子を有し、デジタル信号をアナログ信号に変換する第1DA変換器及び第2DA変換器と、第1DA変換器を制御する第1変換器制御部と、第2DA変換器を制御する第2変換器制御部と、第1変換器制御部に第1デジタル信号を入力すると

10

20

30

40

20

30

40

50

#### [0009]

さらに、本発明に係る DA変調器では、第1変換器制御部は、それぞれが第1DA変換器の複数のセグメント素子の何れかを示すN個のポインタである第1DAC第1ポインタ~第1DAC第1ポインタを有し、第1DAC第Nポインタを順次使用し、第2変換器制御部は、それぞれが第2DA変換器の複数のセグメント素子の何れかを示すN個のポインタである第2DAC第1ポインタ~第2DAC第Nポインタを有し、第2DA変換器は、デジタル信号が入力されるごとに、第2DAC第1ポインタ~第2DAC第Nポインタを順次使用することが好ましい。

#### [0010]

さらに、本発明に係る DA変調器では、第1変換器制御部は、入力されたデジタル信号に基づいて、選択するセグメント素子の個数を決定し、第1DAC第Nポインタが示す第1DA変換器のセグメント素子の順方向に位置する、決定した個数のセグメント素子を選択し、第1DAC第Nポインタが示す第1DA変換器のセグメント素子を、選択したセグメント素子に基づいて変更することが好ましい。

## [ 0 0 1 1 ]

さらに、本発明に係る DA変調器では、第1DA変換器は、第1セグメント素子から第Mセグメント素子までのM個のセグメント素子を有し、第1変換器制御部は、第Mセグメント素子まで順方向に順次選択したときに、次いで第1セグメント素子を選択することが好ましい。

## [ 0 0 1 2 ]

さらに、本発明に係る DA変調器では、第2変換器制御部は、入力されたデジタル信号に基づいて、選択するセグメント素子の個数を決定し、第2DAC第Nポインタが示す第2DA変換器のセグメント素子の順方向又は逆方向に位置する、決定した個数のセグメント素子を選択し、第2DAで類器制御部が第2DAC第Nポインタが示すセグメント素子に基づいて変更し、第2変換器制御部が第2DAC第Nポインタが示すセグメント素子の順方向に位置するセグメント素子を選択した場合、次に第2DAC第Nポインタを使用するときには、第2DAC第Nポインタが示すセグメント素子の逆方向に位置するセグメント素子を選択し、第2変換器制御部が第2DAC第Nポインタが示すセグメント素子の逆方向に位置するセグメント素子を選択した場合、次に第2DAC第Nポインタを使用するときには、第2DAC第Nポインタが示す第2DA変換器のセグメント素子の順方向に位置するセグメント素子を選択することが好ましい。

## [0013]

さらに、本発明に係る DA変調器では、第2DA変換器は、第1セグメント素子から第Mセグメント素子までのM個のセグメント素子を有し、第2変換器制御部は、第Mセ

20

30

40

50

グメント素子まで順方向に順次選択したときに、更に順方向に選択する場合は第1セグメント素子を選択し、第1セグメント素子まで逆方向に順次選択したときに、更に逆方向に 選択する場合は第Mセグメント素子を選択することが好ましい。

[0014]

上記目的を実現するため、本発明に係る A D 変調器は、第1アナログ信号を第1デジタル信号にA D 変調すると共に、第1アナログ信号に直交する第2アナログ信号を第1 デジタル信号に直交する第2デジタル信号に A D 変調する A D 変調器であって、第1デジタル信号を第1フィードバック信号に D A 変調 B と、第1アナログ信号から第1フィードバック信号に D A 変調器と、第1アナログ信号から第1フィードバック信号に D A 変調器と、第1アナログ信号から第1フィードバック信号を減算する第1減算器と、第2アナログ信号から第2フィードバック信号を減算する第1減算器と、第2アナログ信号をフィルタリングする複素マルチバントパスフィルタリングする複素マルチバントパスフィルタリングした信号を第1デジタル信号に A D 変換器と、複素マルチバントパスフィルタがフィルタがフィルタリングした信号を第1 A D 変換器と、複素マルチバントパスフィルタがフィルタがフィルタがフィルタリングした信号を第1 A D 変換器と、複素マルチバントパスフィルタがフィルタリングした信号を第2デジタル信号に A D 変換する第2 A D 変換器と、を有し、第1日 A 変調器及び第2 D A 変調器はそれぞれ、上述の D A 変調器の何れかであることを特徴とする。

【発明の効果】

[0015]

本発明に係るDA変調器では、複素デジタル信号をマルチビットでDA変調する複素マルチバンドパスDA変調器を提供することが可能になった。

【図面の簡単な説明】

[0016]

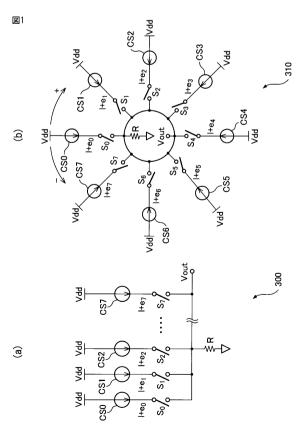

【図1】(a)はセグメント電流セル型DA変換器の回路図であり、(b)は(a)に示すセグメント電流セル型DA変換器の素子をリング状に配置した回路図である。

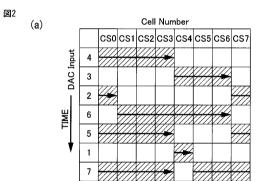

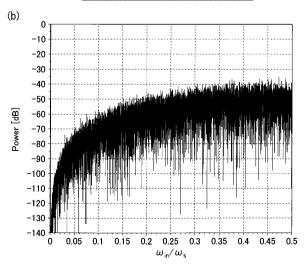

【 図 2 】 ( a ) はローパスエレメントローテーションアルゴリズムを概略的に示す図であり、 ( b ) はローパスエレメントローテーションアルゴリズムを使用した D A 変換器のパワースペクトラムの一例を示す図である。

【図3】(a)はハイパスエレメントローテーションアルゴリズムを概略的に示す図であり、(b)はハイパスエレメントローテーションアルゴリズムを使用した D A 変換器のパワースペクトラムの一例を示す図である。

【図4】(a)は複素バンドパス DA変調器の回路ブロック図であり、(b)は(a)に示す複素共振器の内部回路図であり、(c)は(b)に示す複素共振器のパワースペクトラムの一例を示す図である。

【図 5 】(a)は 2 次複素バンドパス D A 変調器の回路ブロック図であり、(b)は(a)に示す 2 次複素バンドパス D A 変調器のパワースペクトラムの一例を示す図である。

【図6】(a)は複素バンドパス DA変調器の他の例の回路ブロック図であり、(b)は(a)に示す DA変換器の動作アルゴリズムを示す図であり、(c)は、(a)に示す複素バンドパス AD変調器の具体的な回路構成を示す回路ブロック図である。

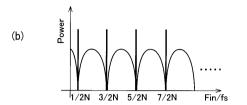

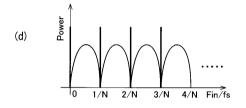

【図 7 】 (a) はマルチバンドパス AD 変調器の一例の回路ブロック図であり、(b) は (a) に示すマルチバンドパス AD 変調器のパワースペクトラムの一例を示す図であり、(c) はマルチバンドパス AD 変調器の他の例の回路ブロック図であり、(d) は (c) に示すマルチバンドパス AD 変調器のパワースペクトラムの一例を示す図である。

【図8】(a)は2次マルチバンドパス DA変調器の一例の回路ブロック図であり、(b)は(a)に示す2次マルチバンドパス DA変調器の信号帯域中心周波数を示す図であり、(c)は、(a)に示す2次マルチバンドパス DA変調器で使用されるローパスエレメントローテーションアルゴリズムの一例を示す図であり、(d)は(a)に示す2次マルチバンドパス DA変調器のパワースペクトラムの一例を示す図であり、(e)は(a)に示す2次マルチバンドパス DA変調器のパワースペクトラムの他の

20

30

40

50

例を示す図である。

【図9】(a)は2次マルチバンドパス DA変調器の他の例の回路ブロック図であり、(b)は(a)に示す2次マルチバンドパス DA変調器の信号帯域中心周波数を示す図であり、(c)は、(a)に示す2次マルチバンドパス DA変調器で使用されるハイパスエレメントローテーションアルゴリズムの一例を示す図であり、(d)は(a)に示す2次マルチバンドパス DA変調器のパワースペクトラムの一例を示す図であり、(e)は(a)に示す2次マルチバンドパス DA変調器のパワースペクトラムの他の例を示す図である。

【図10】(a)は2次複素マルチバンドパス DA変調器の回路ブロック図であり、 (b)は(a)に示す2次複素マルチバンドパス DA変調器のノイズが略ゼロになる 信号帯域を示す図であり、(c)は(a)に示す2次複素マルチバンドパス DA変調器の等価回路である。

【図11】第1実施形態に係る複素マルチバンドパス 変調器の回路ブロック図である

【図 1 2 】図 1 1 に示す複素マルチバンドパス 変調器の動作アルゴリズムを示す図である。

【図 1 3 】図 1 1 に示す複素マルチバンドパス 変調器の具体的な回路構成を示す回路 ブロック図である。

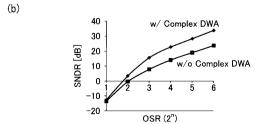

【図14】(a)は図11に示す複素マルチバンドパス 変調器のパワースペクトラムの一例を示す図であり、(b)は図11に示す複素マルチバンドパス 変調器のOSRに対するSNDRの値のシミュレーション結果を示す図である。

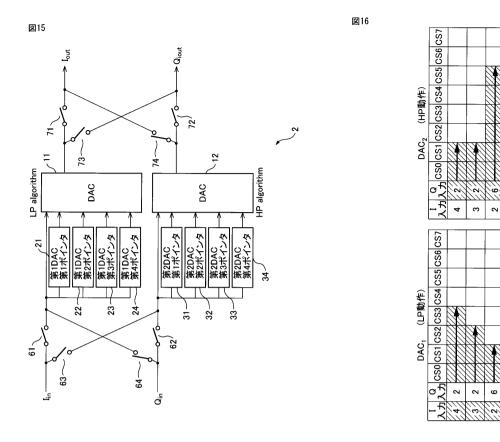

【図15】第2実施形態に係る複素マルチバンドパス 変調器の回路ブロック図である

【図 1 6 】図 1 5 に示す複素マルチバンドパス 変調器の動作アルゴリズムを示す図である。

【図 1 7 】図 1 5 に示す複素マルチバンドパス 変調器の具体的な回路構成を示す回路 ブロック図である。

【図18】(a)は図15に示す複素マルチバンドパス 変調器のパワースペクトラムの一例を示す図であり、(b)は図15に示す複素マルチバンドパス 変調器のOSRに対するSNDRの値のシミュレーション結果を示す図である。

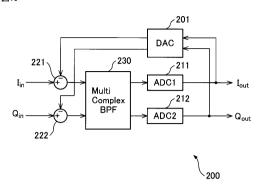

【図19】第3実施形態に係る複素マルチバンドパス 変調器の回路ブロック図である

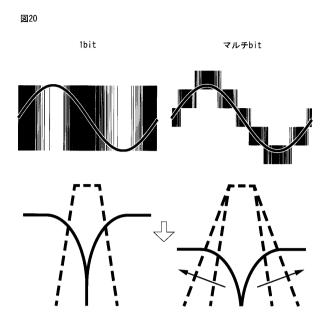

【図 2 0 】実施形態に係る複素マルチバンドパス 変調器の特徴を説明する図である。 【発明を実施するための形態】

[0017]

以下図面を参照して、本発明に係るDA変調器及びAD変調器について説明する。但し、本発明の技術的範囲はそれらの実施の形態に限定されず、特許請求の範囲に記載された発明との均等物に及ぶ点に留意されたい。

[0018]

本発明に係るDA変調器及びAD変調器について説明する前に、本発明に係るDA変調器及びAD変調器に関連する技術について説明する。

[0019]

まず、 A D 変調器用 D W A (Data-Weighted-Averaging) アルゴリズムの第 1 のアルゴリズムであるローパスエレメントローテーションアルゴリズム及び第 2 のアルゴリズムであるハイパスエレメントローテーションアルゴリズムについて説明する。

[0020]

図1(a)はセグメント電流セル型DA変換器の回路図であり、図1(b)は図1(a)に示すセグメント電流セル型DA変換器の素子をリング状に配置した回路図である。

[ 0 0 2 1 ]

セグメント電流セル型 D A 変換器 3 0 0 は、第 1 電流源 C S 0 ~ 第 8 電流源 C S 7 と、

20

30

40

50

電流源に直列接続された第1スイッチS0~第8スイッチS7とを有する。第1電流源CS0~第8電流源CS7は、大きさが互いに等しい電流を流す電流源であることが望まれるが、半導体装置に搭載される場合には製造プロセスのバラツキ等により、第1電流源CS0~第8電流源CS7の電流の大きさは相違する。図1(a)に示す例では、第1電流源CS0の電流の大きさは $I+e_0$ であり、第2電流源CS1の電流の大きさは $I+e_1$ であり、第8電流源CS7の電流の大きさは $I+e_7$ である。図1(a)において、 $e_0$ ~ $e_7$ はミスマッチ値であり、I0 の 変換器の非線形性を示すものである。

## [0022]

セグメント電流セル型 D A 変換器 3 0 0 に入力されるデジタル信号に応じて第 1 電流源 C S 0 から順に電流源を使用する場合、第 1 電流源 C S 0 ~第 8 電流源 C S 7 の電流値の大きさは相違する。例えば、「2」を示すデジタル信号が入力されたときに第 1 電流源 C S 0 及び第 2 電流源 C S 1 をオンするので出力電流の大きさは 2 I + ( $e_0$ +  $e_1$ )となる。また、「4」を示すデジタル信号が入力されたときに第 1 電流源 C S 0 ~第 4 電流源 C S 3 をオンするので出力電流の大きさは 4 I + ( $e_0$ +  $e_1$ +  $e_2$ +  $e_3$ )となる。入力されるデジタル信号に応じて出力電流の大きさが相違することに起因してノイズが発生するため特性が悪化し、セグメント電流セル型 D A 変換器 3 0 0 のパワースペクトルは平坦になる。

## [0023]

セグメント電流セル型 D A 変換器 3 1 0 は、第 1 電流源 C S 0 ~ 第 8 電流源 C S 7 をリング状に配置したものである。セグメント電流セル型 D A 変換器 3 1 0 において、第 1 電流源 C S 0 ~ 第 8 電流源 C S 7 の何れかを順方向に選択することができる。第 1 電流源 C S 0 ~ 第 8 電流源 C S 7 の何れかを順方向に選択するとき、第 1 スイッチ S 0 ~ 第 8 スイッチ S 7 を順次オンして、第 1 電流源 C S 0 ~ 第 8 電流源 C S 7 を順次選択する。第 1 電流源 C S 0 ~ 第 8 電流源 C S 7 の何れかを逆方向に選択するとき、第 8 スイッチ S 7 ~ 第 1 スイッチ S 0 を順次オンして、第 8 スイッチ S 7 ~ 第 1 スイッチ S 0 を順次 選択する。

## [0024]

図 2 ( a ) はローパスエレメントローテーションアルゴリズムを概略的に示す図であり、図 2 ( b ) はローパスエレメントローテーションアルゴリズムを使用した D A 変換器のパワースペクトラムの一例を示す図である。

#### [0025]

ローパスエレメントローテーションアルゴリズムでは、先に入力されたデジタル信号に応じて使用した電流源を記憶して、次いで入力されたデジタル信号に応じて使用「44」では、次定する。図2(cs0~第4電流源CS3を使用では、まずでは、第1電流源CS3をでは、第1電流源CS3を使用する。次明して、第5電流源CS4~第1電流源CS6を使用する。次明して、第5電流源CS4~第一方向に2個の電流源を順次ときに、同ったので、「第1電流源CS0を使用する。次明でで、第1電流源CS0を使用する。次に第1電流源CS0を使用する。次にで、第2を使用する。次に第1電流源CS0を使用する。次にで、第2を使用する。次に第1電流源CS0~第8である。次にで、第2電流源CS1~第1でより、第2電流源CS0~第8での電流源を順次メントローテーションアルゴリズムでは、使用する電流源を順次選択することにより、図2(b)に示される。第1電流源CS0~第8電流源CS0~第1で、第1でのミスマッチは1次ノイズシェープされる。

## [0026]

図 3 ( a ) はハイパスエレメントローテーションアルゴリズムを概略的に示す図であり、図 3 ( b ) はハイパスエレメントローテーションアルゴリズムを使用した D A 変換器のパワースペクトラムの一例を示す図である。

## [0027]

(9)

ハイパスエレメントローテーションアルゴリズムでは、先に入力されたデジタル信号に応じて使用する。次いで使用した電流源を記憶して、次いに決定する。図3(a)に示す例では、まずを反対方向に交互に順次選択するように決定する。図3(a)に示す例では、ますを反対方向に交互に順次選択するように、第1電流源CS3~第4電流源CS3を使用する。次いで、「3」を示すデジタル信号が入力されたときに、逆方向に3個の「2」を源を順次選択して、第2電流源CS1~第4電流源CS3を使用する。次いで、第2電流源CS1~第3電流源CS2を使用する。次にで、第1電流源CS1~第3電流源CS2を使用する。次にで、第1電流源CS5~第8電流源CS7とを使用する。図1(b)に示すように、第6電流源CS7がリング状に配置されており、第1電流源CS9第8電流源CS7とが隣接するためである。このように、ハイパスエレメントローテーションが状に配置されており、第1電流源に第1で、第1では、近辺により、図3(b)に示することが隣接するためである。このように、ハイパスエレメントローテーションが表に、カープされる。

[0028]

図4(a)は複素バンドパス DA変調器の回路ブロック図であり、図4(b)は図4(a)に示す複素共振器の内部回路図であり、図4(c)は図4(b)に示す複素共振器のパワースペクトラムの一例を示す図である。

[0029]

複素バンドパス DA変調器400の入出力関係は、以下のように示される。

【数1】

$$I_{out} + jQ_{out} = \frac{H(z)}{1 + H(z)} (I_{in} + jQ_{in}) + \frac{1}{1 + H(z)} (E_i + jE_q) \quad (1)$$

ここで、 $I_{in}$ は入力信号の同相成分であり、 $Q_{in}$ は入力信号の直交成分であり、 $I_{out}$ は出力信号の同相成分であり、 $Q_{out}$ は出力信号の直交成分である。また、H(z)は複素共振器 40 1 の伝達関数であり、 $E_{i}$ はノイズの同相成分であり、 $E_{q}$ はノイズの直交成分である。式(1)において、信号伝達関数 S T F(z)及びノイズ伝達関数 N T F(z) はそれぞれ、

【数2】

$$STF(z) := \frac{H(z)}{1 + H(z)} \qquad (2)$$

$NTF(z) := \frac{1}{1 + H(z)} \quad (3)$

で示される。また、複素共振器401の伝達関数H(z)は、

30

10

20

30

40

50

【数3】

$$H(z)=rac{eta+jlpha}{z-(eta+jlpha)}$$

=  $rac{e^{j heta}}{z-e^{j heta}}$  (  $an heta=rac{lpha}{eta}$  )

で示される。複素共振器401の伝達関数 H ( z )が大きくなると、信号伝達関数 S T F ( z )は1に漸近し、ノイズ伝達関数 N T F ( z )は略ゼロになり、複素バンドパス D A 変調器400の出力信号のノイズを略ゼロにすることができる。

[0030]

図 5 ( a ) は 2 次 複素 バンドパス D A 変調器の回路 ブロック図であり、図 5 ( b ) は図 5 ( a ) に示す 2 次 複素 バンドパス D A 変調器 のパワースペクトラムの一例を示す図である。

[0031]

2 次複素バンドパス DA変調器 4 1 0 は、直列接続された 2 個の複素共振器 4 1 1 及び 4 1 2 を有する。このような構成を有することにより、 2 次複素バンドパス DA変調器 4 1 0 は、標本化周波数を上げることができると共に、オーバーサンプリング効果により、複素バンドパス DA変調器 4 0 0 よりも SNR (Signal-to-noise ratio)が改善される。

[ 0 0 3 2 ]

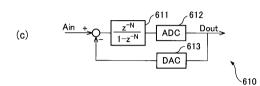

図 6 ( a ) は複素バンドパス D A 変調器の他の例の回路ブロック図であり、図 6 ( b ) は図 6 ( a ) に示す D A 変換器の動作アルゴリズムを示す図である。また、図 6 ( c ) は、図 6 ( a ) に示す複素バンドパス A D 変調器の具体的な回路構成を示す回路プロック図である。

[0033]

複素バンドパス DA変調器 500は、第1DA変換器 501と第2DA変換器 502と、第1ポインタ 511と、第2ポインタ 512と、第1入力スイッチ 521~第4入 カスイッチ 524と、第1出力スイッチ 531~第4出力スイッチ 534とを有する。複素バンドパス DA変調器 500は第1デジタル信号  $I_{in}$ を第1アナログ信号  $I_{out}$ に変換すると共に、第2デジタル信号  $I_{in}$ を第2アナログ信号  $I_{out}$ に変換する。

[0034]

第1DA変換器501は、図1(b)に示すように第1電流源CS0~第8電流源CS7がリング状に配置されており、ローパスエレメントローテーションアルゴリズムにより、入力されたデジタル信号をアナログ信号に順次変換する。第2DA変換器502は、図1(b)に示すように第1電流源CS0~第8電流源CS7がリング状に配置されており、ハイパスエレメントローテーションアルゴリズムにより、入力されたデジタル信号をアナログ信号に順次変換する。第1ポインタ511は第1DA変換器501に先に入力されたデジタル信号に応じて使用した電流源を記憶し、第2ポインタ512は第2DA変換器502に先に入力されたデジタル信号に応じて使用した電流源を記憶する。

20

30

40

50

#### [0035]

第1入力スイッチ521~第4入力スイッチ524は、第1DA変換器501に第1デジタル信号  $I_{in}$ を入力するときに第2DA変換器502に第2デジタル信号  $Q_{in}$ を入力する。この場合、第1入力スイッチ521及び第2入力スイッチ522がオンし、第3入力スイッチ523及び第4入力スイッチ524がオフする。また、第1入力スイッチ521~第4入力スイッチ524は、第2DA変換器502に第1デジタル信号  $I_{in}$ を入力するときに第1DA変換器501に第2デジタル信号  $I_{in}$ を入力する。この場合、第1入力スイッチ521及び第2入力スイッチ522がオフし、第3入力スイッチ523及び第4入力スイッチ521 ながオンする。第1入力スイッチ521~第4入力スイッチ524は、第1デジタル信号  $I_{in}$  及び第2デジタル信号  $I_{in}$  ので第2デジタル信号  $I_{in}$  が入力されるごとに、入力信号を交互に切り替える。

#### [0036]

第1出力スイッチ531~第4出力スイッチ534は、第1DA変換器501から第1アナログ信号  $I_{out}$ を出力するときに第2DA変換器502から第2アナログ信号  $Q_{out}$ を出力する。この場合、第1出力スイッチ531及び第2出力スイッチ532がオンし、第3出力スイッチ533及び第4出力スイッチ534がオフする。また、第1出力スイッチ531~第4出力スイッチ534は、第2DA変換器502から第1アナログ信号  $I_{out}$ を出力するときに第1DA変換器501から第2アナログ信号  $Q_{out}$ を出力する。この場合、第1出力スイッチ531及び第2出力スイッチ532がオフし、第3出力スイッチ533及び第4出力スイッチ534がオンする。第1入力スイッチ521~第4入力スイッチ524は、第1アナログ信号  $I_{out}$  及び第2アナログ信号  $Q_{out}$  が出力されるごとに、出力信号を交互に切り替える。

### [0037]

図6(b)を参照して、複素バンドパス DA変調器500の動作アルゴリズムを説明する。まず、複素バンドパス DA変調器500に「4+3j」が入力される。第1入力スイッチ521~第4入力スイッチ524は、「4」を第1デジタル信号 Iin として第1DA変換器501に入力し、「3」を第2デジタル信号 Qin として第2DA変換器502に入力する。第1DA変換器501は、第1電流源CS0~第4電流源CS3を使用して「4」を示す第1デジタル信号 Iinをアナログ信号に変換する。第2DA変換器502は、第1電流源CS0~第3電流源CS2を使用して「3」を示す第2デジタル信号 Qinをアナログ信号に変換する。第1ポインタ511は第4電流源CS3を記憶し、第2ポインタ512は第3電流源CS2を記憶する。第1出力スイッチ531~第4出力スイッチ534は、第1DA変換器501が変換した「4」を示すアナログ信号を第1アナログ信号 Ioutとして出力し、第2DA変換器502が変換した「3」を示すアナログ信号を第2アナログ信号 Qoutとして出力する。

### [0038]

[0039]

次いで、複素バンドパス DA変調器 500に「2+5j」が入力される。第1入力スイッチ 521~第4入力スイッチ 524は、「2」を第1デジタル信号  $I_{in}$ として第2 DA変換器 502に入力し、「5」を第2デジタル信号  $Q_{in}$ として第1 DA変換器 501に入力する。第1 DA変換器 501は、第1ポインタ 511に記憶される第4電流源 CS3から順方向の 5個の電流源である第1電流源 CS0及び第5電流源 CS4~第8電流源 CS7を使用して「5」を示す第2デジタル信号  $I_{in}$ をアナログ信号に変換する。第2 DA変換器 502は、第2ポインタ 512に記憶される第3電流源 CS2から逆方向の2個の電流源である第2電流源 CS1~第3電流源 CS2を使用して「2」を示す第2デジタル信号  $Q_{in}$ をアナログ信号に変換する。第1ポインタ 511は第1電流源 CS1を記憶する。第1出力スイッチ 531~第4出力スイッチ 534は、第2DA変換器 502が変換した「2」を示すアナログ信号を第1アナログ信号  $Q_{out}$ として出力する。

複素バンドパス DA変調器 500では、第1DA変換器 501と第2DA変換器 502とに第1デジタル信号  $I_{in}$  及び第2デジタル信号  $Q_{in}$  をそれぞれ、交互に入力するように第1入力スイッチ 521~第4入力スイッチ 524を動作させるように制御する。第1DA変換器 501はローパスエレメントローテーションアルゴリズムを適用するように制御される一方、第2DA変換器 502はハイパスエレメントローテーションアルゴリズムを適用するように制御される。このような構成を採用することにより、複素バンドパスDA変調器 500は、第1DA変換器 501及び第2DA変換器 502の非線形性により生じるノイズをノイズシェープすることができる。

[0040]

複素バンドパス D A 変調器 5 0 0 の 具体的な 回路構成を示す複素バンドパス A 変調器 5 5 0 は、第 1 D A 変換器 5 0 1 と、第 2 D A 変換器 5 0 2 と、第 1 変換器制御 部 5 5 1 と、 第 2 変 換 器 制 御 部 5 5 2 と を 有 す る 。 複 素 バ ン ド パ ス は、入力選択部553と、出力選択部554とを更に有する。第1変換器制御部551は 、入力されるデジタル信号に応じてローパスエレメントローテーションアルゴリズムによ り 第 1 D A 変 換 器 5 0 1 の 複 数 の セ グ メン ト 素 子 を 順 次 選 択 す る 。 第 2 変 換 器 制 御 部 5 5 2 は、入力されるデジタル信号に応じてハイパスエレメントローテーションアルゴリズム により 第 2 D A 変 換 器 5 0 2 の 複 数 の セ グ メン ト 素 子 を 順 次 選 択 す る 。 入 力 選 択 部 5 5 3 は、第1入力スイッチ521~第4入力スイッチ524の機能を実現する。すなわち、入 力 選 択 部 5 5 3 は 、 第 1 変 換 器 制 御 部 5 5 1 に 第 1 デ ジ タ ル 信 号 Ii゚ を 入 力 す る と き に 第 2 変換器制御部 5 5 2 に第 2 デジタル信号 Q inを入力する。また、入力選択部 5 5 3 は、 第 2 変換器制御部 5 5 2 に第 1 デジタル信号 I inを入力するときに第 1 変換器制御部 5 5 1 に 第 2 デ ジ タ ル 信 号 Q <sub>i n</sub> を 入 力 す る 。 入 力 選 択 部 5 5 3 は 、 第 1 デ ジ タ ル 信 号 I <sub>i n</sub> 及 び 第 2 デジタル信号 Q in が入力されるごとに、入力信号を交互に切り替える。出力選択部 5 5 4 は、第 1 出力スイッチ 5 3 1 ~ 第 4 出力スイッチ 5 3 4 の機能を実現する。出力選択 部 5 5 4 は、第 1 D A 変換器 5 0 1 から第 1 アナログ信号 I outを出力するときに第 2 D A 変換器 5 0 2 に第 2 アナログ信号 Q out を出力する。また、出力選択部 5 5 4 は、第 2 D A 変換器 5 0 2 から第 1 アナログ信号 I <sub>out</sub>を出力するときに第 1 D A 変換器 5 0 1 か ら第2アナログ信号Q。utを出力する。出力選択部554は、第1アナログ信号 I。ut及び 第 2 アナログ信号 Q outが出力されるごとに、出力信号を交互に切り替える。

[0041]

図7(a)はマルチバンドパス AD変調器の一例の回路ブロック図であり、図7(b)は図7(a)に示すマルチバンドパス AD変調器のパワースペクトラムの一例を示す図である。また、図7(c)はマルチバンドパス AD変調器の他の例の回路ブロック図であり、図7(d)は図7(c)に示すマルチバンドパス AD変調器のパワースペクトラムの一例を示す図である。

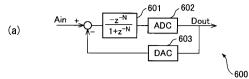

[0042]

マルチバンドパス A D 変調器 6 0 0 は、フィルタ 6 0 1 と、 A D 変換器 6 0 2 と、 D A 変換器 6 0 3 とを有する。フィルタ 6 0 1 の伝達関数 H (z)は、

【数4】

$H(z) = \frac{-z^{-N}}{1 + z^{-N}}$

であり、マルチバンドパス AD変調器600の出力信号Y(z)は、 【数5】

$$Y(z) = X(z) \cdot \left(-z^{-N}\right) + E(z) \cdot \left(1 + z^{-N}\right)$$

10

20

30

で示され、マルチバンドパス AD変調器600の信号伝達関数STF(z)及びノイズ伝達関数NTF(z)はそれぞれ、

【数6】

$$STF = \frac{Y(z)}{X(z)} = -z^{-N}$$

$$NTF = \frac{Y(z)}{E_n(z)} = 1 + z^{-N}$$

10

で示される。マルチバンドパス AD変調器600の信号伝達関数STF(z)が「1」であり、ノイズ伝達関数NTF(z)が「0」である複数の信号帯域中心周波数f<sub>n</sub>はサンプリング周波数f<sub>s</sub>を用いて、図7(b)に示すように、

【数7】

$$f_{2n-1} = \frac{2n-1}{2N} f_s,$$

$$n = \begin{cases} 1, 2, \dots, \frac{N+1}{2} & (N: 奇数) \\ 1, 2, \dots, \frac{N}{2} & (N: 偶数) \end{cases}$$

20

となる。

## [0043]

マルチバンドパス AD変調器 6 1 0 は、フィルタ 6 1 1 と、 AD変換器 6 1 2 と、 DA変換器 6 1 3 とを有する。フィルタ 6 1 1 の伝達関数 H(z)は、

【数8】

30

$$H(z) = \frac{z^{-N}}{1 - z^{-N}}$$

であり、マルチバンドパス AD変調器 6 1 0 の出力信号 Y (z)は、 【数 9】

$$Y(z) = X(z) \cdot z^{-N} + E(z) \cdot (1 - z^{-N})$$

40

で示され、マルチバンドパス AD変調器610の信号伝達関数STF(z)及びノイズ伝達関数NTF(z)はそれぞれ、

#### 【数10】

$$STF = \frac{Y(z)}{X(z)} = z^{-N}$$

$$NTF = \frac{Y(z)}{E(z)} = 1 - z^{-N}$$

で示される。信号伝達関数 S T F ( z ) が「 1 」であり、ノイズ伝達関数 N T F ( z ) が「 0 」である複数の信号帯域中心周波数  $f_n$ はサンプリング周波数  $f_s$ を用いて、図 7 ( d ) に示すように、

## 【数11】

$$f_{2n} = rac{2n}{2N} f_s = rac{n}{N} f_s,$$

$$n = \left\{ egin{array}{ll} 0, 1, 2, \dots, rac{N-1}{2} & (N: 奇数) \\ 0, 1, 2, \dots, rac{N}{2} & (N: 偶数) \end{array}

ight.$$

となる。

## [0044]

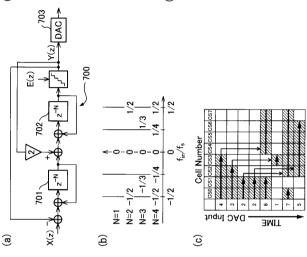

図8(a)は2次マルチバンドパス DA変調器の一例の回路ブロック図であり、図8(b)は図8(a)に示す2次マルチバンドパス DA変調器の信号帯域中心周波数を示す図である。図8(c)は、図8(a)に示す2次マルチバンドパス DA変調器で使用されるローパスエレメントローテーションアルゴリズムの一例を示す図である。図8(d)は図8(a)に示す2次マルチバンドパス DA変調器のパワースペクトラムの一例を示す図であり、図8(e)は図8(a)に示す2次マルチバンドパス DA変調器のパワースペクトラムの他の例を示す図である。

#### [0045]

2 次マルチバンドパス DA変調器 7 0 0 はフィルタ 7 0 1 及び 7 0 2 と DA変換器 7 0 3 とを有する。 DA変換器 7 0 3 は、図 1 (b)に示すように素子がリング状に配置されたセグメント電流セル型 DA変換器である。 2 次マルチバンドパス DA変調器 7 0 0 の出力信号 A out は、

【数12】

$$A_{out}(Z) = Z^{-2N}X(Z) + (1 - Z^{-N})^2 E(Z) + (1 - Z^{-N})\delta(Z)$$

で示される。

## [0046]

図 8 ( c ) を参照して、N = 4、すなわち 4 次のフィルタに対応する 2 次マルチバンドパス D A 変調器で使用されるローパスエレメントローテーションアルゴリズムについて説明する。 D A 変換器 7 0 3 は第 1 ポインタ~第 4 ポインタを有し、第 1 ポインタ~第 4 ポインタがそれぞれ、入力されたデジタル信号に応じてローパスエレメントローテーションアルゴリズムを実行する。

### [0047]

まず、「4」を示すデジタル信号が入力されたときに、第1電流源CS0~第4電流源

10

20

30

40

CS3を使用し、第4電流源CS3を第1ポインタが記憶する。次いで、「3」を示すデジタル信号が入力されたときに、3個の電流源を順次選択して、第1電流源CS0~第3電流源CS2を使用し、第3電流源CS2を第2ポインタが記憶する。次いで、「2」を示すデジタル信号が入力されたときに、2個の電流源を順次選択して、第1電流源CS0と第2電流源CS2を使用し、第2電流源CS1を第3ポインタが記憶する。次いで、「2」を示すデジタル信号が入力されたときに、2個の電流源を順次選択して、第1電流源CS0と第2電流源CS2を使用し、第2電流源CS1を第4ポインタが記憶する。

次いで、「6」を示すデジタル信号が入力されたときに、第1ポインタに記憶される第4電流源CS3の順方向に位置する6個の電流源である第5電流源CS4~第2電流源CS1を第1ポインタが記憶する。次いで、「1」を示すデジタル信号が入力されたときに、第2ポインタに記憶される第3電流源CS3を第2ポインタが記憶する。次いで、「7」を示すデジタル信号が入力されたときに、第3ポインタが記憶する。次いで、「7」を示すデジタル信号が入力されたときに、第3ポインタに記憶される第2電流源CS1の順方向に位置する7個の電流源である第3電流源CS2~第1電流源CS0を使用し、第1電流源CS0を第3ポインタが記憶する。次いで、「5」を示すデジタル信号が入力されたときに、第4ポインタが記憶する。第2電流源CS1の順方向に位置する5個の電流源である第3電流源CS2~第7電流源CS6を使用し、第7電流源CS6を第4ポインタが記憶する。

[0049]

[0048]

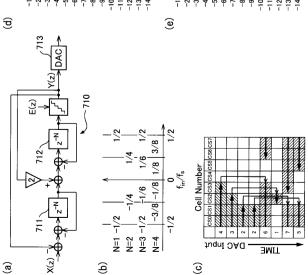

図9(a)は2次マルチバンドパス DA変調器の他の例の回路ブロック図であり、図9(b)は図9(a)に示す2次マルチバンドパス DA変調器の信号帯域中心周波数を示す図である。図9(c)は、図9(a)に示す2次マルチバンドパス DA変調器で使用されるハイパスエレメントローテーションアルゴリズムの一例を示す図である。図9(d)は図9(a)に示す2次マルチバンドパス DA変調器のパワースペクトラムの一例を示す図であり、図9(e)は図9(a)に示す2次マルチバンドパス DA変調器のパワースペクトラムの他の例を示す図である。

[0050]

2 次マルチバンドパス DA変調器 7 1 0 はフィルタ 7 1 1 及び 7 1 2 と DA変換器 7 1 3 とを有する。 DA変換器 7 1 3 は、図 1 (b)に示すように素子がリング状に配置されたセグメント電流セル型 DA変換器である。 2 次マルチバンドパス DA変調器 7 1 0 の出力信号 A out は、

【数13】

$A_{out}(Z) = Z^{-2N}X(Z) + (1 + Z^{-N})^2 E(Z) + (1 + Z^{-N})\delta(Z)$

で示される。

[0051]

図9(c)を参照して、N=4、すなわち4次のフィルタに対応する2次マルチバンドパス DA変調器で使用されるハイパスエレメントローテーションアルゴリズムについて説明する。DA変換器713は第1ポインタ~第4ポインタを有し、第1ポインタ~第4ポインタがそれぞれ、入力されたデジタル信号に応じてハイパスエレメントローテーションアルゴリズムを実行する。

[0052]

まず、「4」を示すデジタル信号が入力されたときに、第1電流源CSO~第4電流源CS3を使用し、第4電流源CS3を第1ポインタが記憶する。次いで、「3」を示すデジタル信号が入力されたときに、3個の電流源を順次選択して、第1電流源CSO~第3電流源CS2を使用し、第3電流源CS2を第2ポインタが記憶する。次いで、「2」を

10

20

30

40

示すデジタル信号が入力されたときに、2個の電流源を順次選択して、第1電流源CS0と第2電流源CS2とを使用し、第2電流源CS1を第3ポインタが記憶する。次いで、「2」を示すデジタル信号が入力されたときに、2個の電流源を順次選択して、第1電流源CS0と第2電流源CS2とを使用し、第2電流源CS1を第4ポインタが記憶する。 【0053】

次いで、「6」を示すデジタル信号が入力されたときに、第1ポインタに記憶される第4電流源CS3から逆方向に位置する6個の電流源である第1電流源CS0~第4電流源CS3及び第7電流源CS6~第8電流源CS7を使用する。そして、第6電流源CS5を第1ポインタが記憶する。次いで、「1」を示すデジタル信号が入力されたときに、第3ポインタが記憶される第3電流源CS2を使用し、第3電流源CS2を使用し、第3電流源CS2を前2ポインタが記憶される第2電流源CS3を第3ポインタに記憶される第2電流源CS1から逆方向に位置する7個の電流源である第1電流源CS3~第8電流源CS1から逆方向に位置する5個の電流源である第1電流源CS1を明まる。次いで、「5」を示すデジタル信号が入力されたときに、第4ポインタに記憶する。次いで、「5」を示すデジタル信号が入力されたときに、第4ポインタが記憶する。で、第8電流源CS1を使用する。そして、第6電流源CS1を第4ポインタが記憶する。

#### [0054]

図4~6を参照して説明された複素バンドパス AD変調器は、1次複素フィルタを使用するものである。また、図7~9を参照して説明されたマルチバンドパス AD変調器は、実信号をN次フィルタでフィルタリングするものであり、複素フィルタを使用するものではない。本発明の発明者らは、これらの AD変調器に基づき、複素マルチバンドパス AD変調器、及び複素マルチバンドパス AD変調器に適用されるDWAアルゴリズムを発明した。

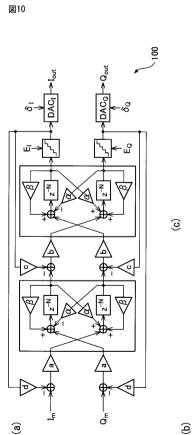

## [0055]

図 1 0 (a) は 2 次複素マルチバンドパス DA変調器の回路ブロック図であり、図 1 0 (b) は図 1 0 (a) に示す 2 次複素マルチバンドパス DA変調器のノイズが略ゼロになる信号帯域を示す図である。また、図 1 0 (c) は、図 1 0 (a) に示す 2 次複素マルチバンドパス DA変調器の等価回路である。

#### [0056]

2 次 D A 変調器 1 0 0 の出力信号 ( I <sub>out</sub> + j Q <sub>out</sub> ) は、 【数 1 4 】

$$l_{out} + jQ_{out} = Z^{-2N}(I_{in} + jQ_{in}) + (j - Z^{-N})^{2}(E_{I} + jE_{Q}) + (j - Z^{-N})(\delta_{I} + j\delta_{Q}).$$

で示される。ここで、 $I_{in}$ は入力信号の同相成分であり、 $Q_{in}$ は入力信号の直交成分であり、 $I_{out}$ は出力信号の同相成分であり、 $Q_{out}$ は出力信号の直交成分である。また、 $E_{in}$ は量子化ノイズの同相成分であり、 $E_{in}$ は量子化ノイズの直交成分であり、 $I_{in}$ はDA変換器のノイズの同相成分であり、 $I_{in}$ はDA変換器のノイズの同相成分であり、 $I_{in}$

## [0057]

2次 DA変調器100の等価回路101は、第1DA変換器11と、第2DA変換器12と、複素共振器102と、複素ノッチ103とを有する。2次 DA変調器100の等価回路101では、DA変換器のノイズの同相成分 DA変調器100の等価回路101では、DA変換器のノイズの 直交成分 Qは、複素ノッチ103に影響する。2次 DA変調器100の等価回路101は、第1DA変換器11及び第2DA変換器12に入力されるデジタル信号が無限大になる可能性があるため、実現することができない。

10

20

30

20

30

40

50

#### [0058]

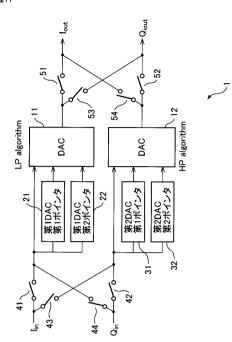

図 1 1 は、第 1 実施形態に係る複素マルチバンドパス 変調器の回路ブロック図である。

### [0059]

DA変調器1は、第1DA変換器11と、第2DA変換器12と、第1DAC第1ポインタ21と、第1DAC第2ポインタ22と、第2DAC第1ポインタ31と、第2DAC第2ポインタ32とを有する。 DA変調器1は、第1入力スイッチ41~第4入力スイッチ44と、第1出力スイッチ51~第4出力スイッチ54とを更に有する。

## [0060]

第1DA変換器11は図6を参照して説明した第1DA変換器501と同様な機能及び構成を有し、第2DA変換器12は図6を参照して説明した第2DA変換器502と同様な機能及び構成を有する。すなわち、第1DA変換器11は、図1(b)に示すように第1電流源CS0~第8電流源CS7がリング状に配置されており、ローパスエレメントローテーションアルゴリズムにより、入力されたデジタル信号をアナログ信号に順次変換する。第2DA変換器12は、図1(b)に示すように第1電流源CS0~第8電流源CS7がリング状に配置されており、ハイパスエレメントローテーションアルゴリズムにより、入力されたデジタル信号をアナログ信号に順次変換する。

## [0061]

第1DAC第1ポインタ21及び第1DAC第2ポインタ22はそれぞれ、第1DA変換器11に先に入力されたデジタル信号に応じて使用した電流源を記憶する。第2DAC第1ポインタ31及び第2DAC第2ポインタ32はそれぞれ、第2DA変換器12に先に入力されたデジタル信号に応じて使用した電流源を記憶する。

## [0062]

第1入力スイッチ41~第4入力スイッチ44は、第1DA変換器11に第1デジタル信号 Iinを入力するときに第2DA変換器12に第2でがオンし、第3入力スイッチ41のの第2人力スイッチ41のの第3人力スイッチ41がオフする。また、第1入力するときに第1でがオンし、第3人力スイッチ44がオフする。また、第1人力するときに第1DA変換入力スイッチ41ので第1日の場合、第1人力スイッチ41がオフする。この場合、第1人力スイッチ41がオフロ、第1人力スイッチ41がオフロ、第1人力スイッチ44がオフロ、第1人力スイッチ44がが第2でが第1日の第1でが2分力スイッチ41~第4人力スイッチ44は、2個の第1デジタル信号 Qinを第12に入力スイッチ41~第4人人力スイッチ41とに入力し、2個の第2でジタル信号 Qinを第12に入力スイッチ44は、2個の第1でジタル信号 Qinを第1日への第1でジタル信号 Qinを第1日への第2でジタル信号 Qinを第1日への第1でジタル信号 Qinを第1日への第2でジタル信号 Qinを第1日の第1でジタル信号 Qinを第1日の第1でジタル信号 Qinを第1日の第1でジタル信号 Qinを第1日の第1でジタル信号 Qinを第1日の第1に入力し、切替動作を再度実行する。

#### [0063]

第1出力スイッチ51~第4出力スイッチ54は、第1DA変換器11から第1アナログ信号 I outを出力するときに第2DA変換器12から第2アナログ信号 Q outを出力する。この場合、第1出力スイッチ51及び第2入力スイッチ52がオンし、第3出力スイッチ53及び第4出力スイッチ54がオフする。また、第1出力スイッチ51~第4出力スイッチ54は、第2DA変換器12から第1アナログ信号 I outを出力するときに第1DA変換器11から第2アナログ信号 Q outを出力する。この場合、第1出力スイッチ51及び第2入力スイッチ52がオフし、第3出力スイッチ53及び第4出力スイッチ51ながオンする。第1出力スイッチ51~第4出力スイッチ54は、第1アナログ信号 I out 及び第2アナログ信号 Q outが2対出力されるごとに、出力信号を交互に切り替える。すなわち、第1出力スイッチ51~第4出力スイッチ54は、2個の第1アナログ信号 I out を第1DA変換器11から出力し、2個の第2アナログ信号 Q out を第2DA変換器12から出力すると、切替動作を実行する。切替動作を実行した後、第1出力スイッチ51~

20

30

40

50

第 4 出力スイッチ 5 4 は、 2 個の第 1 アナログ信号 I <sub>ou t</sub> を第 2 D A 変換器 1 2 から出力し、 2 個の第 2 アナログ信号 Q <sub>ou t</sub> を第 1 D A 変換器 1 1 から出力し、切替動作を再度実行する。

[0064]

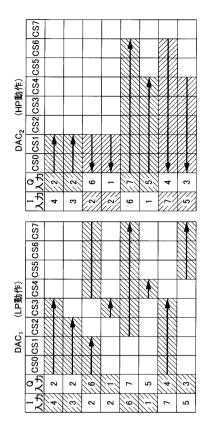

図12は、 DA変調器1の動作アルゴリズムを示す図である。

[0065]

まず、 DA変調器1に「4+2j」が入力される。第1入力スイッチ41~第4入力スイッチ44は、「4」を第1デジタル信号Iinとして第1DA変換器11に入力し、「2」を第2デジタル信号Qinとして第2DA変換器12に入力する。第1DA変換器11は、第1電流源CS0~第4電流源CS3を使用して「4」を示す第1デジタル信号Iinをアナログ信号に変換する。第2DA変換器12は、第1電流源CS0~第2電流源CS1を使用して「2」を示す第2デジタル信号Qinをアナログ信号に変換する。第1DAC第1ポインタ21は第4電流源CS3を記憶し、第2DAC第1ポインタ31は第2電流源CS1を記憶する。第1出力スイッチ51~第4出力スイッチ54は、第1DA変換器11が変換した「4」を示すアナログ信号を第1アナログ信号Ioutとして出力し、第2DA変換器12が変換した「2」を示すアナログ信号を第2アナログ信号Qoutとして出力する。

[0066]

次いで、 DA変調器1に「3+2j」が入力される。第1入力スイッチ41~第4入力スイッチ44は、「3」を第1デジタル信号Iinとして第1DA変換器11に入力し、「2」を第2デジタル信号Qinとして第2DA変換器12に入力する。第1DA変換器11は、第1電流源CS0~第3電流源CS2を使用して「3」を示す第1デジタル信号 Iinをアナログ信号に変換する。第2DA変換器12は、第1電流源CS0~第2電流源CS1を使用して「2」を示す第2デジタル信号Qinをアナログ信号に変換する。第1DAC第2ポインタ22は第3電流源CS2を記憶し、第2DAC第2ポインタ32は第2電流源CS1を記憶する。第1出力スイッチ51~第4出力スイッチ54は、第1DA変換器11が変換した「3」を示すアナログ信号を第1アナログ信号Ioutとして出力し、第2DA変換器12が変換した「2」を示すアナログ信号を第2アナログ信号Qoutとして出力する。

[0067]

次いで、 DA変調器1に「2+6j」が入力される。第1入力スイッチ41~第4入力スイッチ44は、「2」を第1デジタル信号Iinとして第2DA変換器12に入力する。第1DA変換器11に入力する。第1DA変換器11は、第1DAC第1ポインタ21に記憶される第4電流源CS3から順方向に位置する第1電流源CS0~第2電流源CS1及び第5電流源CS4~第8電流源CS7を使用して「6」を示す第2デジタル信号Iinをアナログ信号に変換する。第2DA変換器12は、第2DAC第1ポインタ31に記憶される第2電流源CS1から逆方向の2個の電流源である第1電流源CS1~第2電流源CS1を使用して「2」を示す第2デジタル信号 Qinをアナログ信号に変換する。第1DAC第1ポインタ21は第2電流源CS1を記憶し、第2DAC第1ポインタ31は第1電流源CS0を記憶する。第1出力スイッチ51~第4出力スイッチ54は、第2DA変換器12が変換した「2」を示すアナログ信号を第1アナログ信号Ioutとして出力し、第1DA変換器11が変換した「6」を示すアナログ信号を第2アナログ信号Qoutとして出力する。

[0068]

次いで、 DA変調器 1 に「2+1 j」が入力される。第 1 入力スイッチ 4 1 ~第 4 入力スイッチ 4 4 は、「2」を第 1 デジタル信号  $I_{in}$ として第 2 DA変換器 1 2 に入力し、「1」を第 2 デジタル信号  $Q_{in}$ として第 1 DA変換器 1 1 に入力する。第 1 DA変換器 1 1 は、第 1 DAC第 2 ポインタ 2 2 に記憶される第 3 電流源 CS 2 から順方向に位置する第 4 電流源 CS 3 使用して「1」を示す第 2 デジタル信号  $I_{in}$ をアナログ信号に変換する。第 2 DA変換器 1 2 は、第 2 DAC第 2 ポインタ 3 2 に記憶される第 2 電流源 CS 1

20

30

40

50

から逆方向の2個の電流源である第1電流源CS1~第2電流源CS1を使用して「2」を示す第2デジタル信号Q<sub>in</sub>をアナログ信号に変換する。第1DAC第2ポインタ22は第4電流源CS3を記憶し、第2DAC第2ポインタ32は第1電流源CS0を記憶する。第1出力スイッチ51~第4出力スイッチ54は、第2DA変換器12が変換した「2」を示すアナログ信号を第1アナログ信号I<sub>out</sub>として出力し、第1DA変換器11が変換した「1」を示すアナログ信号を第2アナログ信号Q<sub>out</sub>として出力する。

[0069]

第1DA変換器11と第2DA変換器12に第1デジタル信号 Iin 及び第2デジタル信号 Qin をそれぞれ、2対ずつ交互に入力するように第1入力スイッチ41~第4入力スイッチ44を動作させるように制御する。また、第1DA変換器11と第2DA変換器12で変換されたアナログ信号を変第1デジタル信号 Iin 及び第2デジタル信号 Qin として、2対ずつ交互に出力するように第1出力スイッチ51~第4出力スイッチ54を動作させるように制御する。第1DA変換器11は、第1デジタル信号 Iin を2個アナログ信号に変換する。第2DA変換器12な、第1DA変換器11が第1デジタル信号 Iin をアナログ信号に変換する。第2DA変換器12が多ル信号 Qin をアナログ信号に変換すると、第1デジタル信号 Iin をアナログ信号に変換すると、第1デジタル信号 Iin をアナログ信号に変換する。

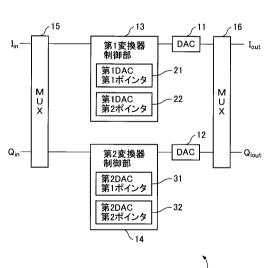

[0070]

図13は、 DA変調器1の具体的な回路構成を示す回路ブロック図である。

[0071]

DA変調器1は、第1DA変換器11と、第2DA変換器12と、第1変換器制御部13と、第2変換器制御部14と、入力選択部15と、出力選択部16とを有する。

[0072]

第 1 変 換 器 制 御 部 1 3 は 、 第 1 D A C 第 1 ポ イ ン タ 2 1 及 び 第 1 D A C 第 2 ポ イ ン タ 2 2を使用して、入力されるデジタル信号に応じてローパスエレメントローテーションアル ゴリズムにより第1DA変換器11の複数のセグメント素子を順次選択する。第2変換器 制 御 部 1 4 は 、 第 2 D A C 第 1 ポ イ ン タ 3 1 及 び 第 2 D A C 第 2 ポ イ ン タ 3 2 を 使 用 し て 、入力されるデジタル信号に応じてハイパスエレメントローテーションアルゴリズムによ り 第 2 D A 変 換 器 5 0 2 の 複 数 の セ グ メ ン ト 素 子 を 順 次 選 択 す る 。 入 力 選 択 部 1 5 は 、 第 1 入力スイッチ 4 1 ~ 第 4 入力スイッチ 4 4 の機能を実現する。すなわち、入力選択部 1 5 は、 第 1 D A 変換器 1 1 に第 1 デジタル信号 I <sub>i n</sub>を入力するときに第 2 D A 変換器 1 2 に第2デジタル信号Qinを入力する。また、入力選択部15は、第2DA変換器12に第 する。入力選択部 1 5 は、第 1 デジタル信号 I in 及び第 2 デジタル信号 Q in が 2 対入力さ れるごとに、入力信号を交互に切り替える。出力選択部16は、第1出力スイッチ51~ 第 4 出 力 ス イ ッ チ 5 4 の 機 能 を 実 現 す る 。 出 力 選 択 部 1 6 は 、 第 1 D A 変 換 器 1 1 か ら 第 1 アナログ信号 I outを出力するときに第 2 D A 変換器 1 2 に第 2 アナログ信号 Q outを出 力 す る 。 ま た 、 出 力 選 択 部 1 6 は 、 第 2 D A 変 換 器 1 2 か ら 第 1 ア ナ ロ グ 信 号 I 。 。 , を 出 力 す る と き に 第 1 D A 変 換 器 1 1 か ら 第 2 ア ナ ロ グ 信 号 Q <sub>o u t</sub> を 出 力 す る 。 出 力 選 択 部 1 6 は、第 1 アナログ信号 I <sub>out</sub> 及び第 2 アナログ信号 Q <sub>out</sub> が 2 対出力されるごとに、出力 信号を交互に切り替える。

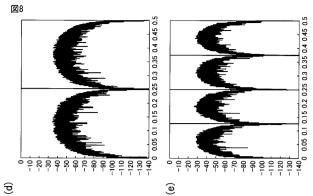

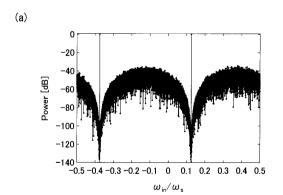

[0073]

図14(a)は、 DA変調器1のパワースペクトラムの一例を示す図である。また、図14(b)は、 DA変調器1のOSR(Over sampling Ratio)に対するSNDR(Signal-to-noise and distortion ratio)の値のシミュレーション結果を示す図である。図14(b)において、四角はDWAアルゴリズムを適用しない場合を示し、ひし形はDWAアルゴリズムを適用した DA変調器1のシミュレーション結果を示す。

[0074]

図 1 4 (a)に示すように、 DA変調器 1 は信号帯域のノイズが低減されている。

20

30

40

50

また、図14(b)に示すように、 DA変調器1は、DWAアルゴリズムを適用しない場合と比較して良好なSNDRが得られる。

#### [0075]

## [0076]

DA変調器2は、第1DA変換器11と、第2DA変換器12と、第1DAC第1ポインタ21~第1DAC第4ポインタ24と、第2DAC第1ポインタ31~第2DAC第4ポインタ31~第4入力スイッチ61~第4入力スイッチ61~第4入力スイッチ61~第1出力スイッチ64と、第1DAC第1ポインタ22とに加えて、カカスイッチ64とで第1ポインタ21と第1DAC第2ポインタ22とに加えて、第1DAC第3ポインタ22とに加えて、第1DAC第3ポインタ33と第1DAC第3ポインタ33と第2DAC第4ポインタ33とまとが、 ロA変調器1と相違する。また、 ロA変調器1とを有することが、 ロA変調器1と更に相違する。また、 ロA変調器2は、第1入力スイッチ41~第4入力スイッチ44の代わりに、第1入カスイッチ61~第4入カスイッチ64が配置されることが、 ロA変調器1と更に相違する。オッチ71~第4出力スイッチ51~第4出力スイッチ54の代わりに、第1出力スイッチ51~第4出力スイッチ54の代わりに、第1出力スイッチ51~第4出力スイッチ54の代わりに、第1出記する。

#### [0077]

第1DAC第3ポインタ23及び第1DAC第4ポインタ24はそれぞれ、第1DA変換器11に先に入力されたデジタル信号に応じて使用した電流源を記憶する。第2DAC第3ポインタ33及び第2DAC第4ポインタ34はそれぞれ、第2DA変換器12に先に入力されたデジタル信号に応じて使用した電流源を記憶する。

#### [0078]

第1入力スイッチ61~第4入力スイッチ64は、入力信号を交互に切り替える周期が第1入力スイッチ41~第4入力スイッチ44と相違する。第1入力スイッチ61~第4入力スイッチ64は、第1デジタル信号 Iin 及び第2デジタル信号 Qin が4対入力されるごとではなく、第1デジタル信号 Iin 及び第2デジタル信号 Qin が4対入力されるごとに入力信号を交互に切り替える。すなわち、第1入力スイッチ61~第4入力スイッチ64は、4個の第1デジタル信号 Iin を第1DA変換器11に入力し、4個の第2デジタル信号 Qin を第2DA変換器12に入力すると、切替動作を実行する。切替動作を実行した後、第1入力スイッチ61~第4入力スイッチ64は、4個の第1デジタル信号 Iin を第2DA変換器12に入力し、4個の第2デジタル信号 Qin を第1DA変換器11に入力し、切替動作を再度実行する。

## [0079]

第1出力スイッチ71~第4出力スイッチ74は、入力信号を交互に切り替える周期が第1出力スイッチ51~第4出力スイッチ54と相違する。第1出力スイッチ71~第4出力スイッチ74は、第1アナログ信号  $I_{out}$  及び第2アナログ信号  $Q_{out}$  が4対出力されるごとに、出力信号を交互に切り替える。すなわち、第1出力スイッチ71~第4出力スイッチ74は、4個の第1アナログ信号  $I_{out}$  を第1DA変換器11から出力し、4個の第2アナログ信号  $Q_{out}$  を第2DA変換器12から出力すると、切替動作を実行する。切替動作を実行した後、第1出力スイッチ71~第4出力スイッチ74は、4個の第1アナログ信号  $I_{out}$  を第2DA変換器12から出力し、4個の第2アナログ信号  $Q_{out}$  を第1DA変換器11から出力し、切替動作を再度実行する。

### [080]

図16は、 DA変調器2の動作アルゴリズムを示す図である。

## [ 0 0 8 1 ]

D A 変調器 2 では、第 1 D A 変換器 1 1 と第 2 D A 変換器 1 2 とに第 1 デジタル信

[0082]

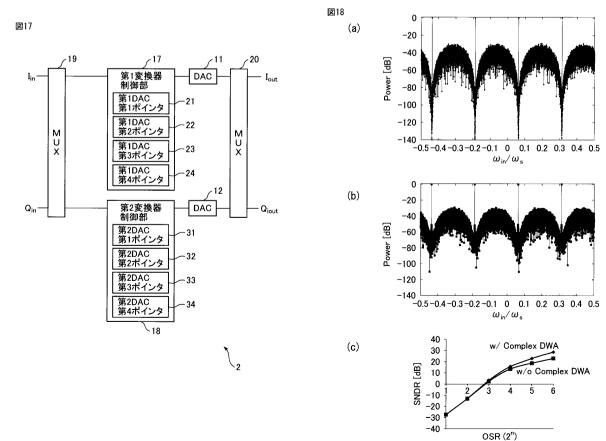

図17は、 DA変調器2の具体的な回路構成を示す回路ブロック図である。

[0083]

DA変調器1は、第1DA変換器11と、第2DA変換器12と、第1変換器制御部17と、第2変換器制御部18と、入力選択部19と、出力選択部20とを有する。

[0084]

第 1 変換器制御部 1 7 は、 4 個のポインタを使用して、入力されるデジタル信号に応じ てローパスエレメントローテーションアルゴリズムにより第1DA変換器11の複数のセ グ メ ン ト 素 子 を 順 次 選 択 す る 。 第 2 変 換 器 制 御 部 1 8 は 、 4 個 の ポ イ ン タ を 使 用 し て 、 入 力されるデジタル信号に応じてハイパスエレメントローテーションアルゴリズムにより第 2 D A 変換器 5 0 2 の複数のセグメント素子を順次選択する。入力選択部 1 9 は、第 1 入 力 ス イ ッ チ 6 1 ~ 第 4 入 力 ス イ ッ チ 6 4 の 機 能 を 実 現 す る 。 す な わ ち 、 入 力 選 択 部 1 9 は 、 第 1 D A 変換器 1 1 に第 1 デジタル信号 I <sub>i n</sub>を入力するときに第 2 D A 変換器 1 2 に第 2 デジタル信号 Q in を入力する。また、入力選択部15は、第2DA変換器12に第1デ ジ タ ル 信 号 Ii。 を 入 力 す る と き に 第 1 D A 変 換 器 1 1 に 第 2 デ ジ タ ル 信 号 Qi。 を 入 力 す る 。入力選択部19は、第1デジタル信号Iin及び第2デジタル信号Qinが4対入力される ごとに、入力信号を交互に切り替える。出力選択部20は、第1出力スイッチ71~第4 出力スイッチ74の機能を実現する。出力選択部20は、第1DA変換器11から第1ア ナログ信号 I。utを出力するときに第2DA変換器12に第2アナログ信号 Q。utを出力す るときに第1DA変換器11から第2アナログ信号Q<sub>out</sub>を出力する。出力選択部20は 、 第 1 アナログ信号 I out 及び第 2 アナログ信号 Q out が 4 対出力されるごとに、出力信号 を交互に切り替える。

[0085]

図18(a)は DA変調器 2 のパワースペクトラムの一例を示す図であり、図18(b)は DWA アルゴリズムを適用しない DA変調器のパワースペクトラムの一例を示す図である。図18(c)は、 DA変調器 2 のOSR (Over sampling Ratio)に対する SNDR (Signal-to-noise and distortion ratio)の値のシミュレーション結果を示す図である。図18(c)において、四角は DWA アルゴリズムを適用しない場合を示し、ひし形は DWA アルゴリズムを適用した DA変調器 1 のシミュレーション結果を示す。

[0086]

図18(a)に示すように、 DA変調器2は信号帯域のノイズが低減されている。 一方、図18(b)に示すように、DWAアルゴリズムを適用しない DA変調器では、信号帯域に多くのノイズが生じている。図18(c)に示すように、 DA変調器1は、DWAアルゴリズムを適用しない場合と比較して良好なSNDRが得られる。

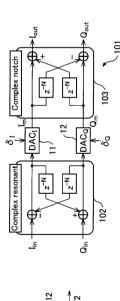

[0087]

図 1 9 は、第 3 実施形態に係る複素マルチバンドパス 変調器の回路ブロック図である。

[0088]

10

20

30

40

20

30

40

50

A D 変調器 2 0 0 は、 D A 変調器 2 0 1 と、第 1 A D 変換器 2 1 1 と、第 2 A D 変換器 2 1 2 と、第 1 減算器 2 2 1 と、第 2 減算器 2 2 2 と、複素マルチバンドパスフィルタ 2 3 0 とを有する。

### [0089]

DA変調器 2 0 1 は、 DA変調器 1 又は 2 と同様な構成及び機能を有する。 DA変調器 2 0 1 は、第 1 デジタル信号  $I_{out}$ を DA変調して、第 1 フィードバック信号として第 1 減算器 2 2 1 に出力し、第 2 デジタル信号  $Q_{out}$ を DA変調して、第 2 フィードバック信号として第 2 減算器 2 2 2 に出力する。第 1 AD変換器 2 1 1 は複素マルチバンドパスフィルタ 2 3 0 がフィルタリングした信号を第 1 デジタル信号  $I_{out}$ に AD変換し、第 2 AD変換器 2 1 2 は複素マルチバンドパスフィルタ 2 3 0 がフィルタリングした信号を第 2 デジタル信号  $Q_{out}$ に AD変換する。第 1 減算器 2 2 1 は DA変調器 2 0 1 から出力される第 1 フィードバック信号を第 1 アナログ信号  $I_{in}$  から減算し、第 2 減算器 2 2 2 は DA変調器 2 0 1 から出力される第 2 フィードバック信号を第 2 アナログ信号  $I_{in}$  から減算する。

## [0090]

複素マルチバンドパスフィルタ230は、N次の信号帯域を有するフィルタである。 DA変調器1を、 DA変調器201として使用するとき、複素マルチバンドパスフィルタ230として2次の信号帯域を有するフィルタを使用する。 DA変調器2を、 DA変調器201として使用するとき、複素マルチバンドパスフィルタ230として4次の信号帯域を有するフィルタを使用する。

#### [0091]

DA変調器1では、第1変換器制御部13は、入力される2個のデジタル信号のそれぞれに対応する2個のポインタを使用してローパスエレメントローテーションアルゴリズムにより第1DA変換器11のセグメント素子を順次選択する。また、第2変換器制御部14は、入力される2個のデジタル信号のそれぞれに対応する2個のポインタを使用してハイパスエレメントローテーションアルゴリズムにより第2DA変換器12のセグメント素子を順次選択する。また、入力選択部15は第1デジタル信号Iin及び第2デジタル信号Qinを2個ごとに交互に選択し、出力選択部16は、第1アナログ信号Iout及び第2アナログ信Qout号を2個ごとに交互に選択する。

## [0092]

また、 DA変調器 2 では、第 1 変換器制御部 1 7 は、入力される 4 個のデジタル信号のそれぞれに対応する 4 個のポインタを使用してローパスエレメントローテーションアルゴリズムにより第 1 DA変換器 1 1 のセグメント素子を順次選択する。また、第 2 変換器制御部 1 8 は、入力される 4 個のデジタル信号のそれぞれに対応する 4 個のポインタを使用してハイパスエレメントローテーションアルゴリズムにより第 2 DA変換器 1 2 のセグメント素子を順次選択する。また、入力選択部 1 9 は第 1 デジタル信号  $I_{in}$  及び第 2 デジタル信号  $Q_{in}$  を 4 個ごとに交互に選択し、出力選択部 2 0 は、第 1 アナログ信号  $Q_{out}$  号を 4 個ごとに交互に選択する。

### [0093]

DA変調器1及び2はそれぞれ、このような構成を有することにより、複素マルチバンドパス 変調が可能になり、 DA変調器1の後段に配置されるアナログフィルタに要求される性能を軽減することができる。

## [0094]

用できる。また、 DA変調器1及び2では、信号帯域近傍で良好なノイズの広がりが 実現可能である。

### [0095]

また、図20に示すように、 DA変調器1及び2では、マルチビット化することにより、パワースペクトラムの絶対値を小さくすることができるため、後段に配置されるアナログフィルタに要求される遮断特性の急峻度が緩和される。

#### [0096]

DA変調器1では第1DA変換器11及び第2DA変換器12に入出力される信号を2個ずつ切り換え、 DA変調器2では第1DA変換器11及び第2DA変換器12に入出力される信号を4個ずつ切り換える。しかしながら、 DA変調器では、第1DA変換器11及び第2DA変換器12に入出力される信号を、2以上の整数であるN個ごとに交互に切り換える構成としてもよい。

#### [0097]

第1 D A 変換器 1 1 及び第 2 D A 変換器 1 2 に入出力される信号を、 N 個ごとに交互に切り換える構成とする場合、第1 変換器制御部 1 3 及び第 2 変換器制御部 1 4 は、入出力される N 個のデジタル信号のそれぞれに対応する N 個のポインタを有する構成になる。

#### [0098]

第1DA変換器11及び第2DA変換器12はそれぞれ、図1(b)に示すように第1電流源CS0~第8電流源CS7がリング状に配置される構造を有するが、第1電流源CS0~第8電流源CS7の代わりに8つの電圧源を有する電圧駆動型の構造としてもよい。また、電流源又は電圧源の数は、DA変換器の精度に応じて適当な数を選択することができる。

#### [0099]

第1変換器制御部13及び17は、第1DAC第1ポインタ21~第1DAC第4ポインタ24がそれぞれ示す電流源の順方向に隣接する電流源から単数又は複数の電流源を順方向に選択する。しかしながら、第1変換器制御部13及び17は、第1DAC第1ポインタ21~第1DAC第4ポインタ24がそれぞれ示す電流源を含めて単数又は複数の電流源を順方向に選択する構成としてもよい。

## [0100]

第2変換器制御部14及び18は、第2DAC第1ポインタ31~第2DAC第4ポインタ34がそれぞれ示す電流源を含めて単数又は複数の電流源を順方向又は逆方向に選択する。しかしながら、第2変換器制御部14及び18は、第1DAC第1ポインタ21~第1DAC第4ポインタ24がそれぞれ示す電流源の順方向又は逆方向に隣接する電流源から単数又は複数の電流源を選択する構成としてもよい。

## 【符号の説明】

### [0101]

1、2、201 DA変調器

1 1 第 1 D A 変 換 器

1 2 第 2 D A 変換器

1 3 、 1 7 第 1 変 換 器 制 御 部

1 4 、 1 8 第 4 変 換 器 制 御 部

15、19 入力選択部

16、20 出力選択部

2 1 ~ 2 4 第 1 D A C 第 1 ポインタ ~ 第 1 D A C 第 4 ポインタ

3 1 ~ 3 4 第 2 D A C 第 1 ポインタ ~ 第 2 D A C 第 4 ポインタ

41~44、61~64 第1入力スイッチ~第4入力スイッチ

2 0 0 A D 変調器

2 1 1 第 1 A D 変換器

2 1 2 第 2 A D 変 換 器

10

20

30

- -

40

# 【図1】

#### 【図3】 【図4】 図3 図4 Cell Number (a) CS0 CS1 CS2 CS3 CS4 CS5 CS6 CS7 DAC - DAC Input (a) 401 3 DACQ 2 TIME 6 **\400** 5 7 (b) (b) 0 -10 -20 -30 -40 -50 401 -60 -70 (c) -80 -90 Power -100 -110 -120 -130 -140 0.05 0.1 0.15 0.2 0.25 0.3 0.35 0.4 0.45 -0:5 -0:4-0:3-0:2-0:1 0 0:1 0:2 0:3 0:4 0:5 $\omega_{\sf in}/\omega_{\sf s}$ $\omega_{\sf in}/\omega_{\sf s}$ 【図5】 【図6】 図6 図5 CS2 CS3 CS4 CS5 CS6 CS7 (a) 第2DA変換器502 DACI > Iout Digital Analog Output H(z) H(z) DAC<sub>Q</sub> -> Q<sub>out</sub> છ (b) 第1DA変換器501 0 -20 HP algorithm DAC -40 Power [dB] 501 502 Pointer → -60 -80 -100 -120 -140 -0.5 -0.4 -0.3 -0.2 -0.1 0

0.1 0.2 0.3 0.4

$\rm f_{in}/f_{s}$

524~

9

**a**

## 【図7】

図7

## 【図8】

## 【図9】

## 【図10】

## 【図11】

## 【図12】

図11

図12

## 【図13】

【図14】

図14

図13

## 【図15】 【図16】

## 【図17】 【図18】

# 【図19】

図19

# 【図20】

## フロントページの続き

(72)発明者 村上 正紘

群馬県前橋市荒牧町四丁目2番地 国立大学法人群馬大学内

(72)発明者 小林 春夫

群馬県前橋市荒牧町四丁目2番地 国立大学法人群馬大学内

F ターム(参考) 5J022 AB02 BA02 BA06 CA07 CE01 CF08