電気学会研究会 電子デバイス/半導体電力変換合同研究会 2015年10月29日

### 高信頼性Nch-LDMOSの提案

○松田順一、神山雅貴、築地伸和、小林春夫 群馬大学

## 概要

- ・はじめに

- 高信頼性LDMOSの必要性と考え方

- 従来型と高信頼性(新)型LDMOSの構造

- シミュレーション結果

- 従来型と新型で電気特性比較( I<sub>DS</sub>-V<sub>GS</sub>, I<sub>DS</sub>-V<sub>DS</sub>, RonA, BV<sub>DS</sub> )

- シミュレーションによる解析

- 真性MOSFETのドレイン電圧(V<sub>DS,int</sub>)とLDMOSのドレイン電圧(V<sub>DS</sub>)の関係

- 横(x)方向の最大電子速度のV<sub>DS</sub> 依存性(at V<sub>GS</sub>=3V and 5V)

- 正孔電流密度と電界の形状の解析(at V<sub>GS</sub>=3V and 5V)

- ドレインpn接合破壊の解析

- ・まとめ

## 高信頼性LDMOSの必要性と考え方

- 高信頼性LDMOSの必要性

- 信頼性: 民生用LDMOS<車載用LDMOS

- 車載用では民生用よりホットキャリア耐性とESD耐性を強化

- 高信頼性LDMOSの考え方

- ホットキャリア耐性の強化

- 真性MOSFETのドレイン近傍でのインパクト・イオン化の抑制

- Kirk効果によるドレイン電流増大(Drain Current Expansion)の抑制

- ESD 耐性の強化(LDMOSをESD素子として兼用する場合)

- バルク・ブレークダウンの発生(pn junction breakdown location is in the bulk.)

- シミュレーションによる検討<sup>(1)</sup>

- 30~50V用Nch-LDMOSで高信頼性構造を検討

- (1) アドバンスソフト社の3次元TCADの中のAdvance/DESSERT(β版)を2次元で使用

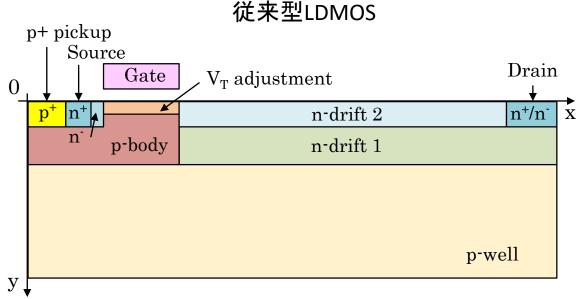

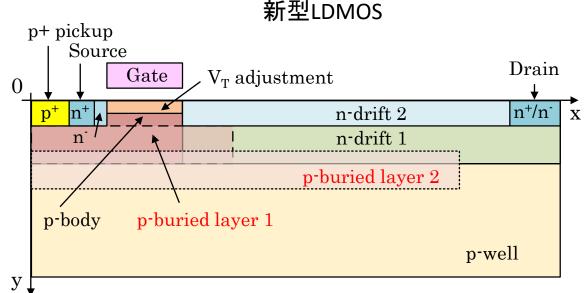

### 従来型と新型Nch-LDMOSの構造

従来型LDMOSは以下の効果を持つ。

- (1) 高ドープp-body ⇒ ドリフト端周りでのRESURFと電流増大の抑制

- (2) p-well ⇒ ドリフト領域に沿ったRESURFと適度な BVds

- (3) V<sub>T</sub> adjustment⇒ V<sub>T</sub> 調整と電流増大の抑制

- (4) n-drift 2 ⇒ 低 RonA と電流増大の抑制

新型LDMOSは従来型に対して以下の効果を追加する。

- (5) p-buried layer 1 ⇒ドリフト端周りでのRESURFと電流増大の抑制の強化

- (6) p-buried layer 2 ⇒ ドリフト領域に沿ったRESURFの強化

- (7) ドレインn<sup>+</sup>下のp-buried layer 2の開口

⇒ 電流増大の抑制と適度なBVdsの維持

## シミュレーションによるNch-LDMOSの構造

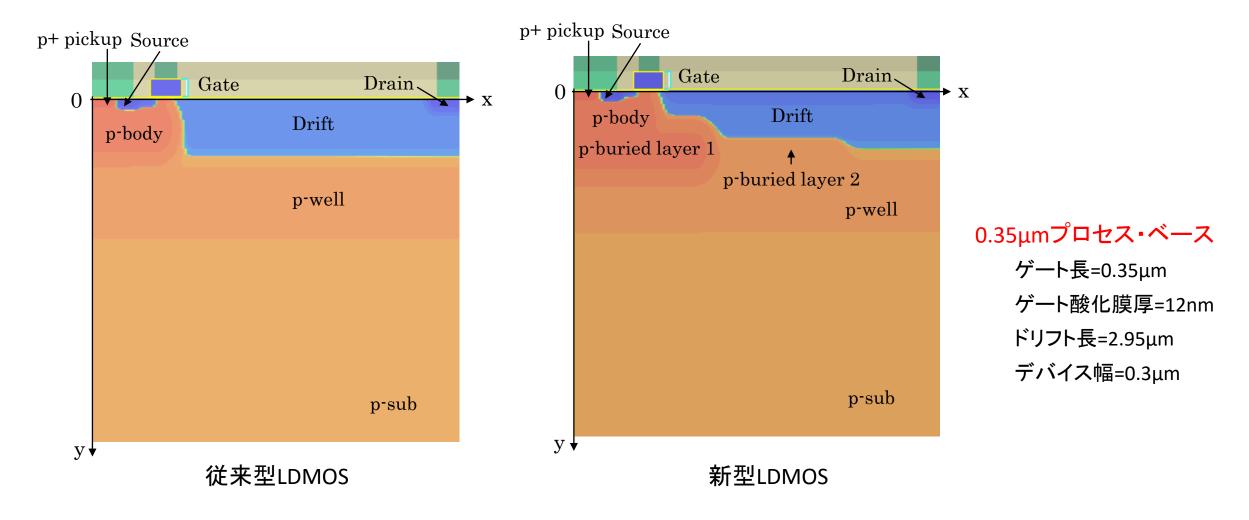

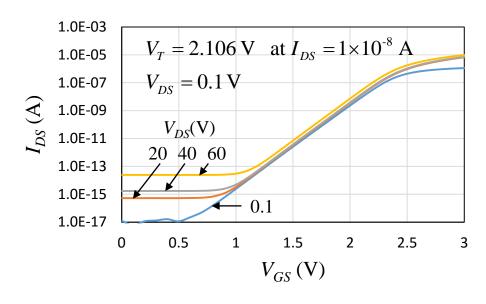

## 従来型と新型LDMOSのI<sub>DS</sub>-V<sub>GS</sub>特性の比較

従来型LDMOS

$$V_T = 2.300 \text{V}$$

at  $I_{DS} = 1 \times 10^{-8} \text{ A}, V_{DS} = 60 \text{ V}$

$V_T (V_{DS} = 60 \text{ V}) - V_T (V_{DS} = 0.1 \text{V}) = 0.125 \text{ V}$

#### 新型LDMOS

$$V_T = 2.021 \text{ V}$$

at  $I_{DS} = 1 \times 10^{-8} \text{ A}, V_{DS} = 60 \text{ V}$

$V_T (V_{DS} = 60 \text{ V}) - V_T (V_{DS} = 0.1 \text{ V}) = 0.085 \text{ V}$

DIBL(Drain Induced Barrier Lowering): 従来型LDMOS>新型LDMOS

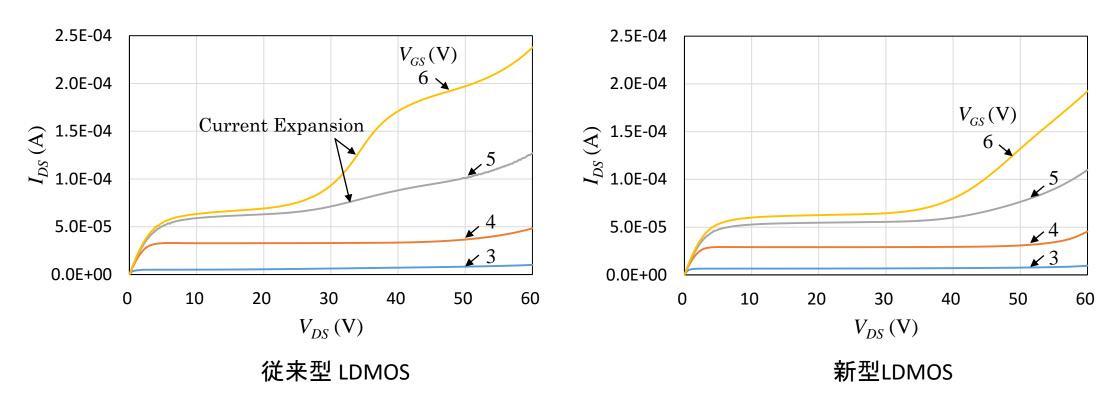

## 従来型と新型LDMOSのI<sub>DS</sub>-V<sub>DS</sub>特性の比較

従来型LDMOSで Current Expansion 発生、新型LDMOSではその発生は無し

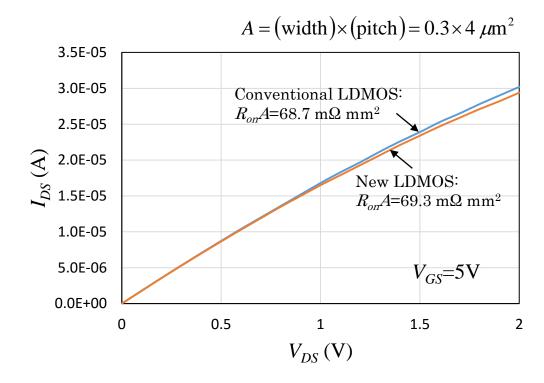

## 従来型と新型LDMOSのR<sub>on</sub>A and BV<sub>DS</sub> の比較

$I_{DS}$ - $V_{DS}$  特性(at  $V_{GS}$ =5V): $R_{on}A$

R<sub>on</sub>A: 従来型LDMOS≒新型LDMOS

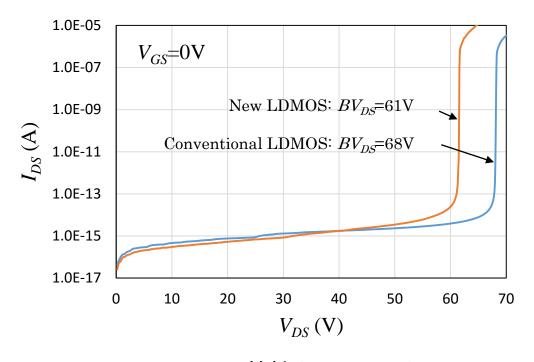

$I_{DS}$ - $V_{DS}$ 特性(at  $V_{GS}$ =0V): $BV_{DS}$

BV<sub>DS</sub>: 従来型LDMOS>新型LDMOS

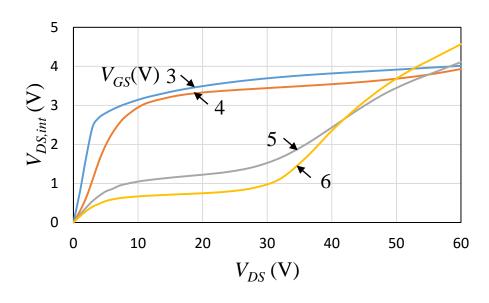

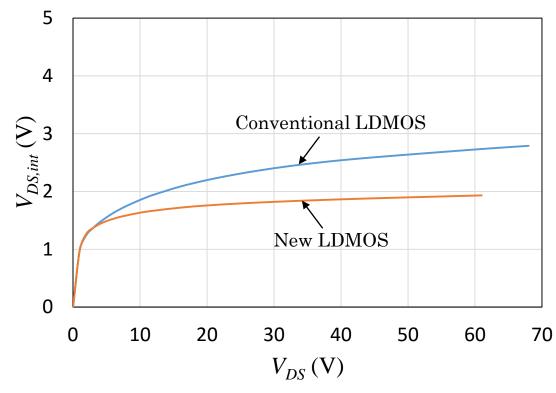

# 真性MOSFET のドレイン電圧(V<sub>DS,int</sub>) vs. LDMOSのドレイン電圧 (V<sub>DS</sub>)

**Conventional LDMOS**

**New LDMOS**

$V_{DS,int}$ : ドレイン側ゲート端表面での電子の擬フェルミ電位で定義

(1) V<sub>GS</sub>=3, 4V と V<sub>GS</sub>=5, 6V で異なる特性

$(2)V_{DSint}$ の飽和特性がDIBLに影響

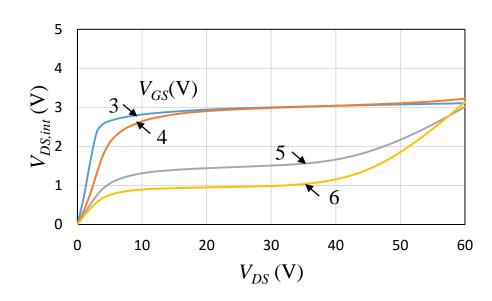

## 従来型と新型LDMOSの表面に沿ったx方向の最大電子速度の比較 at V<sub>cs</sub>=3 and 5V

$I_{DS}$ - $V_{DS}$ の飽和特性( $V_{GS}$ =3V) ⇒従来型も新型もチャネル領域の飽和特性に依存( $V_{DS,int}$ が高いことに対応)  $I_{DS}$ - $V_{DS}$ の飽和特性( $V_{GS}$ =5V) ⇒従来型も新型もドリフト領域の飽和特性に依存( $V_{DS,int}$ が低いことに対応) (従来型のA領域: current expansion 後の飽和特性に寄与⇒真性MOSFETのインパクトイオン化増加)

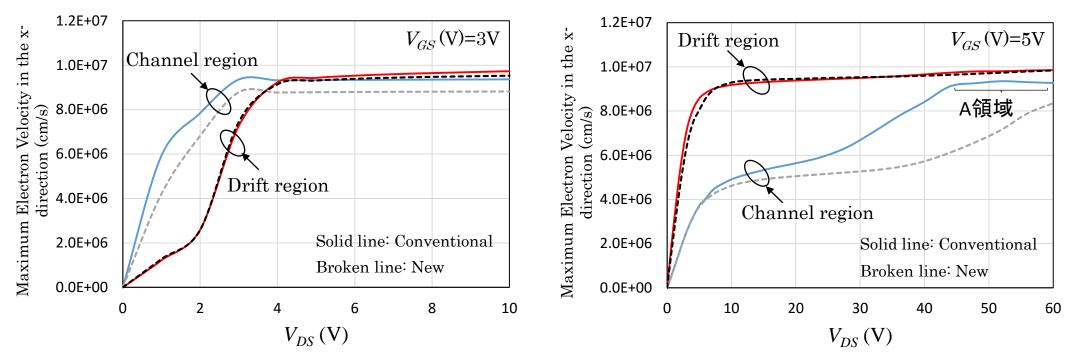

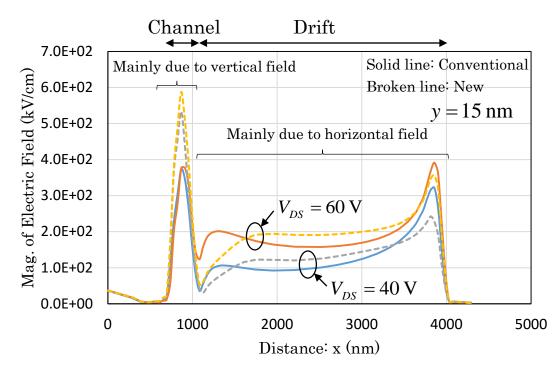

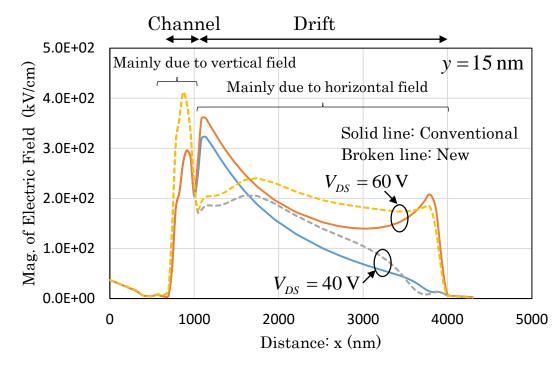

### 従来型と新型LDMOSの正孔電流密度と電界形状の比較

at  $V_{GS}=5V$

正孔電流密度形状

ドリフト両端近傍での正孔電流密度: 従来型LDMOS>新型LDMOS

電界形状

ドリフト両端近傍での電界: 従来型LDMOS > 新型LDMOS

(p-埋め込み層1と2の効果)

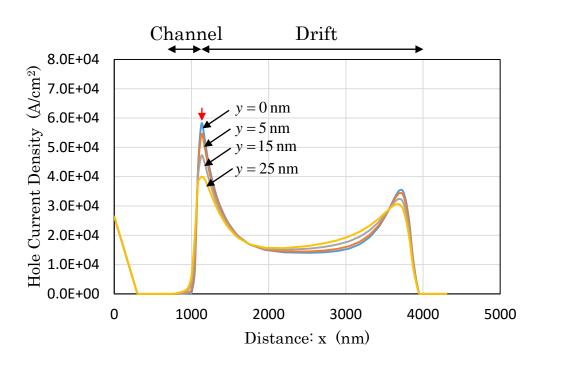

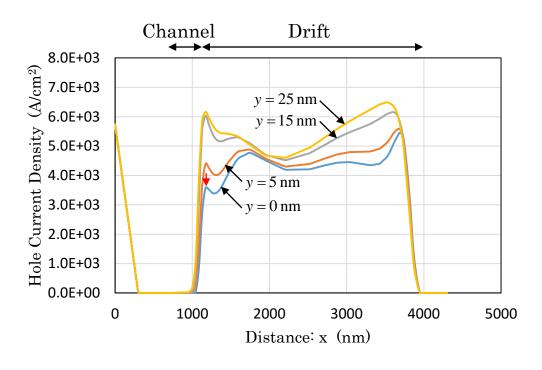

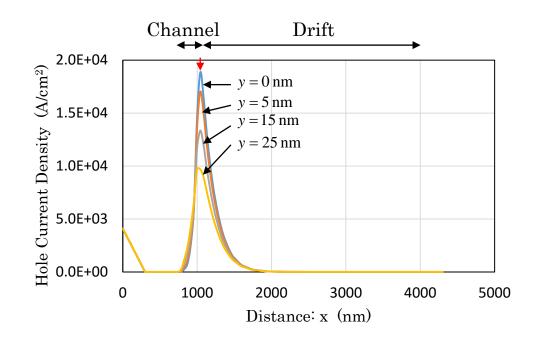

### 従来型と新型LDMOSの正孔電流密度形状の深さ(y)依存性の比較

at  $V_{DS}$ =40V and  $V_{GS}$ =5V

従来型LDMOS

新型LDMOS

チャネル側ドリフト端近傍でのy=0nmにおける正孔電流密度(矢印箇所) ⇒ 新型/従来型LDMOS=1/16

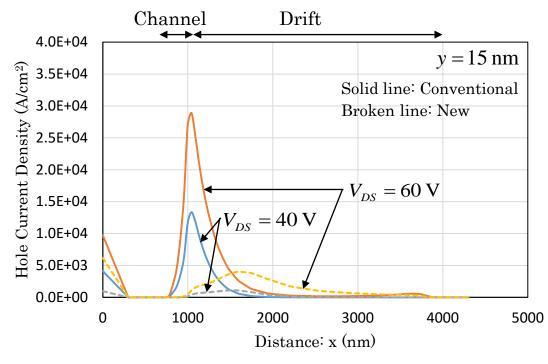

### 従来型と新型LDMOSの正孔電流密度と電界形状の比較

at  $V_{GS}=3V$

正孔電流密度形状

チャネル側ドリフト端近傍の正孔電流密度: 従来型LDMOS>新型LDMOS

電界形状

チャネル側ドリフト端近傍の電界: 従来型LDMOS>新型LDMOS (p-埋め込み層1の効果)

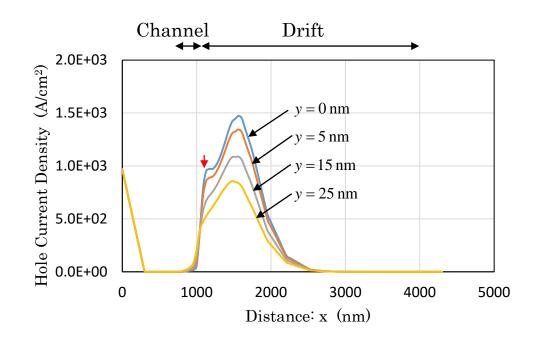

### 従来型と新型LDMOSの正孔電流密度形状の深さ(y)依存性の比較

at  $V_{DS}$ =40V and  $V_{GS}$ =3V

**Conventional LDMOS**

**New LDMOS**

チャネル側ドリフト端近傍でのy=0nmにおける正孔電流密度(矢印箇所) ⇒ 新型/従来型LDMOS=1/19

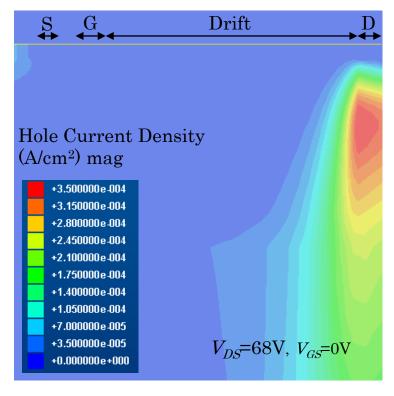

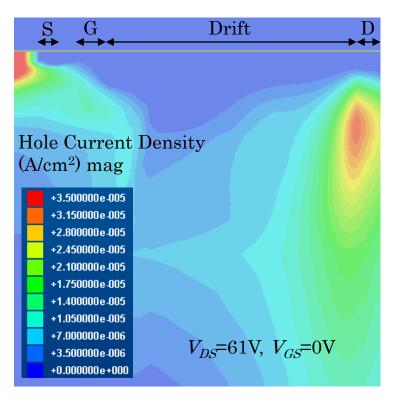

### 従来型と新型LDMOSのブレークダウン時の正孔電流密度分布の比較

従来型LDMOS

新型LDMOS

従来型も新型LDMOSもバルク・ブレークダウンが発生

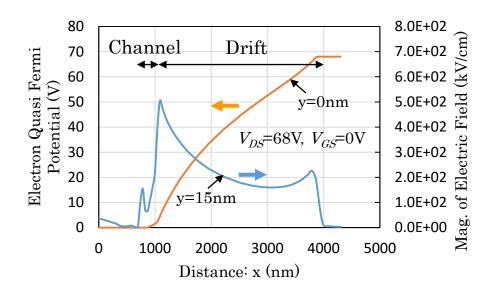

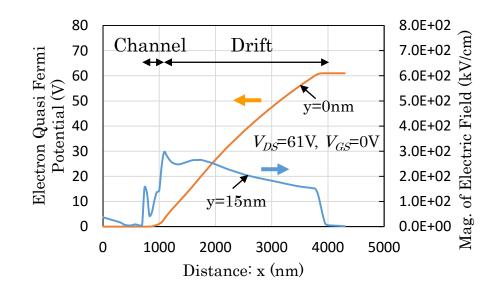

### 従来型と新型LDMOSのブレークダウン時における電子の 擬フェルミ電位と電界形状の比較

従来型LDMOS

新型LDMOS

RESURFのレベル: 従来型LDMOS<新型LDMOS

## 従来型と新型LDMOSでV<sub>DS,int</sub> –V<sub>DS</sub> の比較

at V<sub>GS</sub>=0V

ブレークダウン時

従来型LDMOS

$V_{DS,int}$ =2.79V at  $BV_{DS}$ =68V

新型LDMOS

$V_{DS,int}$ =1.93V at  $BV_{DS}$ =61V

ブレークダウン時にゲート酸化膜(12nm)に掛かる電界: 2.3MV/cm(従来型LDMOS)、1.6MV/cm(新型LDMOS)≪酸化膜破壊電界(約10MV/cm)

## まとめ

| 項目                                            | 従来型LDMOS                                                                   | 新型LDMOS                                                                  |

|-----------------------------------------------|----------------------------------------------------------------------------|--------------------------------------------------------------------------|

| 真性MOSFETのドレイン側ゲート端周りでの<br>インパクト・イオン化による正孔電流密度 | 自                                                                          | 低                                                                        |

| 真性MOSFETのドレイン端周りの<br>ドリフト領域内の電界の大きさ           | 一                                                                          | 低                                                                        |

| ブレークダウンの箇所                                    | バルク                                                                        | バルク                                                                      |

| ドレイン電流増大                                      | 強(Current Expansion)<br>(増大: V <sub>DS</sub> >25V and V <sub>GS</sub> ≥5V) | <mark>弱</mark><br>(増大: for V <sub>DS</sub> >40V and V <sub>GS</sub> ≧5V) |

| V <sub>DS,int</sub> (V) at BV <sub>DS</sub>   | 2.79                                                                       | 1.93                                                                     |

| $\mathrm{BV}_{\mathrm{DS}}(\mathrm{V})$       | 68                                                                         | 61                                                                       |

| RonA (m $\Omega$ mm $^2$ )                    | 68.7                                                                       | 69.3                                                                     |

| $V_T(V)$ at $I_{DS}=1 \times 10^{-8}$ A       | 2.4                                                                        | 2.1                                                                      |

(1) ホットキャリア耐性: 新型LDMOS≫従来型LDMOS

(2) ESD耐性: 新型LDMOS≒従来型LDMOS

## 謝辞

本研究を進めるにあたり、3DTCADを貸して頂いたアドバンスソフト社に深謝致します。

この3D TCADは、国立研究開発法人科学技術振興機構 A-STEPプログラムの助成を受けてアドバンスソフト社で 開発されています。