# CMOS A/D変換器の 入力容量解析

群馬大学大学院工学研究科電気電子工学専攻

小暮英行

# 発表内容

- 1. 入力容量の定義とその求め方

- 2. CMOS ADCの入力容量

- 3. MOSトランジスタのゲート容量

- 4. 差動アンプの入力容量

- 5. 低入力容量差動アンプの提案

- 6. まとめ

# 研究目的

高速CMOS ADCのAC性能向上のため

- •入力容量の非線形性を解析する

- 非線形性を緩和する回路を提案する

# 1. 入力容量の定義とその求め方

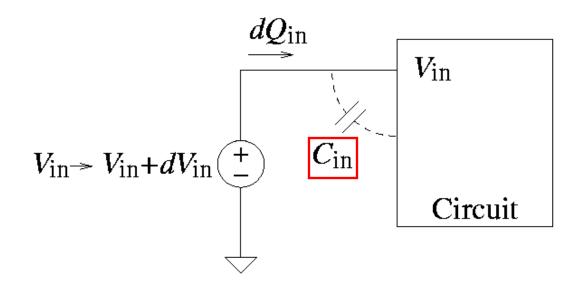

## 入力容量の定義

入力電圧  $V_{\rm in} \rightarrow V_{\rm in} + dV_{\rm in}$ 流入電荷  $dQ_{\rm in}$

$$ightharpoonup$$

入力容量  $C_{

m in} = rac{{

m d} Q_{

m in}}{{

m d} V_{

m in}}$

$$C_{

m in} = rac{{

m d} Q_{

m in}}{{

m d} V_{

m in}}$$

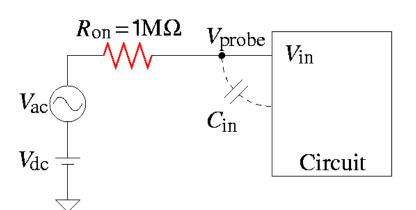

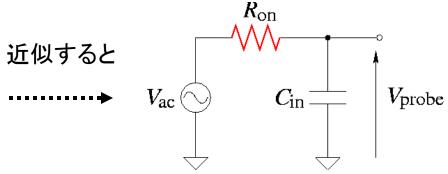

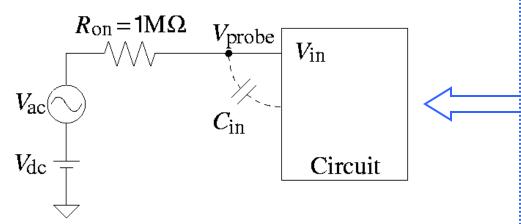

# SPICEシミュレーションによる 入力容量の求め方

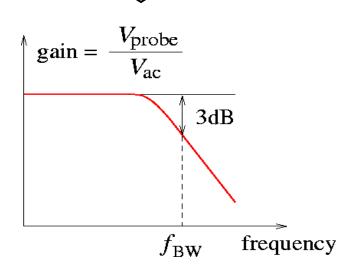

## □ AC解析

帯域

$$f_{\mathrm{BW}} = \frac{1}{2\pi R_{\mathrm{on}} C_{\mathrm{in}}}$$

入力容量

$$C_{\rm in} = \frac{1}{2\pi f_{\rm BW} R_{\rm on}}$$

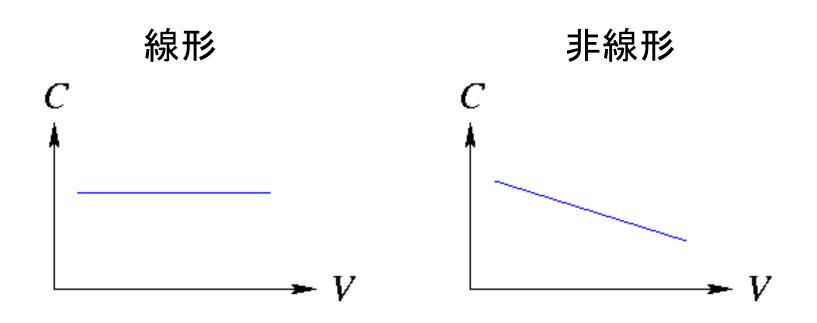

## 容量の非線形性とは

入力容量の非線形性 → AC性能を劣化させる要因

例. 立ち上がりステップ入力と 立ち下がりステップ入力とで応答が異なってしまう

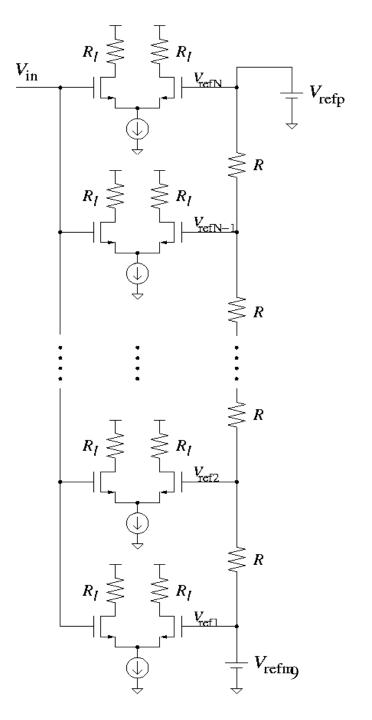

# 2. CMOS ADCの入力容量

#### **CMOS ADC**

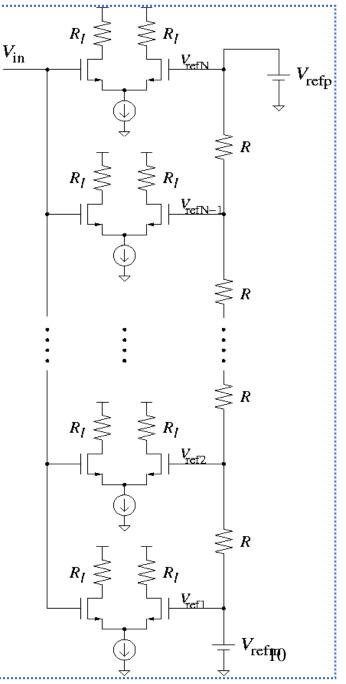

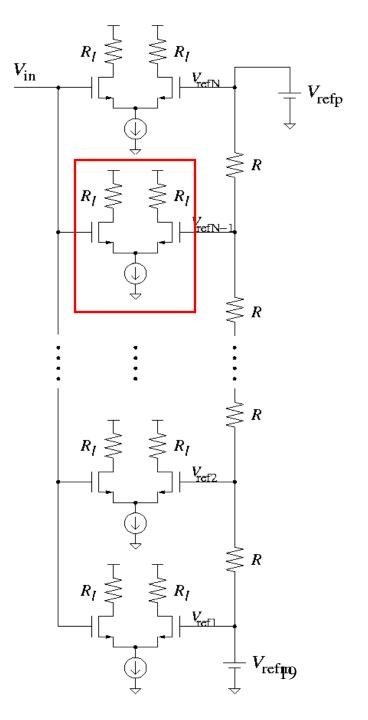

#### フラッシュ型CMOS ADC入力部

- ・差動アンプN個の並列構成

- ・抵抗ラダーからVref生成

- ・差動アンプに入力電圧Vinと Vrefを供給

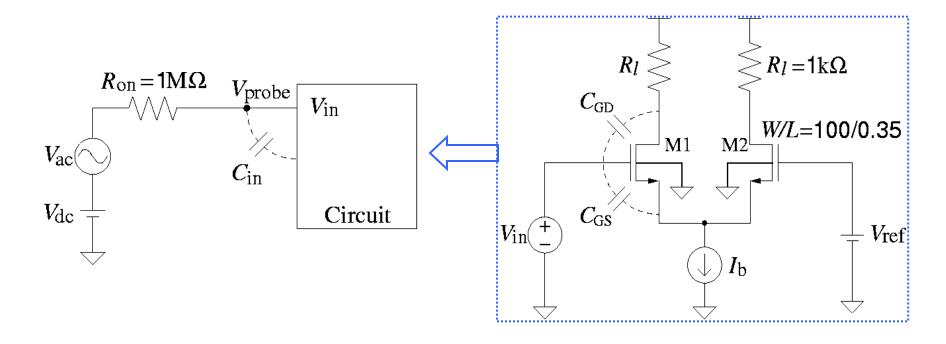

# CMOS ADCの 入力容量の求め方

AC解析より帯域 fbw を求める

$$\Longrightarrow$$

入力容量  $C_{\rm in} = \frac{1}{2\pi f_{\rm BW} R_{\rm on}}$

## シミュレーション条件

- MOSIS 0.35µm CMOS process

- BSIM3 model

- *V*refp=2.5V, *V*refm=1.0V

- $R=5\Omega$ , Rl=1k $\Omega$

- W/L=100/0.35

- *I*bias=200µA

- 差動アンプ数 N=45

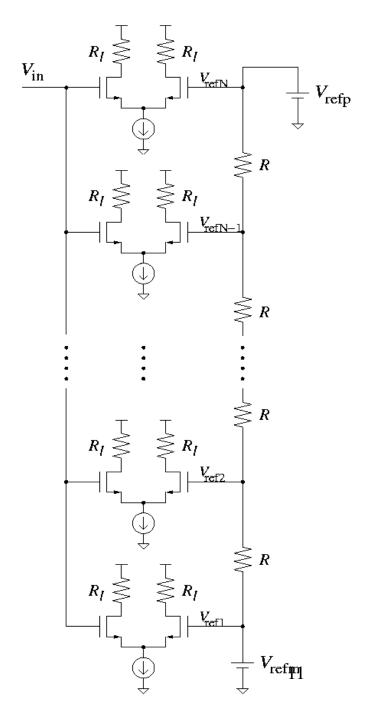

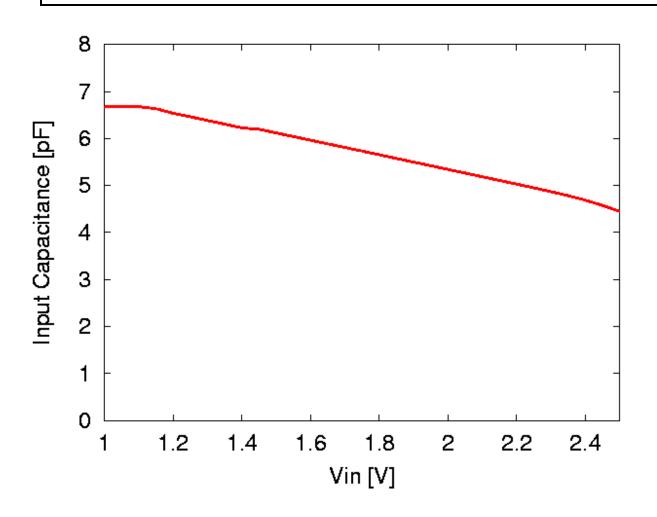

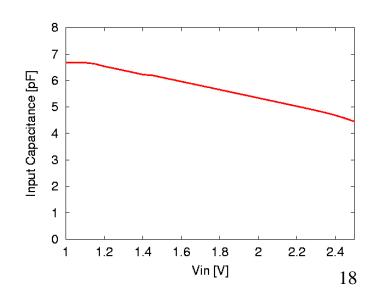

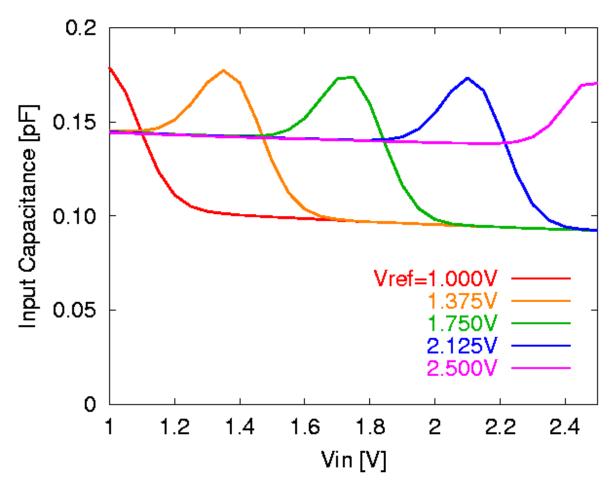

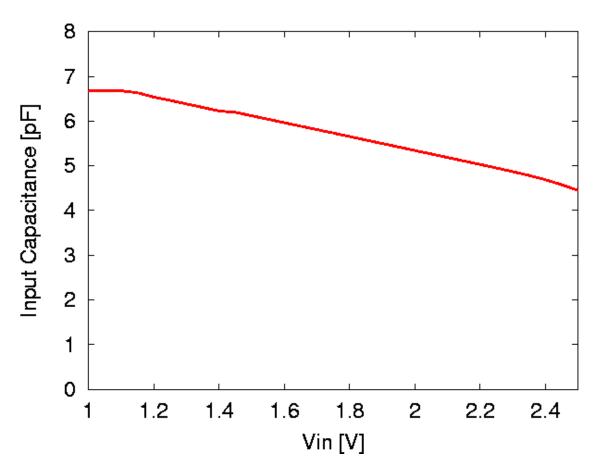

## CMOS ADCの入力容量

入力電圧が高くなると入力容量は減少する

CMOS ADCの入力容量が なぜ非線形なのかを 解析するために...

CMOS ADCの入力容量を

MOSトランジスタのゲート容量の 足し合わせと考える

MOSトランジスタの

ゲート容量を調べる

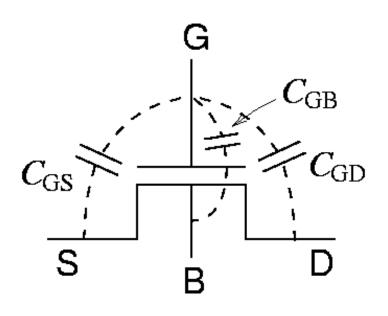

# 3. MOSトランジスタのゲート容量

## MOSトランジスタのゲート容量

ゲート - ドレイン間容量 CGD

ゲート容量

ゲート - ソース間容量 CGS

ゲート - バルク間容量 CGB

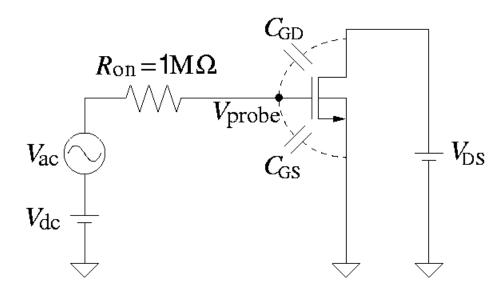

# MOSトランジスタのゲート容量の 求め方

- BSIM3 model

- W/L=100/0.35

AC解析より帯域 fbw を求める

$$ightharpoonegar > ゲート容量  $C_{

m gate} = rac{1}{2\pi f_{

m BW} R_{

m on}}$$$

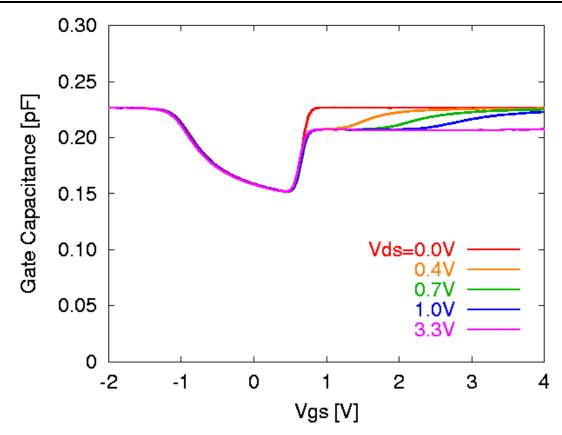

## MOSトランジスタのゲート容量

- OFF時よりON時の方がゲート容量は大きい

- *V*ds が低い方がゲート容量は大きい

- ──> Meyer容量モデルと定性的に合致

#### "ADCの入力容量=MOSゲート容量の総和" と考えると...

ADCの入力電圧が上昇する

□⇒ (入力差動アンプ内の) ON状態のMOSトランジスタ数が増える

□→入力容量が増加する

ADCの入力容量の シミュレーション結果に 矛盾する

## MOSゲート容量の総和では ADCの非線形性を説明できない

差動アンプの 入力容量を調べる

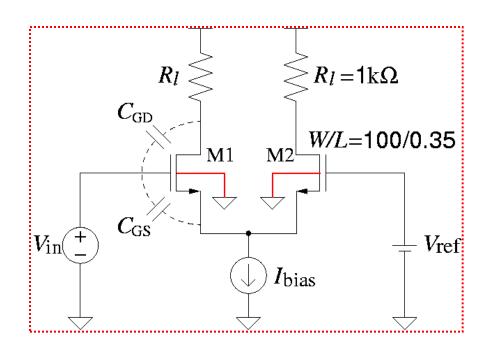

# 4. 差動アンプの入力容量

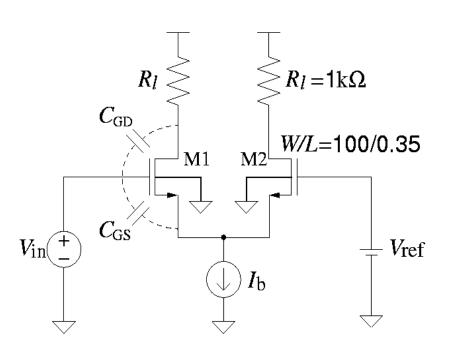

# 差動アンプの入力容量の 求め方

AC解析より帯域 fbw を求める

$$\Longrightarrow$$

入力容量  $C_{\rm in} = rac{1}{2\pi f_{

m BW} R_{

m on}}$

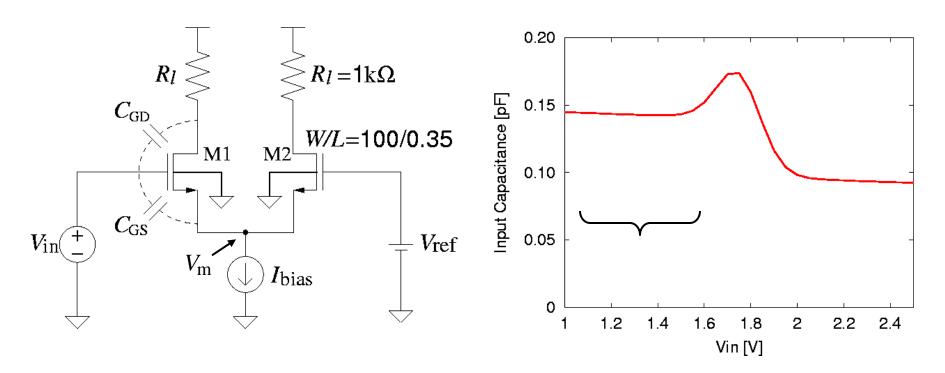

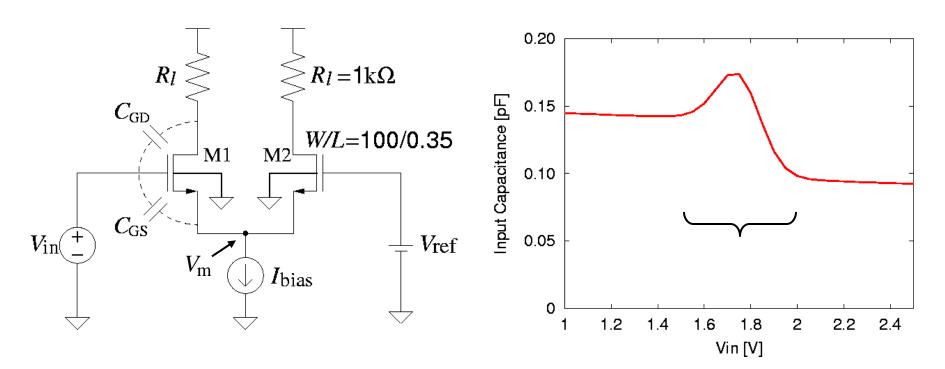

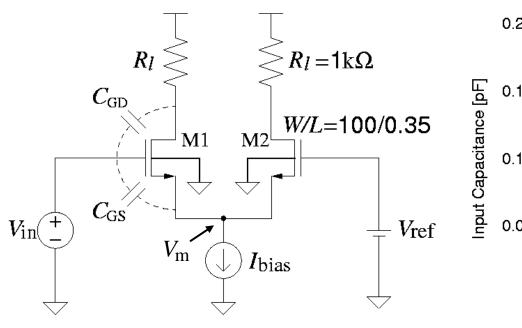

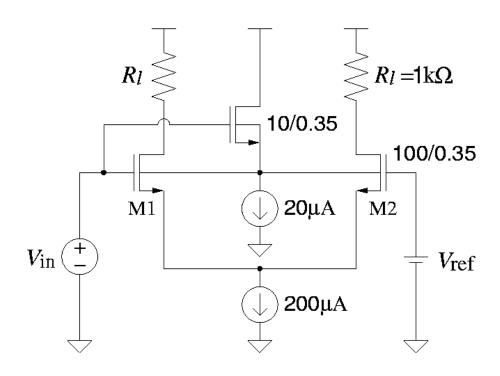

## シミュレーション条件

- BSIM3 model

- *V*ref=1.0V~2.5V

- Rl=1k $\Omega$

- W/L=100/0.35

- $I_b = 200 \mu A$

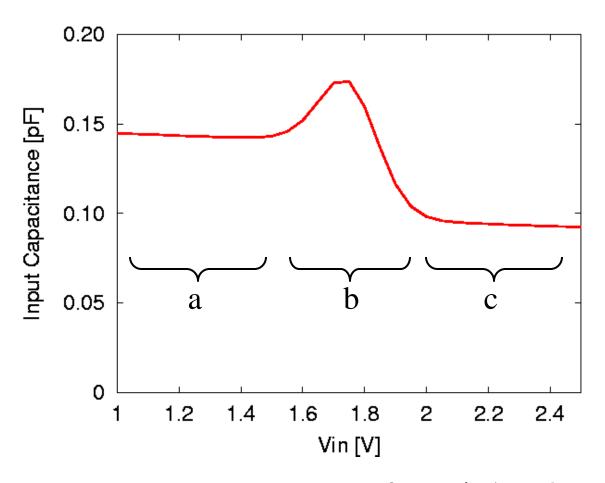

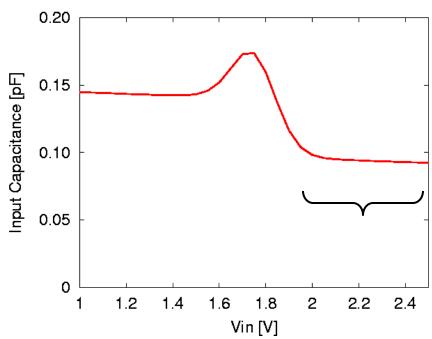

# 差動アンプの入力容量 (Vref=1.75V)

- Vin=Vref 付近で入力容量が増加する

- Vin<Vref より Vin>Vref で入力容量小

## (a). Vin≪Vref の領域

入力VinからOFF状態のMOSトランジスタの容量 CGD, CGS, CGBが見える

□ 確認するためにダミー容量による解析を行う

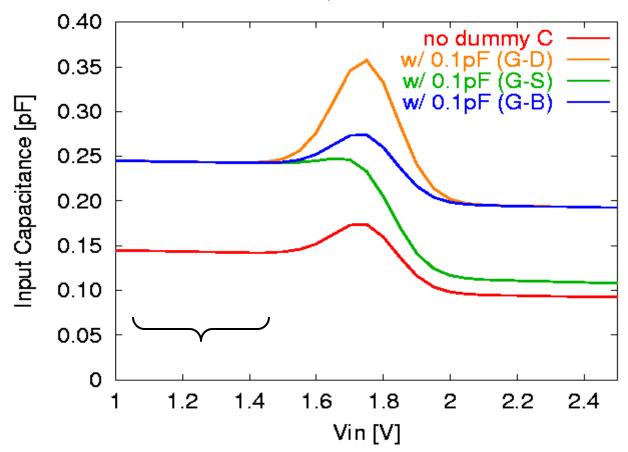

## (a). Vin≪Vref の領域 (ダミー容量による解析)

ダミー容量の影響 G-D間:あり

G-S間: あり

G-B間:あり

Vinから $C_{

m GD}$ ,  $C_{

m GS}$ ,  $C_{

m GB}$ が見える

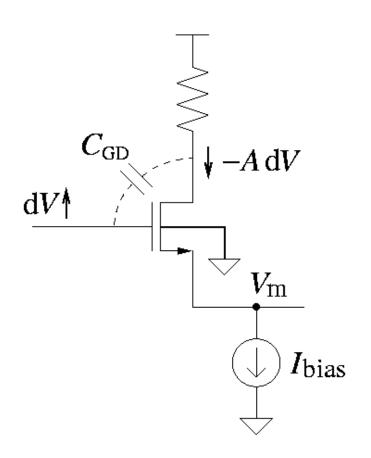

### (b). Vin≈ Vref の領域

#### 差動アンプのゲインが高くなる

ightarrow 入力Vinからミラー容量 (1+A)CGD とCGS , CGB が見える

## (b). Vin ≈ Vref の領域 (ダミー容量による解析)

ダミー容量の影響 G-D間:特にあり

G-S間: 少なくなる

G-B間: あり

Vinから CGDが 特に大きく見える

## (c). Vin ≫ Vref の領域

$V_{\rm in} - V_{\rm m} = const.$

- $\rightarrow$   $C_{GS}$  が見えない

- ightarrow 入力VinからON状態のMOSトランジスタの容量 CGD, CGB だけが見える

### (c). Vink Vref の領域 (ダミー容量による解析)

ダミー容量の影響 G-D間: あり

G-S間: 少ない

G-B間: あり

$V_{

m in}$ から  $C_{

m GS}$ はほとんど見えない

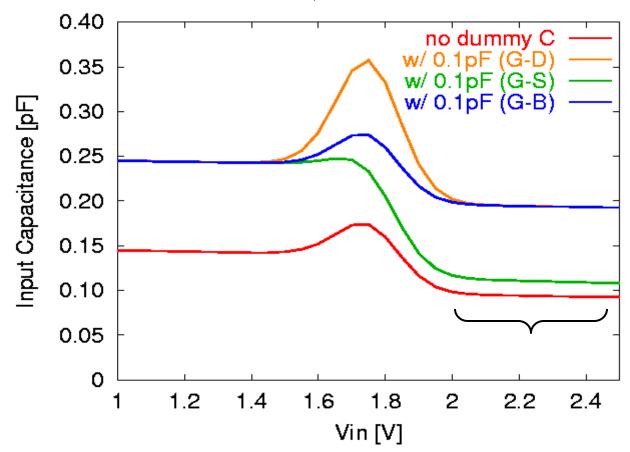

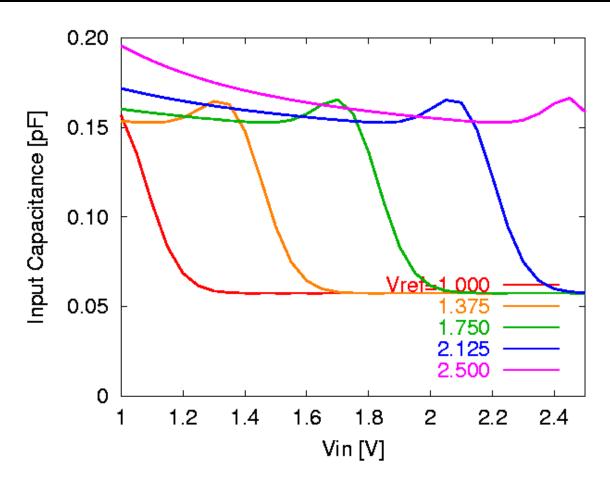

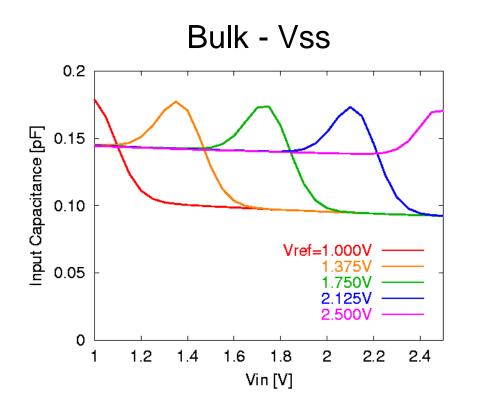

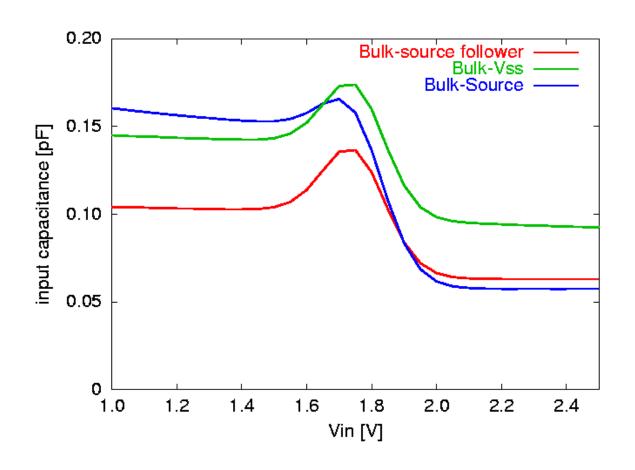

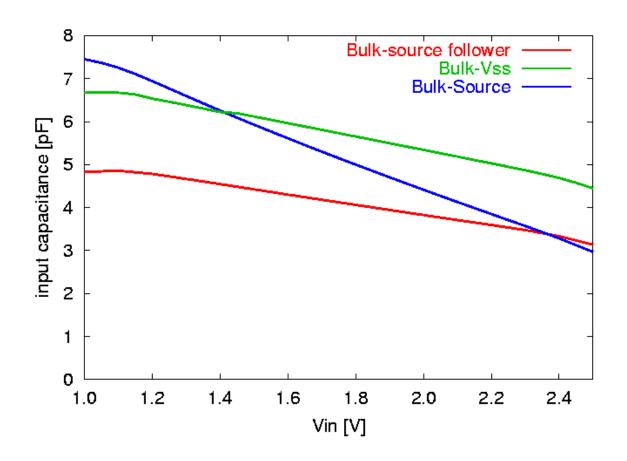

## Vrefを変えた時の差動アンプの入力容量

- Vin  $\approx V$ ref 付近で入力容量が増加する

- Vin < Vref より Vin > Vref で入力容量小

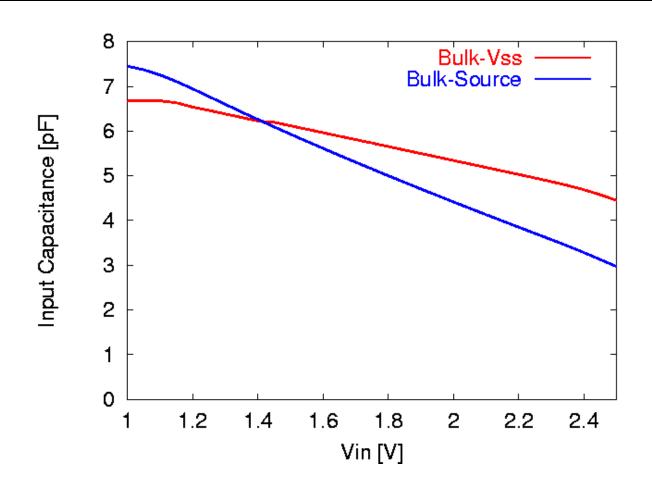

## CMOS ADCの入力容量

差動アンプの入力容量の重ねあわせで CMOS ADCの非線形性が説明できる

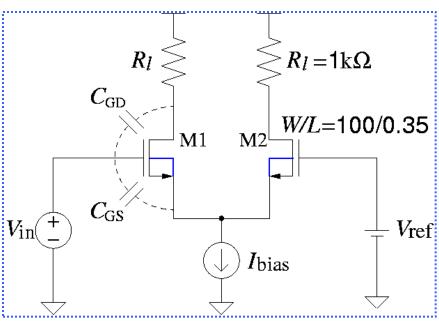

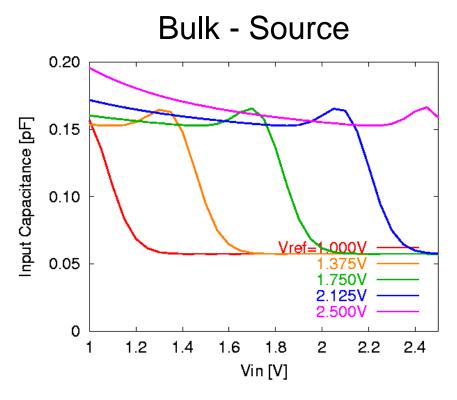

# バルク接続の異なる 差動アンプ

Bulk - Vss

Bulk - Source

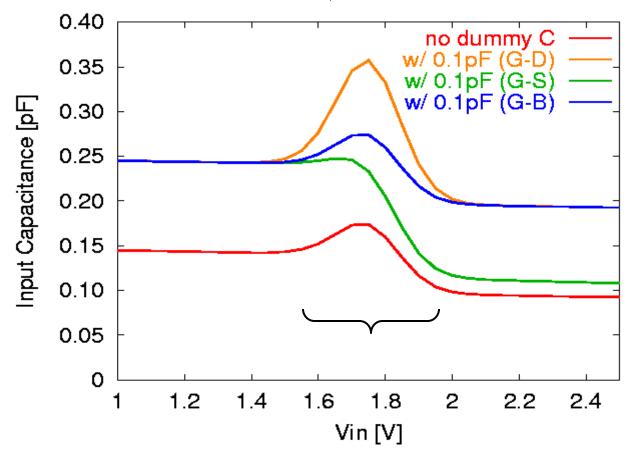

# 差動アンプ(Bulk-Source)の入力容量

- Vin  $\approx V$ ref 付近で入力容量が増加する

- Vin < Vref より Vin > Vref で入力容量小

## 差動アンプの入力容量の比較

Bulk-Source接続

Vin  $\kappa$  Vref : CGSだけでなくCGBも見えなくなる

## CMOS ADCの入力容量の比較

Bulk-Source 接続の方が非線形性が大きい

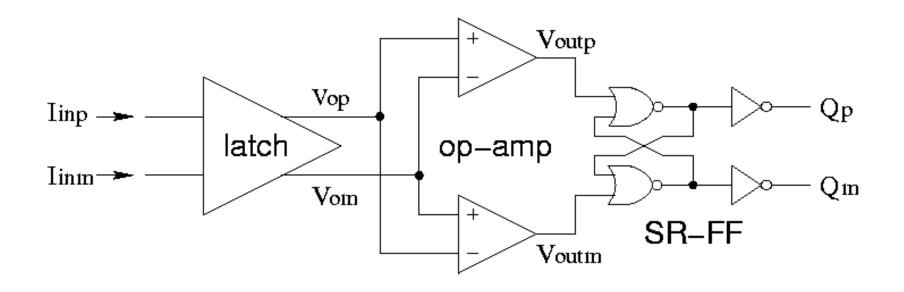

# 5. 低入力容量差動アンプの提案

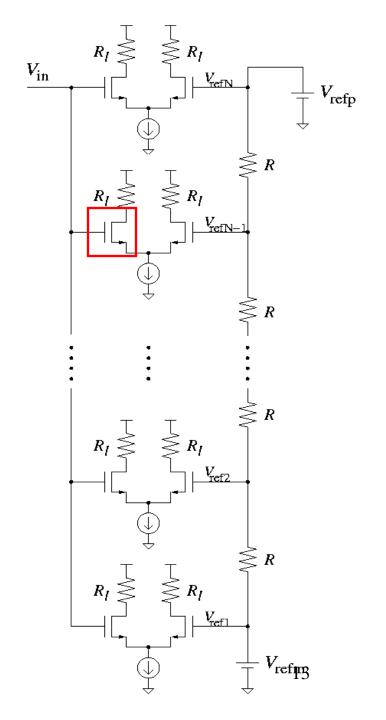

# 低入力容量差動アンプ

- Vin側MOSと並列にソースフォロワを付加

- 両側のMOSのBulkを駆動

ゲート・バルク間電圧が一定となりCGBが見えなくなる

# 差動アンプの入力容量 (Vref=1.75V)

従来の差動アンプ(Bulk-Vss)に比べ 入力容量が約30%減少

#### CMOS ADCの入力容量

従来の差動アンプ(Bulk-Vss)を用いたADCに比べ入力容量が約30%減少

# 6. まとめ

#### 研究成果

この研究により次の事がわかった

- ・CMOS ADCの入力容量 入力電圧が大きくなると減少する

- ・その原因は

MOSゲート容量の足し合わせでは説明できない 入力段差動アンプの入力容量を考える必要あり ・入力差動アンプの入力容量特性

Vin  $\ll V$ ref : CGD , CGS , CGB が見える

$V_{\text{in}} \approx V_{\text{ref}}$  : ミラー容量 (1+A) $C_{\text{GD}} \succeq C_{\text{GS}}$ ,  $C_{\text{GB}}$  が見える

$V_{

m in}$   $\gg$   $V_{

m ref}$  :  $C_{

m GD}$  ,  $C_{

m GB}$  だけが見える

・差動アンプ中のMOSのバルク

Vssに接続: 入力容量の非線形性 小

ソースに接続:入力容量の非線形性 大

低入力容量差動アンプを提案した

# 今後の課題

- 非線形性がADCの性能に与える影響を調べる

- ・実際のADCの非線形性測定

### ミラー容量

$$V_{\text{in}} \rightarrow V_{\text{in}} + dV$$

$V_{\text{out}} \rightarrow V_{\text{out}} - AdV$

$dQ_{\text{GD}} = (1+A) C_{\text{GD}} dV$

容量が (1+A) 倍に見える

# CMOS A/D変換器のコンパレータの高速化

群馬大学大学院工学研究科電気電子工学専攻

小暮英行

# コンパレータのブロック図

差動入力電流 Iinp, Iinm の大小を比較

ロジックレベルで Qp, Qm を出力

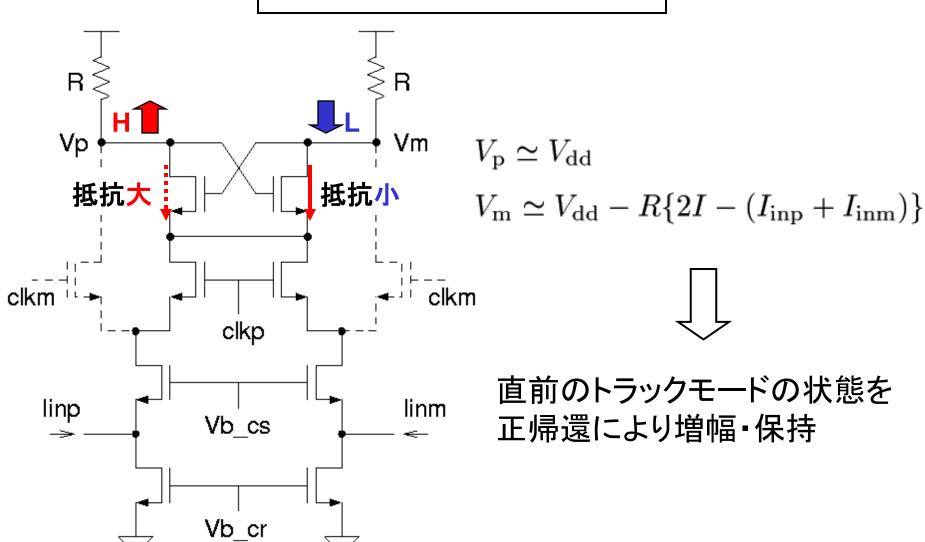

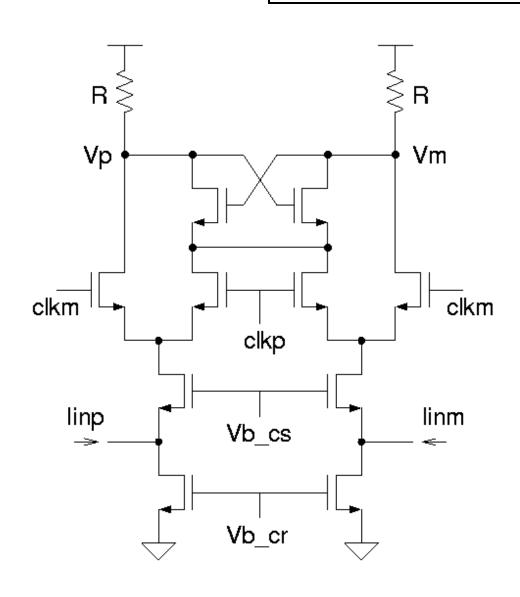

# ラッチ回路

電流入力 Iinp, Iinm 電圧出力 Vp, Vm クロック clkp, clkm

電流入力の大小を 比較・保持

## 2つの動作モード

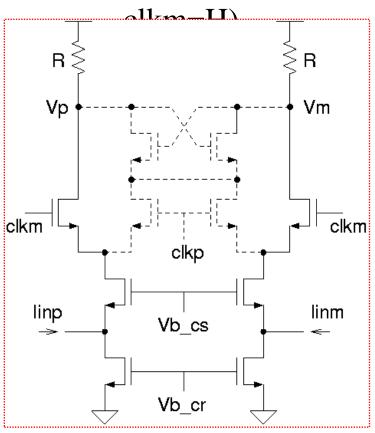

#### トラックモード (clkp=L,

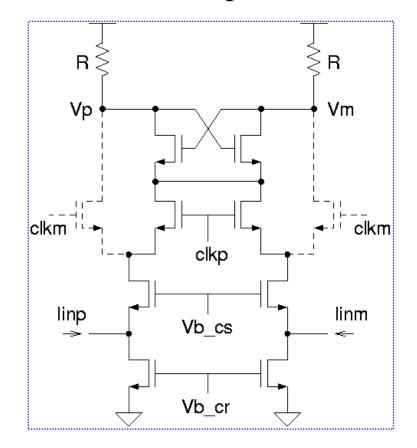

#### ラッチモード (clkp=H, clkm=L)

クロックにより2つの動作モードを交互に遷移する

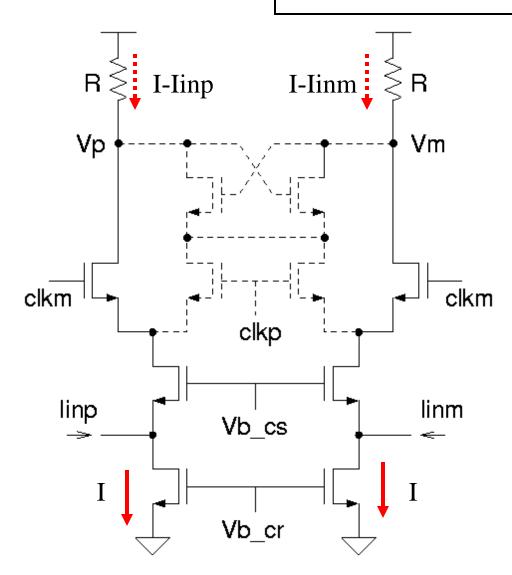

# トラックモード

$$V_{\rm p} = V_{\rm dd} - R(I - I_{\rm inp})$$

$$V_{\rm m} = V_{\rm dd} - R(I - I_{\rm inm})$$

$$\therefore V_{\rm p} - V_{\rm m} = R(I_{\rm inp} - I_{\rm inm})$$

入力電流に比例した電圧を出力

# ラッチモード