# 排他的制御方式単インダクタ4出力降圧形 DC-DC 電源

小堀康功\* 熊倉大地 (小山工業高等専門学校) 築地伸和 呉澍 シャイフルニザム 高井伸和 小林春夫 (群馬大学)

## Single-Inductor Four-Output DC-DC Buck Converter with Exclusive Control

Yasunori Kobori\*, Daichi Kumakura (National College of Technology, Oyama College)

Nobukazu Tsukiji, Shu Wu, Nizam M. Shaiful, Nobukazu Takai, Haruo Kobayashi (Gunma University)

キーワード: DC-DC コンバータ、単インダクタ・マルチ出力 SIMO 電源, 降圧形電源, 4 出力電源 (Keywords, DC-DC Converter, SIMO Converter, Buck Converter, Four-output Converter)

#### 1. はじめに

近年の電子機器では、更なる小型・軽量・省電力化の研究開発が進められている。スイッチング電源では 集積が困難なインダクタ等の電子部品の削減や、内部 回路の削減による LSI の小型化も検討されている。

これまで我々は、単インダクタ・マルチ出力 SIMO (Single-Inductor Multi-Output) DC-DC 電源 $^{1\sim3}$ )によりインダクタ等の削減を検討し、さらに4出力スイッチング電源のシミュレーション結果を報告してきた。今回、4出力 SIMO 降圧形スイッチング電源を実装確認したので報告する。

### 2. 単インダクタ・マルチ出力降圧形電源

### 2.1 降圧形 SIMO 電源の基本構成と動作原理

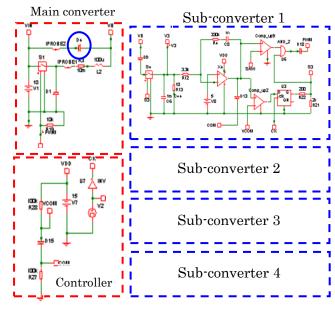

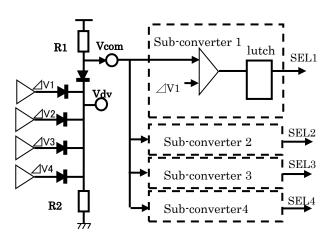

4出力 SIMO 降圧形スイッチング電源の構成を、図1に示す。パワーステージ部に4個のサブコンバータを接続し、排他的 Exclusive に一つのサブコンバータを選択制御する。パワーステージであるメインコンバータ部は、メインスイッチ・還流ダイオード・インダクタで構成される。制御部は、鋸歯状波発生回路およびサブコンバータを排他的に選択する Exclusive 制御回路で構成される。

各サブコンバータは同一構成であり、サブスイッチ・大容量コンデンサ・誤差電圧増幅器・PWM 信号発生器および選択信号 SEL 発生部で構成され、基準電圧のみがそれぞれ異なる。

次に動作を説明する。各サブコンバータでは、共通の鋸歯状波により同期した PWM 信号を発生する。これらの PWM 信号はパワーステージで論理和され、メインスイッチを制御駆動する。一方、サブコンバータの排他的選択方法は、増幅誤差電圧が最大のサブコンバータを選択する Exclusive 方式を採用する。この方式として、各増幅誤差電圧を相互にコンパレータで比較

する方式も考えられるが、サブコンバータ数のフレキシビリティに対応しにくい。そこで、図2のように、各サブコンバータの Vをパワーステージ部に送り、ワイヤード OR 回路により最大の増幅誤差電圧 VMAXを検出して、この VMAXを各サブコンバータに送り返すことにより、サブコンバータ内でセルフ選択できる方式とした。

以上の構成により、基本的に1つのサブコンバータ内の選択信号 SEL のみが H となり、内部のサブスイッチを ON にできる。次の周期には $\triangle$ VMAXが変化して、新たなサブコンバータが選択制御される。このようにして鋸歯状波の立上り端、つまりは PWM 信号の立上り端で、次周期の制御対象を排他的に選択する

図1 4出力 SIMO 方式降圧形スイッチング電源の構成

図2 最大誤差電圧検出用ワイヤード OR 回路

### 2.2 SIMO 電源のシミュレーション結果

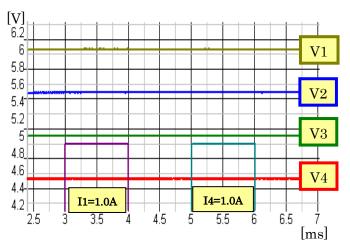

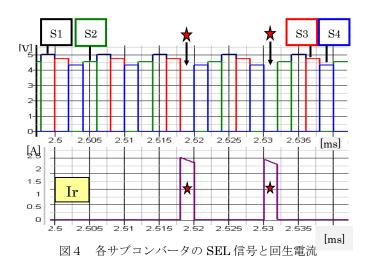

提案する 4 出力降圧形 8 IMO 電源のシミュレーション 回路の主要パラメータを表 1 に、シミュレーション結果の出力電圧を図 3 に、選択信号 8 SEL 等の主要波形を図 4 に示す。表 1 では各サブコンバータの主要パラメータを同一とし、出力電圧を 8 Vo=6.0 4.5 V に、出力負荷電流をそれぞれ 8 Io=8.5 とした。

図3の定常特性では出力電圧は安定であり、制御回路に施された位相遅れ補償により基本的にオフセットは発生していない。図4に、各サブコンバータのSEL信号(S1~S4)と、回生ダイオードに流れる回生電流Irを示した。各SEL信号は識別可能なように、レベル差を付けて表示している。ここで、4つのSEL信号が排他的に1個ずつ現れているが、図中の星印周期ではSEL信号がなく、どのサブコンバータも選択されていない。この場合、図1の回路においてインダクタと並列に接続された回生ダイオード(〇印)が導通し、図4に示すように回生電流が流れていることが分かる。なお、4出力を考慮して、クロック周波数は500kHzとした。

表1 シミュレーション回路の主要パラメータ

| Vin      | 10.0 V               |

|----------|----------------------|

| $V_1$    | 6.0 V                |

| $ m V_2$ | 5.5 V                |

| $V_3$    | 5.0 V                |

| $V_4$    | 4.5 V                |

| Io       | 各 0.5 A              |

| L        | $0.2~\mu\mathrm{H}$  |

| C        | $470~\mu \mathrm{F}$ |

| Fck      | $500~\mathrm{kHz}$   |

図3 提案 SIMO 電源のシミュレーション結果

図5に負荷電流変 Io1と Io4をそれぞれ2倍(0.5A ⇔ 1.0A) に変化させた場合の過渡応答特性(ロードレギュレーション)を、定常リプルと共に拡大して示す。定常時の各出力リプルは安定であり、電流増加時にやや大きくなるが20mVpp 未満と、出力電圧の0.5%以下で問題ない。一方、負荷電流変化⊿Io=0.5Aに対する過渡応答特性では、セルフ・レギュレーションおよびクロス・レギュレーションは共にオーバー/アンダー・シュートとも±5mV程度であり良好な特性である。

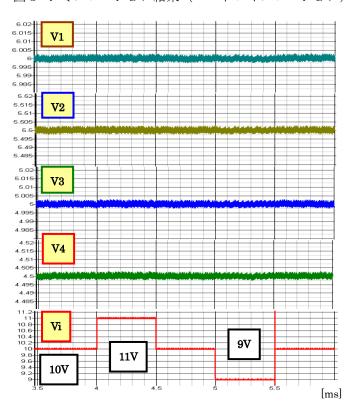

次に、入力電圧の変化に対する出力電圧の応答特性(ラインレギュレーション)を図6に示す。ここでは、入力電圧10Vに対して±10%の電圧変化△Vi=1.0Vとした。各出力リプルのレベルはほぼ一定である。一方、動特性ではオーバー/アンダー・シュート共に検知することができず、ラインレギュレーション特性は非常に良好である。

## [V] 20 mVpp6.02 6.01 5.99 5.98 5.97 5.53 V25.52-5.51 5.5 5.49 5.48-5.03 V3 5.02 5.01 4.99 4.98 4.97-4.53 4.52 4.51 4.5 4.49-4.48 I4=1.0A [ms]

図5 シミュレーション結果 (ロードレギュレーション)

図6シミュレーション結果(ラインレギュレーション)

### 3. 降圧形 SIMO 電源の実装結果

### 3.1 基本構成と実装写真

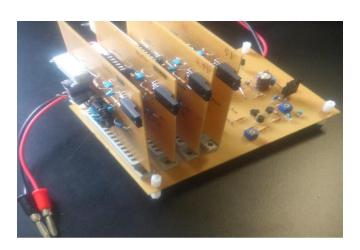

マルチ出力降圧形スイッチング電源の製作にあたり、サブコンバータの増減が可能なようにビルトイン方式を採用した。つまり図1の回路構成において、マザーボード上にパワーステージ回路および制御回路部を全て作製し、各サブコンバータはソケット構成で着脱可能とした。作製したSIMO電源の写真を図7に示す。また、実装時の出力電圧・負荷電流および主要パラメータを表2に示す。ここで目標電圧は、各サブコンバータ内の基準電圧を示しており、出力オフセットはそれぞれ20mV以下であり、出力電圧の0.5%程度と非常に小さい。また、出力電流は固定負荷抵抗で設定しており、全体に0.2A程度と小さめにしている。

図7 製作した降圧形 SIMO 電源

表2 実装電源の主要パラメータ

| 項目            | 目標値                 | 実測値                  |

|---------------|---------------------|----------------------|

| E             | 10.0 V              | 10.0 V               |

| $V_1$         | 4.86 V              | 4.84 V               |

| $V_2$         | 4.37 V              | 4.35 V               |

| $V_3$         | 3.85 V              | 3.83 V               |

| $V_4$         | 3.42 V              | 3.43 V               |

| $I_1, I_2$    |                     | $0.22\mathrm{A}$     |

| $I_3$ , $I_4$ |                     | 0.17 A               |

| L             | $47~\mu \mathrm{H}$ | $1.0~\mu~\mathrm{H}$ |

| C             | $470~\mu\mathrm{F}$ | $470~\mu\mathrm{F}$  |

| Fck           | $500~\mathrm{kHz}$  | $500~\mathrm{kHz}$   |

#### 3.2 実装電源の測定結果

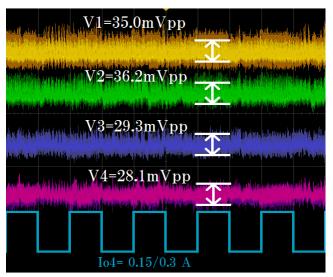

4 出力降圧形 SIMO 電源の実測波形を図8、図9に示す。図8は、サブ電源1の負荷電流 Io1 を切換えたときの、サブコンバータ1のセルフ・レギュレーションおよびサブコンバータ2~4のクロス・レギュレーションを示した。各定常リプルは、パルス性ノイズを除いて 40mVpp 程度とやや大きめだが、過渡応答特性では±5mV 以下と十分小さく問題ない。

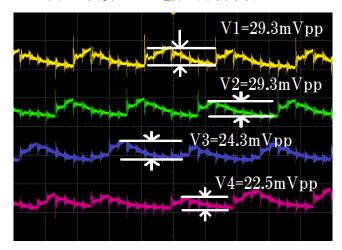

図9の定常リプルの拡大波形では、グランド配線インピーダンスによるクロックに同期したパルス性ノイズが大きい。特に各サブコンバータの出力では、選択直後にコンデンサが充電され始める時、つまり出力リプルが上昇し始める時のパルスノイズが非常に大きい。この時リプル波形がステップ上に  $5\sim10\,\mathrm{mV}$  程度上昇しているが、この原因はコンデンサの ESR (Equivalent Series Resistance:等価直列抵抗)にステップ上にパルス電流が流入したためである。実質的な電圧リプルは  $30\,\mathrm{mVpp}$  程度であり、出力電圧の 0.5% 以下で問題ない。図9における実質の電圧リプルは

図8 実装 SIMO 電源の定常出力リプル

図 9 実装 SIMO 電源の拡大出力リプル

30 mVpp 程度であり、いずれも出力電圧の 0.5%以下で問題ない。一方、各リプルの電圧上昇時間はそれぞれ 1 周期であり、その結果生じるピーク位相をみると、 $V1 \rightarrow V4 \rightarrow V3 \rightarrow V2$  の順に排他的に制御されていることが分かる。

#### 5. まとめ

4出力降圧形 SIMO DC-DC スイッチング電源を検討し、そのシミュレーション確認および実装回路により性能を測定確認した。全体構成として、メインコンバータ部と4つの同一構成のサブコンバータ方式とし、排他的 Exclusive 制御方式とした。

シミュレーションの結果、各サブコンバータの負荷電流を0.5Aとし、出力電圧 $Vo=6.0\sim4.5V$ としたとき、出力電圧リプルは、それぞれ 20mVpp以下と出力電圧の0.5%以下である。また、負荷電流変化 $\triangle Io=0.5A$ に対する過渡応答特性は、オーバー $\triangle Io=0.5A$ にかま1000のである。

実装回路では、出力電圧数のフレキシビリティを考慮して、各サブコンバータを同一回路構成のプラグイン構成とした。この結果、グランド配線によるインピーダンスがやや増加して、クロックに同期したパルス性ノイズが各出力リプルに発生した。実質的な定常リプルは30mVpp程度であり、出力電圧の0.5%以下で問題ない。また負荷電流変化⊿Io=0.15Aに対する過渡応答特性では、±5mV以下とまったく問題のない良好な性能である。

#### 文 献

- [1] Y. Kobori, M. Li, F, Zhao, S. Wu, N. Takai, H. Kobayashi, "Single-Inductor Multi-Output Converters with Four-level Output Voltages," International Conference on Circuit and System, pp.436-439 (Jun. 2014)

- [2] 小堀康功,高井伸和,小林春夫,他9名,"擬似⊿∑変調単一インダクタ2出力 DC-DC スイッチング電源, "IEEJ 電子回路研究会,ECT-12-100 (2012.12)

- [3] S. Tanaka, Y. Kobori, N. Takai, H. Kobayashi, etal, "Single-Inductor Multi-Output DC-DC Converter Design with Hysteresis Control," IEICE International Conference on Integrated Circuits, Design, and Verification, pp.198-203 (2013,11)