## **P8-22**

# **Proposal of High Reliability LDMOS Structure**

Nobukazu Tsukiji, Junya Kojima, Haruo Kobayashi Jun-ichi Matsuda, Masataka Kamiyama,

Division of Electronics and Informatics, Gunma University, Kiryu 376-8515 Japan

#### **Research Background & Objective**

LDMOS···Laterally Diffused MOS

0 0

**Adopting to automotive applications**

If it were not highly reliable .....?

Accident !!!

### Introduction

#### High reliability realization

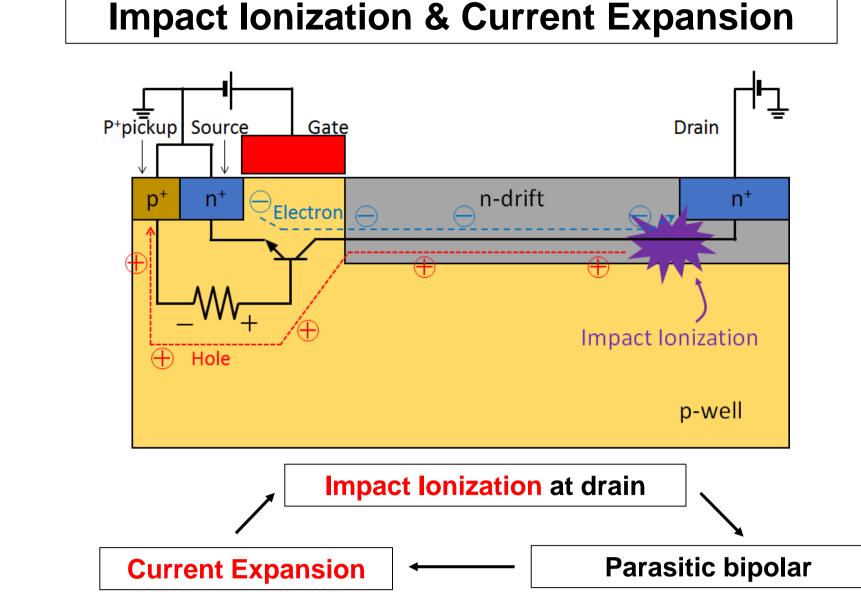

- Reinforcement of Hot Carrier Endurance

- ✓ Suppression of impact ionization

- around drain edge of

- intrinsic MOSFET of LDMOS

- ✓ Suppression of Current Expansion (Kirk effect)

- Reinforcement of ESD Endurance

- ✓ Generation of Bulk Breakdown

(pn junction breakdown location is in bulk.)

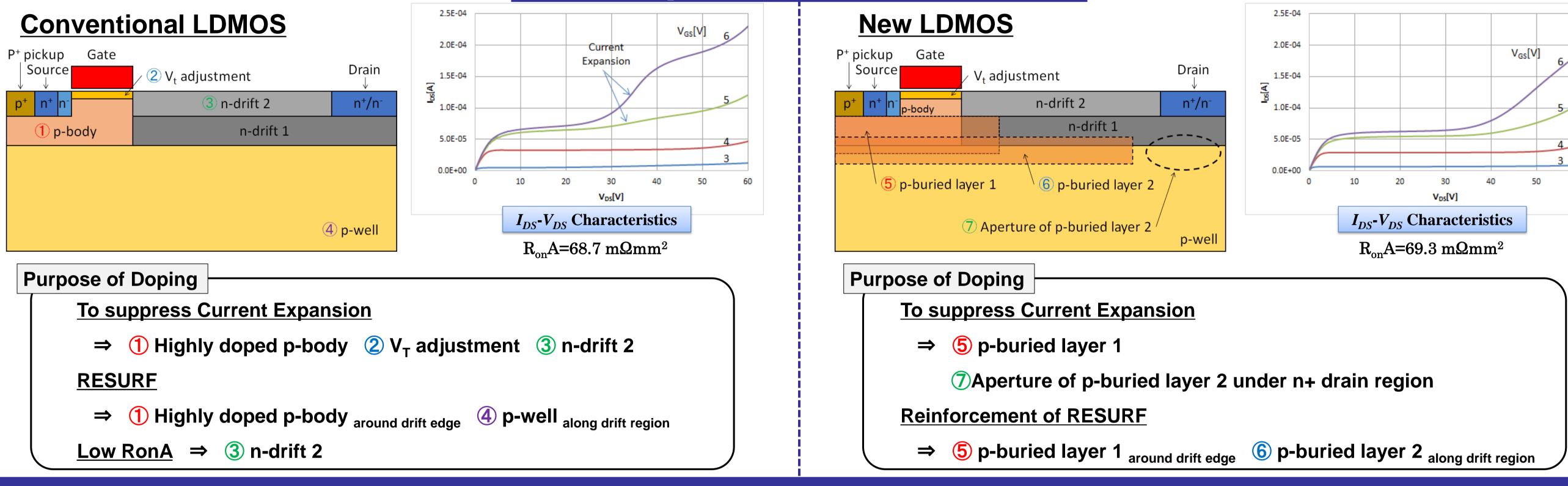

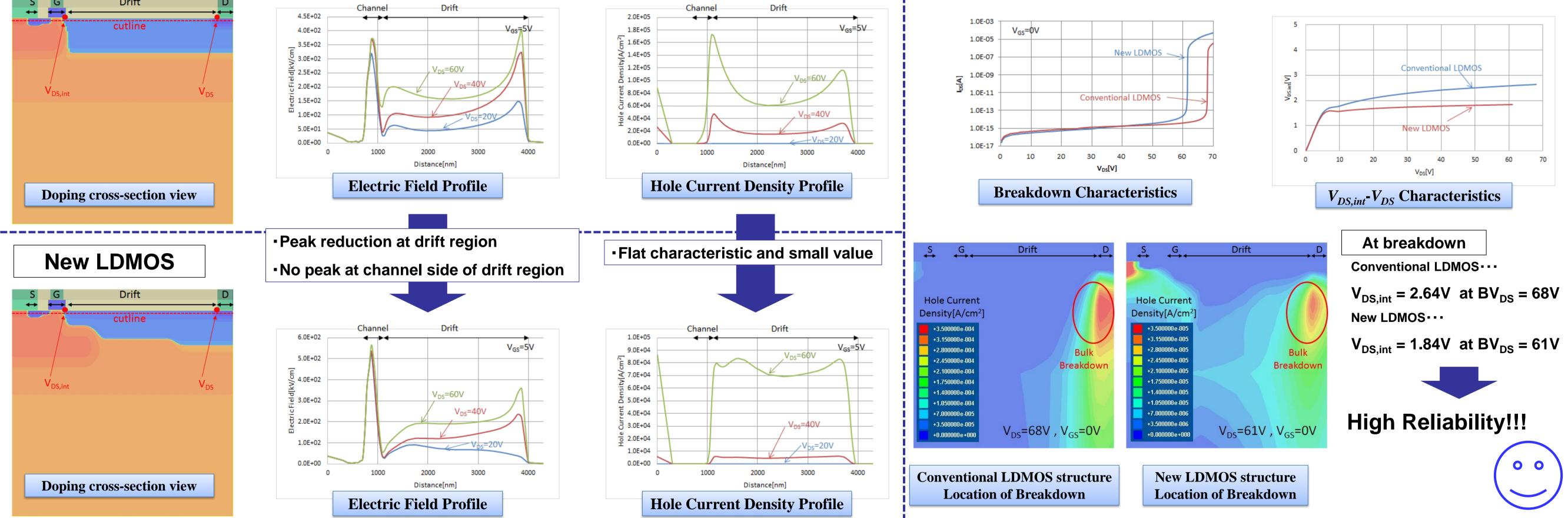

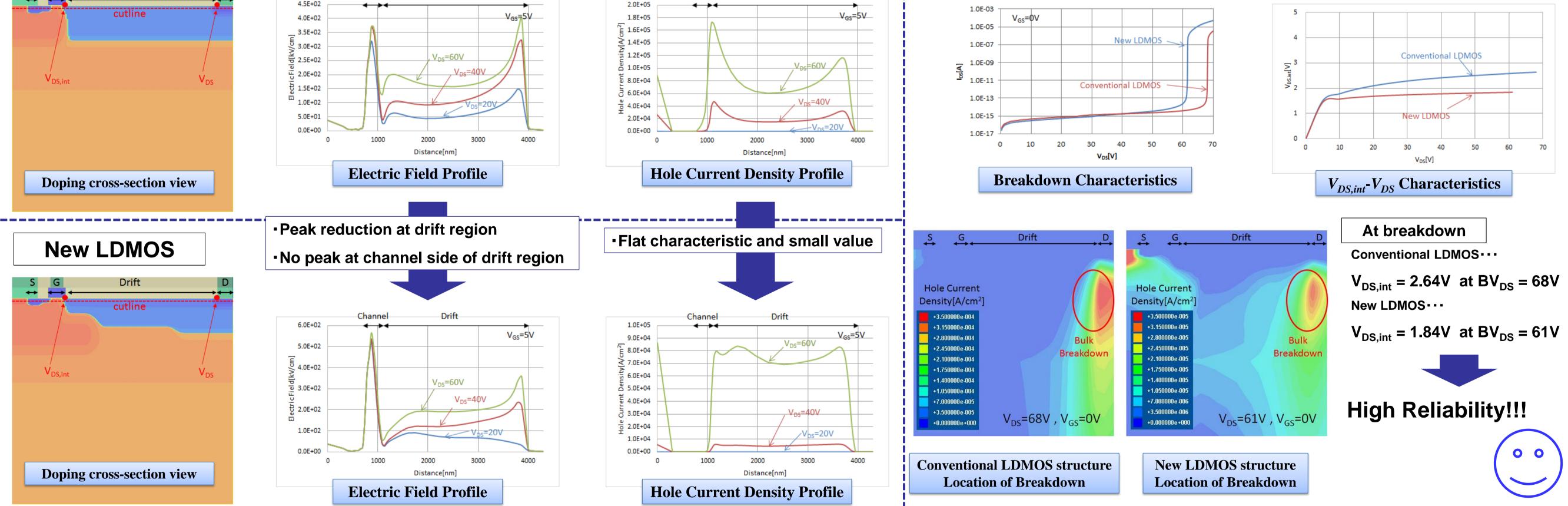

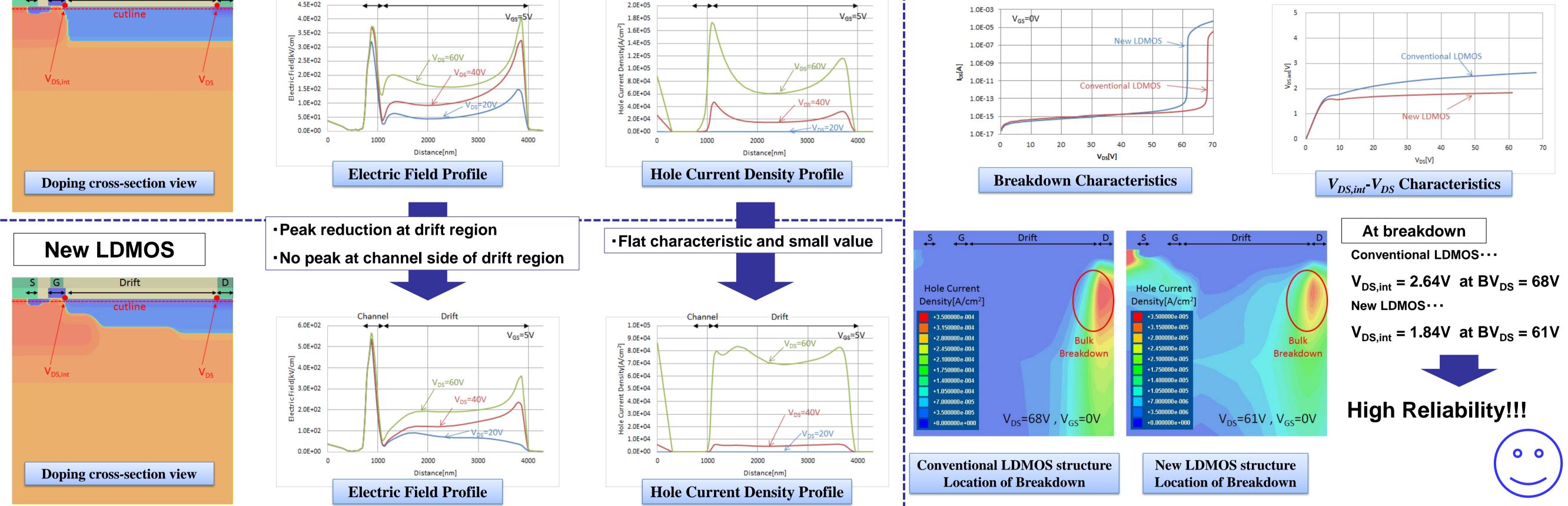

#### **Proposed Structure**

#### **Comparison of Conventional & New**

| Result                                                                                  |                                                                                                                                                                                                         |                                                           |

|-----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|

| Items                                                                                   | Conventional LDMOS                                                                                                                                                                                      | New LDMOS                                                 |

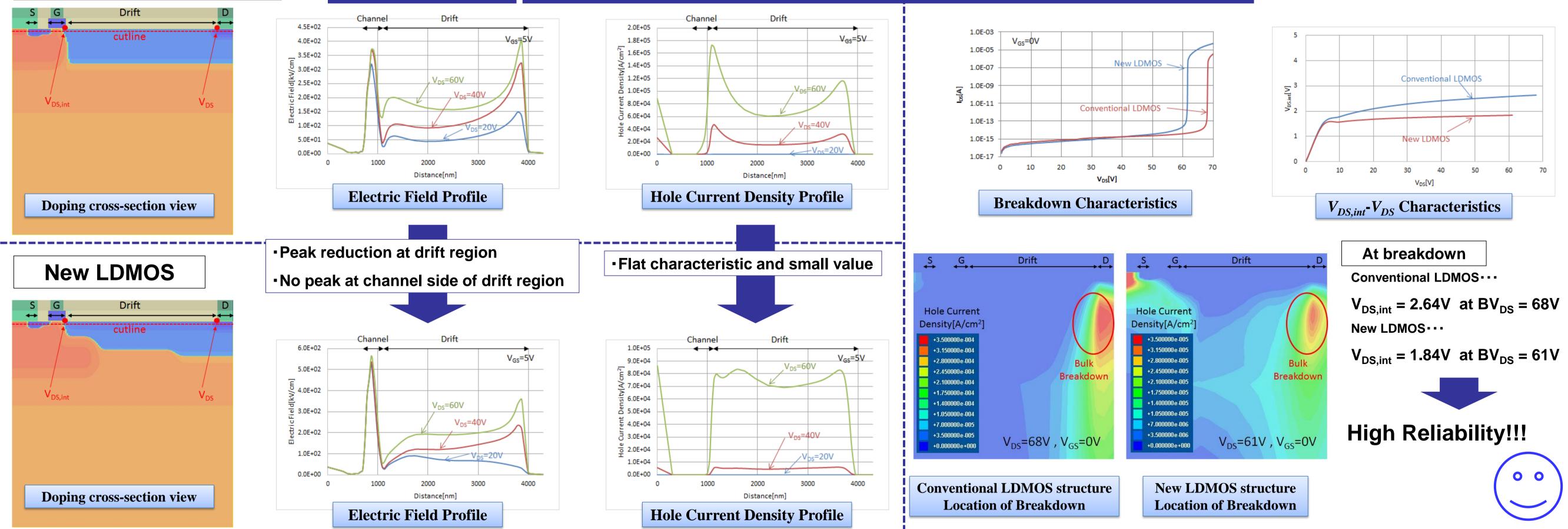

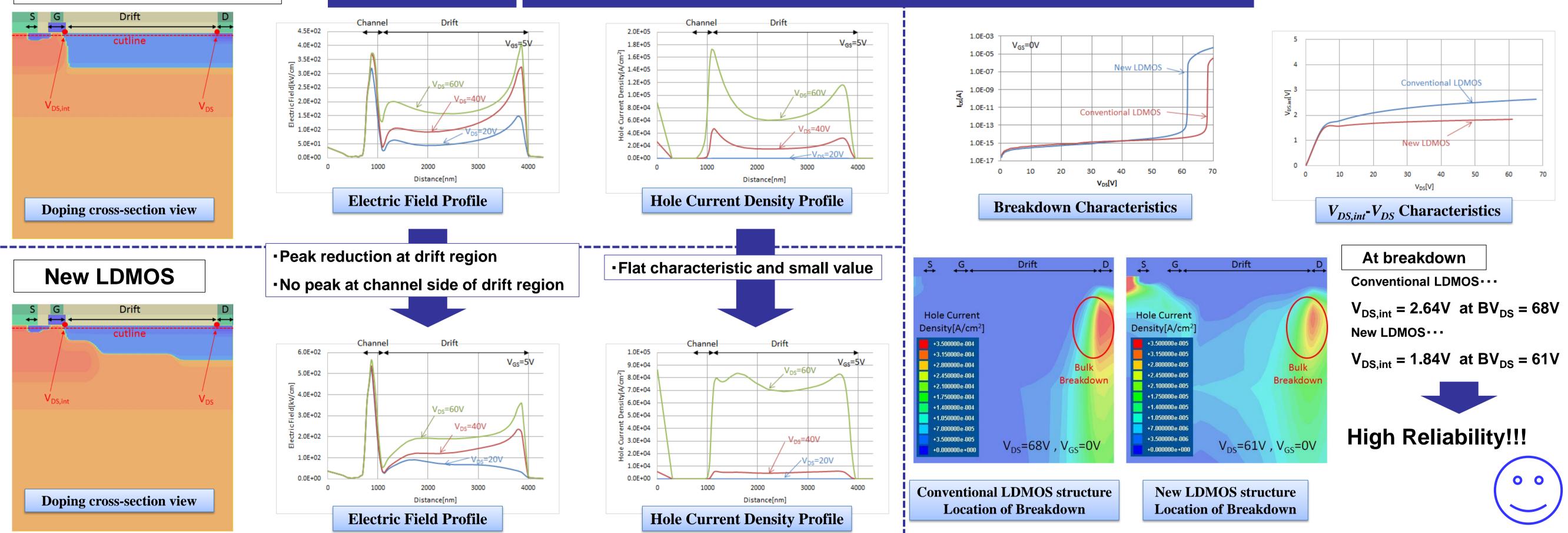

| Hole current density<br>around drain side gate edge<br>of intrinsic MOSFET              | High                                                                                                                                                                                                    | Low                                                       |

| Magnitude of electric field<br>in drift region around drain edge<br>of intrinsic MOSFET | High                                                                                                                                                                                                    | Low                                                       |

| Location of pn junction breakdown                                                       | Bulk                                                                                                                                                                                                    | Bulk                                                      |

| Current increase                                                                        | $\begin{array}{c} Strong \\ \textbf{(current expansion)} \\ & \text{(Generation for} \\ & \text{V}_{\text{DS}} \! > \! 25 \text{V} \text{ and } \text{V}_{\text{GS}} \! \ge \! 5 \text{V}) \end{array}$ | $\underset{V_{DS}>40V \text{ and } V_{GS} \geq 5V}{Weak}$ |

| $V_{DS,int}$ (V) at $BV_{DS}$                                                           | 2.64                                                                                                                                                                                                    | 1.84                                                      |

| $BV_{DS}(V)$                                                                            | 68                                                                                                                                                                                                      | 61                                                        |

| RonA (m $\Omega$ mm <sup>2</sup> )                                                      | 68.7                                                                                                                                                                                                    | 69.3                                                      |

| $V_{\rm T}(V)$ at $I_{\rm DS}=1 \times 10^{-8}  {\rm A}$                                | 2.4                                                                                                                                                                                                     | 2.1                                                       |

### Summary

#### Conclusion

- Proposed a new LDMOS structure for automotive applications.

- Realized by forming dual p-buried layers.

Leading to high reliability and wide SOA.

### References

[1] C. T. Kirk : "A Theory of Transistor Cutoff Frequency (ft) Falloff and High Current Densities", IRE Transactions on **Electron Devices (1962).**

[2] C.-C. Cheng, et. al. : "Investigation of Parasitic BJT Turn-on **Enhanced Two-stage Drain Saturation Current in High-voltage** NLDMOS", 23rd International Symposium on International Power Semiconductor Devices & IC's (2011).

[3] J. Chen : "HV EDMOS Design with Expansion Regime Suppression", Master Thesis of Applied Science, Department of **Electrical and Computer Engineering, University of Toronto (2013).**

**Challenge for the future**

• Reducing the on-resistance

• 3D Simulation, collaborating with

Toronto University, Canada

**AdvanceSoft Corporation is acknowledged**

for providing TCAD simulator.