IEEE 11<sup>th</sup> International Conference on ASIC November 3-6, 2015, Chengdu, China

JAPA

# Study on Maximum Electric Field Modeling Used for HCI Induced Degradation Characteristic of LDMOS Transistors

<u>Masashi Higashino</u>\*, Hitoshi Aoki, Nobukazu Tsukizi, Masaki Kazumi, Takuya Totsuka, Haruo Kobayashi

Gunma University, Japan

#### Supported by MoDeCH Inc.

# OUTLINE

#### Introduction

- Our Research

- HCI Degradation Modeling

- Maximum Electric Function Equation

#### Conclusion

# OUTLINE

#### Introduction

Our Research

#### HCI Degradation Modeling

Maximum Electric Function Equation

#### Conclusion

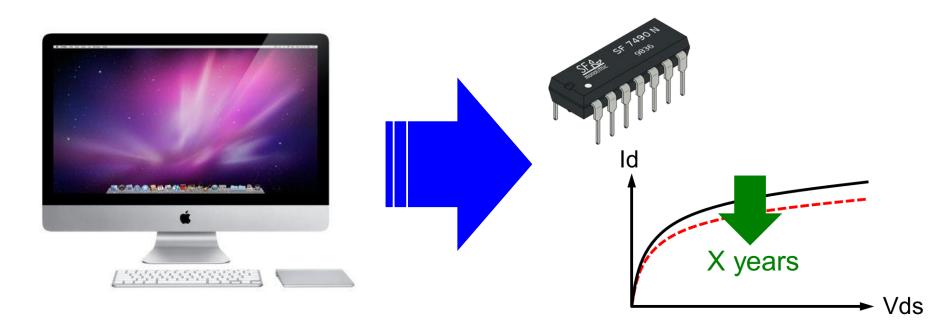

# **Background and Object**

#### Reliability Test Problem in Circuit Design

| Test Items                      | Conditions                              |

|---------------------------------|-----------------------------------------|

| High Temperature Operating Life | Ta=125°C<br>Vop_max, <mark>1000h</mark> |

| Temperature Humidity Bias       | Ta=85°C 85%RH<br>Vop_max, 1000h         |

Circuit design considering with reliability simulations

## **Research Purpose**

Degradation modeling by HCI of n-channel LDMOS'

Maximum electric field modeling for reliability circuit simulations

HCI : Hot Carrier Injection, LDMOS : Laterally Diffused MOSFET

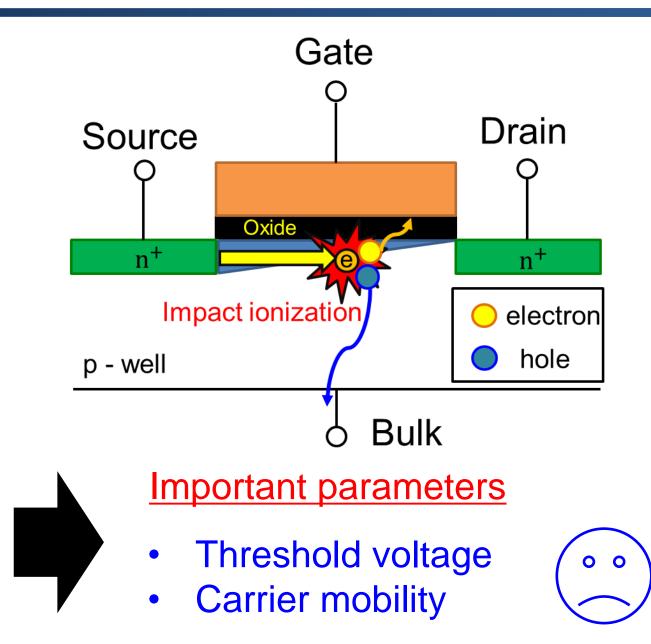

# Degradation by Hot Carrier Injection

# **Degradation of LDMOS Devices**

# OUTLINE

#### Introduction

### Our Research

#### HCI Degradation Modeling

### Maximum Electric Function Equation

Conclusion

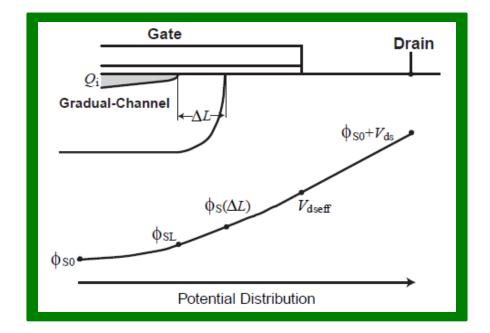

# HiSIM-HV Model for Modeling Vehicle

- Hiroshima-University STARC IGFET Model-High Voltage

- International Industry Standards Model

- Based on Surface-Potential

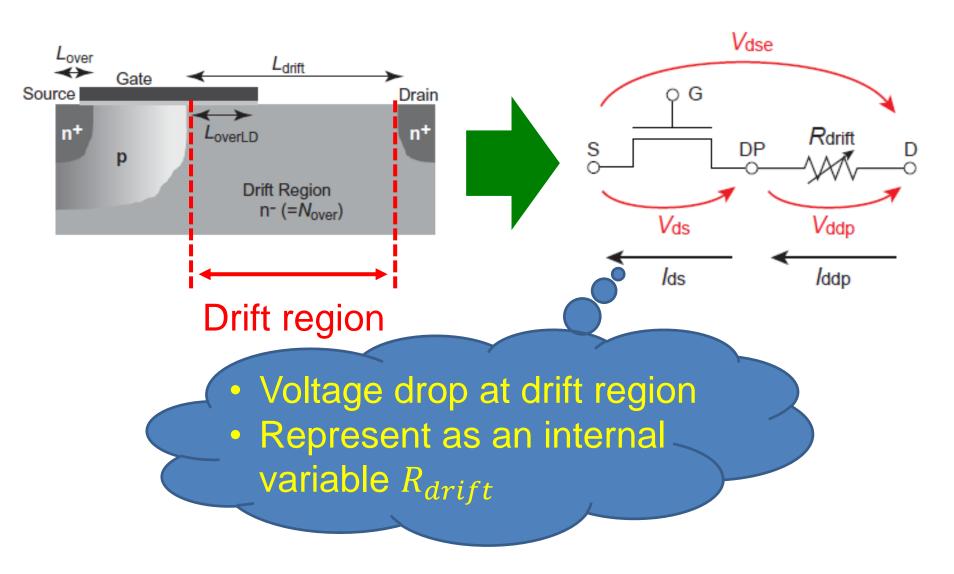

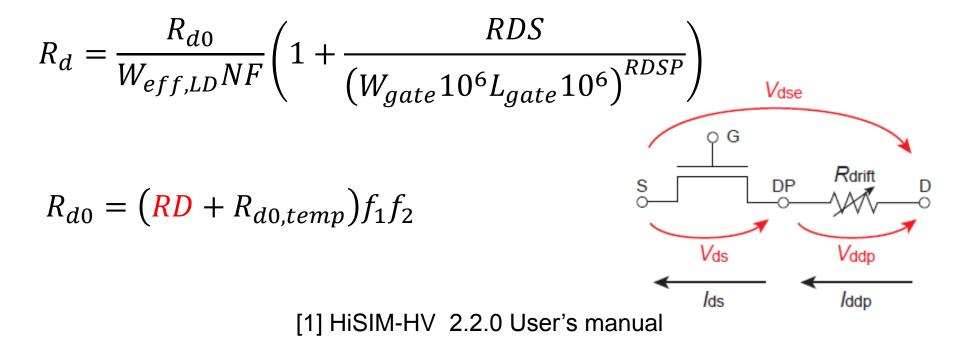

# HiSIM-HV Model used for LDMOS

[1] HiSIM-HV 2.2.0 User's manual

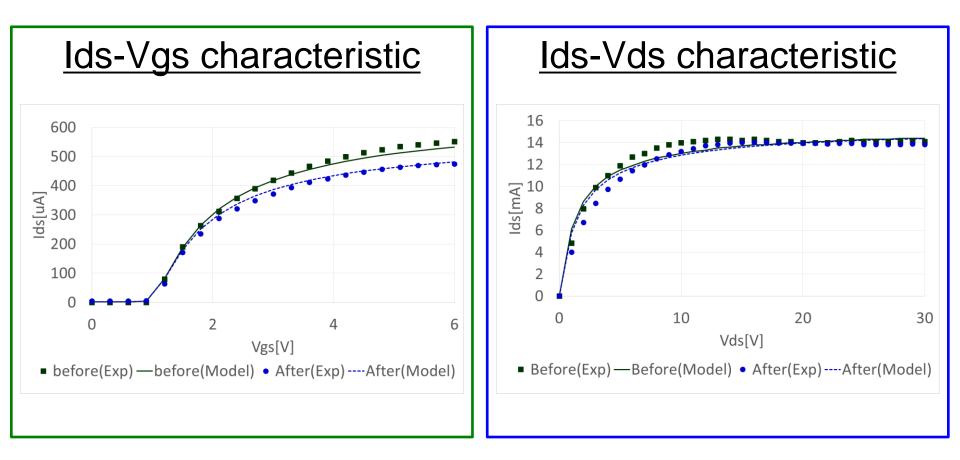

# Model Parameter Extraction and Simulations<sup>11/21</sup>

#### Used measured data

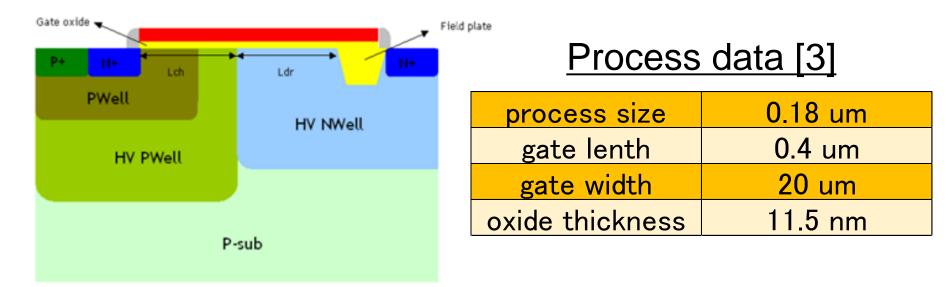

# Cross section view of an n-channel LDMOS [3]

[3] N. Soin.S.S.Shahabudin and K.K.Goh, et al,: "Measurement and Characterization of Hot Carrier Safe Operating Area (HCI-SOA) in 24V n-type Lateral DMOS Transistors", 10th IEEE International Conference on Semiconductor Electronics, pp.659-663 (2012)

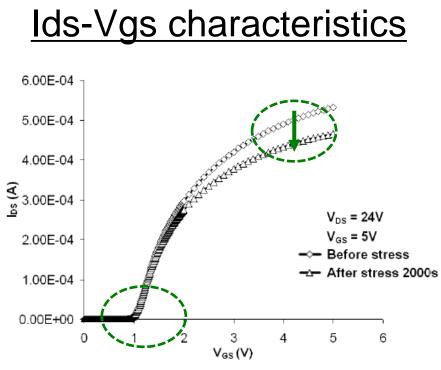

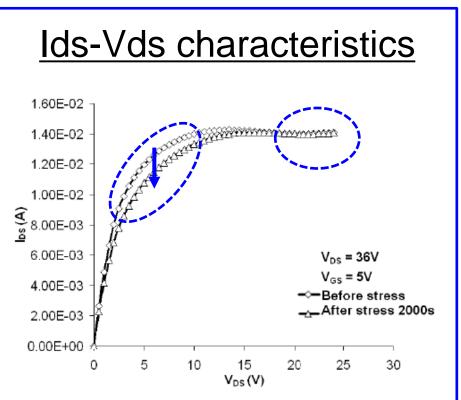

## Analysis of Stress Measurement Results

- Vth is not changed

- Decreasing Ids

12/21

- Ids in saturation region is Not changed

- Ids in pinch-off region is decreased

[3] N. Soin.S.S.Shahabudin and K.K.Goh, et al,: "Measurement and Characterization of Hot Carrier Safe Operating Area (HCI-SOA) in 24V n-type Lateral DMOS Transistors",10th IEEE International Conference on Semiconductor Electronics, pp.659-663 (2012)

## Parameter Selection of HiSIM-HV

$$R_{drift} = (R_d + V_{ds}R_{DVD})\left(1 + RDVG11 - \frac{RDVG11}{RDVG12}V_{gs}\right)$$

$$(1 - V_{bs}RDVB)\left(\frac{LDRIFT1 + LDRIFT2}{DDRIFT - W_{dep}}\right)$$

# **RD Degradation Model**

#### RD : Before $1.1m\Omega$ After $1.4m\Omega$

Increased  $R_{on}$  by decreasing carrier in drift region

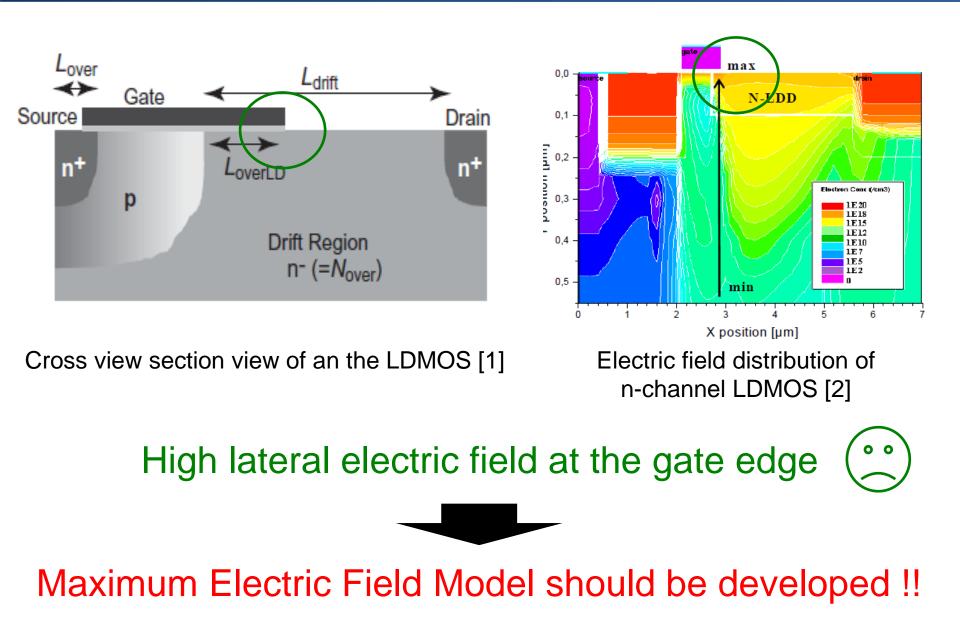

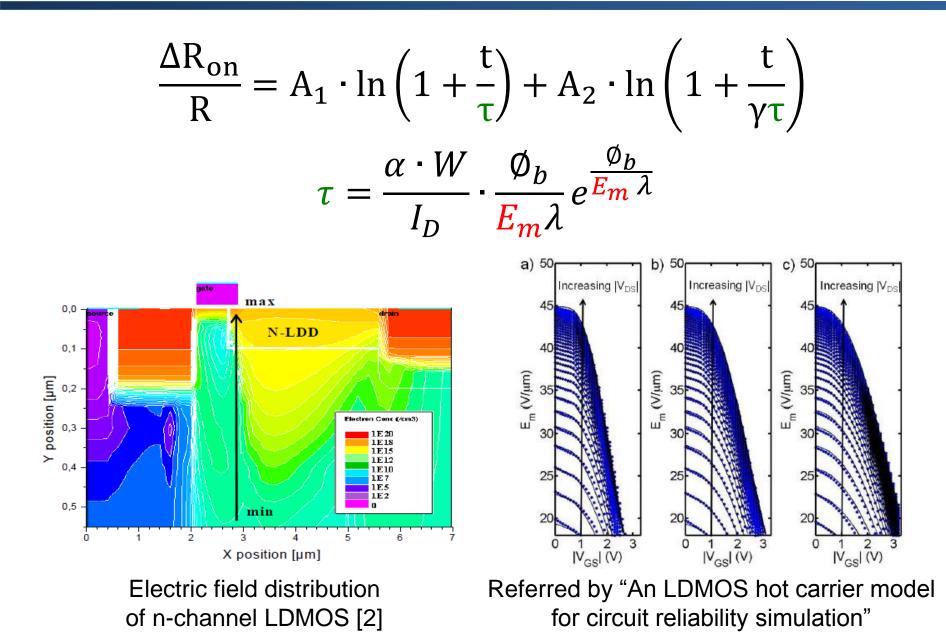

# Maximum Electric field for the Degradation Model

# **Problems of the Referred Model**

The maximum electric field is fitting functions, so far

#### We developed maximum electric field model equations

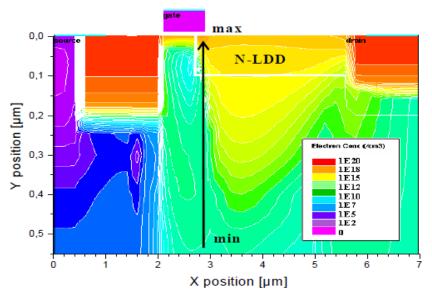

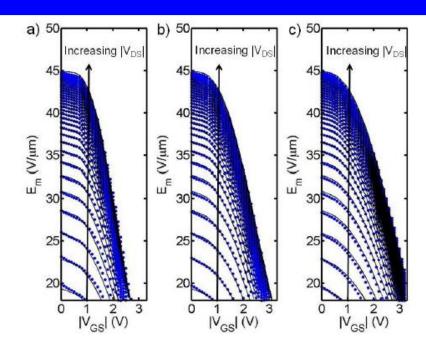

Electric field distribution of n-channel LDMOS [2]

Peak electric field of n-channel LDMOS [4]

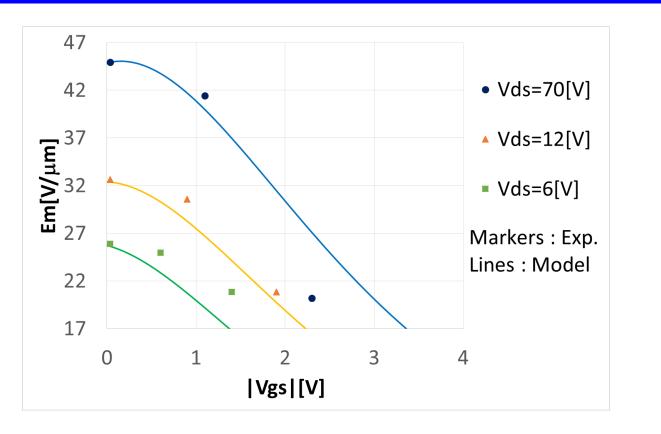

# Maximum Electric Field Function Equation <sup>17/21</sup>

ΗU

Pea

motion Eq.

$$E_{m} = A \cdot exp[-exp(-z) - z + 1]$$

$$A = \alpha \frac{(V_{DS} - V_{DSAT})}{L_{eff}}$$

$$z = \frac{(V_{GS} - V_{TH} - V_{GS\_max})}{\beta}$$

$\alpha$ ,  $\beta$ : fitting parameter,  $V_{GS_max}$ : maximum  $V_{GS}$ ,  $V_{TH}$ : threshold voltage

- Lateral electric field depends on Vds

- Flexible peak value and location

#### Comparison between simulation and proposed function model

The peak value of electric field agrees with T-CAD simulation

The shape of calculated curves is close to T-CAD simulation

# OUTLINE

#### Introduction

### Our Research

#### HCI Degradation Modeling

#### Maximum Electric Function Equation

#### Conclusion

We have characterized fresh and stressed n-channel LDMOS with measurement and simulations.

■We have derived the maximum electric field model equations and demonstrated the effectiveness.

#### **References**

[1]HiSIM-HV 2.2.0 User's manual

[2] M.A.Belaid and K.Ketata : "Hot-Carrier Effects on Power RF LDMOS Device Reliability" EDA Publishing THERMINIC 2008

[3] N. Soin.S.S.Shahabudin and K.K.Goh, et al,: "Measurement and Characterization of Hot Carrier Safe Operating Area (HCI-SOA) in 24V n-type Lateral DMOS Transistors", 10th IEEE International Conference on Semiconductor Electronics, pp.659-663 (2012)

[4] Guido T. Sasse, Jan A.M.Claes and Bart Dev Vries : "An LDMOS hot carrier model for circuit reliability simulation" (2014)

# Thank you for your kind attention

# 謝謝

## Q & A

#### ●発表に使っているLDMOSのプロセスはどこのものか → 論文のデータなので、詳細は不明です

●電界モデルは、SPICEに入れる予定なの? (のようなことを聞かれたと思う) →今後の課題として取り組みます。 (上手く伝わりませんでした)