# 黄金比重み付けDA変換器の構成

<u>澁谷 将平</u>、小林 佑太朗、荒船 拓也、 小林 春夫 群馬大学大学院理工学府 電子情報部門 〒376-8515 群馬県桐生市天神町1-5-1 E-mail:t15804045@gunma-u.ac.jp

二進重み 1,2,4,8,16

非二進重み 1,2,3,6,10,16

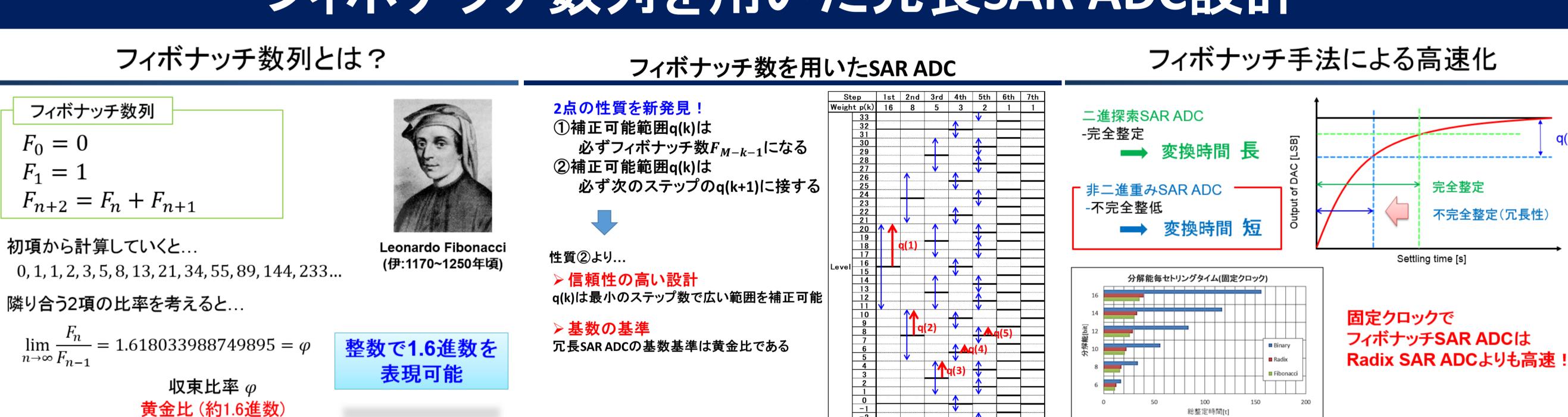

フィボナッチ数列で

冗長性を実現!!

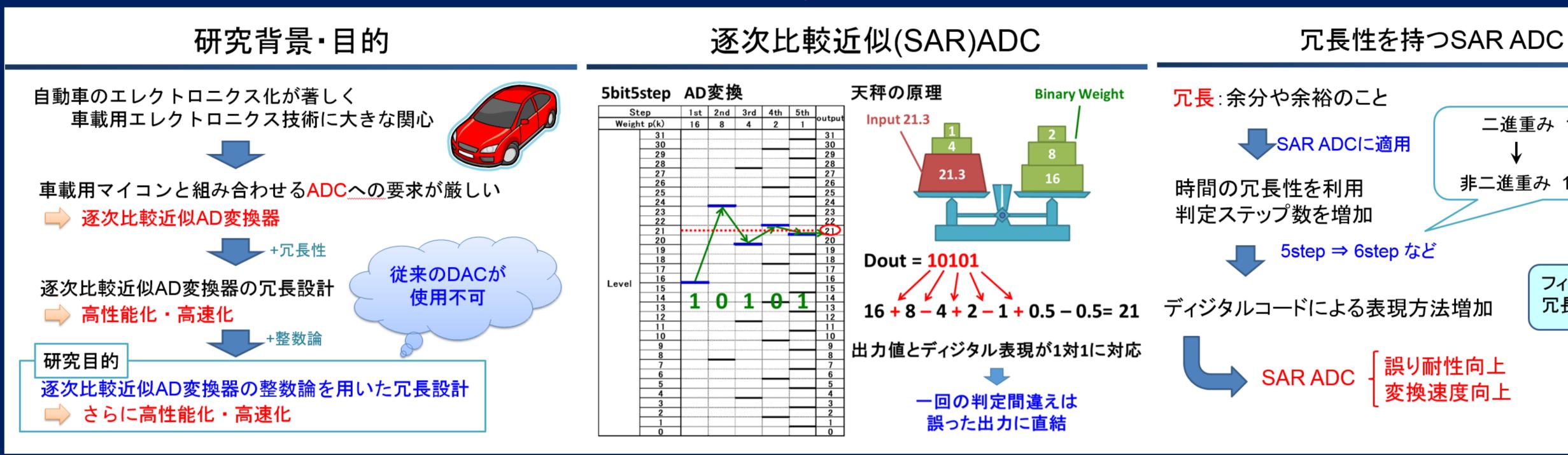

#### 研究目的

## フィボナッチ数列を用いた冗長SAR ADC設計

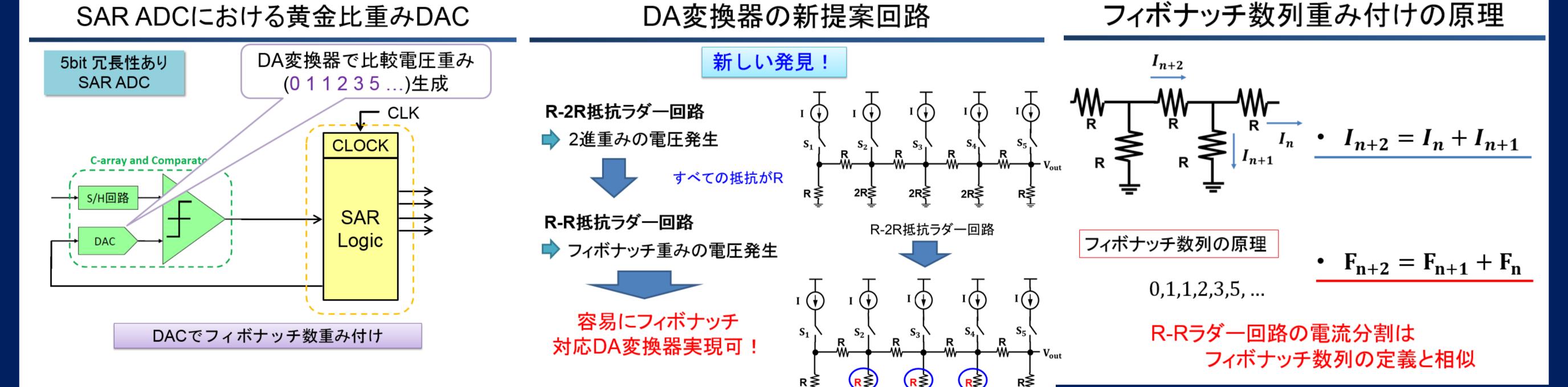

### 黄金比重み付けDA変換器の構成

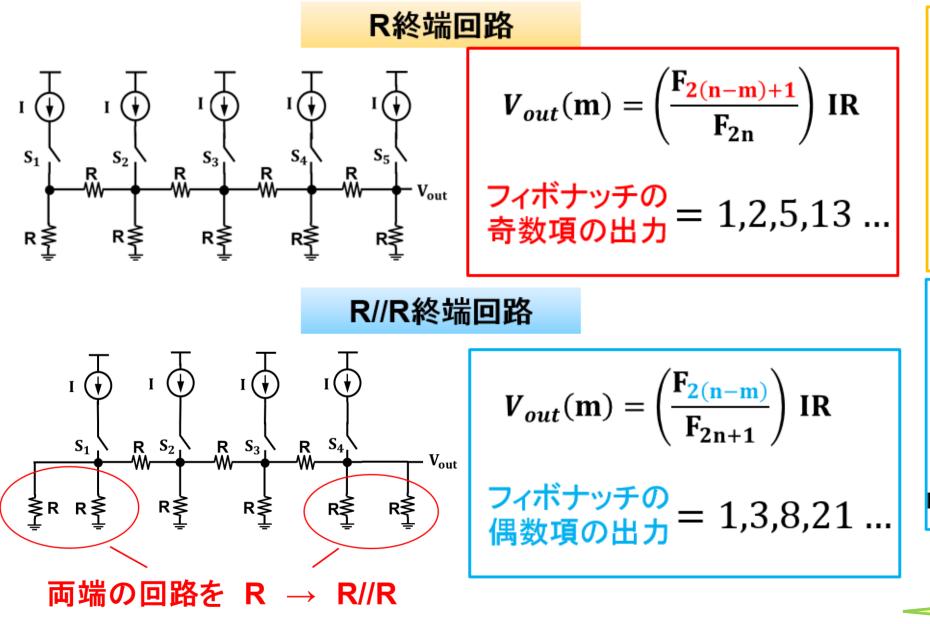

フィボナッチ数列を出力する回路

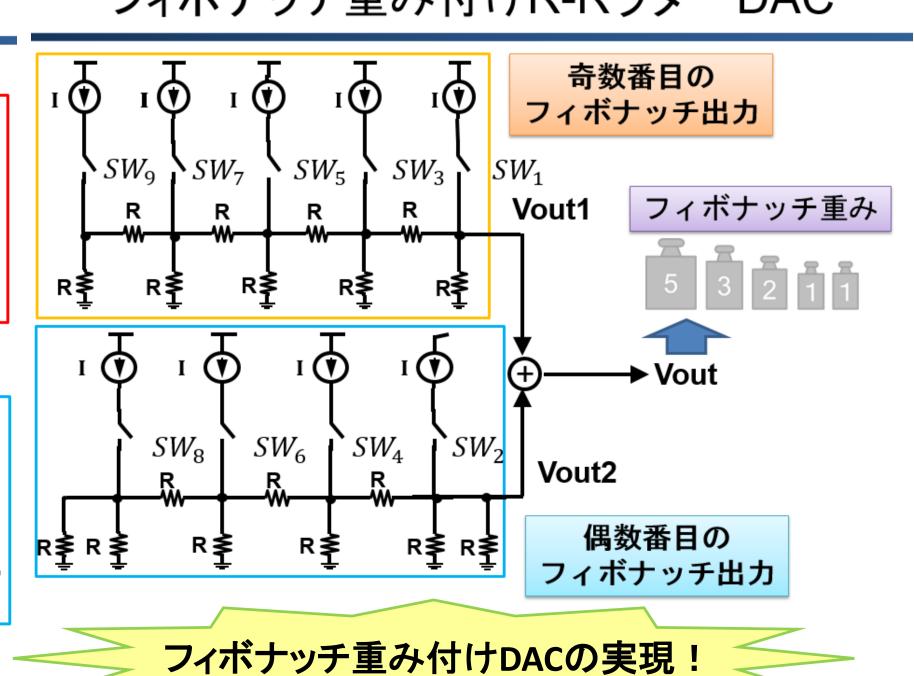

#### フィボナッチ重み付けR-RラダーDAC

R-R抵抗ラダー回路

### 参考文献

◆フィボナッチ冗長設計対応

◆DACで重み付け可能

▶ 整定時間の短縮

➤ 冗長設計による補正力がUP

[1].小林佑太朗、小林春夫 「逐次比較近似ADCの整数論に基づく冗長アルゴリズム設計」 電気学会、電子回路研究会、島根(2014年7月)

➤ SAR ロジック回路の簡略・小規模化

[2].Y. Kobayashi, H. Kobayashi "SAR ADC Algorithm with Redundancy Based on Fibonacci Sequence" International Conference on Analog VLSI Circuits, Ho Chi Minh, Vietnam (Oct., 2014)

簡単な回路構成で実現可能!!

まとめ

まとめ