# 半導体デバイスモデリング技術

○香積 正基 ○ 戸塚拓也 青木均 築地伸和 東野将司 小林 春夫(群馬大学)

> 群馬大学大学院 理工学府 電子情報・数理教育プログラム専攻 小林研究室

- 研究背景

- MOSFETの高信頼性モデル

- LDMOSの高信頼性モデル

- IGBTの高精度マクロモデル

- ・まとめ

- 研究背景

- MOSFETの高信頼性モデル

- LDMOSの高信頼性モデル

- ・IGBTの高精度マクロモデル

- ・まとめ

#### モデリングとは?

・モデル:

方程式や等価回路により動作を表現

・モデリング:

方程式の中には多くの変数(パラメータ)がありプロセス・ デバイスに応じて変化

そのパラメータを実測データを用い抽出・最適化し、高速かつ高精度化

#### モデリングの重要性

• 信頼性試験: コストや時間がかかる

回路設計者がシミュレーション段階で 予測できることによって回避可能

回路シミュレーションを行う際 実際の回路動作にどれだけ近づけるかが重要

#### **MOSFET**

・近年、ますますプロセスの微細化が進む

# $V_{GS}$ $\dot{\tau}$ ート $V_{DS}$ $\dot{\tau}$ ート $\dot{\tau}$

MOSFETの簡易構造図

#### メリット

- ▶ 集積回路の小型化

- ▶ 高速化

- 低消費電力

#### デメリット

- ▶ 製造時の特性ばらつき

- ▶ 回路の比精度の劣化

- ▶ ノイズの増大

#### デジタル回路に恩恵

#### アナログ回路設計を困難

微細化が進むにつれMOSトランジスタの経時・温度劣化による 影響が大きくなるため高信頼性モデルの作成は重要

事前解析できる環境が必要

## 研究背景2

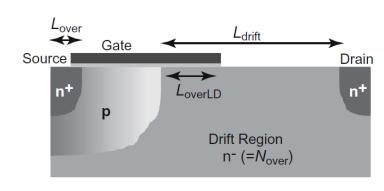

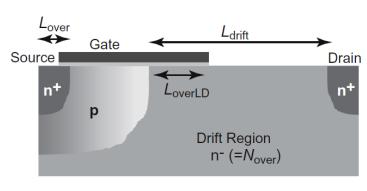

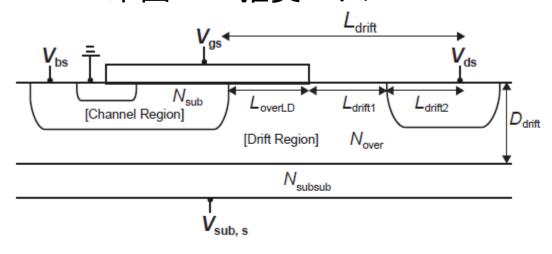

横方向拡散MOS Laterally Diffused MOS(LDMOS)

LDMOSの構造図[1]

- •ドレイン-ゲート間の電界強度緩和する構造

- ・耐圧が高く(~数十ボルト程度), オン抵抗が低い

LDMOSの使用用途: DC/DCコンバータの出力段

携帯基地局用のパワーアンプなど

低電圧領域で用いるMOSトランジスタよりも経時・温度劣化は顕著 劣化によるデバイス信頼性が重要な課題

・高電界領域で発生するHot Carrier Injection効果 による劣化(オン抵抗の増加)が支配的

事前解析できる環境が必要

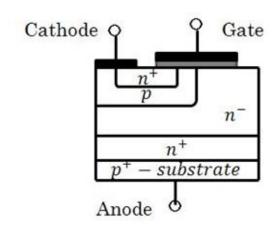

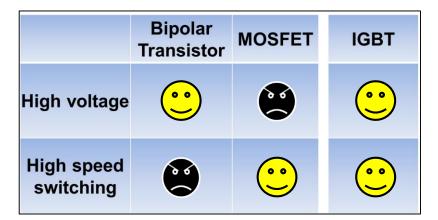

## 絶縁ゲートバイポーラトランジスタ Insulated Gate Bipolar Transistor(IGBT)

- ・高耐圧・大電流に適したパワー半導体

- ・絶縁ゲートによる電圧制御型

- •~数千[V]ほどの高耐圧素子

|                      | Bipolar<br>Transistor | MOSFET | IGBT |

|----------------------|-----------------------|--------|------|

| High voltage         |                       |        |      |

| High speed switching |                       |        |      |

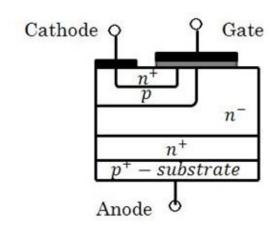

IGBTの簡易構造図

IGBTの使用用途:

車載用高耐圧素子や鉄道車両制御など

高信頼性が求められるアプリケーションに使用されるため、 多くの回路シミュレーションソフトでの事前解析における高精度化は重要

- 研究背景

- MOSFETの高信頼性モデル

- LDMOSの高信頼性モデル

- IGBTの高精度マクロモデル

- ・まとめ

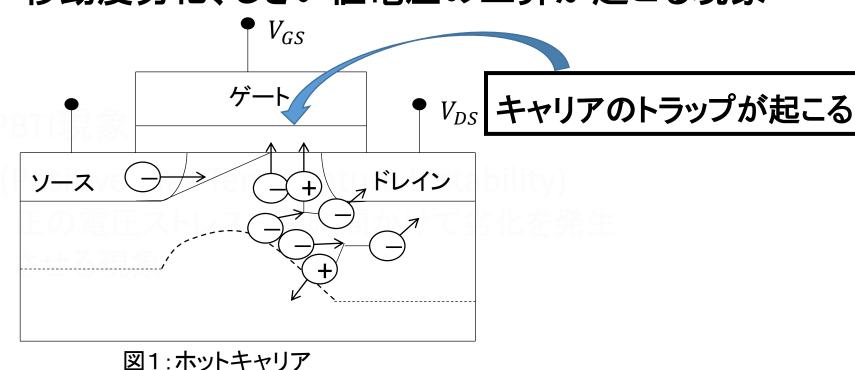

HCI現象

(Hot Carrier Injection)

高電界領域で電界加速により チャネルが大きなエネルギーを得ることで 移動度劣化、しきい値電圧の上昇が起こる現象

· HCI現象

(Hot Carrier Injection)

高電界領域で電界加速により

チャネルが大きなエネルギーを得ることで

移動度劣化、しきい値電圧の上昇が起こる現象

· PBTI現象

より支配的であるHCI現象に着目し 特性解析を行う.

(Positive Bias Temperature Instability)

正の電圧ストレスを長時間かけて

しきい値電圧が上昇する現象

BErkeley Reliability Tools (BERT)のモデル

SPICE上でシミュレートするのに適している

劣化前のDCパラメータを取り込み シミュレーション上で劣化DC特性を予想する

BERTのモデルをBSIM4に使えるように 2004年にKufluogluとAlamによって開発された RDモデル(Reaction-Diffusion model)を基に開発する

## RDモデル

#### 界面トラップ数

$$N_{H(0)}N_{it} \approx \frac{k_F}{k_R}N_0$$

$N_{H(0)}$  界面における水素濃度の初期値

$N_{it}$  界面トラップ数

$k_F$  酸化物電界依存フォワード解離速度定数

k<sub>R</sub> アニーリング速度定数

No Si-H結合の初期値

#### チャネル/酸化膜界面での水素反応式

$$N_{H_x} = k_H N_H^{n_x}$$

N<sub>H</sub> 体積あたりの水素粒子の濃度

k<sub>H</sub> 反応定数

$n_x$  水素粒子あたりの水素原子数

#### Si-H結合の数より界面トラップ数を算出可能

$$N_{it} = \frac{\pi W}{2A_{tot}} n_{\chi} \int_{0}^{\sqrt{D_{H_{\chi}t}}} \left( N_{H_{\chi}(0)} \left[ r - \frac{r^2}{\sqrt{D_{H_{\chi}t}}} \right] \right) dr$$

$$=N_{H_{\mathcal{X}}(0)}\frac{\pi n_{\mathcal{X}}}{12L}D_{H_{\mathcal{X}}t}$$

$D_{H_x t}$   $N_H$ の密度

$A_{tot}$  ゲート下の総面積

L MOSFETの長さ

W MOSFETの幅

## DC HCIモデル1

先ほどの3つの式を組み合わせると下式になる

$$N_{it} = \left(\frac{k_F N_0}{k_R}\right)^{\frac{n_\chi}{1+n_\chi}} \left(\frac{n_\chi \pi k_H}{12L} D_H\right)^{\frac{1}{1+n_\chi}} * t^{\frac{1}{1+n_\chi}}$$

$D_H$  水素原子の密度  $t$  時間  $C_{HCI}$ 技術依存なパラメータ

界面トラップによる電圧依存特性をしきい値特性カーブのずれで表現

$$\Delta V_{th_{DEGRADATION}} = C_{HCI} \left( \frac{k_F N_0}{k_R} \right)^{\frac{n_\chi}{1 + n_\chi}} \left( \frac{n_\chi \pi k_H}{12L} D_H \right)^{\frac{1}{1 + n_\chi}} * t^{\frac{1}{1 + n_\chi}}$$

### しきい値(BSIM4)

$$\begin{split} V_{th} &= \textit{VTH0} + \Delta \textit{V}_{th,\ body\_effect} - \Delta \textit{V}_{th,\ carge_{sharing}} - \Delta \textit{V}_{th,\ DIBL} \\ &+ \Delta \textit{V}_{th,\ reverse\_short\_cannel} + \Delta \textit{V}_{th,\ narrow_{width}} \\ &+ \Delta \textit{V}_{th,\ small\_size} - \Delta \textit{V}_{th,\ pocket\_implant} \quad + \Delta \textit{V}_{th\_DEGRADATION} \end{split}$$

14

## DC HCIモデル2

•移動度劣化現象のモデル化をVthを用いて実現

#### BSIM4の移動度モデル(MOBMOD=2)

$$\mu_{eff} = \frac{00}{1 + (UA + UC * V_{bseff}) \left[\frac{V_{gsteff} + C_0(VTH0 - VFB - \emptyset_S)}{TOXE}\right]^{EU}}$$

フラットバンド電圧 U0 キャリア移動度 **VFB**  $V_{gsteff}$   $V_{qs}$ - $V_{th}$ の実効値 移動度劣化の一次係数 **UA**

移動度劣化の基板効果係数 UC 実効基板・ソース電圧  $V_{bseff}$

電気ゲート酸化膜厚 **TOXF** 表面電位  $\emptyset_{s}$

ドレイン電圧がゼロにおけるしきい値電圧 VTH0 定数でnMOSの場合2.0  $C_0$

$$\Delta V_{th_{DEGRADATION}} = C_{HCI} \left( \frac{k_F N_0}{k_R} \right)^{\frac{n_\chi}{1 + n_\chi}} \left( \frac{n_\chi \pi k_H}{12L} D_H \right)^{\frac{1}{1 + n_\chi}} * t^{\frac{1}{1 + n_\chi}}$$

•しきい値電圧のHCIによるずれを移動度モデル式に代入

➡ 移動度劣化現象のモデル化

## 製作したTEG

- ・90nmプロセスを用いたnチャネルMOSFET シミュレーションに用いるデバイス

- ・Large チャネル幅 10.0μm チャネル長 10.0μm

#### 劣化させる環境

・65nmのデバイスの実験データ

をもとにパラメータ劣化させる

- · 温度 300.15K

- ・劣化時間 1000秒

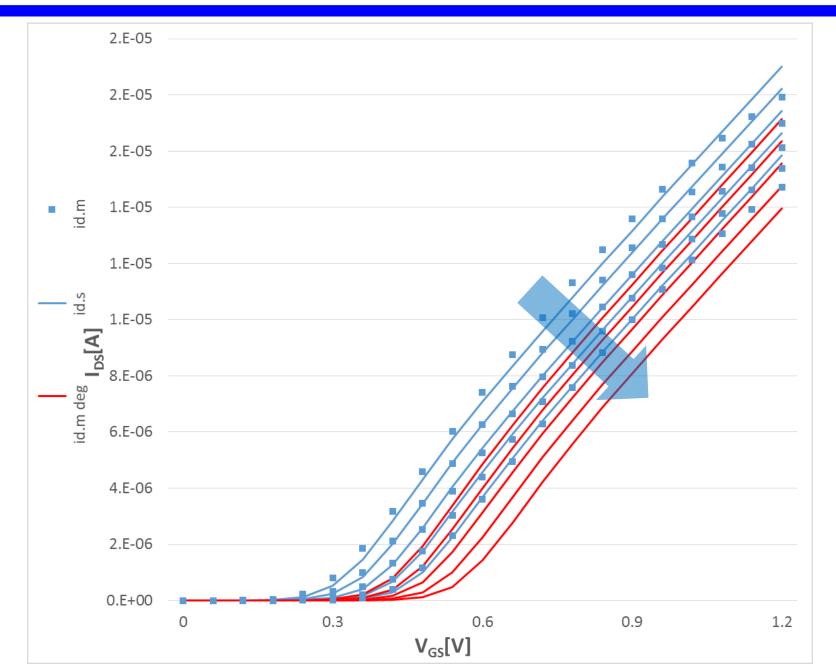

# Large I<sub>D</sub> - V<sub>GS</sub>

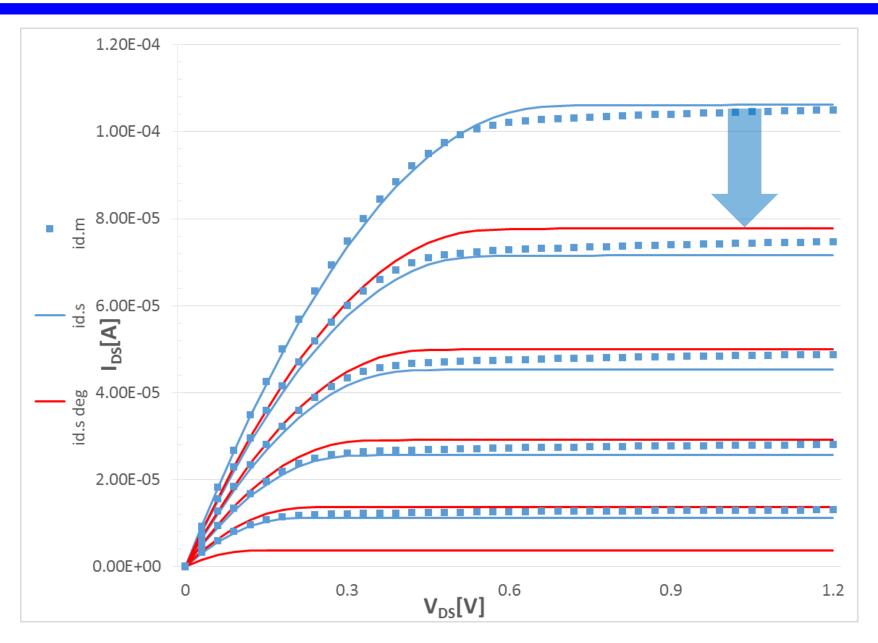

# Large $I_D - V_{DS}$

Fresh

70min後

# **劣化測定結果**: I<sub>DS</sub>-V<sub>GS</sub>

- $80^{\circ}\text{C}, V_{DS} = 1.2 \text{V}, V_{GS} = 1.0 \text{V}$

- ・ デバイスサイズ L 0.2um W5um

- ・HCI現象を用いて界面トラップによる しきい値特性カーブのずれをSPICEモデルに代入, 移動度劣化現象をモデル化し、劣化シミュレーションを開発

- ・TEGを用いてフレッシュ状態のモデルパラメータを抽出 シミュレーション上で劣化DC特性を示した

・実測から、劣化モデルを適用できることを確認した

- 研究背景

- MOSFETの高信頼性モデル

- LDMOSの高信頼性モデル

- ・IGBTの高精度マクロモデル

- ・まとめ

## 研究背景

## 横方向拡散MOS Laterally Diffused MOS(LDMOS)

- •ドレイン-ゲート間の電界強度緩和する構造

- ・耐圧が高く、オン抵抗が低い(~数十ボルト程度)

- ・LDMOSの使用用途: DC/DCコンバータの出力段

携帯基地局用のパワーアンプなど

LDMOSの構造図[1]

低電圧領域で用いるMOSトランジスタよりも経時・温度劣化は顕著 劣化によるデバイス信頼性が重要な課題

・高電界領域で発生するHot Carrier Injection効果 による劣化(オン抵抗の増加)が支配的

事前解析できる環境が必要

## HiSIM-HVにおけるドリフト式

Hi-SIM-HVとは 回路シミュレータに搭載されている LDMOS米国CMC推奨モデル

$$R_{drift} = \left(R_{\mathsf{d}} + V_{\mathsf{ds}} + R_{\mathsf{DVD}}\right) \left(1 + \mathsf{RDVG11} - \frac{\mathsf{RDVG11}}{\mathsf{RDVG12}} \cdot V_{\mathsf{gs}}\right) \cdot \left(1 - V_{\mathsf{bs}} \cdot \mathsf{RDVB}\right) \cdot \left(\frac{\mathsf{LDRIFT1} + \mathsf{LDRIFT2}}{\mathsf{DDRIFT} - W_{\mathsf{dep}}}\right)$$

$$R_d = \frac{R_{\text{d0}}}{W_{\text{eff,LD}} \cdot \text{NF}} \left( 1 + \frac{\text{RDS}}{\left(W_{\text{gate}} \cdot 10^6 \cdot L_{\text{gated0}} \cdot 10^6\right)^{\text{RDSP}}} \right)$$

$$R_{d0} = \left( \mathbf{RD} + R_{d0, \text{temp}} \right) f_1 \cdot f_2$$

## オン抵抗増加基準モデルの方程式

$$\frac{\Delta R_{on}}{R_{on}} = A_1 \ln \left( 1 + \frac{t}{\tau} \right) + A_2 * \ln \left( 1 + \frac{1}{\gamma * \tau} \right)$$

$$A_1$$

,  $A_2$ ,  $\gamma$  フィッテングパラメータ  $t$  ストレス時間

τ 特性時間

$$\tau = \frac{\alpha \cdot W}{\mathbf{I}_D} \cdot \frac{\phi_b}{E_m * \lambda} \cdot e^{\frac{\phi_b}{E_m \cdot \lambda}}$$

α フィッテングパラメータ

W デバイスの幅

$E_m$  ピーク電界の大きさ

$\phi_b$   $\mathsf{S_{i} ext{-}O_2}$ のエネルギー障壁を乗り越えるために

必要なエネルギー

λ キャリアが散乱しエネルギーを失う前に電場に届く平均

$$\lambda = \lambda_0 \cdot \tanh\left(\frac{E_p}{2 \cdot k_B \cdot T_i}\right)$$

$E_n$  Si中の光学フォノンエネルギー(0.063 eV)

k<sub>B</sub> ボルツマン定数(8.62\*10E-5 eV/K)

$T_i$  接合温度

$\lambda_0$  K=0でのホットキャリアの平均移動速度

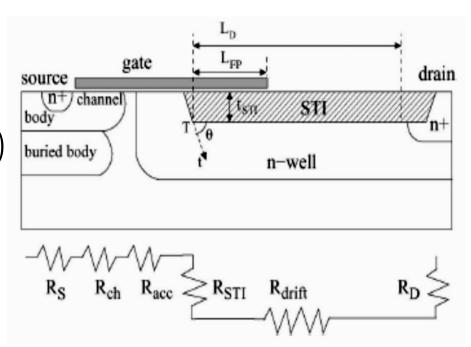

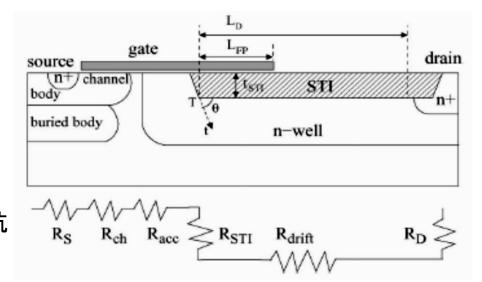

## LDMOSとオン抵抗の相関

$$R_{drift} = R_{drift,1} + R_{drift,2}$$

$R_{drift,1}$ は、ゲート下の蓄積領域  $R_{drift,2}$ は $R_{drift,1}$ 以降にあるドリフト領域及びドレイン端

$$R_{drift.1} = \left(\frac{1}{R_{drift,acc}} + \frac{1}{R_{drift,sh}}\right)^{-1}$$

$$R_{drift,acc} = \frac{L_{FP,eff}}{\left(\mu_{eff}C_{STI}W(V_{GS} - V_{fb})\right)}$$

$$R_{drift,sh} = \frac{L_{FP}}{q\mu_n N_d W t_{eff}}$$

$$R_{drift,2} = \frac{(L_D - L_{FP})}{(q\mu_n N_d W t_{eff})}$$

## オン抵抗モデルの方程式

$$R_{drift.1} = \left(\frac{1}{R_{drift,acc}} + \frac{1}{R_{drift,sh}}\right)^{-1}$$

$$R_{drift,acc}$$

蓄積領域のオン抵抗  $R_{drift,sh}$  シート抵抗

$$R_{drift,acc} = \frac{L_{FP,eff}}{\left(\mu_{eff}C_{STI}W(V_{GS} - V_{fb})\right)}$$

$$C_{STI}$$

$\epsilon_{ox}/t_{STI}$

$\mathsf{C}_{\mathsf{STI}} \qquad \stackrel{\epsilon_{ox}}{t_{STI}} \ t_{oSTI} \qquad \mathsf{STI酸化膜の厚さ}$

$L_{FP,eff}$  実行フィールドプレート $(L_{FP})$

フィッテングパラメータ

$$R_{drift,sh} = \frac{L_{FP}}{(q\mu_n N_d W t_{eff})}$$

$$t_{\it eff}$$

STIの実効的な深さ

$$R_{drift,2} = \frac{(L_D - L_{FP})}{/(q\mu_n N_d W t_{eff})}$$

L<sub>n</sub> 実行ドリフト長

#### LDMOS構造に対応したオン抵抗式

$$R_{drift.1} = \left(\frac{1}{R_{drift,acc}} + \frac{1}{R_{drift,sh}}\right)^{-1}$$

$$R_{drift,acc} = \frac{L_{FP,eff}}{\left(\mu_{eff}C_{STI}W(V_{GS}-V_{fb})\right)}$$

$$R_{drift,sh} = \frac{L_{FP}}{(q\mu_n N_d W t_{eff})}$$

#### HiSIM-HV ドリフト領域におけるオン抵抗式

$$R_{drift} = \left(R_{\text{d}} + V_{\text{ds}} + R_{\text{DVD}}\right) \left(1 + \text{RDVG11} - \frac{\text{RDVG11}}{\text{RDVG12}} V_{\text{gs}}\right) \cdot \left(1 - V_{\text{bs}} \cdot \text{RDVB}\right) \cdot \left(\frac{\text{LDRIFT1} + \text{LDRIFT2}}{\text{DDRIFT} - W_{\text{dep}}}\right)$$

V<sub>GS</sub>依存があるため HiSIM-HVにおけるRDVG11 または、RDVG12を変化させることで表現可能

$$R_{drift,2} = \frac{(L_D - L_{FP})}{(q\mu_n N_d W t_{eff})}$$

$R_{drift,2}$ はドリフト領域及びドレイン端

- LDD層LFP後のドリフト・ドレイン端までの抵抗

- この領域が、HCIによって劣化

- HiSIM-HVではLDDのドレイン端コンタクト抵抗, RD, に相当

- μ<sub>n</sub>はInterfacial TrapによるMobility degradationにより劣化

HiSIM-HVにおけるオン抵抗劣化 RD,RDVG11,RDVG12を用いて表現可能

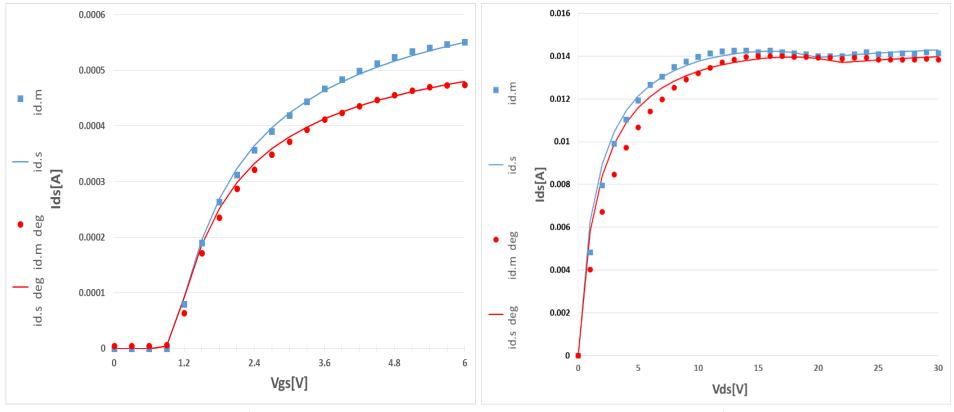

## 論文データでの劣化抽出

N. Soin.S.S.Shahabudin and K.K.Goh, et al,: "Measurement and Characterization of Hot Carrier Safe Operating Area (HCI-SOA) in 24V n-type Lateral DMOS Transistors",10th IEEE International Conference on Semiconductor Electronics, pp.659-663 (2012) において報告されている直流電流・電圧特性を数値化し、測定データとした

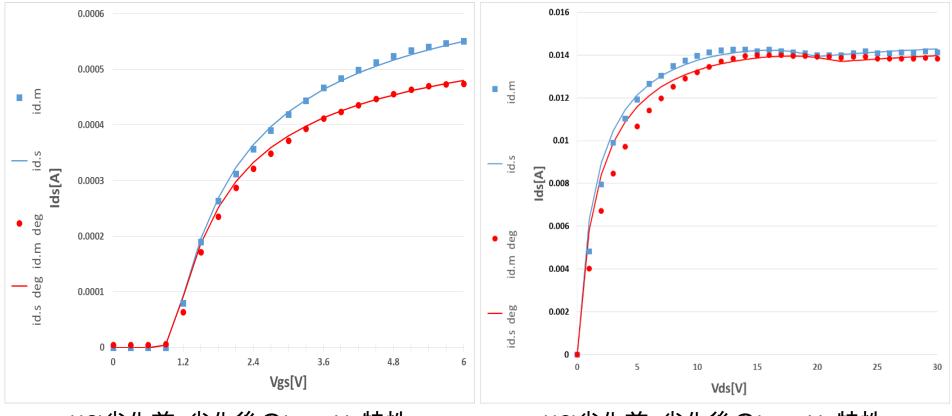

HCI劣化前・劣化後のI<sub>ds</sub> vs V<sub>gs</sub>特性

HCI劣化前・劣化後のI<sub>ds</sub> vs V<sub>ds</sub>特性

## 論文データでの劣化抽出

RD, RDVG12のみを使用して合わせこんだ

RD 1.076m → 1.301m(増加)

RDVG12 6.026 → 9.081 (増加)

HCI劣化前・劣化後のI<sub>ds</sub> vs V<sub>gs</sub>特性

HCI劣化前・劣化後のI<sub>ds</sub> vs V<sub>ds</sub>特性

## 論文データからは劣化した結果しか分からない

→劣化測定を行い劣化時間とパラメータ変化の相互関係を検証

### 測定条件

```

I<sub>ds</sub>-V<sub>gs</sub>測定

V<sub>gs</sub>=0~5[V]かつV<sub>ds</sub>=50~150[mV]であり50[mV]ステップ

I<sub>ds</sub>-V<sub>ds</sub>測定

V<sub>gs</sub>=2.1~2.5[V] であり0.1[V]ステップかつV<sub>ds</sub>=0~5[V]

温度は室温

```

#### ストレスバイアス

```

V<sub>gs</sub>=2.4[V], V<sub>ds</sub>=2.4[V]

劣化時間は2[h]ごとに1000[h]

```

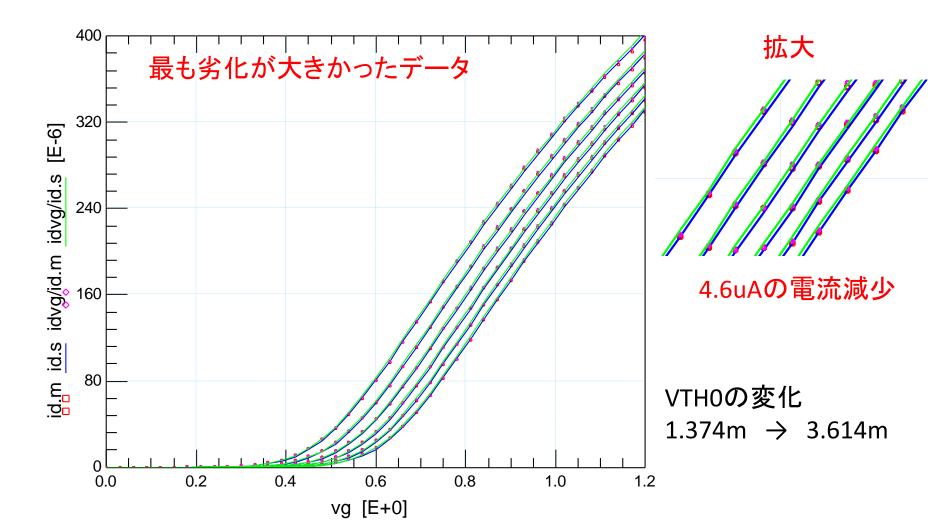

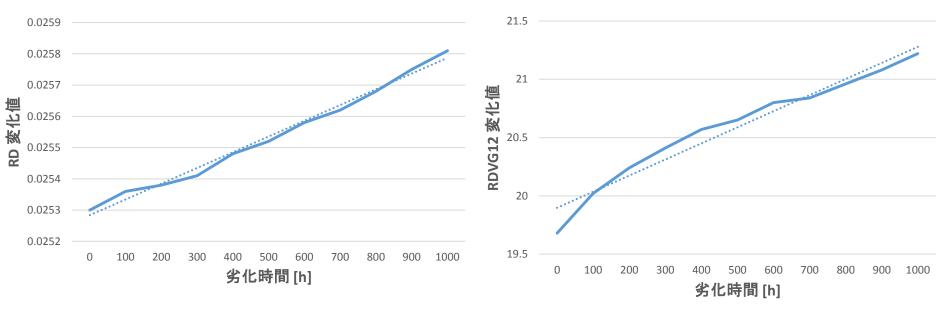

## 測定データでの劣化抽出

RDと劣化時間の相関関係

RDVG12と劣化時間の相関関係

$$RD_{stress} = A_1 * t_{deg} + RD_{fresh}$$

$RDVG12_{stress} = B_1 * t_{deg} + RDVG12_{fresh}$

$t_{deg}$  劣化時間  $RD_{fresh}$ 及び $RDVG12_{fresh}$  パラメータの初期値  $A_1$ ,  $B_1$  フィッテングパラメータ

- HiSIM-HVとLDMOS構造からドリフト領域における オン抵抗の関係性を示し、HCI劣化による パラメータ変化の予想を立てた

- ・ 論文データを用いて、予想通り劣化を示せるか検証した

・劣化測定を行いパラメータ変化と劣化時間の 関係を調べパラメータを式に置き換えることで 劣化を示すモデルを開発した

- 研究背景

- MOSFETの高信頼性モデル

- LDMOSの高信頼性モデル

- IGBTの高精度マクロモデル

- ・まとめ

## 研究背景

## 絶縁ゲートバイポーラトランジスタ Insulated Gate Bipolar Transistor(IGBT)

- ・高耐圧・大電流に適したパワー半導体

- ・絶縁ゲートによる電圧制御型

- •~数千[V]ほどの高耐圧素子

IGBTの簡易構造図

IGBTの使用用途:

車載用高耐圧素子や鉄道車両制御など

高信頼性が求められるアプリケーションに使用されるため、 多くの回路シミュレーションソフトでの事前解析における高精度化は重要

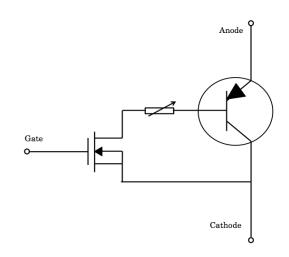

## 研究目的

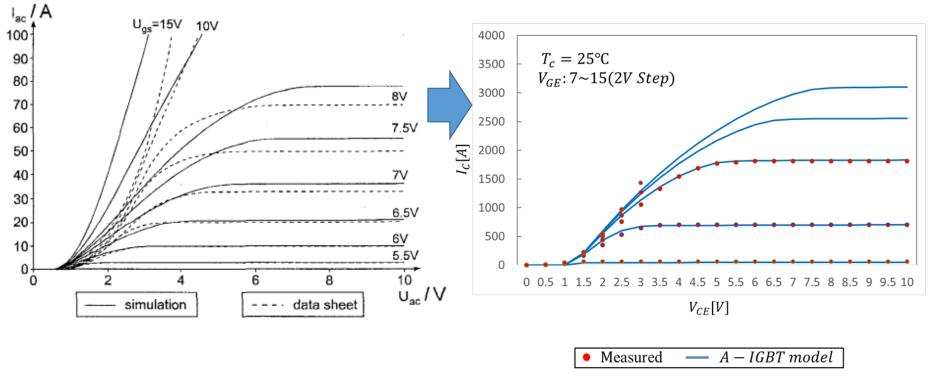

## 従来のマクロモデル

#### 実測の差が大きい

- フリーホイールダイオードのシミュレーション不可

- ・DMOS出力抵抗が一定

- ・小信号AC解析を考慮していない etc...

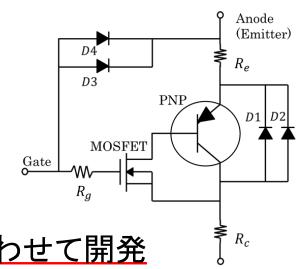

## 提案するマクロモデル

- 静特性,動特性についてより高精度に表現

- ・より高精度なシミュレーションを行える環境 マクロモデルをSPICEの基本エレメントを組み合わせて開発

多くの回路設計ツールのソースコードを改造することなく使用可能

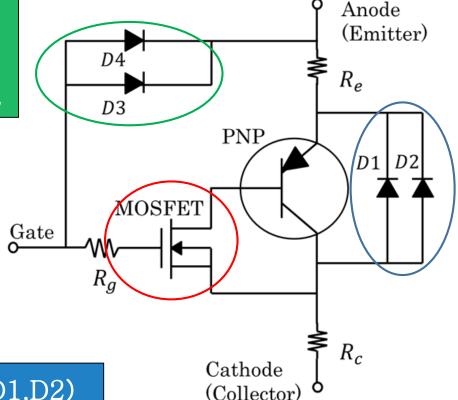

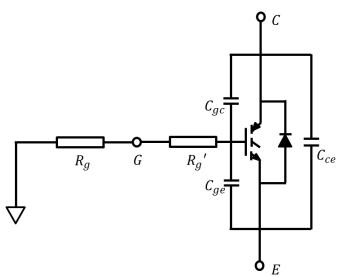

## 提案マクロモデルの新規性

# **並列に2つのダイオードを接続** (D3,D4)

•AC解析やトランジェント解析のための ゲートキャパシタを表現

#### BSIM4モデルに変更

- ・ドリフト電流モデル

- ・出力抵抗モデル を正確に表現

#### 並列に2つのダイオードを接続(D1,D2)

- •n<sup>-</sup>の逆方向Breakdown電圧をコントロール

- ・フリーホイールダイオードの 順方向電流特性のシミュレーションを行う役割

## 使用したDATA SHEET

- 日立製IGBT MBN1200E33E

IGBTのマクロモデルをSPICEに実装

BSIM4モデル

Gummel-Poonモデル

PNダイオードモデル

パラメータを抽出・チューニング

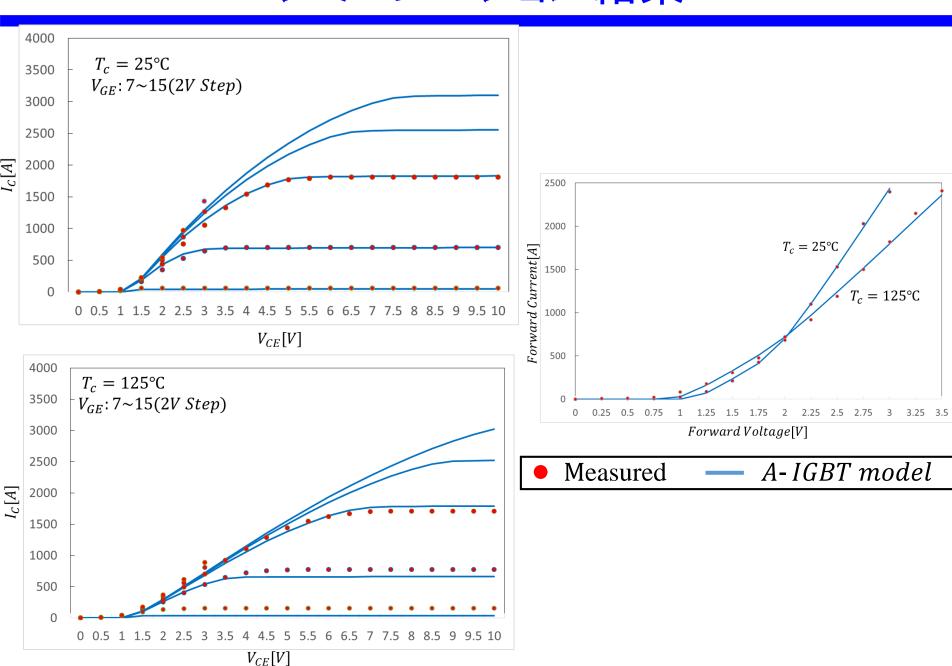

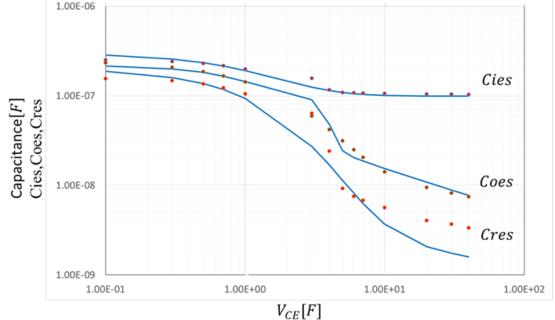

## シミュレーション結果

$$C_{ies} = C_{ge}$$

$C_{res} = C_{gc}$

$C_{oes} = C_{ce} + C_{gc}$

Measured

A - IGBT model

3つの容量のすべてで rmsエラー5%未満

[1] O. Apeldoom, S. Schmitt, and R.W. De Doncker: "An Electrical Model of a NPT-IGBT Including Transient Temperature Effects Realized with PSpice Device Equations Modeling", IEEE Catalog, No. 97TH8280 pp.223-228 (1997)

- SPICEシミュレータ用のIGBTのマクロモデルを提案し、データシートからI-V, C-V,トランジェント特性の測定値として使用して、モデルパラメータを高精度に抽出

- ・4つの接合ダイオードはIGBTのフリーホイールダイオードや接合容量を表現するために使用

- ・シミュレーション結果では移動度および飽和速度の温度効果に関連したモデルパラメータを抽出することで、高温での静特性、動特性を正確に表現できている

- 研究背景

- MOSFETの高信頼性モデル

- LDMOSの高信頼性モデル

- IGBTの高精度マクロモデル

- ・まとめ

- 多くの回路設計者が考慮するしきい値や飽和電流などをより高精度にシミュレーションできる環境を目的に研究

- モデリングにより実用性を考慮したシミュレーションの信頼性における 成果をあげることができた

- ・ 従来のモデルにHCI効果による劣化モデルを組みこむことでより信頼性 の高いシミュレーション環境を開発

- マクロモデルのメリットである基本エレメントの組み合わせによって 多くのシミュレーション環境に適応した高精度のモデルを開発

・北陸先端科学技術大学院大学 金子先生 モデルとモデリングの定義の確認

・東京工業大学 高橋先生 モデリングを行い高速化するイメージがわからない MOSFETの劣化実験の結果が見えていなかった (線が細すぎてわかっていなかったので説明した) 抽出は自分達で行ったのか ・中央大学 築山先生 MOSFETの信頼性モデリングにおいて

$$V_{th_{DEGRADATION}} = C_{HCI} \left( \frac{k_F N_0}{k_R} \right)^{\frac{n_\chi}{1 + n_\chi}} \left( \frac{n_\chi \pi k_H}{12L} D_H \right)^{\frac{1}{1 + n_\chi}} * t^{\frac{1}{1 + n_\chi}}$$

$$V_{th_{DEGRADATION}} = A*B*C*t^{\frac{1}{1+n_{\chi}}}$$

A,B,Cをフィッテングパラメータとし劣化時間をtにいれて ただパラメータを変化させているだけではないとしたほう がいい