S23-1 Analog Circuits III10:15-10:45 AMOct. 28, 2016 (Fri)

2016 IEEE 13<sup>th</sup> International Conference on Solid-State and Integrated Circuit Technology

Oct. 25- Oct.28, 2016

White Horse Lake Jianguo Hotel, Hangzhou, China

# Analog / Mixed-Signal Circuit Design Based on Mathematics

Haruo Kobayashi Haijun Lin

*Gunma University, Japan Xiamen University of Technology, China*

Gunma University Kobayashi Lab

- Statement of This Paper

- Analog Circuit Design based on Mathematics

- ADC/DAC Design based on Mathematics

- TDC Design based on Mathematics

- Conclusion

### • <u>Statement of This Paper</u>

- Analog Circuit Design based on Mathematics

- ADC/DAC Design based on Mathematics

- TDC Design based on Mathematics

- Conclusion

### Our Statement

### Beautiful mathematics

good analog/mixed-signal circuit

#### Besides transistor level design

- Control theory

- Number theory

- Statistics

- Coding theory

- Modulation

- Signal processing algorithm

Enhance analog/mixed-signal circuit performance

### Statement of This Paper

### Analog Circuit Design based on Mathematics

- Control Theory and Operational Amplifier Design

- Complex Signal Processing and Analog Filter

- ADC/DAC Design based on Mathematics

- TDC Design based on Mathematics

- Conclusion

### Statement of This Paper

### Analog Circuit Design based on Mathematics

- Control Theory and Operational Amplifier Design

- Complex Signal Processing and Analog Filter

- ADC/DAC Design based on Mathematics

- TDC Design based on Mathematics

- Conclusion

### Control Theory and Operational Amplifier Design

#### Our proposal

#### For

Analysis and design of operational amplifier stability

#### Use

Routh-Hurwitz stability criterion

- Popular in control theory

- Not in circuit design

We can obtain Explicit stability condition for circuit parameters (which can NOT be obtained only with Bode plot).

[1] J. Wang, H. Kobayashi, et. al., "Analysis and Design of Operational Amplifier Stability Based on Routh-Hurwitz Method", IEEE ICSICT (Oct. 2016).

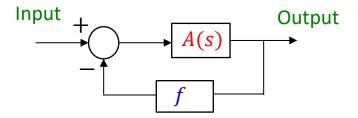

#### **Routh-Hurwitz Stability Criteria**

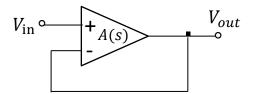

• Transfer function of closed-loop system  $G(s) = \frac{A(s)}{1 + fA(s)} = \frac{N(s)}{D(s)}$

Suppose

$N(s) = b_m s^m + b_{m-1} s^{m-1} + \dots + b_1 s + b_0$  $D(s) = a_n s^n + a_{n-1} s^{n-1} + \dots + a_1 s + a_0$

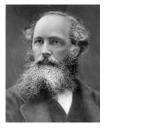

J. Maxwell

A. Stodola

System is stable if and only if Maxwell and Stodola found out !!

real parts of all the roots s<sub>p</sub> of the following are negative:

Characteristic equation  $D(s) = a_n s^n + a_{n-1} s^{n-1} + \dots + a_1 s + a_0 = 0$

To satisfy this, what are the conditions for  $a_n, a_{n-1}, \dots a_1, a_0$ ?

Routh and Hurwitz solved this problem independently !!

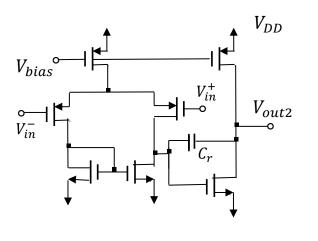

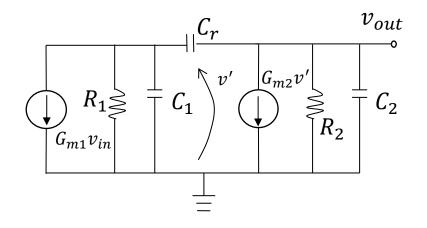

#### Amplifier Circuit and Small Signal Model

Open-loop transfer function from small signal model

$$A(s) = \frac{v_{out}(s)}{v_{in}(s)} = A_0 \frac{1 + b_1 s}{1 + a_1 s + a_2 s^2}$$

$$b_1 = -\frac{C_r}{G_{m2}}$$

$$A_{0} = G_{m1}G_{m2}R_{1}R_{2}$$

$$a_{2} = R_{1}R_{2}C_{2}\left[C_{1} + \left(1 + \frac{C_{1}}{C_{2}}\right)C_{r}\right]$$

$$a_{1} = R_{1}C_{1} + R_{2}C_{2} + (R_{1} + R_{2} + R_{1}G_{m2}R_{2})C_{r}$$

Amplifier circuit

Small signal model

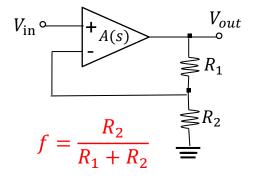

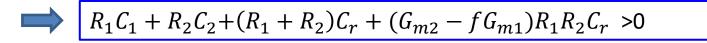

#### **Explicit Condition for Feedback Stability**

Closed-loop transfer function:

$$\frac{V_{out}(s)}{V_{in}(s)} = \frac{A(s)}{1 + fA(s)} = \frac{A_0(1 + b_1 s)}{1 + fA_0 + (a_1 + fA_0 b_1)s + a_2 s^2}$$

Necessary and sufficient stability condition based on R-H criterion

$\implies a_1 + f A_0 b_1 > 0$

Explicit stability condition for parameters

### Statement of This Paper

### Analog Circuit Design based on Mathematics

- Control Theory and Operational Amplifier Design

- Complex Signal Processing and Analog Filter

- ADC/DAC Design based on Mathematics

- TDC Design based on Mathematics

- Conclusion

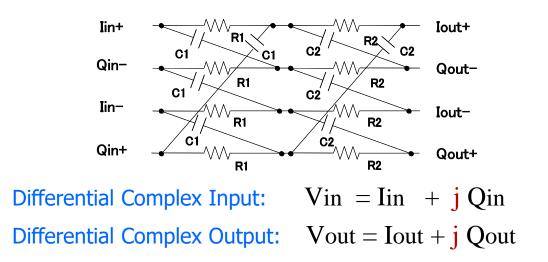

# **RC Polyphase Filter**

- Its input and output are complex signals.

- Passive RC analog filter

- One of key components in wireless transceiver analog front-end

- I, Q signal generation

- Image rejection

[1] Y. Niki, S. Sasaki, H. Kobayashi, "Flat Passband Gain Design Algorithm for 2nd-order RC Polyphase Filter," IEEE ASICON (Nov. 2015).

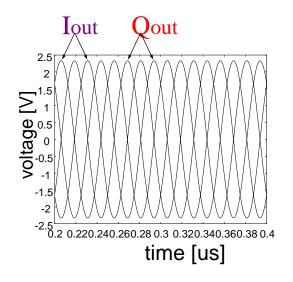

# **Roles of RC Polyphase Filter**

$$Iin = \cos (\omega_{L0} t)$$

$$Polyphase$$

$$Filter$$

$$Qout = A \sin (\omega_{L0} t+\theta)$$

#### Image rejection

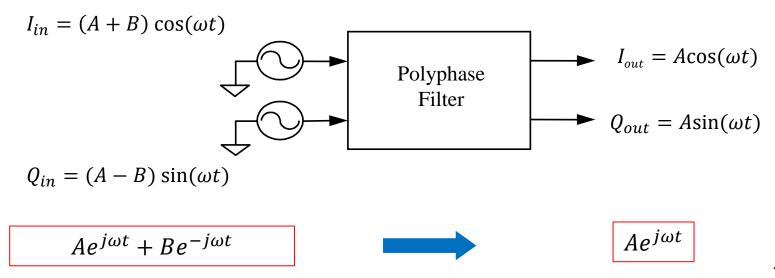

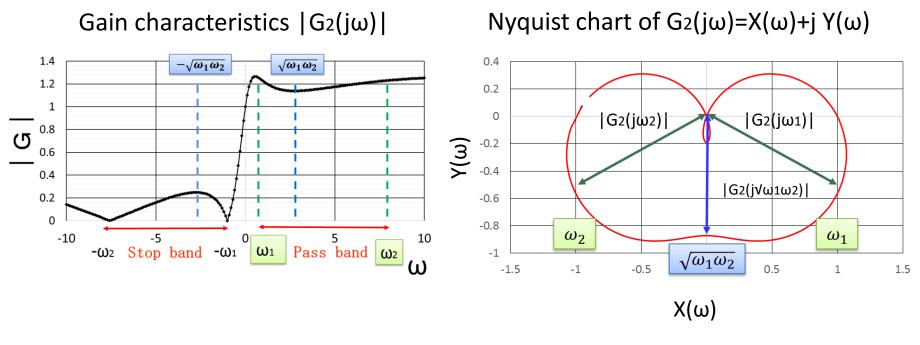

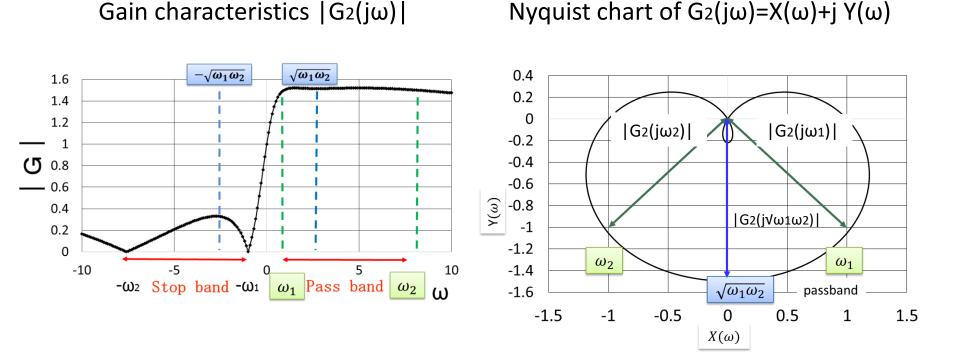

### Nyquist Chart of Complex Transfer Function G2

$|G_2(j\omega_1)| = |G_2(j\omega_2)|$

But in general

$|G_2(j\omega_1)| = |G_2(j\omega_2)| + |G_2(j\sqrt{\omega_1\omega_2})|$

### Our Idea for Flat Passband Gain Algorithm

If we make  $|G_2(j\omega_1)| = |G_2(j\omega_2)| = |G_2(j\sqrt{\omega_1\omega_2})|$ , gain would be flat from  $\omega_1$  to  $\omega_2$ .

- Statement of This Paper

- Analog Circuit Design based on Mathematics

- ADC/DAC Design based on Mathematics

- Fibonacci Sequence and SAR ADC Design

- Adaptive Signal Processing and ADC Calibration

- Magic Square and DAC Design

- TDC Design based on Mathematics

- Conclusion

ADC: Analog-to-Digital Converter DAC: Digital-to-Analog Converter

- Statement of This Paper

- Analog Circuit Design based on Mathematics

- ADC/DAC Design based on Mathematics

- Fibonacci Sequence and SAR ADC Design

- Adaptive Signal Processing and ADC Calibration

- Magic Square and DAC Design

- TDC Design based on Mathematics

- Conclusion

ADC: Analog-to-Digital Converter DAC: Digital-to-Analog Converter

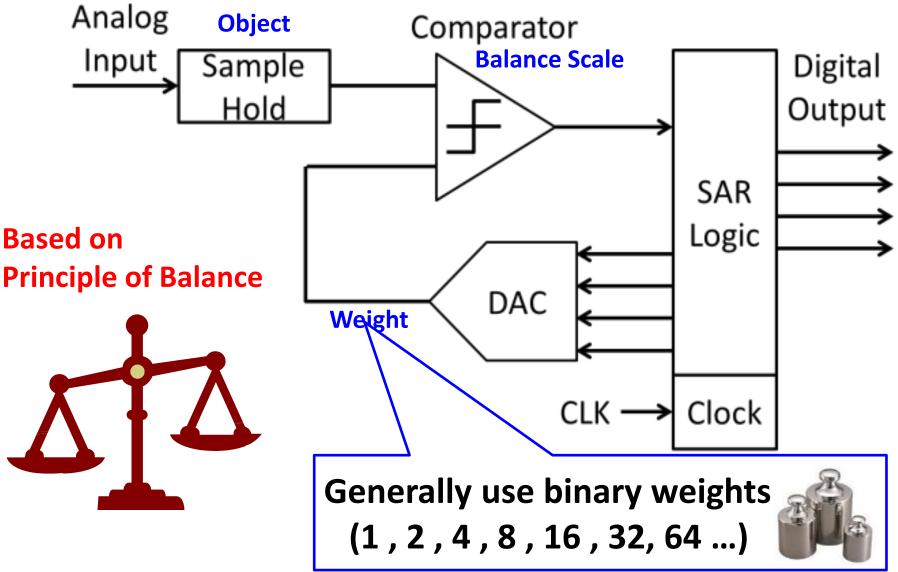

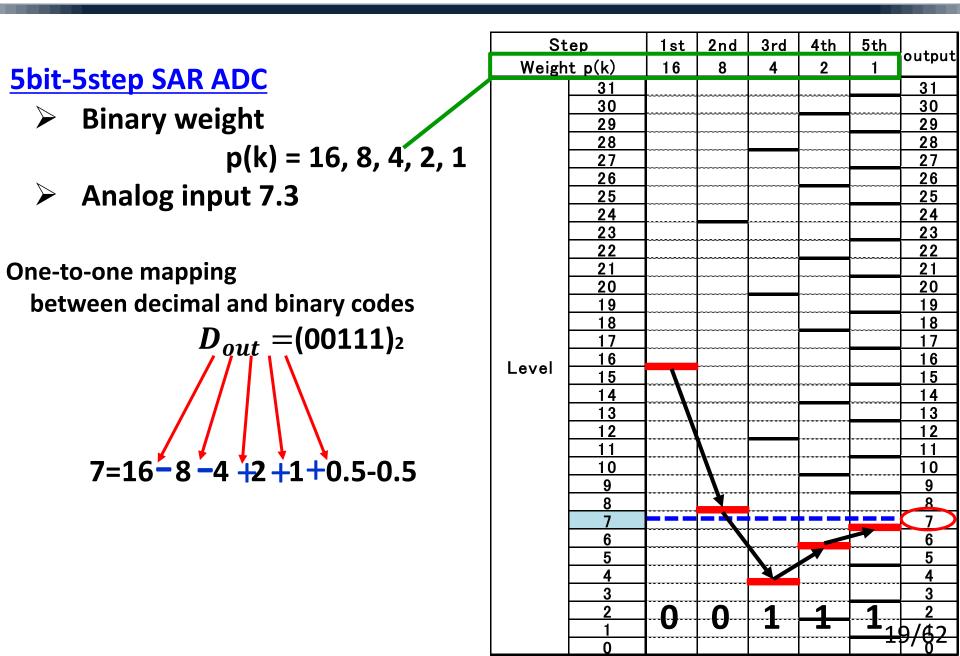

## SAR ADC Configuration

### **Binary Search SAR ADC Operation**

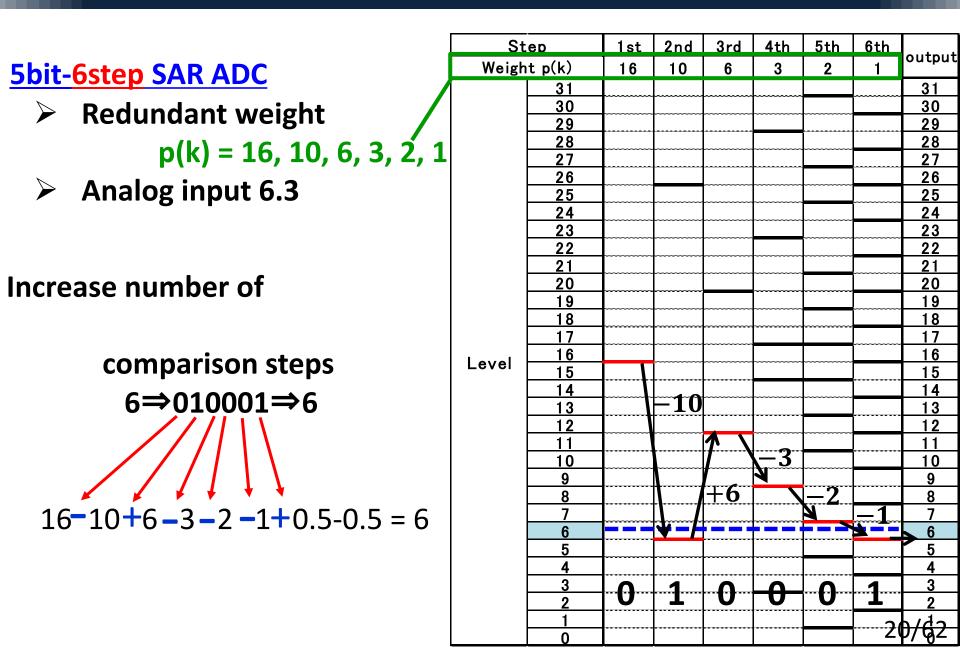

### Redundant Search SAR ADC Operation

# Fibonacci Sequence

### **Definition (n=0,1,2,3...)**

$$F_0 = 0$$

$$F_1 = 1$$

$$F_{n+2} = F_n + F_{n+1}$$

Example of numbers(Fibonacci number)

0, 1, 1, 2, 3, 5, 8, 13, 21, 34, 55, 89...

Leonardo Fibonacci (around 1170-1250)

### Property

The closest terms ratio converges to <u>"Golden Ratio"</u>!

$$\lim_{n \to \infty} \frac{F_n}{F_{n-1}} = 1.618033988749895 = \varphi$$

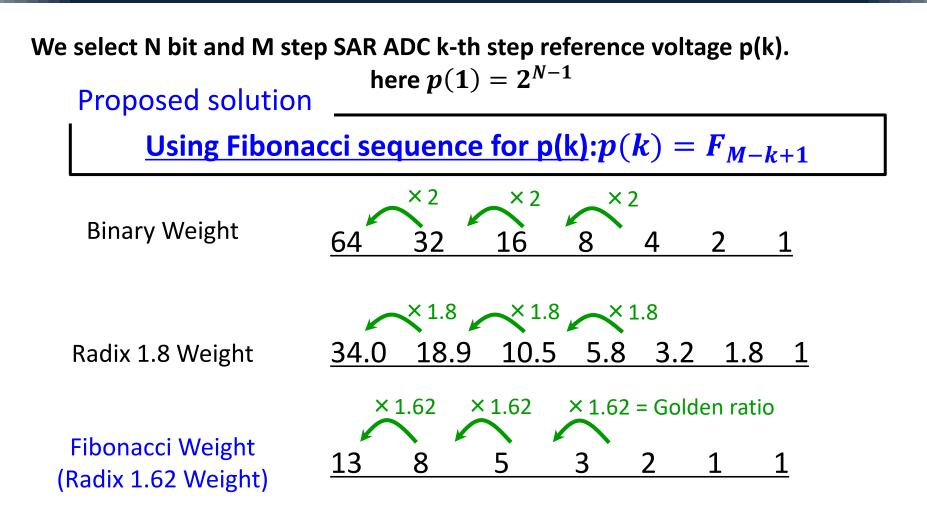

# Fibonacci Weights

Property converging to Golden Ratio

Realize Radix 1.62 Weight by using only integer ! 22

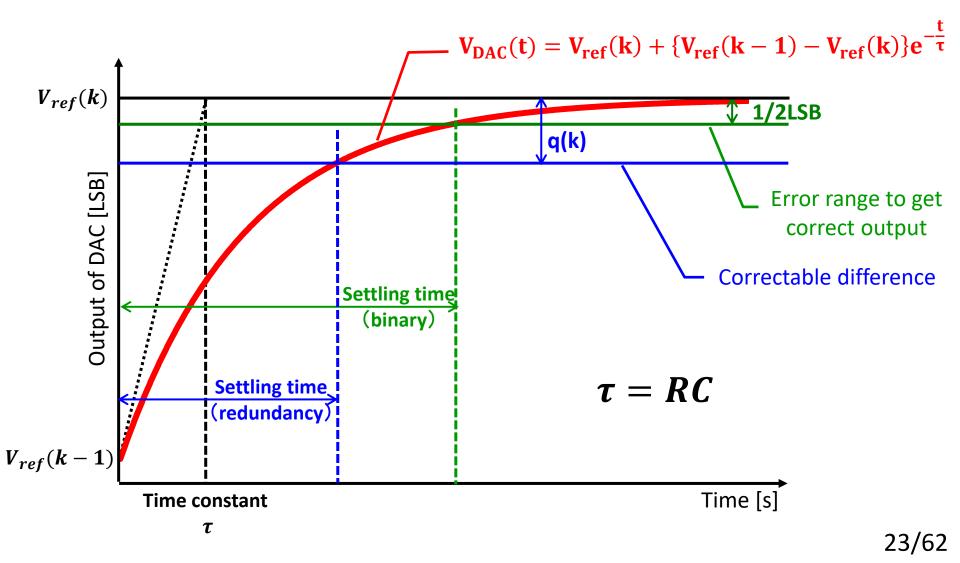

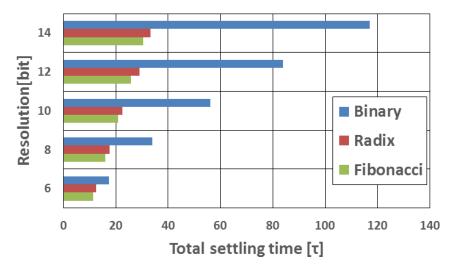

## **Internal DAC Settling Time**

DAC Settling model by a simple first-order RC circuit

# SAR ADC Speed and DAC Settling

Redundancy

**Incomplete settling**

<u>5bit SAR ADC</u>

**Binary search (complete settling)**

| Step1 Step2 Step3 Step4 Ste |

|-----------------------------|

|-----------------------------|

time

The shortest

**AD** conversion

time !!

#### **Redundant search (incomplete settling)**

| Step1 Step2 Step3 Step4 | Step5 Step6 Step7 |

|-------------------------|-------------------|

|-------------------------|-------------------|

**Error correction**

time

#### Fibonacci search (incomplete settling)

**Error correction**

time

# Fibonacci Weights SAR ADC

We have found the following:

#### Reliable

Comparator decision errors can be recovered with redundancy.

#### Fastest SAR AD Conversion

In case the internal DAC incomplete settling is considered.

[1] Y. Kobayashi, H. Kobayashi, et. al.,

"SAR ADC Design Using Golden Ratio Weight Algorithm", ISCIT (Oct. 2015).

[2] T. Arafune, Y. Kobayashi, H. Kobayashi, et. al., "Fibonacci Sequence Weighted SAR ADC Algorithm and its DAC Topology," IEEE ASICON (Nov. 2015).

- Statement of This Paper

- Analog Circuit Design based on Mathematics

- ADC/DAC Design based on Mathematics

- Fibonacci Sequence and SAR ADC Design

- Adaptive Signal Processing and ADC Calibration

- Magic Square and DAC Design

- TDC Design based on Mathematics

- Conclusion

ADC: Analog-to-Digital Converter DAC: Digital-to-Analog Converter

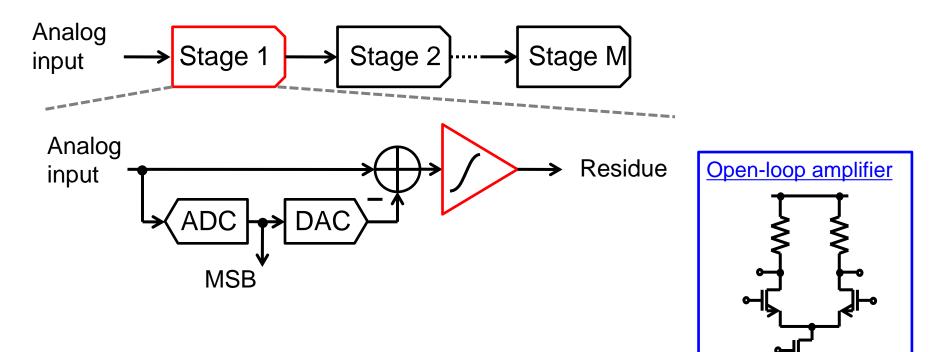

### Power Consumption of Pipelined ADC

•First stage amplifier : Consumes considerable power

- First stage amplifier : Open-loop

- Low power consumption

•Nonlinearity of open-loop amplifier : background self-calibration

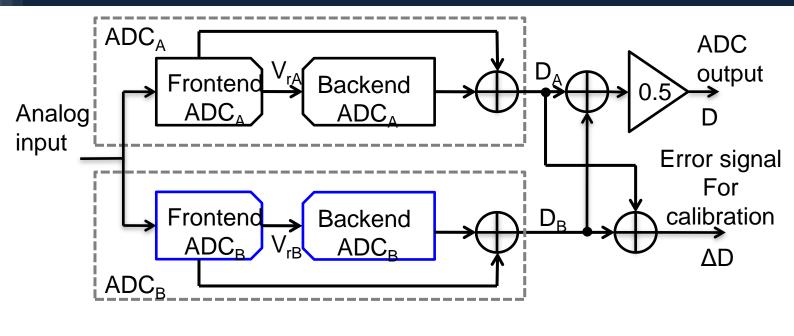

### Split ADC Structure

Each channel ADC: half gm, half capacitor different residue logic converge quickly

Power consumption : small overhead

Chip area : small overhead

T. Yagi, H. Kobayashi, "Background Calibration Algorithm for Pipelined ADC with Open-Loop Residue Amplifier Using Split ADC Structure," IEEE APCCAS, (Dec. 2010).

Haijun Lin, "Split-Based 200Msps and 12 bit ADC Design", IEEE ASICON (Nov. 2015).

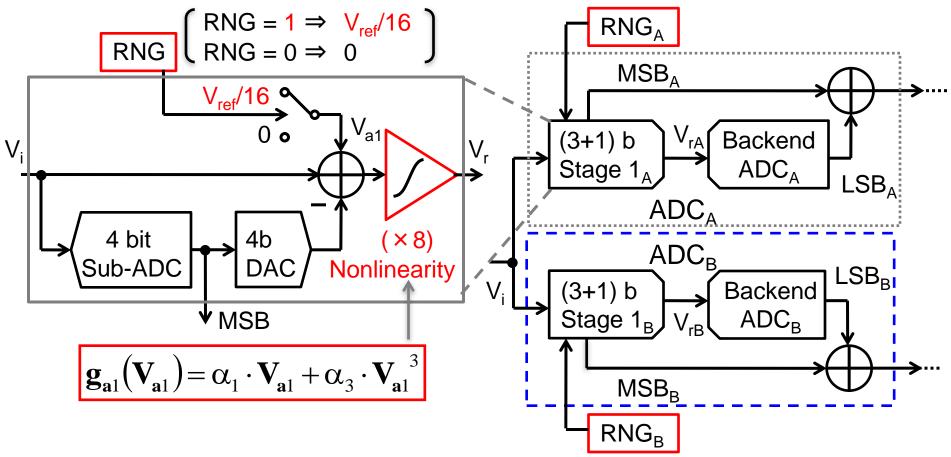

#### **Complicated Adaptive Signal Processing for Calibration**

Adding pseudo randomly

**RNG:Random Numbar Generator**

→ Generate two residue waveforms

•RNG(A & B) : Set default value to different

29/62

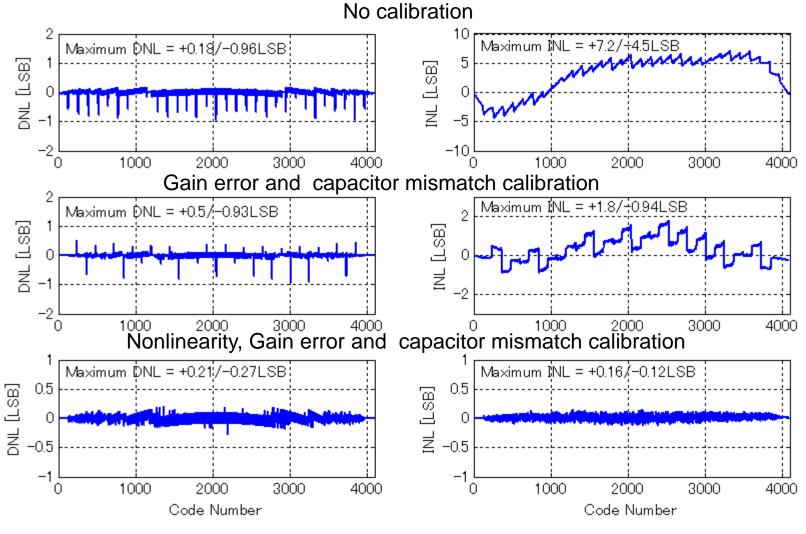

### Validate the Effectiveness with MATLAB

C mismatch : 2% (σ)

Nonlinearity of amplifier :

$$\mathbf{g}_{a1}(\mathbf{V}_{a1}) = 7.5 \cdot \mathbf{V}_{a1} + (-15) \cdot \mathbf{V}_{a1}^{3}$$

- Nonlinearity correction

- ✓ LMS loop :  $\mu_A = 1/8192$

- ✓ IIR filter gain :

$$J_{3a} = 1/512$$

- •Gain error, C mismatch correction

- ✓ IIR filter gain:

$\mu_{1a} = 1/1024$

### <u>ADC<sub>B</sub> (Stage1<sub>B</sub>)</u>

C mismatch : 2% (σ)

Nonlinearity of amplifier :

$$\mathbf{g}_{b1}(\mathbf{V}_{b1}) = 7.6 \cdot \mathbf{V}_{b1} + (-15.2) \cdot \mathbf{V}_{b1}$$

- •Nonlinearity correction

- ✓ LMS loop :

✓ IIR filter gain:

$$\mu_{3b} = 1/512$$

- •Gain error, C mismatch correction

- ✓ IIR filter gain :  $\mu_{1b} = 1/1024$

# DNL and INL of the ADC output

•Calibrate all error : DNL, INL are within  $\pm 0.5$ LSB

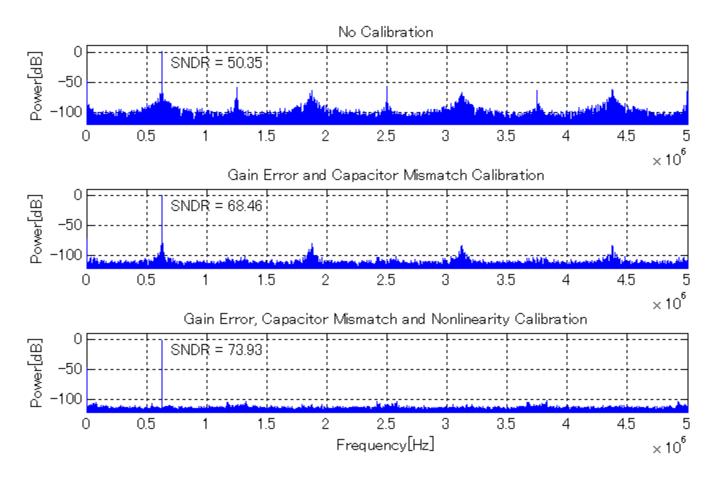

# **Output Power Spectrum**

Calibrate all error : SNDR=73.9dB

- Statement of This Paper

- Analog Circuit Design based on Mathematics

- ADC/DAC Design based on Mathematics

- Fibonacci Sequence and SAR ADC Design

- Adaptive Signal Processing and ADC Calibration

- Magic Square and DAC Design

- TDC Design based on Mathematics

- Conclusion

ADC: Analog-to-Digital Converter DAC: Digital-to-Analog Converter

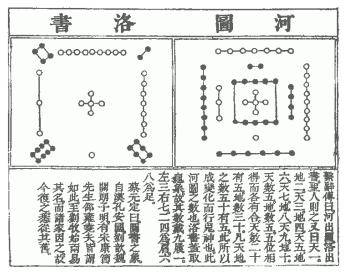

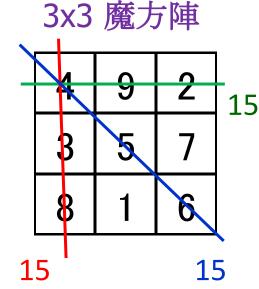

### What is Magic Square (魔方陣)?

- Classical mathematics

- Origin from Chinese academia

- "Constant sum" characteristics

- Varieties of magic squares

| 59 | 5  | 4  | 62 | 63 | 1  | 8  | 58 |

|----|----|----|----|----|----|----|----|

| 9  | 18 | 17 | 49 | 50 | 42 | 19 | 56 |

| 55 | 20 | 28 | 33 | 29 | 40 | 45 | 10 |

| 54 | 44 | 38 | 31 | 35 | 26 | 21 | 11 |

| 12 | 43 | 39 | 30 | 34 | 27 | 22 | 53 |

| 13 | 24 | 25 | 36 | 32 | 37 | 41 | 52 |

| 51 | 46 | 48 | 16 | 15 | 23 | 47 | 14 |

| 7  | 60 | 61 | 3  | 2  | 64 | 57 | 6  |

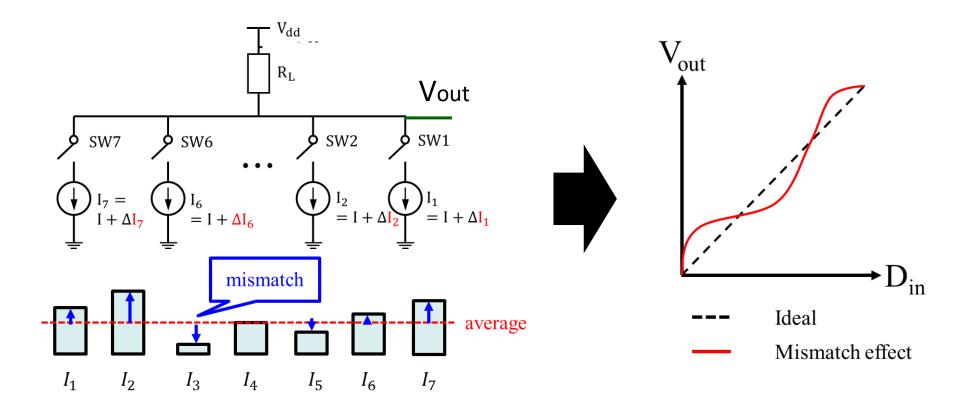

# Unary DAC and Mismatch Problem

In practice, current sources have mismatches. DAC becomes non-linear.

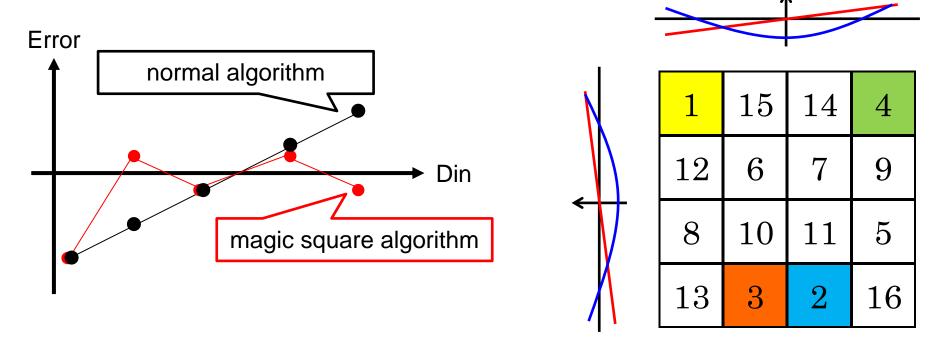

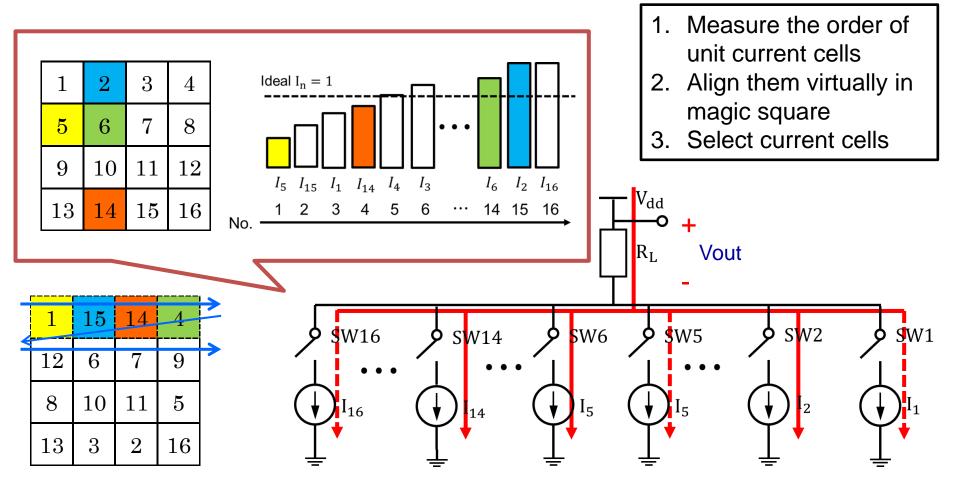

### Possibility of Using Magic Square (魔方陣)

- Semiconductor devices have random and systematic mismatches

- Changing the switching order with magic square

Cancellation of mismatch effects

[1] M. Higashino, H. Kobayashi, "DAC Linearity Improvement Algorithm With Unit Cell Sorting Based on Magic Square", IEEE VLSI-DAT (April 2016).

### Inspired New Algorithm

• Unit current source selection-order change algorithm

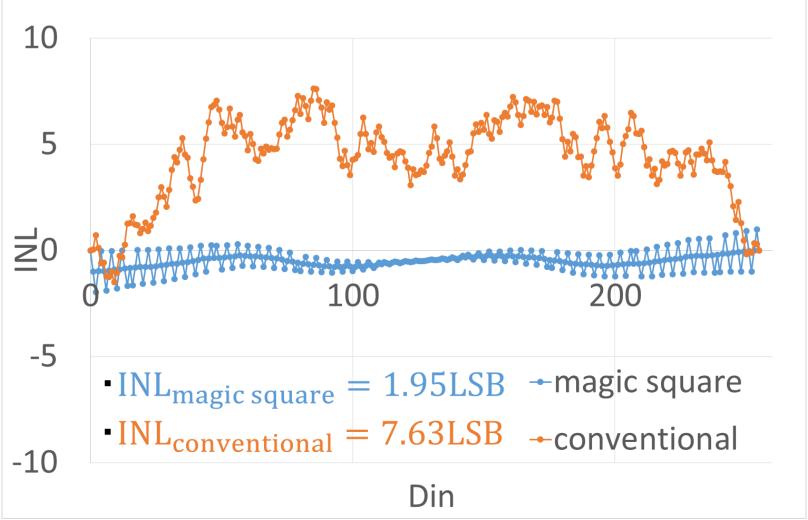

# **MATLAB Simulation Result**

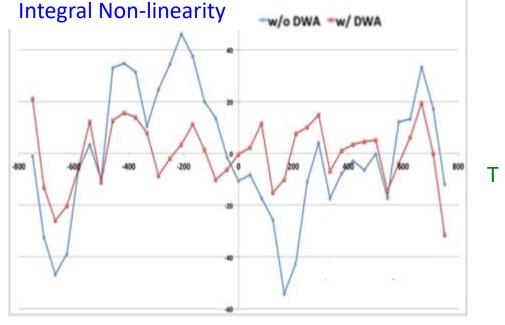

#### Integral Non-Linearity (INL)

• 5.7 LSB improvement by the magic square algorithm

- Statement of This Paper

- Analog Circuit Design based on Mathematics

- ADC/DAC Design based on Mathematics

- TDC Design based on Mathematics

- Histogram and TDC Linearity Calibration

- Gray Code and TDC Design

- $\Delta\Sigma$  Modulation and TDC

Conclusion

#### **TDC:** Time-to-Digital Converter

- Statement of This Paper

- Analog Circuit Design based on Mathematics

- ADC/DAC Design based on Mathematics

- TDC Design based on Mathematics

- Histogram and TDC Linearity Calibration

- Gray Code and TDC Design

- $\Delta\Sigma$  Modulation and TDC

Conclusion

#### **TDC:** Time-to-Digital Converter

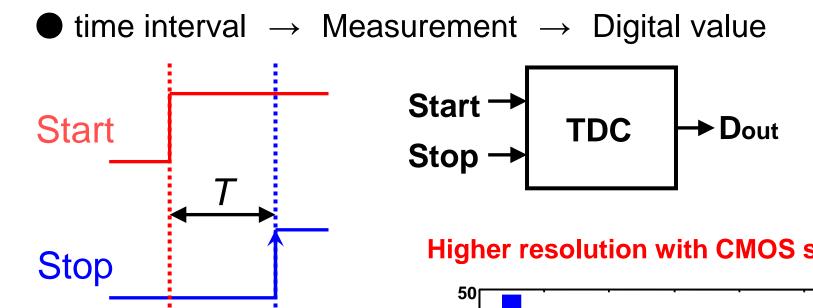

# Time to Digital Converter (TDC)

Key component of time-domain analog circuit Higher resolution can be obtained with scaled CMOS

#### **Higher resolution with CMOS scaling**

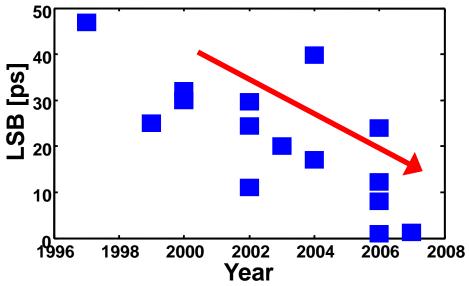

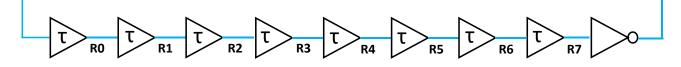

# Flash-type TDC

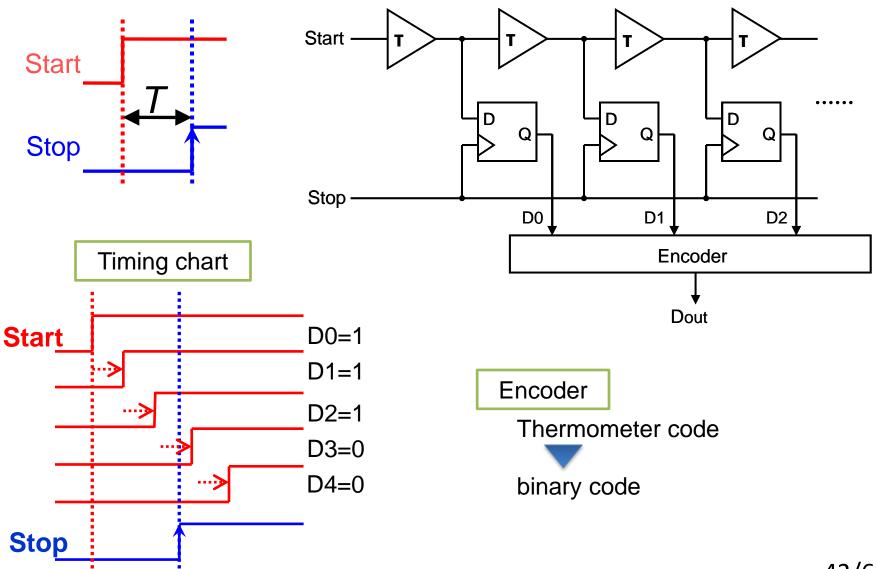

#### **Delay Cell Variation Inside TDC Circuit**

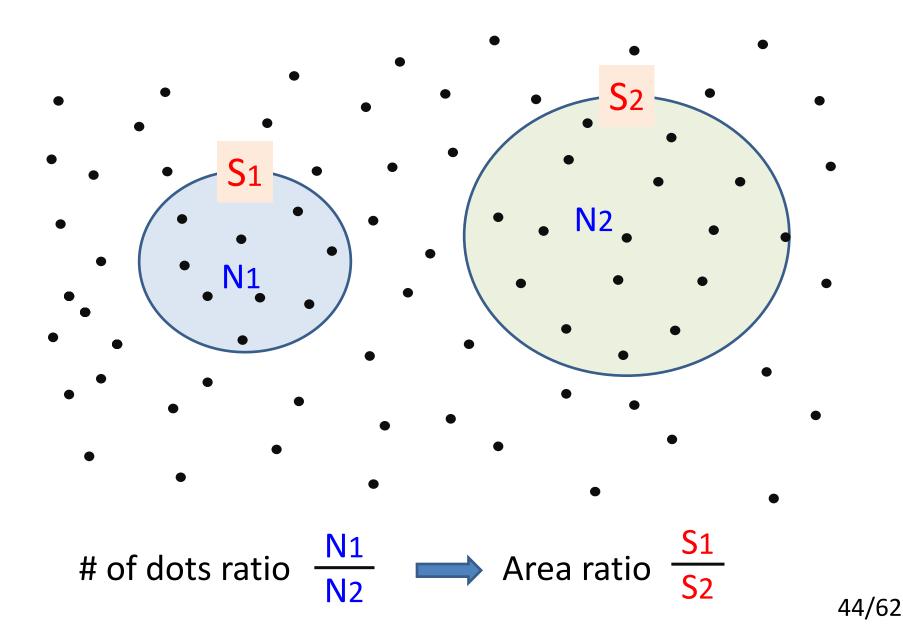

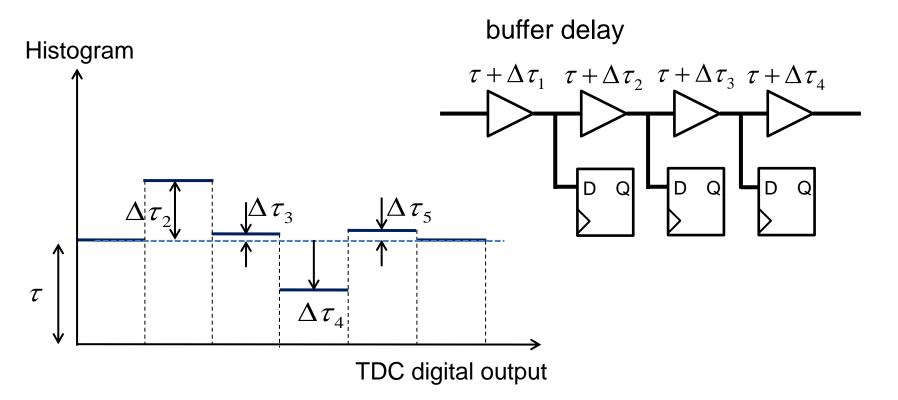

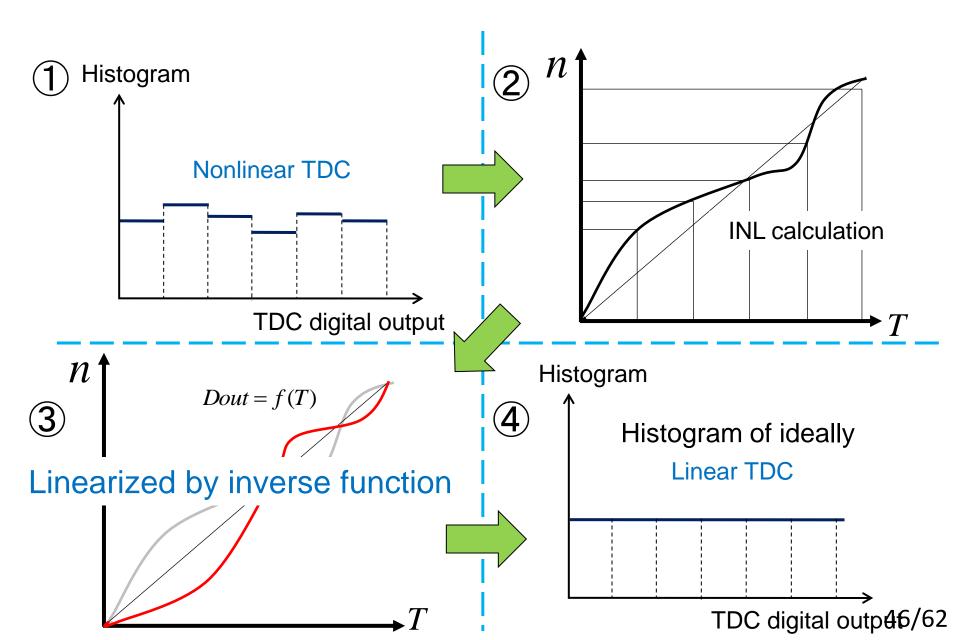

### Measurement with Histogram

#### **Delay Variation Measurement with Histogram**

TDC is non-linear due to delay variation

[1] S. Ito, H. Kobayashi, "Stochastic TDC Architecture with Self-Calibration," IEEE APCCAS (Dec. 2010).

[2] T. Chujo, H. Kobayashi, "Experimental Verification of Timing Measurement Circuit With Self-Calibration", IEEE IMS3TW (Sept. 2014).

45/62

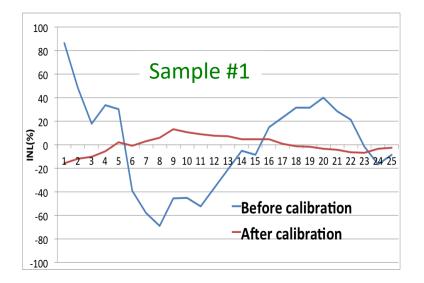

#### **Principle of Self-Calibration**

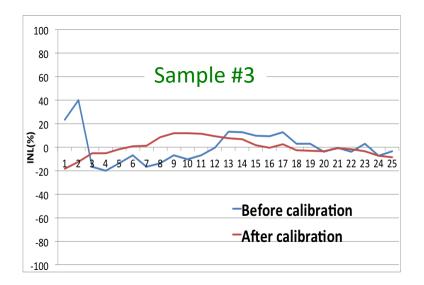

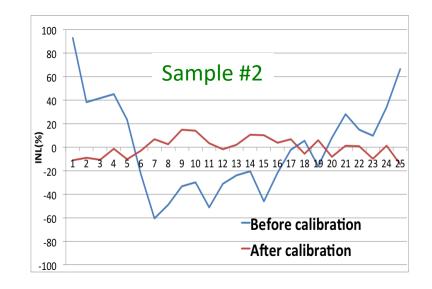

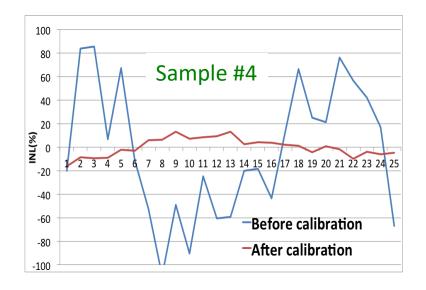

### Measurement Results (INL)

- Statement of This Paper

- Analog Circuit Design based on Mathematics

- ADC/DAC Design based on Mathematics

- TDC Design based on Mathematics

- Histogram and TDC Linearity Calibration

- Gray Code and TDC Design

- $\Delta\Sigma$  Modulation and TDC

Conclusion

**TDC:** Time-to-Digital Converter

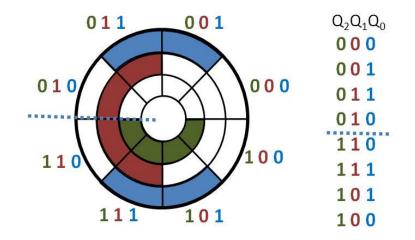

### Concept of Gray code

# Gray code is a binary numeral system where two successive values differ in only one bit.

4-bit Gray code vs. 4-bit Natural Binary Code

| Decimal<br>numbers | Natural Binary<br>Code | 4-bit Gray<br>Code |

|--------------------|------------------------|--------------------|

| 0                  | 0000                   | 0000               |

| 1                  | 0001                   | 0001               |

| 2                  | 0010                   | 0011               |

| 3                  | 0011                   | 0010               |

| 4                  | 0100                   | 0110               |

| 5                  | 0101                   | 0111               |

| 6                  | 0110                   | 0101               |

| 7                  | 0111                   | 0100               |

| 8                  | 1000                   | <b>1</b> 100       |

| 9                  | 1001                   | 1101               |

| 10                 | 1010                   | 1111               |

| 11                 | 1011                   | 1110               |

| 12                 | 1100                   | 1010               |

| 13                 | 1101                   | 1011               |

| 14                 | 1110                   | 1001               |

| 15                 | 1111                   | 1000               |

FRANK GRAY and A. L. Johnsrud in television booth. Behind the glass panels at sides and top are the photo-electric cells.

Gray code was invented by Frank Gray at Bell Lab in 1947. 49/62

#### How to utilize Gray code in TDC

In a ring oscillator, between any two adjacent states, only one output changes at a time.

| 8-stage Ring Oscillator Output |    |    |    |    | 4-bit Gray Code |    |           |    |    |    |    |

|--------------------------------|----|----|----|----|-----------------|----|-----------|----|----|----|----|

| RO                             | R1 | R2 | R3 | R4 | R5              | R6 | <b>R7</b> | G3 | G2 | G1 | G0 |

| 0                              | 0  | 0  | 0  | 0  | 0               | 0  | 0         | 0  | 0  | 0  | 0  |

| 1                              | 0  | 0  | 0  | 0  | 0               | 0  | 0         | 0  | 0  | 0  | 1  |

| 1                              | 1  | 0  | 0  | 0  | 0               | 0  | 0         | 0  | 0  | 1  | 1  |

| 1                              | 1  | 1  | 0  | 0  | 0               | 0  | 0         | 0  | 0  | 1  | 0  |

| 1                              | 1  | 1  | 1  | 0  | 0               | 0  | 0         | 0  | 1  | 1  | 0  |

| 1                              | 1  | 1  | 1  | 1  | 0               | 0  | 0         | 0  | 1  | 1  | 1  |

| 1                              | 1  | 1  | 1  | 1  | 1               | 0  | 0         | 0  | 1  | 0  | 1  |

| 1                              | 1  | 1  | 1  | 1  | 1               | 1  | 0         | 0  | 1  | 0  | 0  |

| 1                              | 1  | 1  | 1  | 1  | 1               | 1  | 1         | 1  | 1  | 0  | 0  |

| 0                              | 1  | 1  | 1  | 1  | 1               | 1  | 1         | 1  | 1  | 0  | 1  |

| 0                              | 0  | 1  | 1  | 1  | 1               | 1  | 1         | 1  | 1  | 1  | 1  |

| 0                              | 0  | 0  | 1  | 1  | 1               | 1  | 1         | 1  | 1  | 1  | 0  |

| 0                              | 0  | 0  | 0  | 1  | 1               | 1  | 1         | 1  | 0  | 1  | 0  |

| 0                              | 0  | 0  | 0  | 0  | 1               | 1  | 1         | 1  | 0  | 1  | 1  |

| 0                              | 0  | 0  | 0  | 0  | 0               | 1  | 1         | 1  | 0  | 0  | 1  |

| 0                              | 0  | 0  | 0  | 0  | 0               | 0  | 1         | 1  | 0  | 0  | 0  |

For any given Gray code, each bit can be generated by a certain ring oscillator.

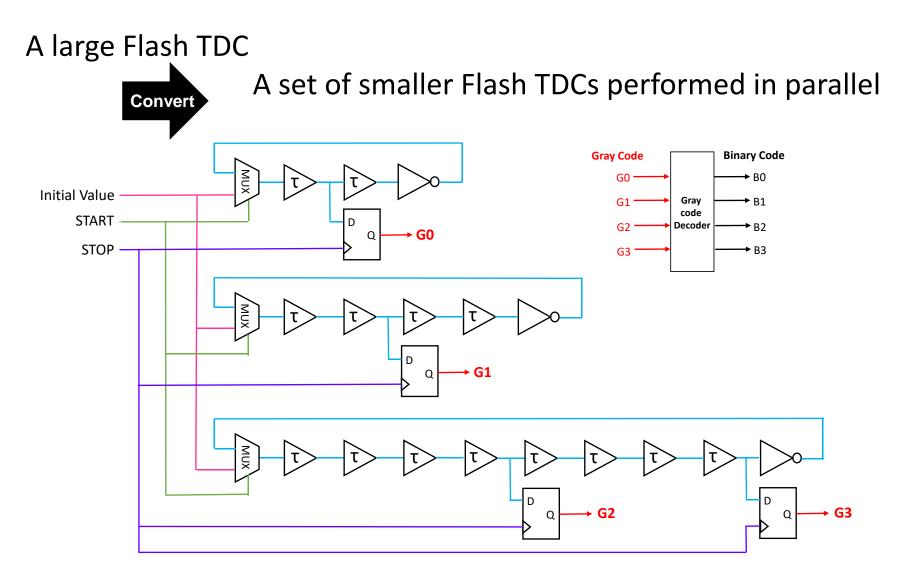

#### Proposed 4-bit Gray code TDC

Proposed Gray code TDC architecture in 4-bit case

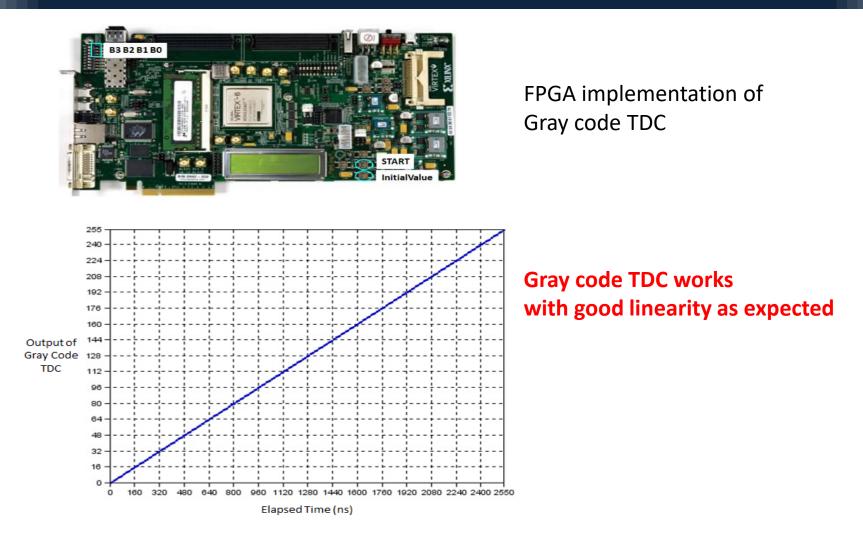

#### FPGA measurement results of 8-bit Gray code TDC

[1] C. Li, H. Kobayashi, "A Gray Code Based Time-to-Digital Converter Architecture and its FPGA Implementation", IEEE International Symposium on Radio-Frequency Integration Technology (RFIT), Sendai, Japan (Aug. 26-28, 2015).

### Flash TDC vs. Gray code TDC

|                | Number of             | Number of             | Maximum stage of        |  |  |

|----------------|-----------------------|-----------------------|-------------------------|--|--|

|                | delay cells           | DFFs                  | RO                      |  |  |

| Gray code TDC  | 2 <sup>n</sup> -2     | п                     | 2 <sup><i>n</i>-1</sup> |  |  |

| Flash-type TDC | 2 <i><sup>n</sup></i> | 2 <i><sup>n</sup></i> | 2 <i><sup>n</sup></i>   |  |  |

For large measurement range, the number of flip-flops in Gray code TDC decreases rapidly ( $_{n \ll 2^{n}}$ )

#### **Reduction of circuit complexity!!**

- Statement of This Paper

- Analog Circuit Design based on Mathematics

- ADC/DAC Design based on Mathematics

- TDC Design based on Mathematics

- Histogram and TDC Linearity Calibration

- Gray Code and TDC Design

- $\Delta\Sigma$  Modulation and TDC

Conclusion

**TDC:** Time-to-Digital Converter

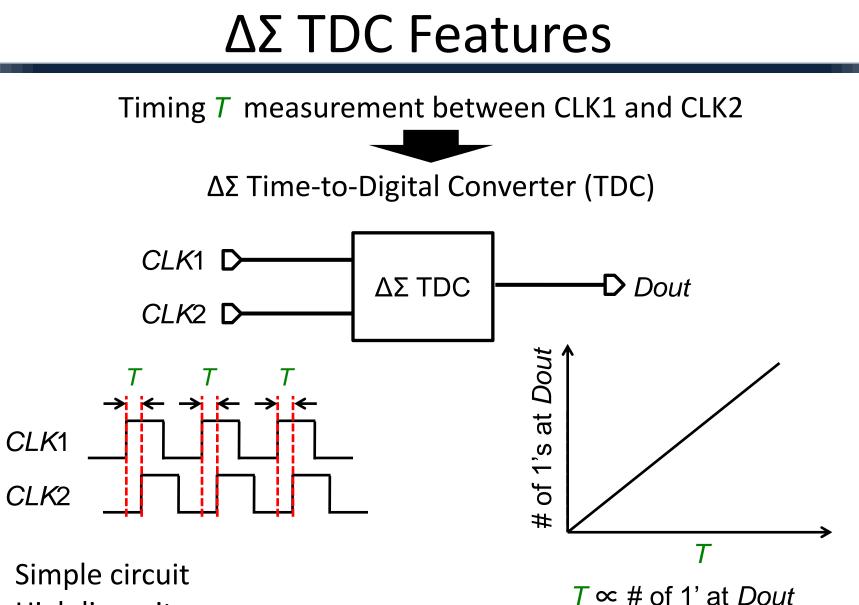

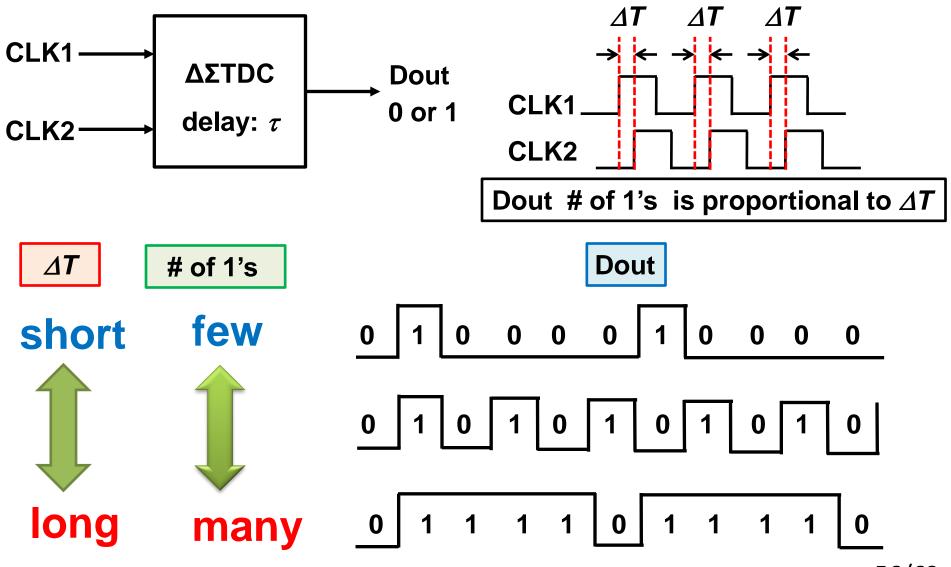

- **High linearity**

- Measurement time  $\rightarrow$  longer  $\Rightarrow$  time resolution  $\rightarrow$  finer •

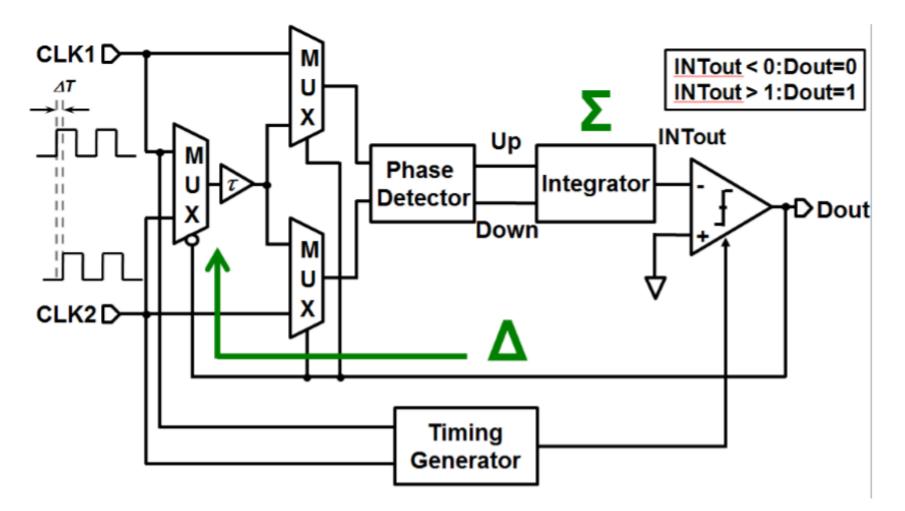

## Principle of $\Delta\Sigma TDC$

# **ΔΣTDC Configuration**

[1] T. Chujo, H. Kobayashi, "Timing Measurement BOST With Multi-bit Delta-Sigma TDC", IEEE IMSTW (June 2015).

[2] Y. Osawa, H. Kobayashi, "Phase Noise Measurement Techniques Using Delta-Sigma TDC", IEEE IMS3TW (Sept. 2014).

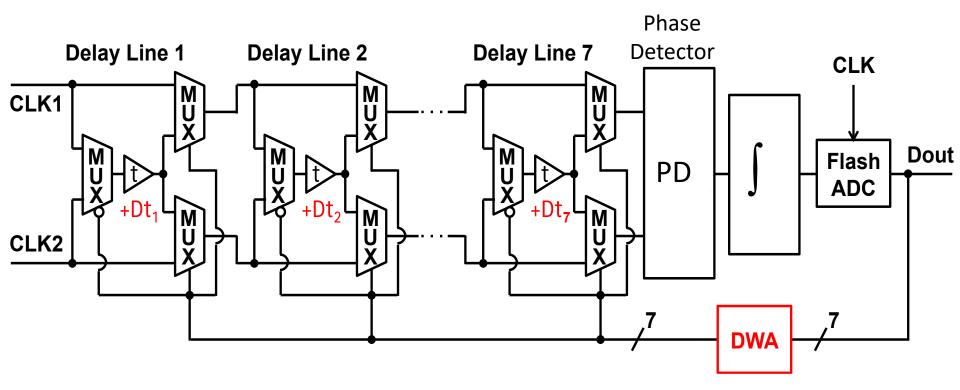

# Multi-bit ΔΣΤDC

#### For short measurement time:

**DWA:** Data Weighted Averaging

DSP algorithm of compensation for mismatches among delays.

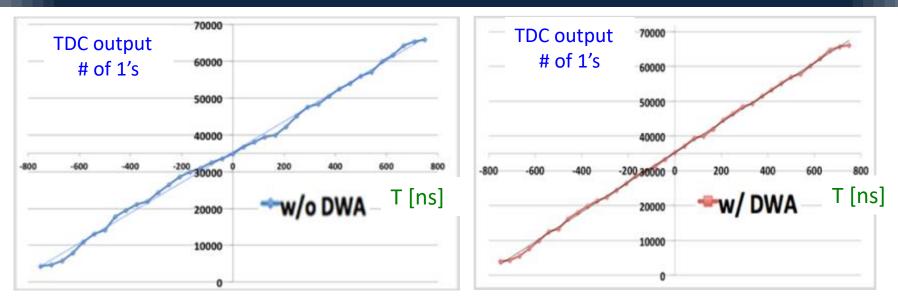

# Measured Result

#### Analog FPGA Implementation

10,000 TDC output data are measured.

T [ns]

#### Statement of This Paper

- Analog Circuit Design based on Mathematics

- ADC/DAC Design based on Mathematics

- TDC Design based on Mathematics

#### • <u>Conclusion</u>

#### Conclusion

- Traditionally, people believe that analog / mixed-signal circuit design is art and craft.

- Here we show that mathematics can contribute to the design as science.

Both art and science are used for good analog / mixed-signal circuit design

# 思而不学则殆

Analog / mixed-signal IC designers should study mathematics for sophisticated design.

Kobayashi aboratorv