# 高信頼性・低特性オン抵抗 100V デュアル RESURF LDMOS トランジスタ

松田 順一\* 小島 潤也 築地 伸和 神山 雅貴 小林 春夫(群馬大学)

High Reliability 100V Dual RESURF LDMOS Transistor with Low Specific On-Resistance Jun-ichi Matsuda\*, Jun-ya Kojima, Nobukazu Tsukiji, Masataka Kamiyama, Haruo Kobayashi (Gunma University)

This paper proposes a high reliability dual RESURF LDMOS transistor with low specific on-resistance for 100V automotive applications. The proposed LDMOS transistor is designed to suppress drain current expansion due to Kirk effect and impact ionization in the vicinity of the gate-side drift edge, ensuring good hot carrier reliability. Simulation verified that the breakdown location is in the bulk, leading to good ESD performance. A specific on-resistance of 150mΩmm² at a breakdown voltage of 129V, top-notch performance, is also obtained.

キーワード:横方向二重拡散 MOS,信頼性,ホットキャリア,静電破壊,電流増大,カーク効果 (LDMOS, reliability, hot carrier, ESD, current expansion, Kirk effect)

## 1. はじめに

民生品の DC-DC コンバータ、FPD (Flat Panel Display) 用ドライバ等に多用されている LDMOS (Lateral Double Diffused MOS)トランジスタを車載品に展開する場合、一層の高信頼性と広い SOA (Safe Operating Area) が要求される。このためには、ホットキャリア耐性を上げ、ドレイン電圧とゲート電圧が高い時発生する電流増大(Current Expansion: CE) $^{(1)^{\sim}(4)}$ を抑える必要がある。また、LDMOSトランジスタを ESD 素子として兼用する場合、ゲート酸化膜を保護するために基板内部でブレークダウンを発生させ、ESD 耐性を上げる必要がある。これらの要件を満たし、かつ低特性オン抵抗を持つ  $30\sim50$ V 動作のデュアルRESURF LDMOSトランジスタが既に報告  $^{(5)(6)}$ されている。今回、その LDMOS 構造を基に 100V 動作用の LDMOS構造を提案し、その特性をシミュレーションで確認した。

2.で提案型 LDMOS トランジスタ構造を従来型と比較して紹介し、3.でシミュレーション結果を示し、4.でその結果を解析する。そして、5.でまとめる。

# 2. 従来型と提案型 LDMOS トランジスタ

## 〈2·1〉 従来型 LDMOS トランジスタ

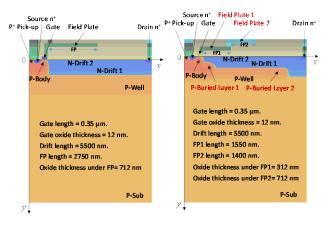

従来型LDMOSトランジスタの断面構造を図1(a)に示す。 ここでは、ドリフト層上に素子分離用の酸化膜のない単純な構造とした。ドリフト層は上層と下層の2層構造となっており、SOAを上げるために上層の濃度を高くしてある(7)。

(a) 従来型 LDMOS

(b) 提案型 LDMOS

図 1 従来型と提案型 LDMOS トランジスタの断面 Fig. 1. Cross-sectional views of the conventional and the proposed LDMOS transistors.

フィールド・プレート (Field Plate: FP) 長は、ドリフト長の半分である。

## 〈2·2〉 提案型 LDMOS トランジスタ

提案型LDMOSトランジスタの断面構造を図1(b)に示す。本構造では、従来型をベースにドリフト層を 2 段階(デュアル)の P-埋め込み層で囲ってある。P-埋め込み層 2 はドリフト層全体の RESURF (Reduced Surface Field)を強め、P-埋め込み層 1 はゲート近傍のドリフト層内のRESURFを一層強化している。FP は 2 段階になっており、

FP1 がゲート近傍の RESURF を強めている。これらの RESURF により、ドリフト層の上層部分のドーズ量を従来 型より増加してあり、SOA の強化と低オン抵抗化を図って いる。

## 〈2·3〉 プロセスとシミュレーション

0.35μm CMOS プロセスをベースに、デバイス・シミュレータを用いて不純物プロファイルを関数入力し、従来型と提案型 LDMOS 構造を形成した。図 1 内に各 LDMOS 構造のサイズを記載してある。LDMOS の幅は、0.2μm である。用いたデバイス・シミュレータはアドバンスソフト社の Advance/DESSERT(®) (サンプル版) である。このシミュレータは 3 次元のシミュレーション機能を有するが、2 次元で行なった。

## 3. シミュレーション結果

## 〈3·1〉 電気的基本特性

しきい値電圧  $V_T$  (at  $V_{DS}$ =0.1V,  $I_{DS}$ =10.8A) は、2.18V (従来型)、2.63V (提案型) であった。また、 $V_{DS}$ =80V での  $V_T$ は、2.07V (従来型)、2.57V (提案型) であった。したがって、 $V_{DS}$ が 0.1V から 80V まで変化すると、 $V_T$ は従来型で 0.11V、また提案型で 0.06V ほどそれぞれ低下する

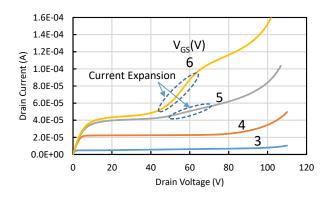

(a) 従来型 LDMOS

(b) 提案型 LDMOS

図2 従来型と提案型 LDMOS トランジスタの I<sub>DS</sub>-V<sub>DS</sub> 特性 Fig. 2. I<sub>DS</sub>-V<sub>DS</sub> characteristics of the conventional and the proposed LDMOS transistors.

が、いずれもその量は小さく、両型とも DIBL(Drain Induced Barrier Lowering)起因のしきい値電圧低下が十分に抑制されている。

特性オン抵抗  $R_{on}A$  (at Vas=5V) は、178m  $\Omega$  mm<sup>2</sup>(従来型)、150m  $\Omega$  mm<sup>2</sup>(提案型)であり、提案型で低くなっている。

#### 〈3·2〉 IDS-VDS特性

図 2(a)に従来型、また(b)に提案型 LDMOS トランジスタの  $I_{DS}$ - $V_{DS}$  特性を示す。従来型で、 $V_{CS}$ =5V では  $V_{DS}$ =40V 辺りから CE が弱く出ているが、 $V_{CS}$ =6V ではそれが顕著になっている。提案型で、 $V_{CS}$ =5V では  $V_{DS}$ =80V 辺りから、電流が増大しているが、CE は発生していない。 $V_{CS}$ =6V では  $V_{DS}$ =60V 辺りから弱い CE が発生している。つまり、提案型では、動作電圧範囲  $V_{CS}$ =0~5V と  $V_{DS}$ =0~100V で CE を発生させない動作が可能である。

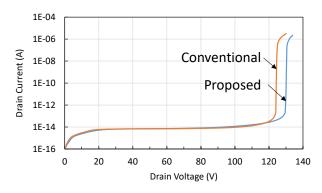

## 〈3·3〉 ブレークダウン時の電流電圧特性

図 3に従来型と提案型 LDMOS トランジスタのブレーク ダウン時の電流電圧特性を示す。ブレークダウン電圧  $BV_{DS}$  (at  $I_{DS}$ = $1\times10^{-13}$ A) は、124V(従来型)、129V(提案型)であり、提案型で高くなっているが、100V 動作の 場合、従来型と提案型のどちらでも問題ないと考える。

## 4. 解析

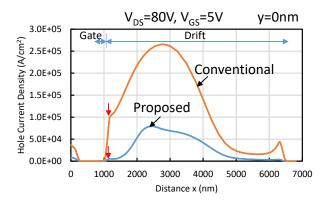

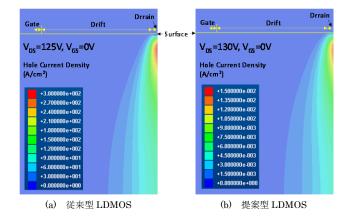

#### 〈4·1〉 正孔電流密度と電界強度

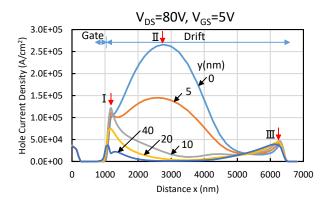

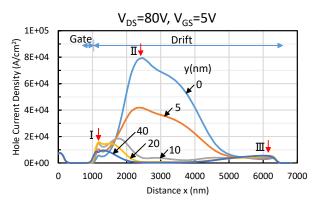

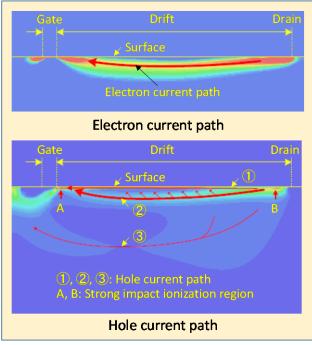

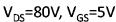

インパクトイオン化によって生じる正孔電流が従来型と提案型 LDMOS トランジスタでどのように異なるかを調べる。図 4 に飽和領域( $V_{DS}$ =80V,  $V_{GS}$ =5V)で動作している従来型と提案型 LDMOS トランジスタにおいて、界面に沿った方向(x 方向)の正孔電流密度プロファイルを示す。提案型の正孔電流密度プロファイルは、全体的に従来型より低くなっている。真性 MOSFET の特性に最も影響を与えるゲート側ドリフト端(真性 MOSFET のドレイン)での提案型の正孔電流密度は、従来型に比べて一桁以上低下してい

図 3 従来型と提案型 LDMOS トランジスタの ブレークダウン時の電流電圧特性

Fig. 3. Breakdown characteristics of the conventional and the proposed LDMOS transistors.

図 4 飽和領域で動作している従来型と提案型 LDMOS トランジスタの界面に沿った正孔電流密度プロファイル

Fig. 4. Hole current density profiles along the surface of the conventional and the proposed LDMOS transistors operating in the saturation region.

図 5 飽和領域で動作している従来型と提案型 LDMOS トランジスタの界面に沿った電界強度プロファイル

Fig. 5. Electric field magnitude profiles along the surface of the conventional and the proposed LDMOS transistors operating in the saturation region.

る。ホットキャリアによる劣化寿命 MTTF(Mean Time To Failure)が、DAHC(Drain Avalanche Hot Carriers)注入の場合、基本的に基板電流(この場合、ゲート側ドリフト端での正孔電流密度)のべき乗( $\sim$ -3乗)に比例する  $^{(9)}$ ことを考慮すると、提案型のホットキャリア耐性は従来型より十分にあるものと考える。

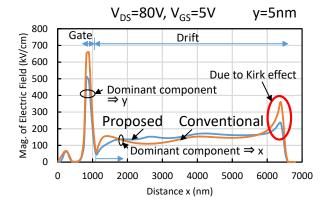

図 5 に図 4 と同じバイアス条件で、従来型と提案型LDMOS トランジスタの界面に沿った電界強度プロファイルを示す。ドレイン側ドリフト端で従来型と提案型は電界強度にピークを持ち、どちらも Kirk 効果 (10)(11)が表れている。しかしながら、提案型のピークは低く、Kirk 効果が抑

(a) 従来型 LDMOS

(b) 提案型 LDMOS

図 6 飽和領域で動作している従来型と提案型 LDMOS トランジスタの各深さ(y)における界面に沿った方向の 正孔電流密度プロファイル

Fig. 6. Hole current density profiles along the surface at y-locations of the conventional and the proposed LDMOS transistors operating in the saturation region.

えられていることが分かる。これは、ドリフト層上層のドーズ量を提案型の方で増やせたことによる。また、ゲート側ドリフト端近傍においても、提案型の電界強度は低くなっている。この電界強度の低下は、提案型で採用した P・埋め込み層 1 と FP1 により RESURF が強く効いたためである。

図 6 に図 4 と同じバイアス条件で従来型と提案型LDMOS トランジスタの各深さ(y)における界面に沿った方向の正孔電流密度プロファイルを示す。図 6(a)の従来型では、x=2700nm 辺りにある大きなピーク(II)は、y の増加とともに急に減少するが、ゲート側ドリフト端にある小さなピーク(I)は、y の増加とともに y=10nm で最大になり、その後減少する。ドレイン側ドリフト端のピーク(II)は、 $y=0\sim20$ nm の範囲でほぼ一定である。一方、図 6(b)の提案型では、x=2500nm 辺りにある大きなピーク(II)は、従来型と同様に y の増加とともに急に減少するが、ゲート

側ドリフト端にある小さなピーク(I)は、yの増加ととも

(a) 従来型 LDMOS

(b) 提案型 LDMOS

図7 飽和領域で動作している従来型と提案型 LDMOS トランジスタの電子と正孔の電流経路

Fig. 7. Electron and hole current paths of the conventional and the proposed LDMOS transistors operating in the saturation region.

に y=10~20nm の範囲で最大になっており、その後低下す る。ドレイン側ドリフト端のピーク (Ⅲ) は、y=0~40nm の範囲でほぼ一定である。この正孔電流密度のプロファイ ルの原因を考察する。正孔は電界加速された電子のインパ クトイオン化により発生する。すなわち、正孔は電子電流 の経路に沿って発生する。 図7に図4と同じバイアス条件 での電子と正孔の電流経路を示す。図7によると、従来型 と提案型の電子電流経路は、 どちらもドリフト両端では表 面にあるが、それ以外では表面から離れてドリフト内部に ある。正孔は、この電子電流経路に沿って発生しており、 正孔電流の主経路②を形成している。また、インパクトイ オン化は、従来型も提案型もともに、図中のAとBの箇所 で強くなっている。Bの箇所での Kirk 効果によるインパク トイオン化が、図 6 のⅢの正孔電流密度プロファイルを形 成している。B の箇所で発生した正孔は、正孔電流経路② の他に、表面①と基板内部③を流れる。②の経路を流れる 成分の一部が、途中で①に加わり、①を増加させる。しか しながら、①の成分はゲート側ドリフト端で広がって基板

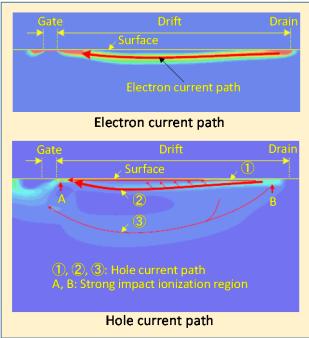

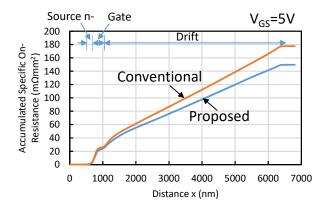

図8 従来型と提案型 LDMOS トランジスタの 界面に沿った方向の累積特性オン抵抗

Fig. 8. Accumulated specific on-resistances along the surface of the conventional and the proposed LDMOS transistors.

## 表 1 従来型と提案型 LDMOS トランジスタの 特性オン抵抗成分 (V<sub>GS</sub>=5V)

Table 1. Specific on-resistance components of the conventional and the proposed LDMOS transistors at  $V_{\rm GS}$ =5V.

| Region    | Conventional $(m\Omega mm^2)$ |       | Proposed $(m\Omega mm^2)$ |       |

|-----------|-------------------------------|-------|---------------------------|-------|

| Source n- | 4.5                           | 2.5%  | 3.6                       | 2.4%  |

| Channel   | 25.8                          | 14.5% | 24.4                      | 16.3% |

| Drift     | 147.4                         | 83.0% | 121.6                     | 81.3% |

| Total     | 177.6                         | 100%  | 149.7                     | 100%  |

図 9 従来型と提案型 LDMOS トランジスタの ブレークダウン直後の正孔電流密度分布

Fig. 9. Hole current density distributions just after the breakdown of the conventional and the proposed LDMOS transistors.

へ流れるため、その端へ向かって①の表面成分は低下し、結果として図 6 のIIのピークを形成する。したがって、このピークはその個所でのインパクトイオン化によるものではないため、表面へのダメージは非常に少ないと考える。図 6 のI のピークは、電子電流経路に沿ってゲート側ドリフト端に向けて高くなる電子電流密度により増加していくインパクトイオン化に起因するものであり、そのピーク位置はA の箇所と一致する。A の箇所からゲート領域に入っていくと電界のx 成分の低下にともないインパクトイオン化が減少する。したがって、A の箇所で発生するインパクトイオン化が真性 MOSFET 特性へ影響を与える。③の成分は、①と②に比べると非常に小さく、基板の深い領域を流れることから信頼性上のダメージを与えることはない。

#### 〈4・2〉 特性オン抵抗

図 8 に従来型と提案型 LDMOS トランジスタの界面に沿った方向の累積特性オン抵抗を示す。また、この累積特性オン抵抗から求めた、ソース n・、チャネル、そしてドリフトの各領域の特性オン抵抗成分を表 1 に示す。提案型の累積特性オン抵抗は、従来型に対しソースとチャネル領域で若干低下しているが、ドリフト領域で大きく低下していることが分かる。これは、提案型では、P・埋め込み層 1 と 2 及び FP1 と 2 により RESURF が強化されており、ドリフト領域へのドーピング濃度を上げることができたためである。

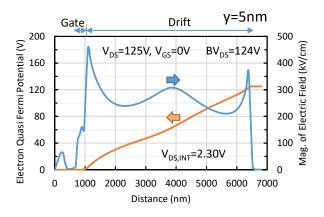

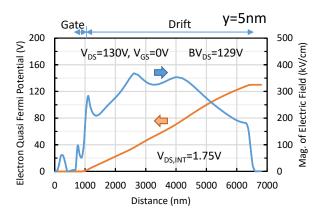

## 〈4·3〉 ブレークダウン

図9に従来型と提案型LDMOSトランジスタのブレークダウン直後の正孔電流密度分布を示す。どちらもドレインの下で正孔電流密度が高くなっており、その個所でブレークダウン(すなわちバルクブレークダウン)が発生している。したがって、ブレークダウン時にゲート酸化膜へのダメージはどちらも無く、これらのLDMOSをESD素子とし

#### (a) 従来型 LDMOS

## (b) 提案型 LDMOS

図 10 従来型と提案型 LDMOS トランジスタの ブレークダウン時における界面に沿う方向の電界強度と 電子の擬フェルミ電位プロファイル

Fig. 10. Electric field magnitude and electron quasi Fermi potential profiles along the surface at the breakdown of the conventional and the proposed LDMOS transistors.

図 11 RonA-BVDSの特性

Fig. 11.  $R_{on}A$ - $BV_{DS}$  characteristics.

て使用した場合、ESD 耐性は高いものと考える。

図10に従来型と提案型LDMOSトランジスタのブレークダウン時における界面に沿った方向の電界強度と電子の擬フェルミ電位プロファイルを示す。従来型の電界強度は、両ドリフト端で高くなっており、ゲート側ドリフト端で4.57×10 $^5$  V/cm、ドレイン側ドリフト端で3.70×10 $^5$  V/cmとなっている。一方、提案型の電界強度は、ドリフト領域の中央近傍で高く、最大で3.68×10 $^5$  V/cm (x=2600nm)となっており、提案型の最大電界強度が従来型より低く抑えられている。これは、提案型のRESURFが従来型より有効に効いていることを示しており、結果として提案型の $BV_{DS}$ が従来型より高くなる。

図 10 から、ソースに対する電圧を表している電子の擬フェルミ電位は、提案型と従来型ともにドリフト領域ではRESURFによりドレインからゲート端へ向けてほぼ直線的に低下しており、ゲート端(真性 MOSFET のドレイン)で十分に低下していることが分かる。この場合、真性MOSFET のドレイン電圧  $V_{DS,INT}$ は、提案型で 1.75V (at  $V_{DS}=130$ V)、従来型で 2.30V (at  $V_{DS}=125$ V)になっている。これらの電圧によるゲート酸化膜内の電界強度はゲート酸化膜厚 12nm に対し、提案型で 1.5 MV/cm、従来型で 1.9 MV/cm になり、いずれも酸化膜破壊電界強度(>10MV/cm)に対し十分な余裕がある。

また、図10から、提案型のゲート側ドリフト端の電界強度は、従来型の約半分になっており、その個所でのインパクトイオン化は、提案型の方で低くなることが分かる。したがって、繰り返しESDストレスにおける、提案型の真性MOSFETの特性変化は、従来型に対し小さいものと推測する。

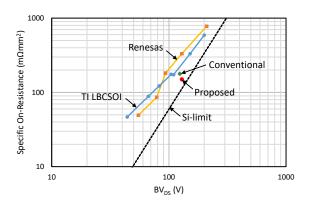

## 〈4·4〉 特性オン抵抗 対 ブレークダウン電圧の特性

図 11 に従来型と提案型 LDMOS トランジスタの $R_{on}A$ - $BV_{DS}$ の特性を既に発表されたもの  $^{(12)}$ と比較して示す。これから、従来型の特性  $(R_{on}A$ =178 $m\Omega$ mm²,  $BV_{DS}$ =124V)は TI LBCSOI に近いが、提案型の特性  $(R_{on}A$ =150 $m\Omega$ mm²,  $BV_{DS}$ =129V)は Si リミットに近く、最先端レベルにあることが分かる。

#### 5. まとめ

車載用途を含めた高信頼性・低特性オン抵抗 100V 動作のLDMOSトランジスタとして、ドリフト層を 2 段階の P-埋め込み層で囲うデュアル RESURF 構造とし、フィールド・プレートも 2 段階とする構造を提案し、その特性をシミュレーションで確認した。従来型では最大動作ゲート電圧  $V_{GS}=5V$  で CE の発生があるが、提案型ではそのゲート電圧で CE の発生はない。また、提案型ではゲート側ドリフト端(真性 MOSFET のドレイン)近傍でインパクトイオン化により発生する正孔電流密度が従来型に比べて 1 桁以上低く、高ホットキャリア耐性を期待できる。提案型の特性オン抵抗  $R_{on}A$  は 150m $\Omega$ mm $^2$ 、ブレークダウン電圧  $BV_{DS}$ は 129Vとなっており、 $R_{on}A$ - $BV_{DS}$ 特性は最先端レベルにある。更

に、ブレークダウンの箇所は、従来型も提案型もバルクであるため、ブレークダウン時にゲート酸化膜へのダメージはなく、提案型の ESD 耐性は従来型と同程度に高いものと考える。しかしながら、繰り返し ESD ストレスを考慮した場合、ブレークダウン時のデバイス内部の電界強度から提案型の ESD 耐性が従来型より優れているものと推測する。

#### 6. 謝辞

本研究で用いたデバイス・シミュレータは、アドバンスソフト社から借用させて頂いているものであり、アドバンスソフト社に深謝申し上げる。なお、このシミュレータは、国立研究開発法人科学技術振興機構 A-STEP プログラムの助成を受けてアドバンスソフト社で開発されたものである。

## 文 献

- (1) C.-C. Cheng, H. L. Chou, F. Y. Chu, R. S. Liou, Y. C. Lin, K. M. Wu, Y. C. Jong, C. L. Tsai, J. Cai, and H. C. Tuan: "Investigation of Parasitic BJT Turn-on Enhanced Two-stage Drain Saturation Current in High-voltage NLDMOS", 23rd International Symposium on International Power Semiconductor Devices & IC's (ISPSD), pp.208–210(2011)

- (2) S. Reggiani, G. Baccarani, E. Gnani, A. Gnudi, M. Denison, S. Pendharkar, R. Wise, and S. Seetharaman, : "Explanation of the Rugged LDMOS Behavior by Means of Numerical Analysis", IEEE Transactions on Electron Devices, Vol.56, No.11 pp.2811-2818 (2009)

- (3) S. Poli, S. Reggiani, R. K. Sharma, M. Denison, E. Gnani, A. Gnudi, and G. Baccarani: "Optimization and Analysis of the Dual n/p-LDMOS Device," IEEE Trans. Electron Devices, Vol. 59, No. 3, pp. 745-753 (2012)

- (4) J. Chen: "HV EDMOS Design with Expansion Regime Suppression", Master Thesis of Applied Science, Department of Electrical and Computer Engineering, University of Toronto, (2013)

- (5) 松田順一,神山雅貴,築地伸和,小林春夫:「高信頼性 Nch-LDMOSの提案」,電気学会研究会資料,電子デバイス 半導体電力変換 合同研究会,EDD-15-066,SPC-15-148,pp. 11-16 (2015)

- (6) 松田順一, 小島潤也, 神山雅貴, 築地伸和, 小林春夫: 「高信頼性・低オン抵抗デュアル RESURF Nch-LDMOS の提案」, 第63 回応用物理学会春季学術講演会, 東工大 大岡山キャンパス, 20a·S422-11 (2016)

- (7) P. L. Hower, J. Lin, and S. Merchant: "Snapback and Safe Operating Area of LDMOS Transistors", Technical Digest of International Electron Devices Meeting, IEMD'99, pp.193-196(1999)

- (8) 山口憲,原田昌紀,桑原匠史,大倉康幸:「デバイスシミュレーション」、アドバンスシミュレーション(アドバンスソフト株式会社)、 Vol. 21, pp. 39-69, (2015).

- (9) C. Hu, S. C. Tam, F.-C. Hsu, P.-K. Ko, T.-Y. Chan, and K. W. Terrill: "Hot-electron-induced MOSFET degradation, monitor, and improvement", IEEE Trans. Electron Devices, Vol. 32, No. 2, pp. 375-385 (1985)

- (10) C. T. Kirk: "A Theory of Transistor Cutoff Frequency (ft) Falloff and High Current Densities", IRE Transactions on Electron Devices, Vol. 9, No. 2 pp.164–174(1962)

- (1 1) H. C. Poon, H. K. Gummel, and D. L. Scharfetter: "High Injection in Epitaxial Transistors", IEEE Transactions on Electron Devices, Vol.16, No.5 pp.455-457 (1969)

- (12) http://www.dongbuhitek.co.kr/data/cyberpr/4.pdf