# Gray-code入力DA変換器の検討

群馬大学理工学府 修士2年 姜 日晨\* Gopal Adhikari 小林 春夫

# 目次

- l. 研究背景•目的

- II. 提案するGray-code入力のDACの構成と動作

- III. SPICEによるシミュレーション検証

- IV. まとめ

# 目次

- l. 研究背景•目的

- II. 提案するGray-code入力のDACの構成と動作

- III. SPICEによるシミュレーション検証

- IV. まとめ

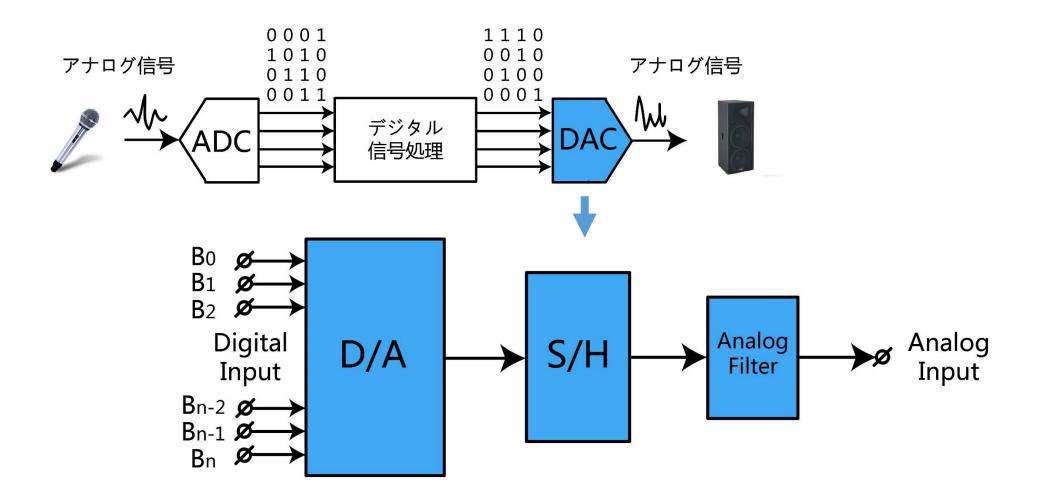

#### デジタル-アナログコンバータ(DAC、ダック)

#### 研究目的

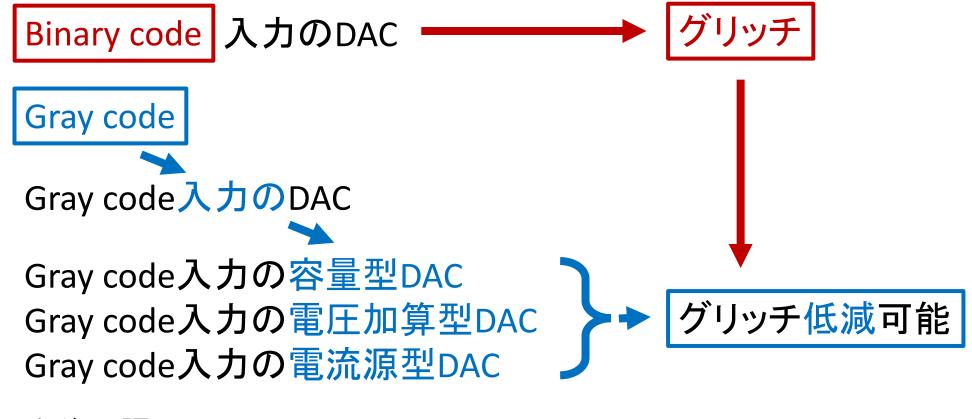

Gray-codeを入力としての綺麗な構成のDACは実現が難しいと考えられてきた.

本論文ではGray-code入力のDACが実現できることを示す.

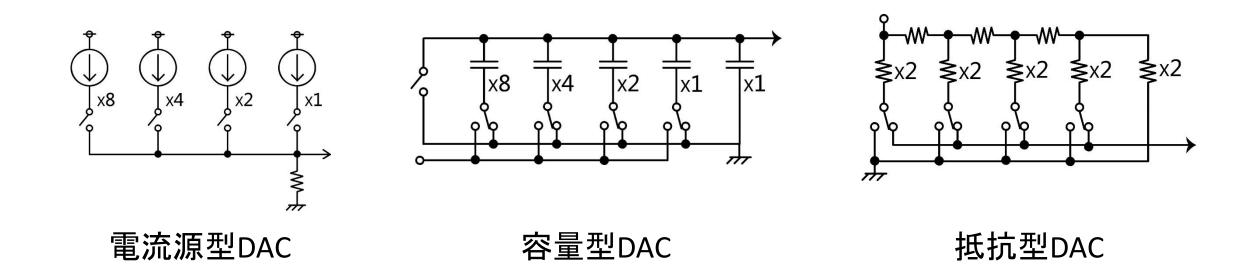

#### D/A変換器の基本的なアーキテクチャ

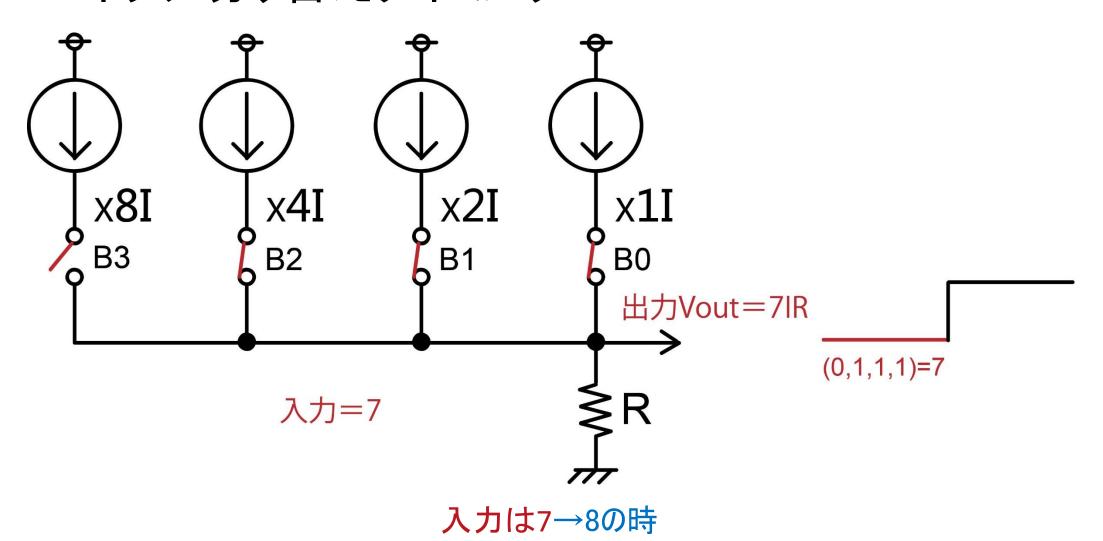

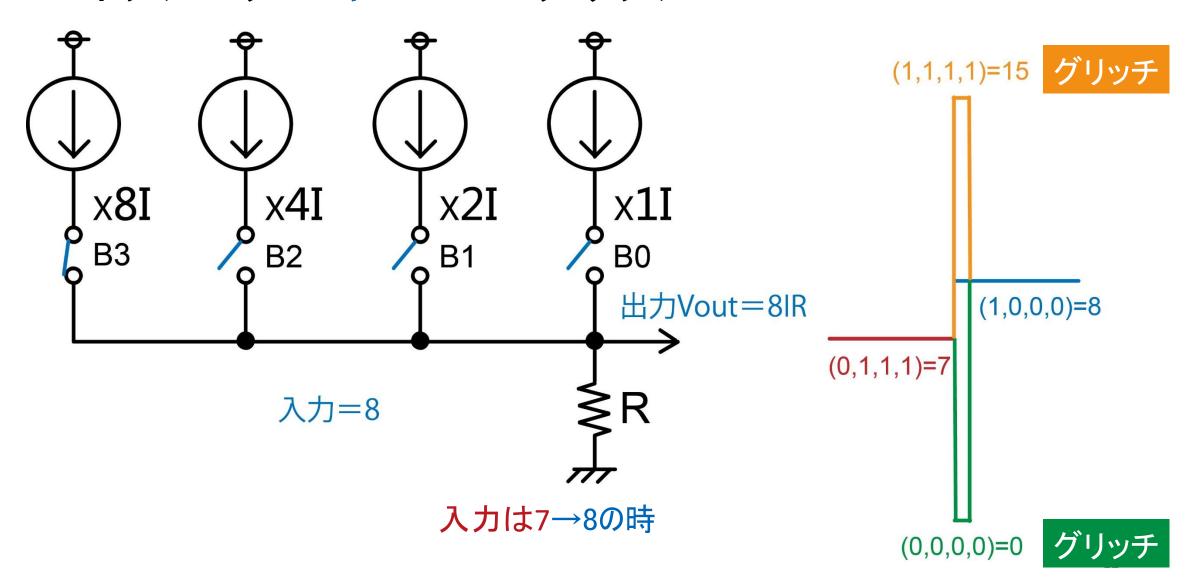

スイッチは2進数(バイナリコード、Binary code)で駆動 一 グリッチ

# グリッチ (Glitch) の影響

グラフィックデスプレイでのグリッチ

# グリッチの発生原理

| Decimal numbers | Natural Binary code |  |

|-----------------|---------------------|--|

| 0               | 0000                |  |

| 1               | 0001                |  |

| 2               | 0010                |  |

| 3               | 0011                |  |

| 4               | 0100                |  |

| 5               | 0101                |  |

| 6               | 0110                |  |

| 7               | 0111                |  |

| 8               | 1000                |  |

| 9               | 1001                |  |

| 10              | 1010                |  |

| 11              | 1011                |  |

| 12              | 1100                |  |

| 13              | 1101                |  |

| 14              | 1110                |  |

| 15              | 1111                |  |

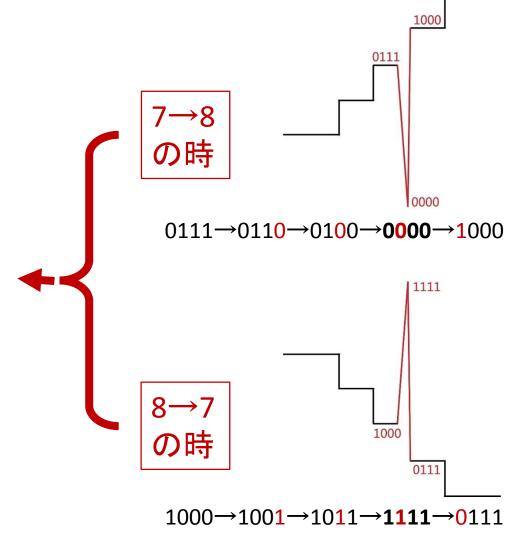

最上位ビット(MSB)が変化(中央値の付近)

ワーストケース

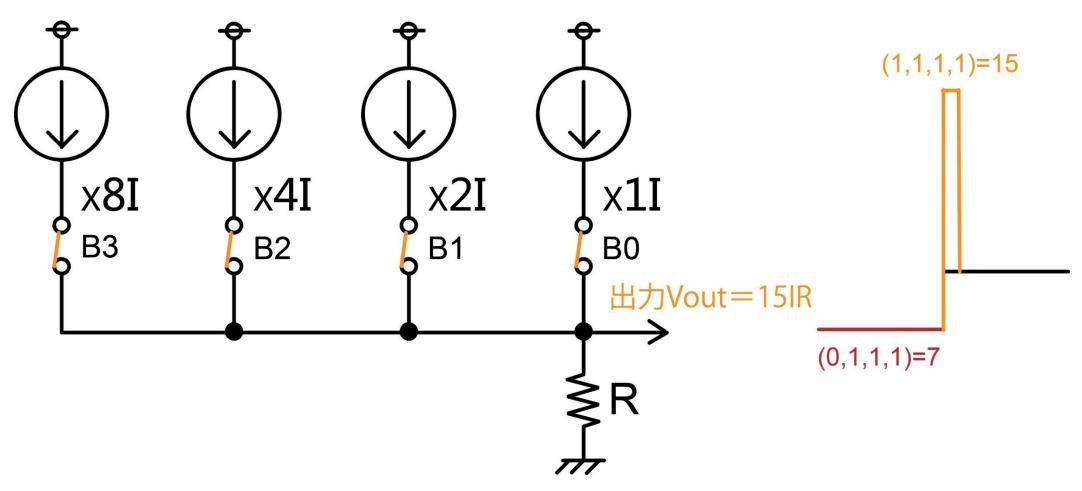

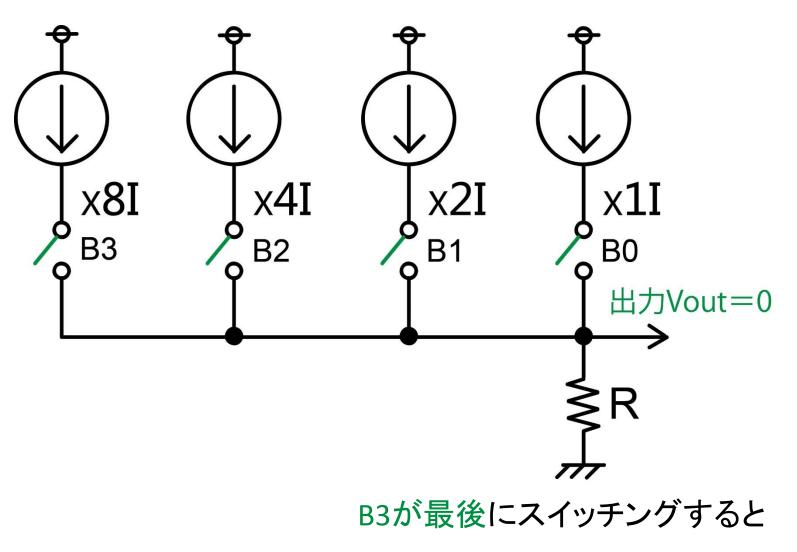

## スイッチ切り替えタイミング

#### スイッチ切り替えタイミング その 1

B3が最初にスイッチングすると

## スイッチ切り替えタイミング その 1

(0,1,1,1)=7 (0,0,0,0)=0

#### スイッチングスキュー → グリッチ

# グレイコード (Gray-code)

グレイコード: 前後に隣接する符号間のハミング距離が必ず1

ベル研究所のフランク・グレイが1947年の特許出願書で最初に使用した。

#### グレイコードD/A変換器

Binary code と Gray code の変換が容易(EXOR)

$(G_n=B_{n+1}\oplus B_n)$

Gray code 入力のDA変換器

グリッチが小さくできる

Binary code:  $0111 \rightarrow 0110 \rightarrow 0100 \rightarrow 0000 \rightarrow 1000$

Gray code: 0100→1100

| Decimal numbers | Natural<br>Binary code | Gray code |

|-----------------|------------------------|-----------|

| 0               | 0000                   | 0000      |

| 1               | 0001                   | 0001      |

| 2               | 0010                   | 0011      |

| 3               | 0011                   | 0010      |

| 4               | 0100                   | 0110      |

| 5               | 0101                   | 0111      |

| 6               | 0110                   | 0101      |

| 7               | 0111                   | 0100      |

| 8               | 1000                   | 1100      |

| 9               | 1001                   | 1101      |

| 10              | 1010                   | 1111      |

| 11              | 1011                   | 1110      |

| 12              | 1100                   | 1010      |

| 13              | 1101                   | 1011      |

| 14              | 1110                   | 1001      |

| 15              | 1111                   | 1000      |

# 目次

- 1. 研究背景•目的

- II. 提案するGray-code入力のDACの構成と動作

- III. SPICEによるシミュレーション検証

- IV. まとめ

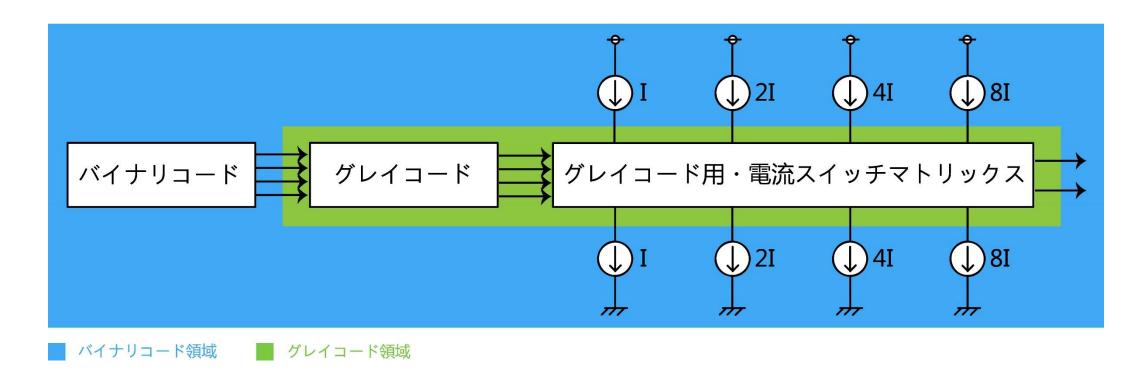

## 提案するGray-code入力のDACの構成と動作

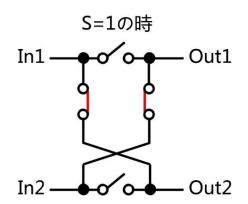

- 1. Gray-code入力の電流源型DAC (I-DAC)

- 2. Gray-code入力の容量型DAC (C-DAC)

- 3. Gray-code入力の電圧加算型DAC (V-DAC)

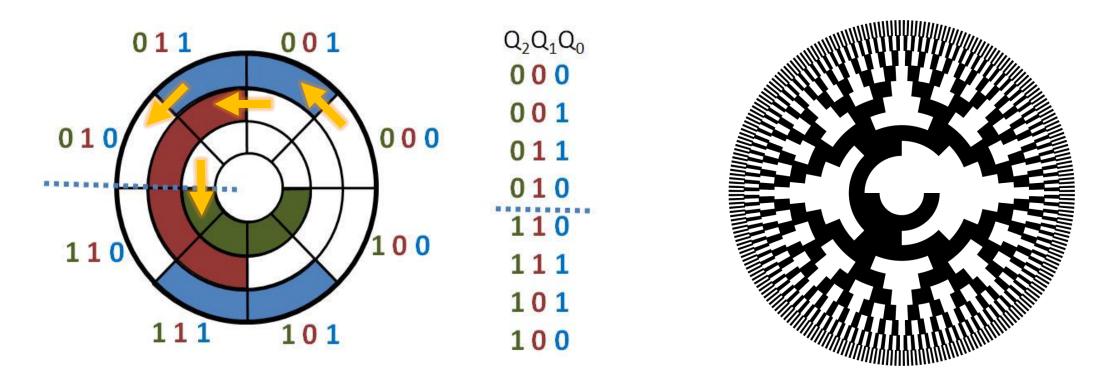

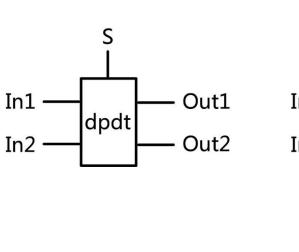

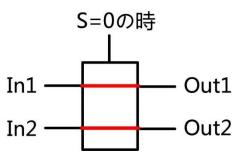

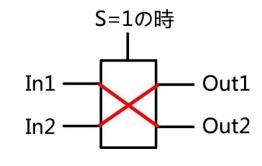

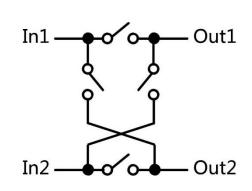

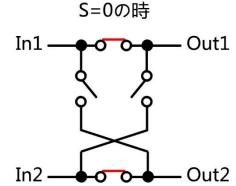

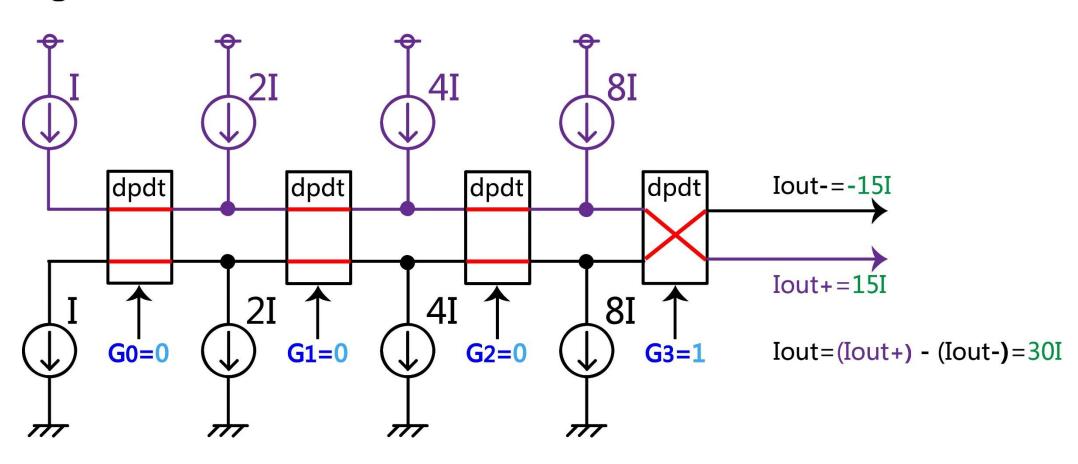

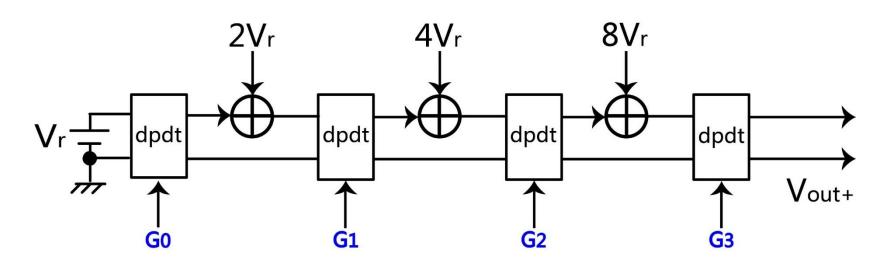

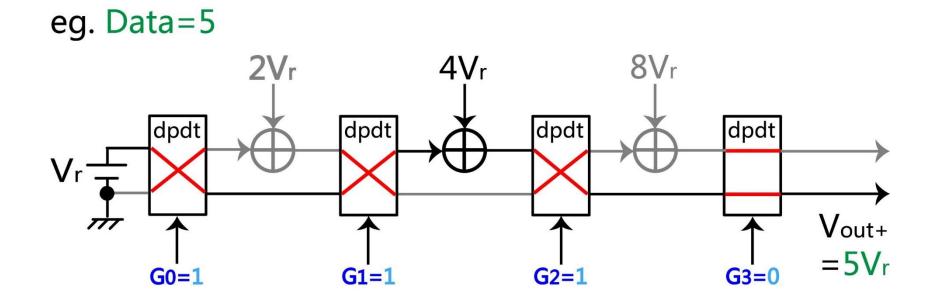

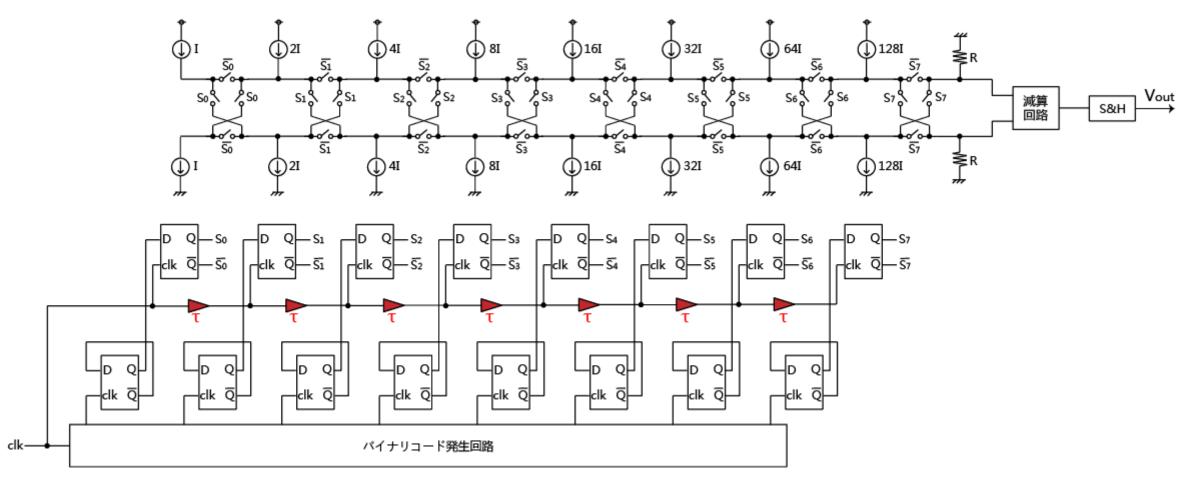

#### 電流/電圧スイッチマトリックス

パラレル接続

クロス接続

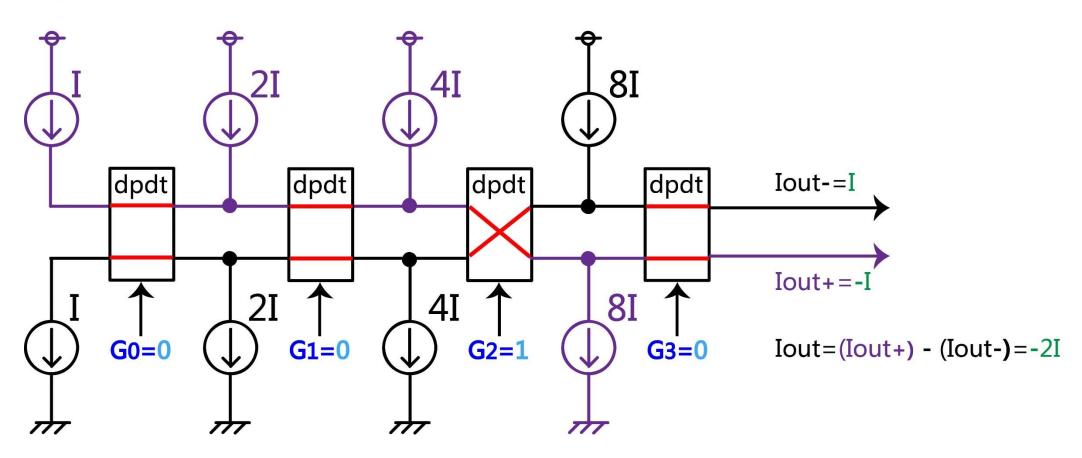

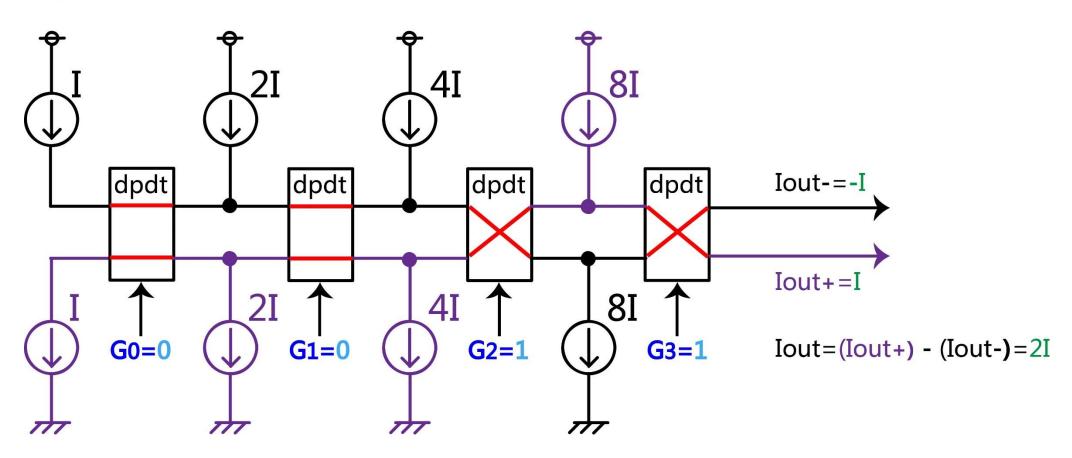

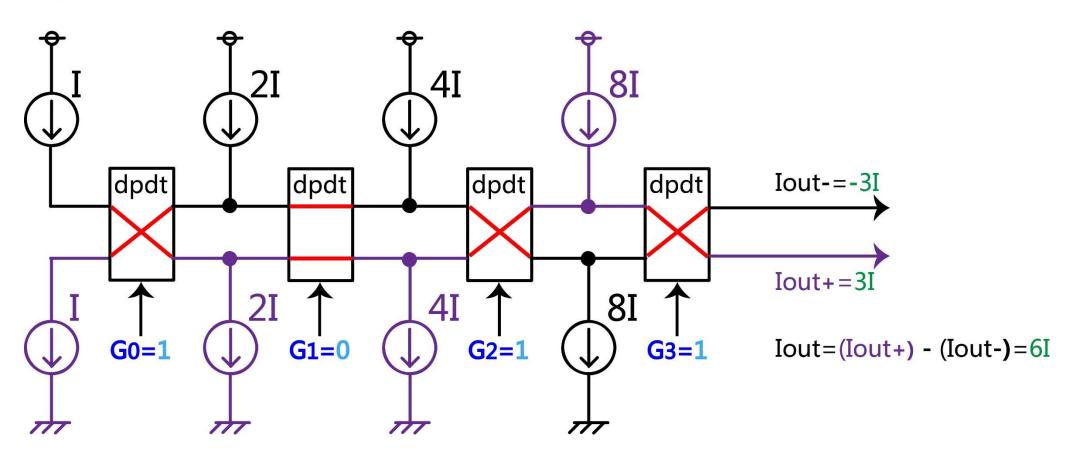

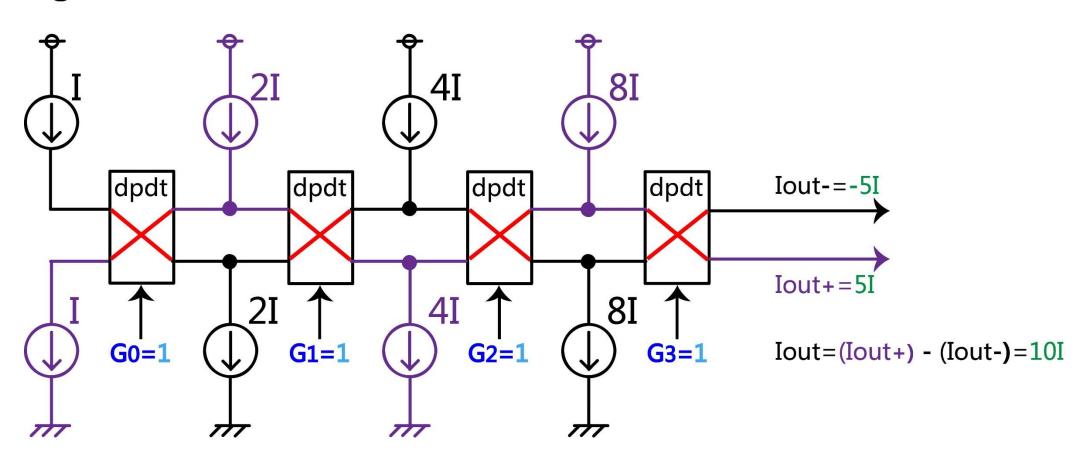

double-pole double-throw(dpdt, 双極双投) スイッチで実現

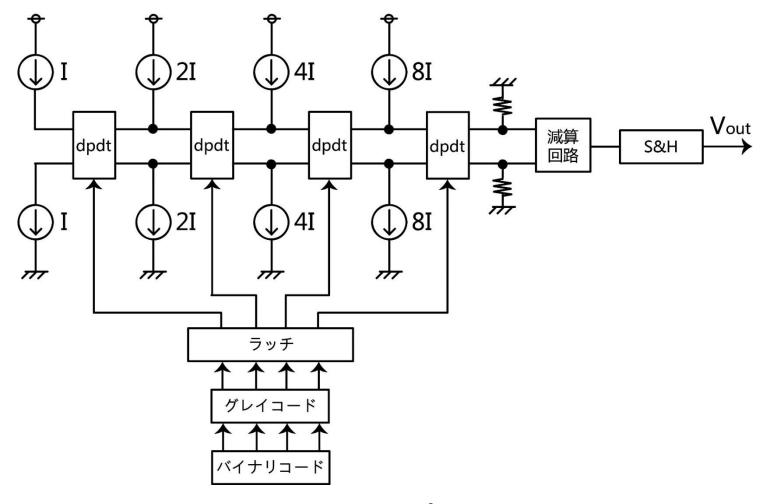

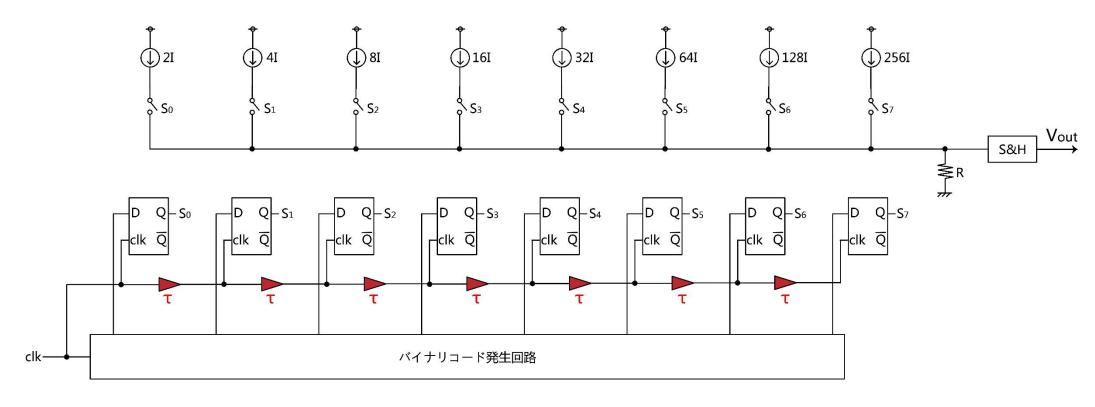

## 1. Gray-code入力の電流源型DAC

Gray-code入力の電流源型DAC

#### コード変換

バイナリの電流源順番に対応できるGray-code入力

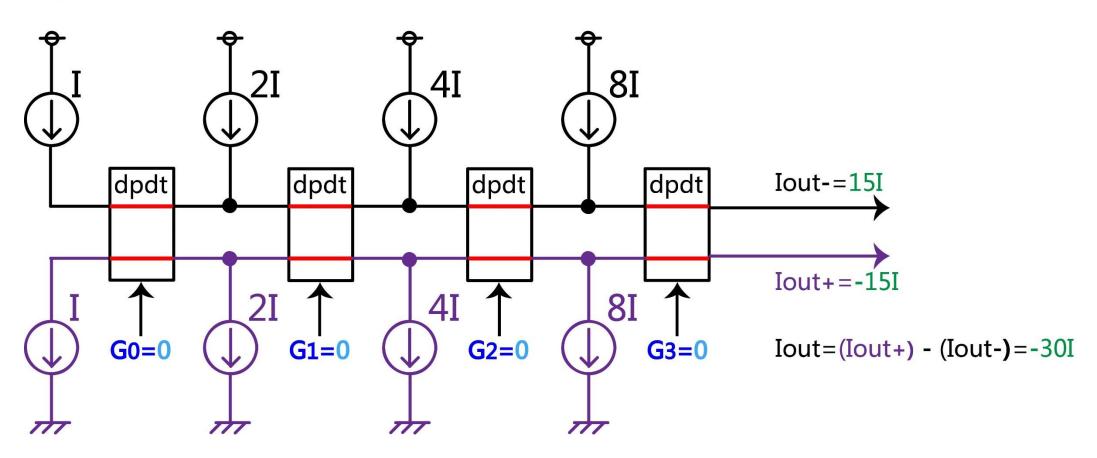

## Gray-code入力のI-DACの動作(データ=0の場合)

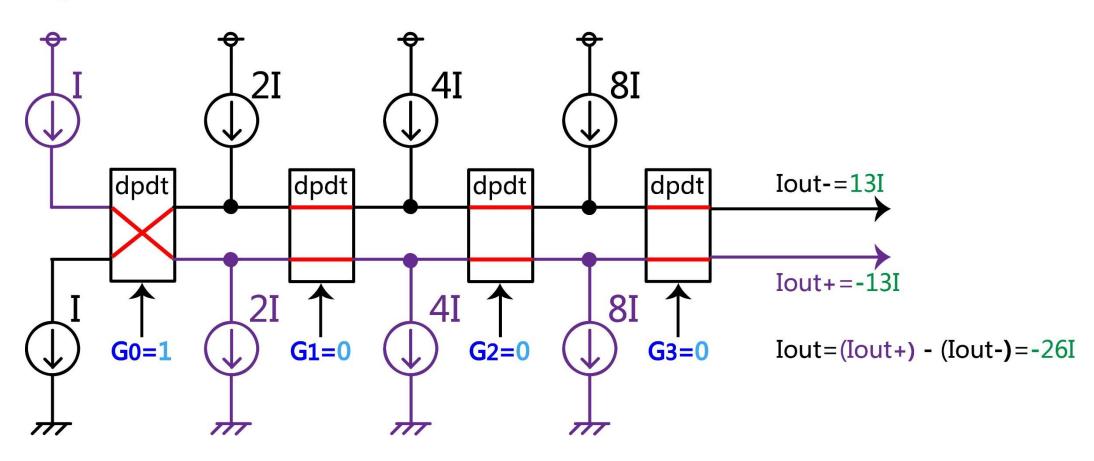

## Gray-code入力のI-DACの動作(データ=1の場合)

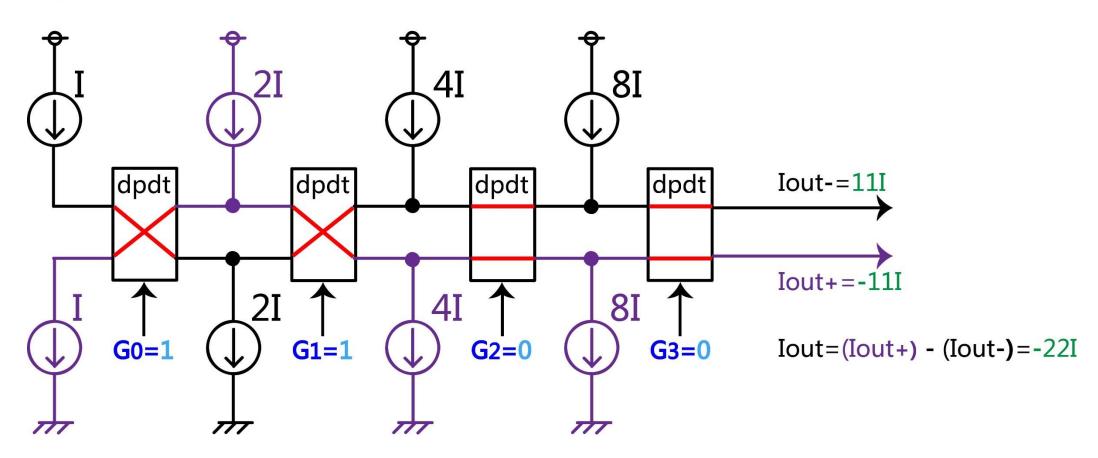

## Gray-code入力のI-DACの動作(データ=2の場合)

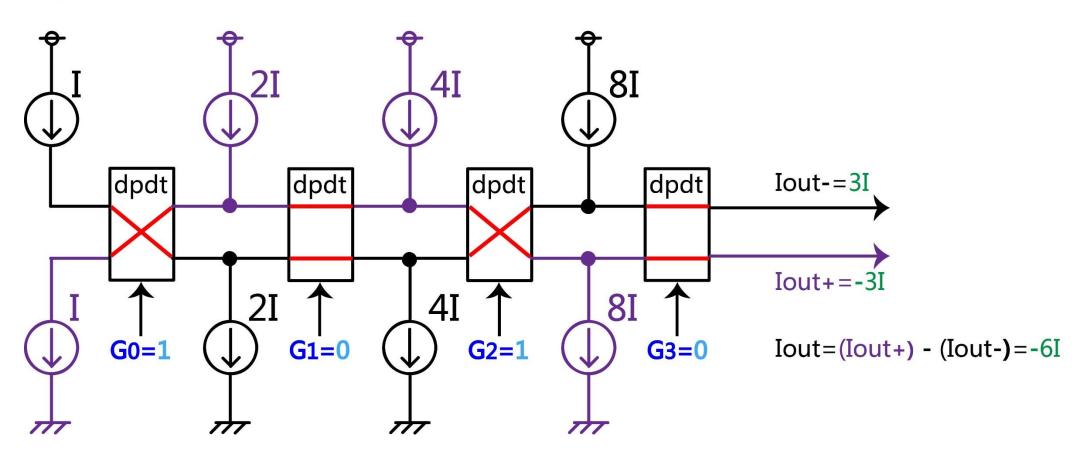

## Gray-code入力のI-DACの動作(データ=3の場合)

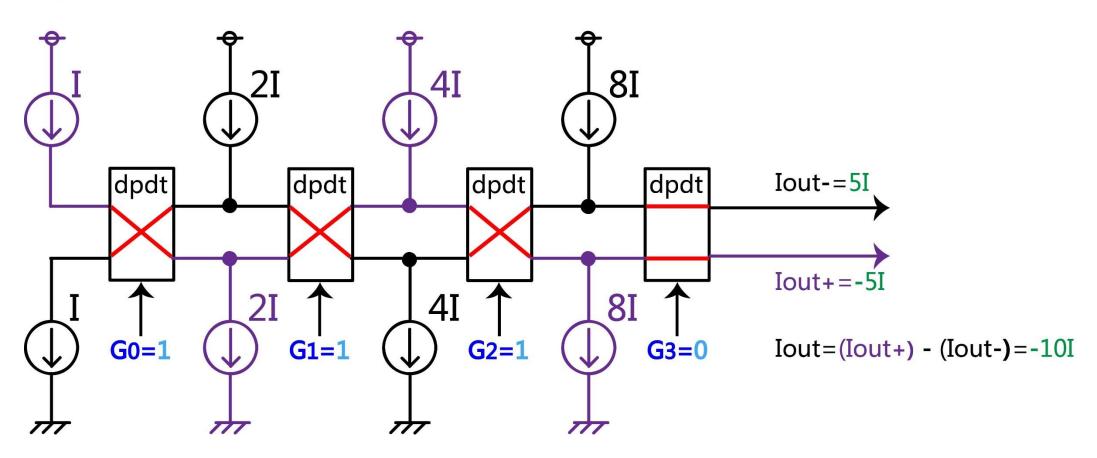

## Gray-code入力のI-DACの動作(データ=4の場合)

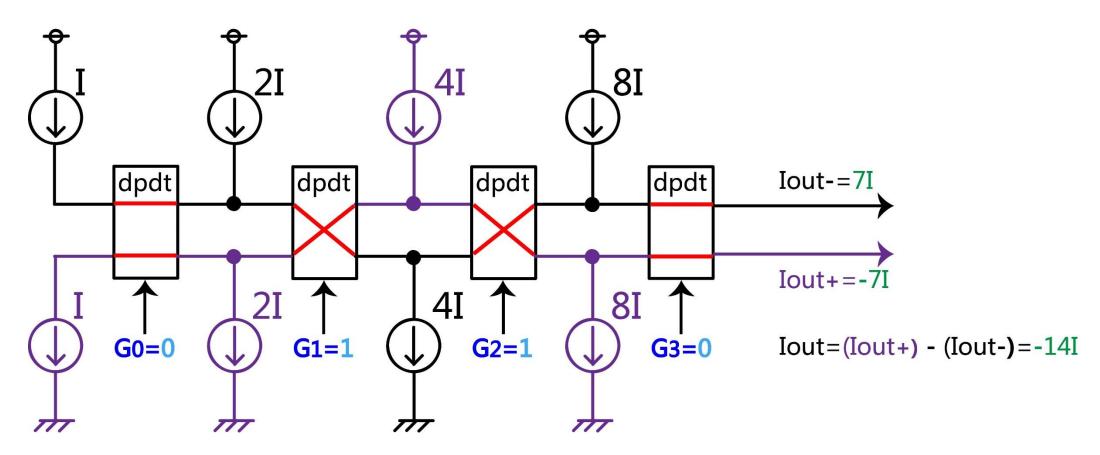

## Gray-code入力のI-DACの動作(データ=5の場合)

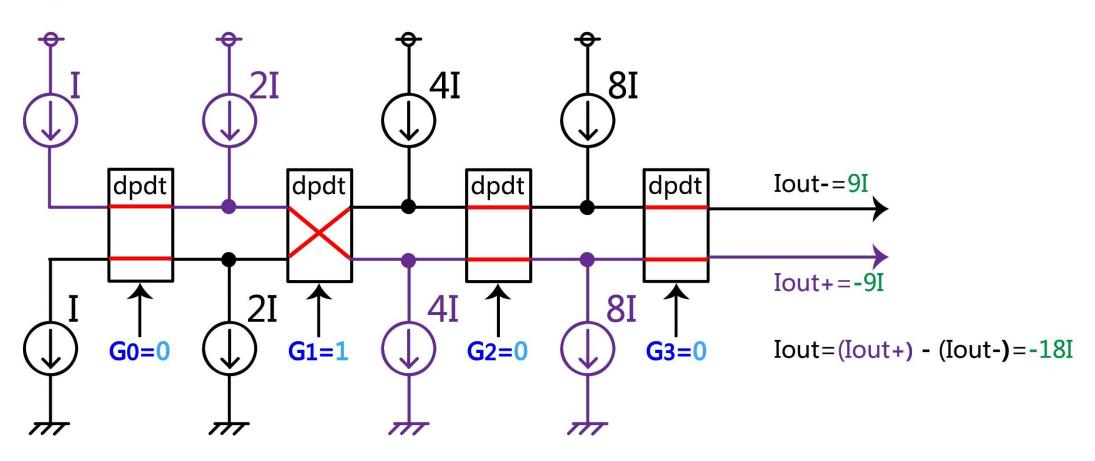

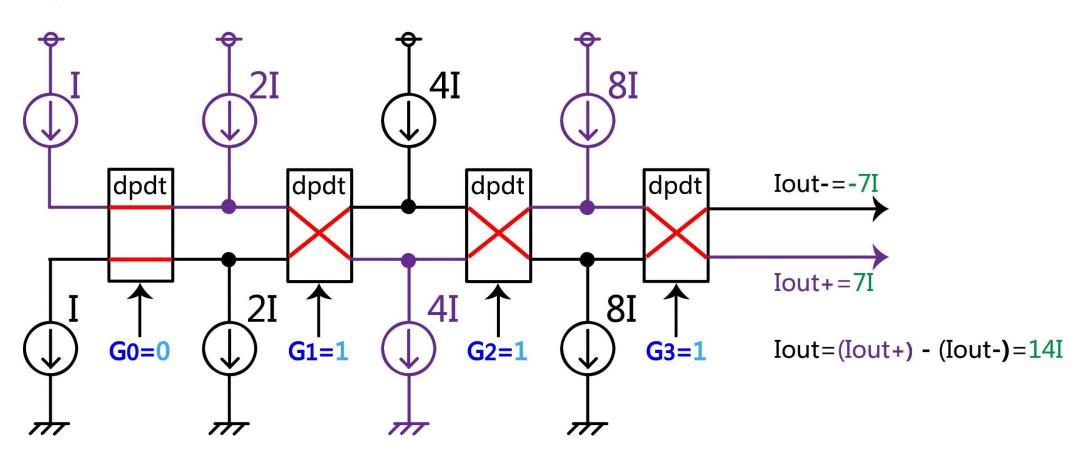

#### Gray-code入力のI-DACの動作(データ=6の場合)

## Gray-code入力のI-DACの動作(データ=7の場合)

## Gray-code入力のI-DACの動作(データ=8の場合)

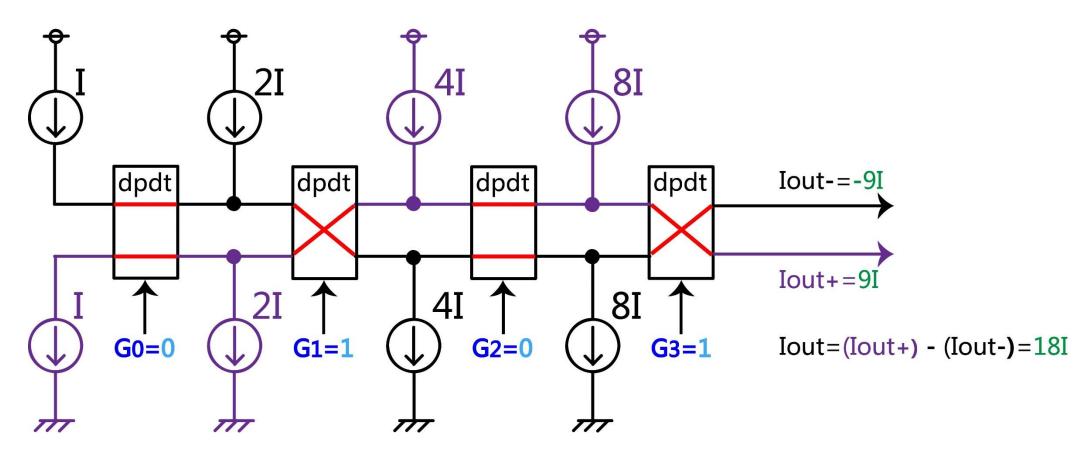

#### Gray-code入力のI-DACの動作(データ=9の場合)

## Gray-code入力のI-DACの動作(データ=10 の場合)

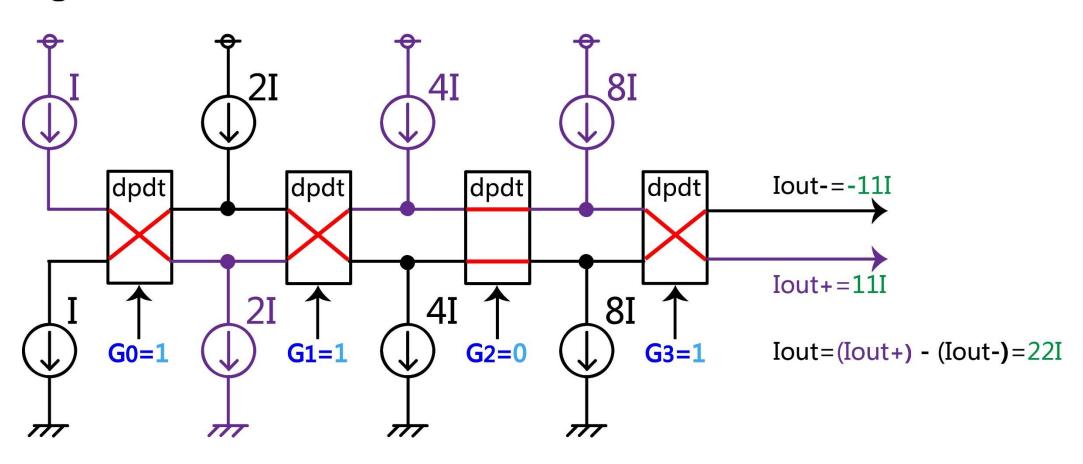

## Gray-code入力のI-DACの動作(データ=11の場合)

## Gray-code入力のI-DACの動作(データ=12の場合)

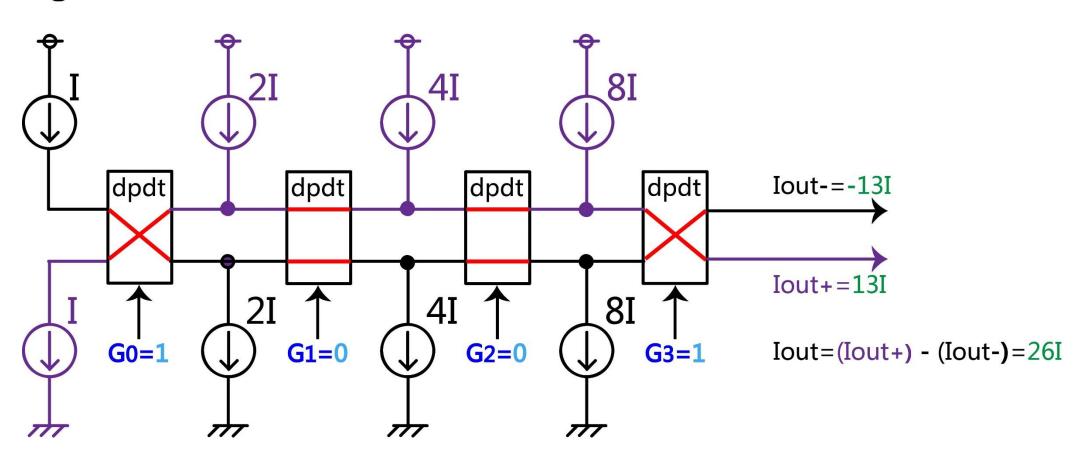

## Gray-code入力のI-DACの動作(データ=13 の場合)

## Gray-code入力のI-DACの動作(データ=14の場合)

## Gray-code入力のI-DACの動作(データ=15の場合)

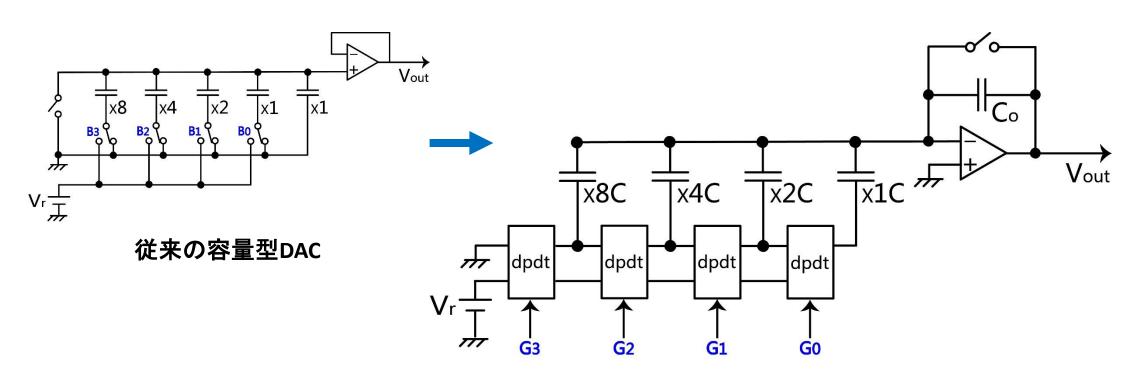

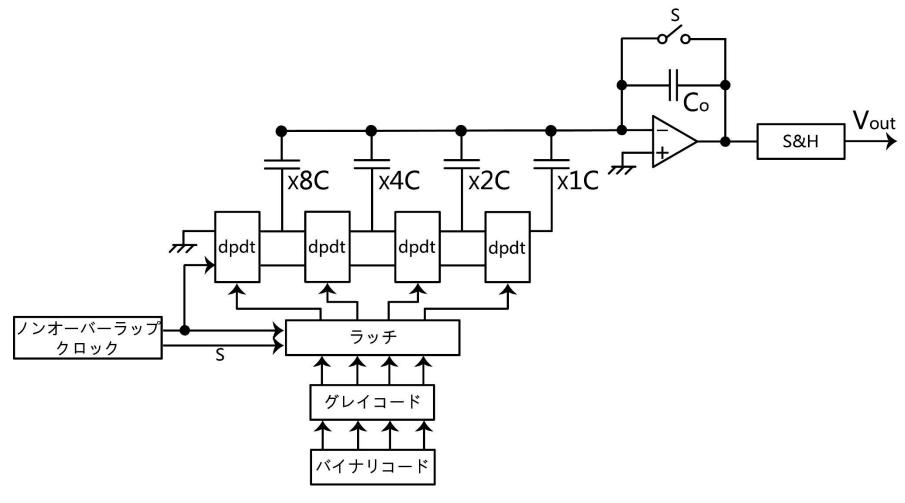

# 2. Gray-code入力の容量型DAC

Gray-code入力の容量型DAC

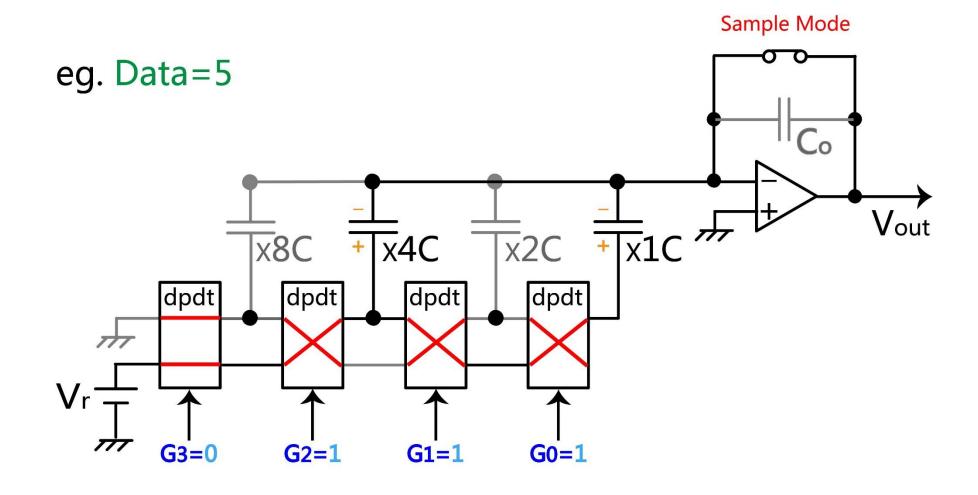

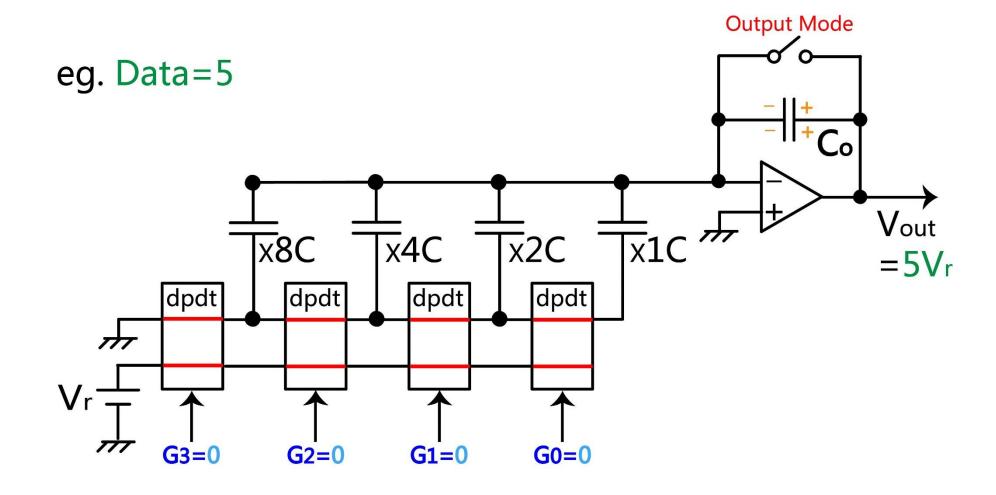

# Gray-code入力のC-DACの動作(データ=5の場合)

# Gray-code入力のC-DACの動作(データ=5の場合)

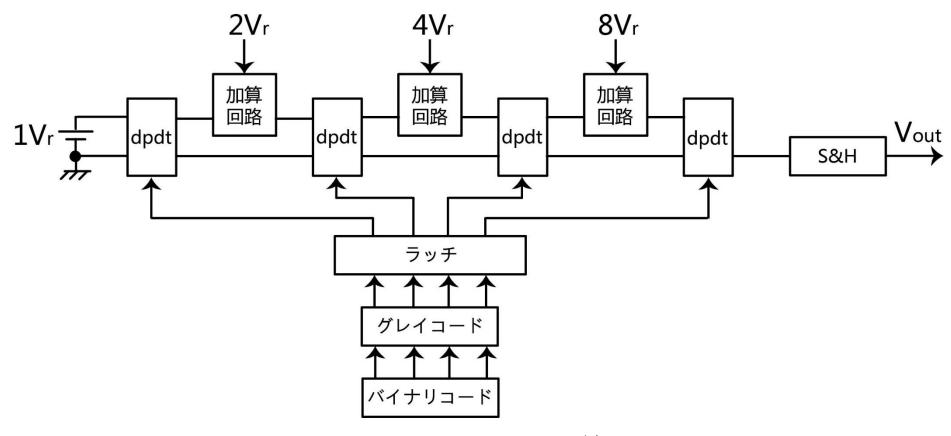

# 3. Gray-code入力の電圧加算型DAC

Gray-code入力の電圧加算型DAC

#### Gray-code入力のV-DACの動作(データ=5の場合)

# 目次

- I. 研究背景·目的

- II. 提案するGray-code入力のDACの構成と動作

- III. SPICEによるシミュレーション検証

- IV. まとめ

#### SPICEによるシミュレーション検証

- 1. Gray-code入力の電流出力型DAC (I-DAC) のシミュレーション

- 2. Gray-code入力の容量型DAC (C-DAC) のシミュレーション

- 3. Gray-code入力の電圧加算型DAC (V-DAC) のシミュレーション

- 4. グリッチ除去の検証

<sup>\*</sup> LTspice IVを使用

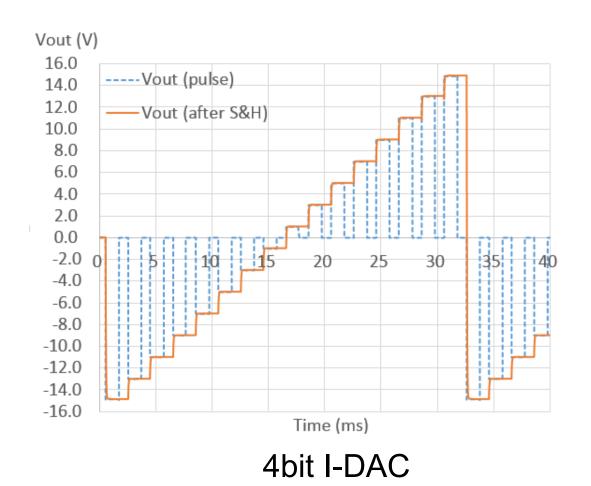

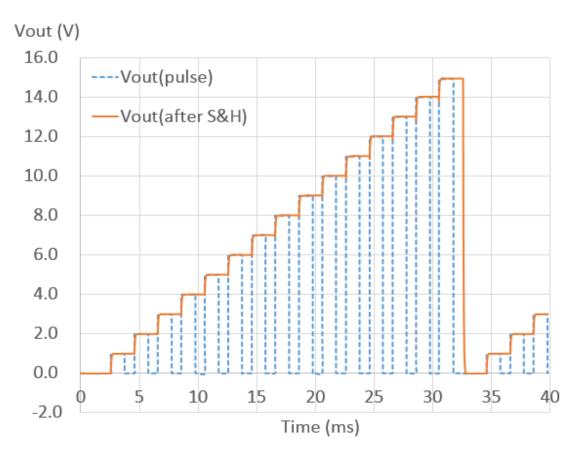

# 1. Gray-code入力のI-DACのSPICE実現

Gray-code入力の電流出力型DAC

# 1. Gray-code入力のI-DACのシミュレーション

Vout (V) -10 -20 -30 Time (ms) 8bit I-DAC

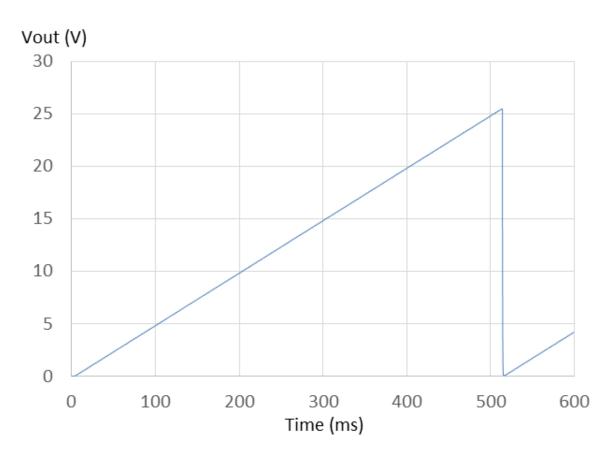

# 2. Gray-code入力のC-DACのSPICE実現

Gray-code入力の容量型DAC

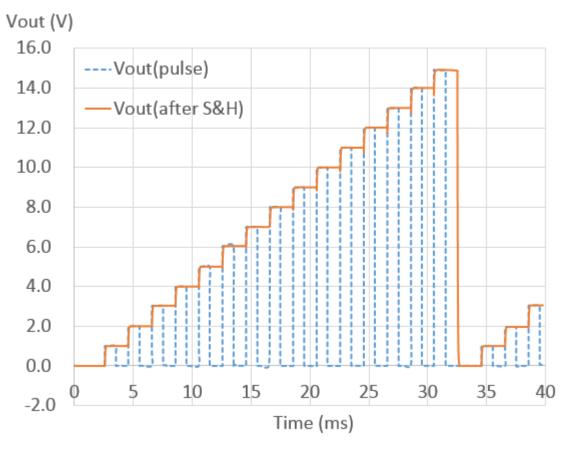

# 2. Gray-code入力のC-DACのシミュレーション

4bit C-DAC

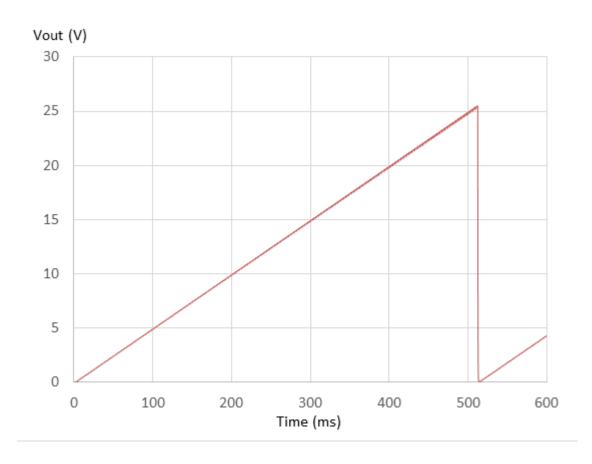

8bit C-DAC

# 3. Gray-code入力のV-DACのSPICE実現

Gray-code入力の電圧加算型DAC

# 3. Gray-code入力のV-DACのシミュレーション

4bit V-DAC

8bit V-DAC

#### 4. グリッチ除去の検証

スイッチング遅延がついた従来のI-DAC (8 bit)

#### 4. グリッチ除去の検証

スイッチング遅延がついたGray-code入力のI-DAC (8 bit)

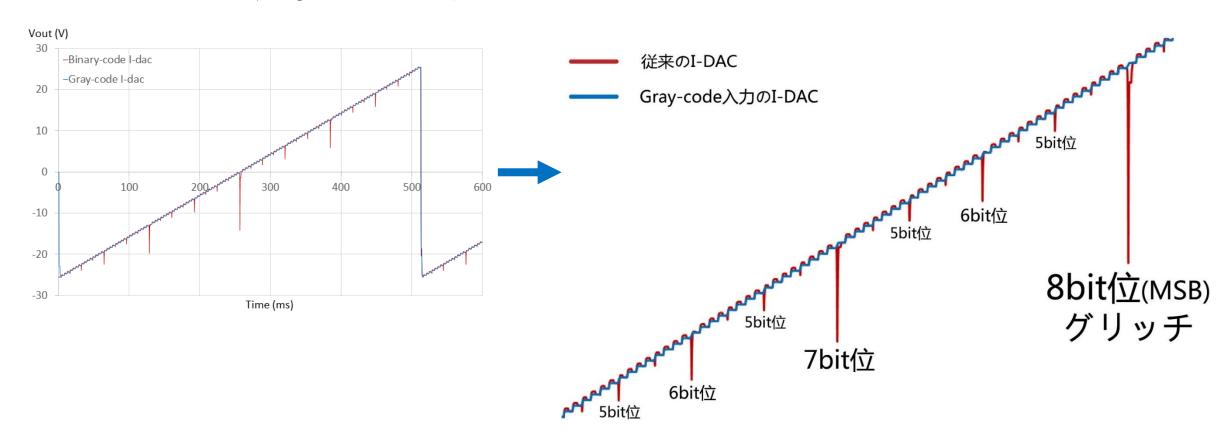

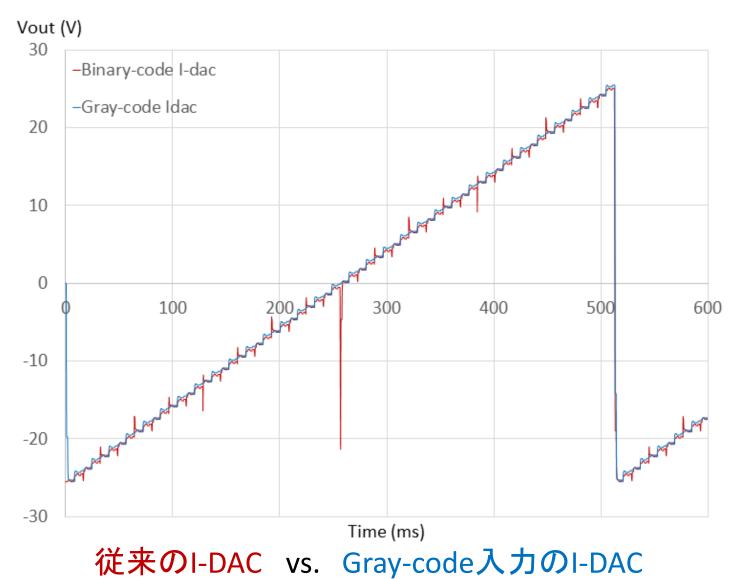

#### アップスウィーピング

従来のI-DAC vs. Gray-code入力のI-DAC

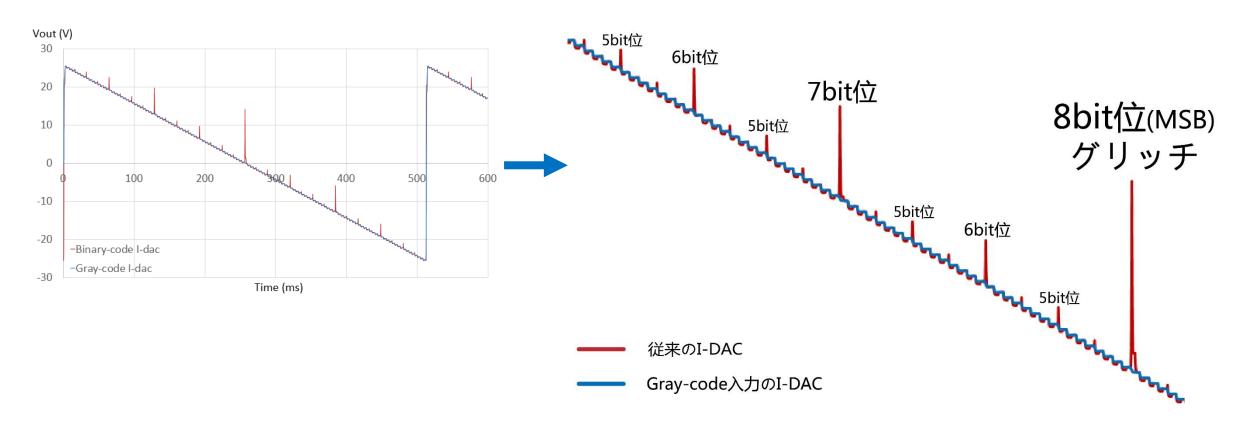

#### ダウンスウィーピング

従来のI-DAC vs. Gray-code入力のI-DAC

#### ランダムなスイッチング遅延

#### 目次

- I. 研究背景·目的

- II. 提案するGray-code入力のDACの構成と動作

- III. SPICEによるシミュレーション検証

- IV. まとめ

#### まとめ

#### 今後の課題:

電圧/電流スイッチマトリックスのMOSFETでの設計

#### Q/A

Q:この研究は先行研究に比べて発展された点は何ですか。

A:研究背景でお話したように、Gray-codeを入力としての綺麗な構成のDACは実現が難しいと考えられています。本論文ではGray-code入力のDACが実現できることを示します。